Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 38                                                                            |

| Program Memory Size        | 32KB (11K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 512 x 8                                                                       |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                     |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv32ka304-i-mv |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

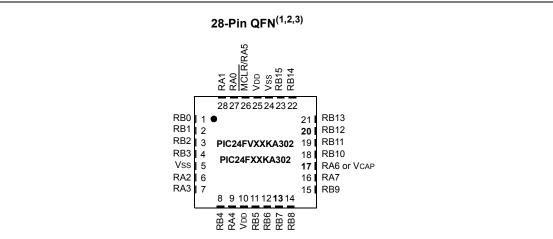

## **Pin Diagrams**

| D:  | eatures                                                   |                                                           |

|-----|-----------------------------------------------------------|-----------------------------------------------------------|

| Pin | PIC24FVXXKA302                                            | PIC24FXXKA302                                             |

| 1   | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0      | PGED1/AN2/ULPWU/CTCMP/C1IND/C2INB/C3IND/U2TX/CN4/RB0      |

| 2   | PGEC1/AN3/C1INC/C2INA/U2RX/CTED12/CN5/RB1                 | PGEC1/AN3/C1INC/C2INA/U2RX/CTED12/CN5/RB1                 |

| 3   | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2        | AN4/C1INB/C2IND/SDA2/T5CK/T4CK/U1RX/CTED13/CN6/RB2        |

| 4   | AN5/C1INA/C2INC/SCL2/CN7/RB3                              | AN5/C1INA/C2INC/SCL2/CN7/RB3                              |

| 5   | Vss                                                       | Vss                                                       |

| 6   | OSCI/AN13/CLKI/CN30/RA2                                   | OSCI/AN13/CLKI/CN30/RA2                                   |

| 7   | OSCO/AN14/CLKO/CN29/RA3                                   | OSCO/AN14/CLKO/CN29/RA3                                   |

| 8   | SOSCI/AN15/U2RTS/CN1/RB4                                  | SOSCI/AN15/U2RTS/CN1/RB4                                  |

| 9   | SOSCO/SCLKI/U2CTS/CN0/RA4                                 | SOSCO/SCLKI/U2CTS/CN0/RA4                                 |

| 10  | Vdd                                                       | VDD                                                       |

| 11  | PGED3/ASDA1 <sup>(2)</sup> /SCK2/CN27/RB5                 | PGED3/ASDA1 <sup>(2)</sup> /SCK2/CN27/RB5                 |

| 12  | PGEC3/ASCL1 <sup>(2)</sup> /SDO2/CN24/RB6                 | PGEC3/ASCL1 <sup>(2)</sup> /SDO2/CN24/RB6                 |

| 13  | U1TX/C2OUT/OC1/INT0/CN23/RB7                              | U1TX/INT0/CN23/RB7                                        |

| 14  | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                          | SCL1/U1CTS/C3OUT/CTED10/CN22/RB8                          |

| 15  | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                        | SDA1/T1CK/U1RTS/IC2/CTED4/CN21/RB9                        |

| 16  | SDI2/IC1/CTED3/CN9/RA7                                    | SDI2/IC1/CTED3/CN9/RA7                                    |

| 17  | VCAP                                                      | C2OUT/OC1/CTED1/INT2/CN8/RA6                              |

| 18  | PGED2/SDI1/OC3/CTED11/CN16/RB10                           | PGED2/SDI1/OC3/CTED11/CN16/RB10                           |

| 19  | PGEC2/SCK1/OC2/CTED9/CN15/RB11                            | PGEC2/SCK1/OC2/CTED9/CN15/RB11                            |

| 20  | AN12/HLVDIN/SS2/IC3/CTED2/INT2/CN14/RB12                  | AN12/HLVDIN/SS2/IC3/CTED2/CN14/RB12                       |

| 21  | AN11/SDO1/OCFB/CTPLS/CN13/RB13                            | AN11/SDO1/OCFB/CTPLS/CN13/RB13                            |

| 22  | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 | CVREF/AN10/C3INB/RTCC/C1OUT/OCFA/CTED5/INT1/CN12/<br>RB14 |

| 23  | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15              | AN9/C3INA/T3CK/T2CK/REFO/SS1/CTED6/CN11/RB15              |

| 24  | Vss/AVss                                                  | Vss/AVss                                                  |

| 25  | Vdd/AVdd                                                  | Vdd/AVdd                                                  |

| 26  | MCLR/Vpp/RA5                                              | MCLR/Vpp/RA5                                              |

| 27  | VREF+/CVREF+/AN0/C3INC/CTED1/CN2/RA0                      | VREF+/CVREF+/AN0/C3INC/CN2/RA0                            |

| 28  | CVREF-/VREF-/AN1/CN3/RA1                                  | CVREF-/VREF-/AN1/CN3/RA1                                  |

Legend: Pin numbers in **bold** indicate pin function differences between PIC24FV and PIC24F devices.

**Note 1:** Exposed pad on underside of device is connected to Vss.

2: Alternative multiplexing for SDA1 (ASDA1) and SCL1 (ASCL1) when the I2CSEL Configuration bit is set.

3: PIC24F32KA304 device pins have a maximum voltage of 3.6V and are not 5V tolerant.

### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  | F                                 |               |                        |                |                                  | FV                                |               |                        |                |     |        |             |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|-------------|

|          |                                  | Pin Number                        |               |                        |                |                                  | Pin Number                        |               |                        |                |     |        |             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description |

| RA0      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I/O | ST     | PORTA Pins  |

| RA1      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I/O | ST     |             |

| RA2      | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I/O | ST     |             |

| RA3      | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I/O | ST     |             |

| RA4      | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | I/O | ST     |             |

| RA5      | 1                                | 1                                 | 26            | 18                     | 19             | 1                                | 1                                 | 26            | 18                     | 19             | I/O | ST     |             |

| RA6      | 14                               | 20                                | 17            | 7                      | 7              | _                                | _                                 | —             | _                      | _              | I/O | ST     |             |

| RA7      | _                                | 19                                | 16            | 6                      | 6              | _                                | 19                                | 16            | 6                      | 6              | I/O | ST     |             |

| RA8      | _                                | _                                 |               | 32                     | 35             | _                                | _                                 | —             | 32                     | 35             | I/O | ST     |             |

| RA9      | _                                | _                                 |               | 35                     | 38             | _                                | _                                 | —             | 35                     | 38             | I/O | ST     |             |

| RA10     | _                                | _                                 |               | 12                     | 13             | _                                | _                                 | —             | 12                     | 13             | I/O | ST     |             |

| RA11     | _                                | _                                 |               | 13                     | 14             | _                                | _                                 | —             | 13                     | 14             | I/O | ST     |             |

| RB0      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I/O | ST     | PORTB Pins  |

| RB1      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I/O | ST     |             |

| RB2      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I/O | ST     |             |

| RB3      | _                                | 7                                 | 4             | 24                     | 26             | _                                | 7                                 | 4             | 24                     | 26             | I/O | ST     |             |

| RB4      | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I/O | ST     |             |

| RB5      | _                                | 14                                | 11            | 41                     | 45             | _                                | 14                                | 11            | 41                     | 45             | I/O | ST     |             |

| RB6      | _                                | 15                                | 12            | 42                     | 46             | _                                | 15                                | 12            | 42                     | 46             | I/O | ST     |             |

| RB7      | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | I/O | ST     |             |

| RB8      | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I/O | ST     |             |

| RB9      | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | I/O | ST     |             |

| RB10     | _                                | 21                                | 18            | 8                      | 9              | _                                | 21                                | 18            | 8                      | 9              | I/O | ST     |             |

| RB11     | _                                | 22                                | 19            | 9                      | 10             | _                                | 22                                | 19            | 9                      | 10             | I/O | ST     |             |

| RB12     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I/O | ST     |             |

| RB13     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | I/O | ST     |             |

| RB14     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I/O | ST     |             |

| RB15     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I/O | ST     |             |

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY AND DATA EEPROM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through data space. It also offers a direct method of reading or writing a word of any address within data EEPROM memory. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

| Note: | The TBLRDH and TBLWTH instructions are |

|-------|----------------------------------------|

|       | not used while accessing data EEPROM   |

|       | memory.                                |

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time, and to program one row at a time. It is also possible to program single words.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks, and single row write block (96 bytes) are edge-aligned from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

**Note:** Writing to a location multiple times without erasing it is not recommended.

All of the table write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the Programming Executive (PE), to manage the programming process. Using an SPI data frame format, the Programming Executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

## 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. For more information, refer to **Section 5.5 "Programming Operations"**.

## 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a program or erase operation, the processor stalls (Waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| U-0      | U-0 | U-0         | U-0             | U-0 | U-0 | U-0 | U-0       |

|----------|-----|-------------|-----------------|-----|-----|-----|-----------|

| _        | —   | —           | —               | —   | —   | _   | —         |

| bit 15   |     |             | •               |     | •   |     | bit 8     |

|          |     |             |                 |     |     |     |           |

| U-0      | U-0 | U-0         | U-0             | U-0 | U-0 | U-0 | R/W-0, HS |

| _        | _   | —           | —               | —   | —   | _   | ULPWUIF   |

| bit 7    |     |             |                 |     |     |     | bit 0     |

|          |     |             |                 |     |     |     |           |

| l edenq. |     | HS = Hardwa | re Settable bit |     |     |     |           |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-1 Unimplemented: Read as '0'

bit 0 ULPWUIF: Ultra Low-Power Wake-up Interrupt Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

| REGISTER     | 8-17: IPC0                 | : INTERRUPT                             | PRIORITY (       | CONTROL RI        | EGISTER 0       |                 |         |

|--------------|----------------------------|-----------------------------------------|------------------|-------------------|-----------------|-----------------|---------|

| U-0          | R/W-1                      | R/W-0                                   | R/W-0            | U-0               | R/W-1           | R/W-0           | R/W-0   |

| —            | T1IP2                      | T1IP1                                   | T1IP0            | —                 | OC1IP2          | OC1IP1          | OC1IP0  |

| bit 15       |                            |                                         |                  |                   |                 |                 | bit 8   |

| U-0          | R/W-1                      | R/W-0                                   | R/W-0            | U-0               | R/W-1           | R/W-0           | R/W-0   |

|              | IC1IP2                     | IC1IP1                                  | IC1IP0           |                   | INT0IP2         | INT0IP1         | INTOIPO |

| bit 7        |                            |                                         |                  |                   |                 |                 | bit 0   |

| Logondu      |                            |                                         |                  |                   |                 |                 |         |

| Legend:      | la hit                     | VV - VVritabla I                        | .:+              |                   | nantad hit raa  | d aa 'O'        |         |

| R = Readab   |                            | W = Writable I                          | אנ               | -                 | nented bit, rea |                 |         |

| -n = Value a | t POR                      | '1' = Bit is set                        |                  | '0' = Bit is cle  | ared            | x = Bit is unkr | iown    |

| bit 15       | Unimpleme                  | nted: Read as 'o                        | ,                |                   |                 |                 |         |

| bit 14-12    | T1IP<2:0>: ⊺               | Timer1 Interrupt                        | Priority bits    |                   |                 |                 |         |

|              | 111 <b>= Interru</b>       | upt is Priority 7 (ł                    | nighest priority | interrupt)        |                 |                 |         |

|              | •                          |                                         |                  |                   |                 |                 |         |

|              | •                          |                                         |                  |                   |                 |                 |         |

|              |                            | upt is Priority 1<br>upt source is disa | bled             |                   |                 |                 |         |

| bit 11       |                            | nted: Read as '0                        |                  |                   |                 |                 |         |

| bit 10-8     | -                          | : Output Compa                          |                  | nterrunt Priorit  | v bite          |                 |         |

| DIL 10-0     |                            | upt is Priority 7 (I                    |                  |                   | y bits          |                 |         |

|              | •                          |                                         | lightest phoney  | interrupt)        |                 |                 |         |

|              | •                          |                                         |                  |                   |                 |                 |         |

|              | 001 <b>= Interru</b>       | upt is Priority 1                       |                  |                   |                 |                 |         |

|              |                            | upt source is disa                      |                  |                   |                 |                 |         |

| bit 7        | Unimpleme                  | nted: Read as '0                        | 3                |                   |                 |                 |         |

| bit 6-4      | IC1IP<2:0>:                | Input Capture C                         | hannel 1 Inter   | rupt Priority bit | S               |                 |         |

|              | 111 = Interru              | upt is Priority 7 (ł                    | nighest priority | interrupt)        |                 |                 |         |

|              | •                          |                                         |                  |                   |                 |                 |         |

|              | •<br>001 <b>– Intorr</b> i | upt is Priority 1                       |                  |                   |                 |                 |         |

|              |                            | upt source is disa                      | abled            |                   |                 |                 |         |

| bit 3        |                            | nted: Read as '0                        |                  |                   |                 |                 |         |

| bit 2-0      | -                          | : External Intern                       |                  | its               |                 |                 |         |

| 5112 0       |                            | upt is Priority 7 (I                    |                  |                   |                 |                 |         |

|              | •                          |                                         |                  |                   |                 |                 |         |

|              |                            |                                         |                  |                   |                 |                 |         |

|              | •                          |                                         |                  |                   |                 |                 |         |

|              |                            | upt is Priority 1<br>upt source is disa |                  |                   |                 |                 |         |

### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, each port pin can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The maximum open-drain voltage allowed is the same as the maximum  $V_{\text{IH}}$  specification.

## 11.2 Configuring Analog Port Pins

The use of the ANS and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRISx bit set (input). If the TRISx bit is cleared (output), the digital output level (VOH or VOL) will be converted.

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 ANALOG SELECTION REGISTERS

I/O pins with shared analog functionality, such as A/D inputs and comparator inputs, must have their digital inputs shut off when analog functionality is used. Note that analog functionality includes an analog voltage being applied to the pin externally.

To allow for analog control, the ANSx registers are provided. There is one ANS register for each port (ANSA, ANSB and ANSC). Within each ANSx register, there is a bit for each pin that shares analog functionality with the digital I/O functionality.

If a particular pin does not have an analog function, that bit is unimplemented. See Register 11-1 to Register 11-3 for implementation.

### REGISTER 11-1: ANSA: ANALOG SELECTION (PORTA)

| U-0           | U-0                                                                  | U-0              | U-0 | U-0                                     | U-0   | U-0   | U-0   |

|---------------|----------------------------------------------------------------------|------------------|-----|-----------------------------------------|-------|-------|-------|

| —             | —                                                                    | —                | —   | —                                       | —     | —     | —     |

| bit 15        |                                                                      |                  |     |                                         |       |       | bit 8 |

|               |                                                                      |                  |     |                                         |       |       |       |

| U-0           | U-0                                                                  | U-0              | U-0 | R/W-1                                   | R/W-1 | R/W-1 | R/W-1 |

|               | —                                                                    | -                | —   | ANSA3                                   | ANSA2 | ANSA1 | ANSA0 |

| bit 7         |                                                                      |                  |     |                                         |       |       | bit 0 |

|               |                                                                      |                  |     |                                         |       |       |       |

| Legend:       |                                                                      |                  |     |                                         |       |       |       |

| R = Readable  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |     |                                         |       |       |       |

| -n = Value at | POR                                                                  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |

bit 15-4 Unimplemented: Read as '0'

bit 3-0 ANSA<3:0>: Analog Select Control bits

1 = Digital input buffer is not active (use for analog input)

0 = Digital input buffer is active

## EQUATION 16-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED<sup>(1)</sup>

FCY

FSCK = Primary Prescaler \* Secondary Prescaler

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

## TABLE 16-1: SAMPLE SCKx FREQUENCIES<sup>(1,2)</sup>

| Fcy = 16 MHz               | Secondary Prescaler Settings |         |      |      |      |      |  |

|----------------------------|------------------------------|---------|------|------|------|------|--|

|                            |                              | 1:1     | 2:1  | 4:1  | 6:1  | 8:1  |  |

| Primary Prescaler Settings | 1:1                          | Invalid | 8000 | 4000 | 2667 | 2000 |  |

|                            | 4:1                          | 4000    | 2000 | 1000 | 667  | 500  |  |

|                            | 16:1                         | 1000    | 500  | 250  | 167  | 125  |  |

|                            | 64:1                         | 250     | 125  | 63   | 42   | 31   |  |

| Fcy <b>= 5 MHz</b>         |                              |         |      |      |      |      |  |

| Primary Prescaler Settings | 1:1                          | 5000    | 2500 | 1250 | 833  | 625  |  |

|                            | 4:1                          | 1250    | 625  | 313  | 208  | 156  |  |

|                            | 16:1                         | 313     | 156  | 78   | 52   | 39   |  |

|                            | 64:1                         | 78      | 39   | 20   | 13   | 10   |  |

**Note 1:** Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

2: SCKx frequencies are indicated in kHz.

#### REGISTER 26-10: DEVREV: DEVICE REVISION REGISTER

| U-0                                | U-0 | U-0 | U-0 | U-0                                     | U-0             | U-0      | U-0    |

|------------------------------------|-----|-----|-----|-----------------------------------------|-----------------|----------|--------|

| —                                  | —   | —   | —   | —                                       | —               | —        | —      |

| bit 23                             |     |     |     |                                         |                 |          | bit 16 |

|                                    |     |     |     |                                         |                 |          |        |

| U-0                                | U-0 | U-0 | U-0 | U-0                                     | U-0             | U-0      | U-0    |

| —                                  | —   | —   | —   | —                                       | —               | —        | —      |

| bit 15                             | •   | -   |     |                                         |                 | •        | bit 8  |

|                                    |     |     |     |                                         |                 |          |        |

| U-0                                | U-0 | U-0 | U-0 | R                                       | R               | R        | R      |

| —                                  |     | —   | —   | REV3                                    | REV2            | REV1     | REV0   |

| bit 7                              | •   | -   |     |                                         |                 | •        | bit 0  |

|                                    |     |     |     |                                         |                 |          |        |

| Legend:                            |     |     |     |                                         |                 |          |        |

| R = Readable bit W = Writable bit  |     |     |     | U = Unimplem                            | ented bit, read | l as '0' |        |

| -n = Value at POR (1' = Bit is set |     |     |     | '0' = Bit is cleared x = Bit is unknown |                 |          | nown   |

|                                    |     |     |     |                                         |                 |          |        |

bit 23-4 Unimplemented: Read as '0'

bit 3-0 **REV<3:0>:** Minor Revision Identifier bits

### TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                          |

|-----------------|--------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                      |

| (text)          | Means "content of text"                                                              |

| [text]          | Means "the location addressed by text"                                               |

| { }             | Optional field or operation                                                          |

| <n:m></n:m>     | Register bit field                                                                   |

| .b              | Byte mode selection                                                                  |

| .d              | Double-Word mode selection                                                           |

| .S              | Shadow register select                                                               |

| .W              | Word mode selection (default)                                                        |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |

| f               | File register address ∈ {0000h1FFFh}                                                 |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4            | 4-bit unsigned literal $\in \{015\}$                                                 |

| lit5            | 5-bit unsigned literal $\in \{031\}$                                                 |

| lit8            | 8-bit unsigned literal $\in \{0255\}$                                                |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be '0'                                |

| None            | Field does not require an entry, may be blank                                        |

| PC              | Program Counter                                                                      |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                       |

| Wb              | Base W register ∈ {W0W15}                                                            |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor working register pair (direct addressing)                          |

| Wn              | One of 16 working registers $\in$ {W0W15}                                            |

| Wnd             | One of 16 destination working registers $\in$ {W0W15}                                |

| Wns             | One of 16 source working registers $\in$ {W0W15}                                     |

| WREG            | W0 (working register used in File register instructions)                             |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                         |

| Wso             | Source W register ∈ { Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }         |

| Assembly<br>Mnemonic | Assembly Syntax |             | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-----------------|-------------|------------------------------|---------------|----------------|--------------------------|

| TBLRDL               | TBLRDL          | Ws,Wd       | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| TBLWTH               | TBLWTH          | Ws,Wd       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| TBLWTL               | TBLWTL          | Ws,Wd       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| ULNK                 | ULNK            |             | Unlink Frame Pointer         | 1             | 1              | None                     |

| XOR                  | XOR             | f           | f = f .XOR. WREG             | 1             | 1              | N, Z                     |

|                      | XOR             | f,WREG      | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |

|                      | XOR             | #lit10,Wn   | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |

|                      | XOR             | Wb,Ws,Wd    | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |

|                      | XOR             | Wb,#lit5,Wd | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |

| ZE                   | ZE              | Ws,Wnd      | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

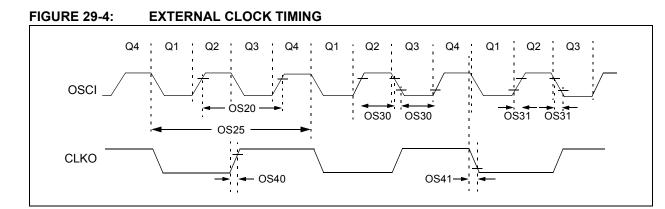

## 29.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC24FV32KA304 family AC characteristics and timing parameters.

#### TABLE 29-17: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions:     | 1.8V to 3.6V PIC24F32KA3XX                    |

|--------------------|------------------------------------|-----------------------------------------------|

|                    | _                                  | 2.0V to 5.5V PIC24FV32KA3XX                   |

| AC CHARACTERISTICS | Operating temperature:             | -40°C $\leq$ TA $\leq$ +85°C for Industrial   |

|                    |                                    | -40°C $\leq$ TA $\leq$ +125°C for Extended    |

|                    | Operating voltage VDD range as des | scribed in Section 29.1 "DC Characteristics". |

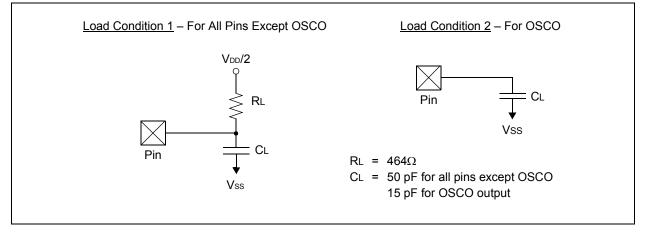

#### FIGURE 29-3: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 29-18: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                             |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|------------------------------------------------------------------------|

| DO50         | Cosc2  | OSCO/CLKO Pin         | _   | —                  | 15  | pF    | In XT and HS modes when the<br>external clock is used to drive<br>OSCI |

| DO56         | Сю     | All I/O Pins and OSCO | —   | —                  | 50  | pF    | EC mode                                                                |

| DO58         | Св     | SCLx, SDAx            |     | —                  | 400 | pF    | In I <sup>2</sup> C™ mode                                              |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| AC CHARACTERISTICS Standard Operating Conditions: 1.8V to 3.6V PIC24F32KA3<br>2.0V to 5.5V PIC24FV32KA |               |                                                                         |                     |                                                                                                                                                                                    |                    |                          |                                   |

|--------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------|-----------------------------------|

| AC CH                                                                                                  | ARACI         | ERISTICS                                                                | Operating terr      | $\begin{array}{ll} \mbox{temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                    |                          |                                   |

| Param<br>No.                                                                                           | Sym           | Characteristic                                                          | Min                 | Typ <sup>(1)</sup> Max Units Conditions                                                                                                                                            |                    |                          |                                   |

| OS10                                                                                                   | Fosc          | External CLKI Frequency<br>(External clocks allowed<br>only in EC mode) | DC<br>4             |                                                                                                                                                                                    | 32<br>8            | MHz<br>MHz               | EC<br>ECPLL                       |

| OS15                                                                                                   |               | Oscillator Frequency                                                    | 0.2<br>4<br>4<br>31 | <br> <br>                                                                                                                                                                          | 4<br>25<br>8<br>33 | MHz<br>MHz<br>MHz<br>kHz | XT<br>HS<br>XTPLL<br>SOSC         |

| OS20                                                                                                   | Tosc          | Tosc = 1/Fosc                                                           | —                   | —                                                                                                                                                                                  | _                  | _                        | See Parameter OS10 for Fosc value |

| OS25                                                                                                   | TCY           | Instruction Cycle Time <sup>(2)</sup>                                   | 62.5                | —                                                                                                                                                                                  | DC                 | ns                       |                                   |

| OS30                                                                                                   | TosL,<br>TosH | External Clock in (OSCI)<br>High or Low Time                            | 0.45 x Tosc         | —                                                                                                                                                                                  | _                  | ns                       | EC                                |

| OS31                                                                                                   | TosR,<br>TosF | External Clock in (OSCI)<br>Rise or Fall Time                           | _                   | —                                                                                                                                                                                  | 20                 | ns                       | EC                                |

| OS40                                                                                                   | TckR          | CLKO Rise Time <sup>(3)</sup>                                           | —                   | 6                                                                                                                                                                                  | 10                 | ns                       |                                   |

| OS41                                                                                                   | TckF          | CLKO Fall Time <sup>(3)</sup>                                           | _                   | 6                                                                                                                                                                                  | 10                 | ns                       |                                   |

#### TABLE 29-19: EXTERNAL CLOCK TIMING REQUIREMENTS

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The instruction cycle period (TcY) equals two times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type, under standard operating conditions, with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSCI/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

**3:** Measurements are taken in EC mode. The CLKO signal is measured on the OSCO pin. CLKO is low for the Q1-Q2 period (1/2 TCY) and high for the Q3-Q4 period (1/2 TCY).

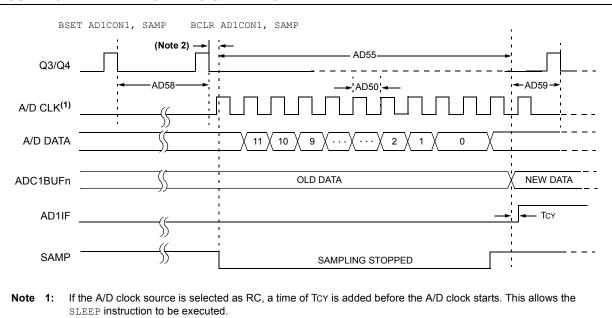

#### FIGURE 29-22: A/D CONVERSION TIMING

2: This is a minimal RC delay (typically 100 ns) which also disconnects the holding capacitor from the analog input.

| AC CHARACTERISTICS |                       |                                                      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |          |          |            |                                       |  |

|--------------------|-----------------------|------------------------------------------------------|-------------------------------------------------------|----------|----------|------------|---------------------------------------|--|

| Param<br>No.       | Symbol Characteristic |                                                      | Min.                                                  | Тур      | Max.     | Units      | Conditions                            |  |

|                    |                       | (                                                    | Clock Pa                                              | rameter  | s        |            |                                       |  |

| AD50               | Tad                   | A/D Clock Period                                     | 600                                                   | —        | —        | ns         | Tcy = 75 ns, AD1CON3 in default state |  |

| AD51               | TRC                   | A/D Internal RC Oscillator<br>Period                 | _                                                     | 1.67     | —        | μs         |                                       |  |

|                    |                       |                                                      | Convers                                               | ion Rate | )        |            |                                       |  |

| AD55               | TCONV                 | Conversion Time                                      | _                                                     | 12<br>14 | _        | Tad<br>Tad | 10-bit results<br>12-bit results      |  |

| AD56               | FCNV                  | Throughput Rate                                      | _                                                     |          | 100      | ksps       |                                       |  |

| AD57               | TSAMP                 | Sample Time                                          | _                                                     | 1        | _        | Tad        |                                       |  |

| AD58               | TACQ                  | Acquisition Time                                     | 750                                                   |          | _        | ns         | (Note 2)                              |  |

| AD59               | Tswc                  | Switching Time from Convert to Sample                | _                                                     | —        | (Note 3) |            |                                       |  |

| AD60               | TDIS                  | Discharge Time                                       | 12                                                    |          | —        | Tad        |                                       |  |

|                    |                       | (                                                    | Clock Pa                                              | rameter  | s        |            |                                       |  |

| AD61               | TPSS                  | Sample Start Delay from<br>Setting Sample bit (SAMP) | 2                                                     | _        | 3        | Tad        |                                       |  |

### TABLE 29-41: A/D CONVERSION TIMING REQUIREMENTS<sup>(1)</sup>

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

2: The time for the holding capacitor to acquire the "New" input voltage when the voltage changes full scale after the conversion (VDD to Vss or Vss to VDD).

**3:** On the following cycle of the device clock.

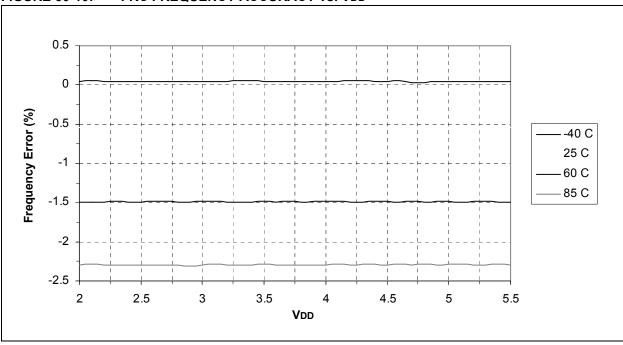

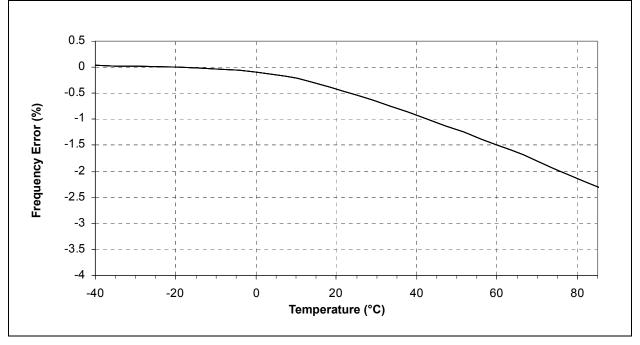

FIGURE 30-10: FRC FREQUENCY ACCURACY vs. VDD

FIGURE 30-49: TYPICAL Vol vs. Iol (GENERAL I/O,  $2.0V \le VDD \le 5.5V$ )

0 Γοι (MA)

## FIGURE 30-50: TYPICAL VOH vs. IOH (GENERAL I/O, AS A FUNCTION OF TEMPERATURE, $2.0V \le V \text{DD} \le 5.5 \text{V})$

| (л) нол | - |                   | - | _ |  |

|---------|---|-------------------|---|---|--|

|         |   | Іон ( <b>mA</b> ) |   |   |  |

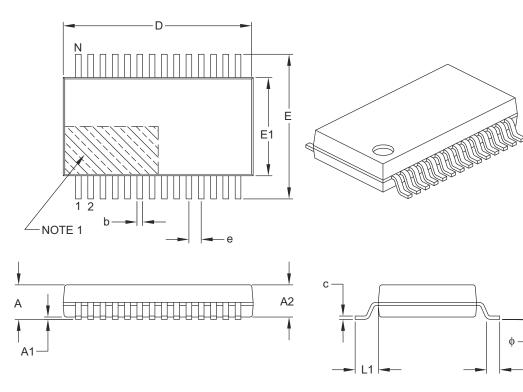

## 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|----------|----------|-------------|--|--|--|

| Dimensio                 | Dimension Limits |          | NOM      | MAX         |  |  |  |

| Number of Pins           | Ν                |          | 28       |             |  |  |  |

| Pitch                    | е                |          | 0.65 BSC |             |  |  |  |

| Overall Height           | А                | -        | -        | 2.00        |  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75     | 1.85        |  |  |  |

| Standoff                 | A1               | 0.05     | -        | _           |  |  |  |

| Overall Width            | Е                | 7.40     | 7.80     | 8.20        |  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30     | 5.60        |  |  |  |

| Overall Length           | D                | 9.90     | 10.20    | 10.50       |  |  |  |

| Foot Length              | L                | 0.55     | 0.75     | 0.95        |  |  |  |

| Footprint                | L1               | 1.25 REF |          |             |  |  |  |

| Lead Thickness           | С                | 0.09     | -        | 0.25        |  |  |  |

| Foot Angle               | ф                | 0°       | 4°       | 8°          |  |  |  |

| Lead Width               | b                | 0.22     | -        | 0.38        |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

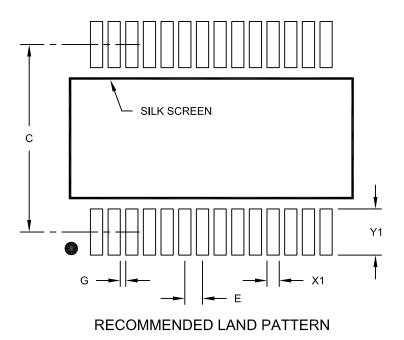

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |      | S    |  |

|--------------------------|------------------|----------|------|------|--|

| Dimension                | Dimension Limits |          | NOM  | MAX  |  |

| Contact Pitch            | E                | 0.65 BSC |      |      |  |

| Contact Pad Spacing      | С                |          | 7.20 |      |  |

| Contact Pad Width (X28)  | X1               |          |      | 0.45 |  |

| Contact Pad Length (X28) | Y1               |          |      | 1.75 |  |

| Distance Between Pads    | G                | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

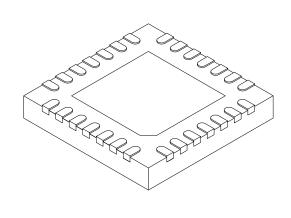

### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | М        | MILLIMETERS |      |  |

|-------------------------|--------|----------|-------------|------|--|

| Dimension               | Limits | MIN      | NOM         | MAX  |  |

| Number of Pins          | N      |          | 28          |      |  |

| Pitch                   | е      |          | 0.65 BSC    |      |  |

| Overall Height          | A      | 0.80     | 0.90        | 1.00 |  |

| Standoff                | A1     | 0.00     | 0.02        | 0.05 |  |

| Terminal Thickness      | A3     | 0.20 REF |             |      |  |

| Overall Width           | E      | 6.00 BSC |             |      |  |

| Exposed Pad Width       | E2     | 3.65     | 3.70        | 4.20 |  |

| Overall Length          | D      | 6.00 BSC |             |      |  |

| Exposed Pad Length      | D2     | 3.65     | 3.70        | 4.20 |  |

| Terminal Width          | b      | 0.23     | 0.30        | 0.35 |  |

| Terminal Length         | L      | 0.50     | 0.55        | 0.70 |  |

| Terminal-to-Exposed Pad | K      | 0.20     | -           | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

NOTES: