Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                    |

| Number of I/O              | 38                                                                             |

| Program Memory Size        | 32KB (11K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 512 x 8                                                                        |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                      |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fv32ka304t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  | +1 VJ2104                         | F             |                        |                |                                  |                                   | FV            | -                      |                |     |        |             |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|-------------|

|          |                                  |                                   | Pin Number    |                        |                |                                  |                                   | Pin Number    |                        |                |     |        |             |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description |

| RA0      | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | I/O | ST     | PORTA Pins  |

| RA1      | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | I/O | ST     |             |

| RA2      | 7                                | 9                                 | 6             | 30                     | 33             | 7                                | 9                                 | 6             | 30                     | 33             | I/O | ST     |             |

| RA3      | 8                                | 10                                | 7             | 31                     | 34             | 8                                | 10                                | 7             | 31                     | 34             | I/O | ST     |             |

| RA4      | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | I/O | ST     |             |

| RA5      | 1                                | 1                                 | 26            | 18                     | 19             | 1                                | 1                                 | 26            | 18                     | 19             | I/O | ST     |             |

| RA6      | 14                               | 20                                | 17            | 7                      | 7              | _                                | _                                 | —             | _                      | _              | I/O | ST     |             |

| RA7      | _                                | 19                                | 16            | 6                      | 6              | _                                | 19                                | 16            | 6                      | 6              | I/O | ST     |             |

| RA8      | _                                | _                                 |               | 32                     | 35             | _                                | _                                 | —             | 32                     | 35             | I/O | ST     |             |

| RA9      | _                                | _                                 |               | 35                     | 38             | _                                | _                                 | —             | 35                     | 38             | I/O | ST     |             |

| RA10     | _                                | _                                 |               | 12                     | 13             | _                                | _                                 | —             | 12                     | 13             | I/O | ST     |             |

| RA11     | _                                | _                                 |               | 13                     | 14             | _                                | _                                 | —             | 13                     | 14             | I/O | ST     |             |

| RB0      | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I/O | ST     | PORTB Pins  |

| RB1      | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I/O | ST     |             |

| RB2      | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I/O | ST     |             |

| RB3      | _                                | 7                                 | 4             | 24                     | 26             | _                                | 7                                 | 4             | 24                     | 26             | I/O | ST     |             |

| RB4      | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | I/O | ST     |             |

| RB5      | _                                | 14                                | 11            | 41                     | 45             | _                                | 14                                | 11            | 41                     | 45             | I/O | ST     |             |

| RB6      | _                                | 15                                | 12            | 42                     | 46             | _                                | 15                                | 12            | 42                     | 46             | I/O | ST     |             |

| RB7      | 11                               | 16                                | 13            | 43                     | 47             | 11                               | 16                                | 13            | 43                     | 47             | I/O | ST     |             |

| RB8      | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | I/O | ST     |             |

| RB9      | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | I/O | ST     |             |

| RB10     | _                                | 21                                | 18            | 8                      | 9              | _                                | 21                                | 18            | 8                      | 9              | I/O | ST     |             |

| RB11     | _                                | 22                                | 19            | 9                      | 10             | _                                | 22                                | 19            | 9                      | 10             | I/O | ST     |             |

| RB12     | 15                               | 23                                | 20            | 10                     | 11             | 15                               | 23                                | 20            | 10                     | 11             | I/O | ST     |             |

| RB13     | 16                               | 24                                | 21            | 11                     | 12             | 16                               | 24                                | 21            | 11                     | 12             | I/O | ST     |             |

| RB14     | 17                               | 25                                | 22            | 14                     | 15             | 17                               | 25                                | 22            | 14                     | 15             | I/O | ST     |             |

| RB15     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I/O | ST     |             |

### TABLE 1-3: PIC24FV32KA304 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

|          |                                  |                                   | F             |                        |                |                                  |                                   | FV            |                        |                |     |        |                                 |  |

|----------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|----------------------------------|-----------------------------------|---------------|------------------------|----------------|-----|--------|---------------------------------|--|

|          |                                  |                                   | Pin Number    | •                      |                |                                  |                                   | Pin Number    | •                      |                |     |        |                                 |  |

| Function | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | 20-Pin<br>PDIP/<br>SSOP/<br>SOIC | 28-Pin<br>SPDIP/<br>SSOP/<br>SOIC | 28-Pin<br>QFN | 44-Pin<br>QFN/<br>TQFP | 48-Pin<br>UQFN | I/O | Buffer | Description                     |  |

| T1CK     | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | Т   | ST     | Timer1 Clock                    |  |

| T2CK     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | Ι   | ST     | Timer2 Clock                    |  |

| ТЗСК     | 18                               | 26                                | 23            | 15                     | 16             | 18                               | 26                                | 23            | 15                     | 16             | I   | ST     | Timer3 Clock                    |  |

| T4CK     | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | I   | ST     | Timer4 Clock                    |  |

| T5CK     | 6                                | 6                                 | 3             | 23                     | 25             | 6                                | 6                                 | 3             | 23                     | 25             | Ι   | ST     | Timer5 Clock                    |  |

| U1CTS    | 12                               | 17                                | 14            | 44                     | 48             | 12                               | 17                                | 14            | 44                     | 48             | Ι   | ST     | UART1 Clear-to-Send Input       |  |

| U1RTS    | 13                               | 18                                | 15            | 1                      | 1              | 13                               | 18                                | 15            | 1                      | 1              | 0   | _      | UART1 Request-to-Send Output    |  |

| U1RX     | 6                                | 6                                 | 3             | 2                      | 2              | 6                                | 6                                 | 3             | 2                      | 2              | I   | ST     | UART1 Receive                   |  |

| U1TX     | 11                               | 16                                | 13            | 3                      | 3              | 11                               | 16                                | 13            | 3                      | 3              | 0   | —      | UART1 Transmit                  |  |

| U2CTS    | 10                               | 12                                | 9             | 34                     | 37             | 10                               | 12                                | 9             | 34                     | 37             | Ι   | ST     | UART2 Clear-to-Send Input       |  |

| U2RTS    | 9                                | 11                                | 8             | 33                     | 36             | 9                                | 11                                | 8             | 33                     | 36             | 0   | _      | UART2 Request-to-Send Output    |  |

| U2RX     | 5                                | 5                                 | 2             | 22                     | 24             | 5                                | 5                                 | 2             | 22                     | 24             | I   | ST     | UART2 Receive                   |  |

| U2TX     | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | 0   | _      | UART2 Transmit                  |  |

| ULPWU    | 4                                | 4                                 | 1             | 21                     | 23             | 4                                | 4                                 | 1             | 21                     | 23             | I   | ANA    | Ultra Low-Power Wake-up Input   |  |

| VCAP     | _                                | —                                 | _             | —                      | _              | 14                               | 20                                | 17            | 7                      | 7              | Р   | —      | Core Power                      |  |

| Vdd      | 20                               | 28,13                             | 25,10         | 17,28,40               | 18,30,43       | 20                               | 28,13                             | 25,10         | 17,28,40               | 18,30,43       | Р   | —      | Device Digital Supply Voltage   |  |

| VREF+    | 2                                | 2                                 | 27            | 19                     | 21             | 2                                | 2                                 | 27            | 19                     | 21             | Ι   | ANA    | A/D Reference Voltage Input (+) |  |

| VREF-    | 3                                | 3                                 | 28            | 20                     | 22             | 3                                | 3                                 | 28            | 20                     | 22             | Ι   | ANA    | A/D Reference Voltage Input (-) |  |

| Vss      | 19                               | 27,8                              | 24,5          | 16,29,39               | 17,31,42       | 19                               | 27,8                              | 24,5          | 16,29,39               | 17,31,42       | Р   | _      | Device Digital Ground Return    |  |

### 5.5.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time by erasing the programmable row. The general process is as follows:

- 1. Read a row of program memory (32 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase a row (see Example 5-1):

- a) Set the NVMOPx bits (NVMCON<5:0>) to '011000' to configure for row erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 32 instructions from data RAM into the program memory buffers (see Example 5-1).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '011000' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-5.

| MOV #0x4058, W0                  | ;                                       |

|----------------------------------|-----------------------------------------|

| MOV W0, NVMCON                   | ; Initialize NVMCON                     |

| Init pointer to row to be ERASED |                                         |

| MOV #tblpage(PROG_ADDR), W0      | ;                                       |

| MOV W0, TBLPAG                   | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W     | 0 ; Initialize in-page EA[15:0] pointer |

| TBLWTL W0, [W0]                  | ; Set base address of erase block       |

| DISI #5                          | ; Block all interrupts                  |

|                                  | for next 5 instructions                 |

| MOV #0x55, W0                    |                                         |

| MOV W0, NVMKEY                   | ; Write the 55 key                      |

| MOV #0xAA, W1                    | ;                                       |

| MOV W1, NVMKEY                   | ; Write the AA key                      |

| BSET NVMCON, #WR                 | ; Start the erase sequence              |

| NOP                              | ; Insert two NOPs after the erase       |

| NOP                              | ; command is asserted                   |

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY ROW – ASSEMBLY LANGUAGE CODE

### EXAMPLE 5-4: LOADING THE WRITE BUFFERS – 'C' LANGUAGE CODE

```

// C example using MPLAB C30

#define NUM INSTRUCTION PER ROW 64

int __attribute__ ((space(auto_psv))) progAddr = 0x1234; // Global variable located in Pgm Memory

unsigned int offset;

unsigned int i;

unsigned int progData[2*NUM INSTRUCTION PER ROW]; // Buffer of data to write

//Set up NVMCON for row programming

NVMCON = 0 \times 4001;

// Initialize NVMCON

//Set up pointer to the first memory location to be written

TBLPAG = __builtin_tblpage(&progAddr); // Initialize PM Page Boundary SFR

offset = __builtin_tbloffset(&progAddr); // Initialize lower word of address

offset = __builtin_tbloffset(&progAddr);

// Initialize lower word of address

//Perform TBLWT instructions to write necessary number of latches

for(i=0; i < 2*NUM INSTRUCTION PER ROW; i++)</pre>

{

__builtin_tblwtl(offset, progData[i++]);

// Write to address low word

__builtin_tblwth(offset, progData[i]);

// Write to upper byte

offset = offset + 2;

// Increment address

}

```

### EXAMPLE 5-5: INITIATING A PROGRAMMING SEQUENCE – ASSEMBLY LANGUAGE CODE

| DISI | #5          | ; 1 | Block all interrupts                  |

|------|-------------|-----|---------------------------------------|

|      |             | :   | for next 5 instructions               |

| MOV  | #0x55, W0   |     |                                       |

| MOV  | W0, NVMKEY  | ; 1 | Write the 55 key                      |

| MOV  | #0xAA, W1   | ;   |                                       |

| MOV  | W1, NVMKEY  | ; 1 | Write the AA key                      |

| BSET | NVMCON, #WR | ; ; | Start the erase sequence              |

| NOP  |             | ; : | 2 NOPs required after setting WR      |

| NOP  |             | ;   |                                       |

| BTSC | NVMCON, #15 | ; 1 | Wait for the sequence to be completed |

| BRA  | \$-2        | ;   |                                       |

|      |             |     |                                       |

### EXAMPLE 5-6: INITIATING A PROGRAMMING SEQUENCE – 'C' LANGUAGE CODE

| <pre>// C example using MPLAB C30</pre> |                                                 |

|-----------------------------------------|-------------------------------------------------|

| asm("DISI #5");                         | // Block all interrupts for next 5 instructions |

| builtin_write_NVM();                    | // Perform unlock sequence and set WR           |

## REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | <ol> <li>Interrupt request has occurred</li> </ol>        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | <ol> <li>Interrupt request has occurred</li> </ol>        |

|       | 0 = Interrupt request has not occurred                    |

| bit 0 | INT0IF: External Interrupt 0 Flag Status bit              |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

### REGISTER 8-11: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

## bit 0 INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

### REGISTER 8-19: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1                              | R/W-0                                | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |

|------------------|------------------------------------|--------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|

| _                | U1RXIP2                            | U1RXIP1                              | U1RXIP0          | _                | SPI1IP2          | SPI1IP1         | SPI1IP0 |  |  |

| bit 15           |                                    |                                      |                  |                  |                  |                 | bit 8   |  |  |

| U-0              | R/W-1                              | R/W-0                                | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |

| _                | SPF1IP2                            | SPF1IP1                              | SPF1IP0          |                  | T3IP2            | T3IP1           | T3IP0   |  |  |

| bit 7            |                                    | 1                                    |                  |                  |                  | 1               | bit (   |  |  |

| Legend:          |                                    |                                      |                  |                  |                  |                 |         |  |  |

| R = Readat       | ole bit                            | W = Writable                         | bit              | U = Unimpler     | nented bit, read | l as '0'        |         |  |  |

| -n = Value a     | at POR                             | '1' = Bit is set                     |                  | '0' = Bit is cle |                  | x = Bit is unkn | iown    |  |  |

|                  |                                    |                                      |                  |                  |                  |                 |         |  |  |

| bit 15           | Unimplemen                         | ted: Read as '                       | )'               |                  |                  |                 |         |  |  |

| bit 14-12        | -                                  | : UART1 Rece                         |                  | riority bits     |                  |                 |         |  |  |

|                  |                                    | pt is Priority 7 (                   | =                | -                |                  |                 |         |  |  |

|                  | •                                  |                                      | 0 . ,            | • /              |                  |                 |         |  |  |

|                  | 001 = Interrupt is Priority 1      |                                      |                  |                  |                  |                 |         |  |  |

|                  |                                    |                                      |                  |                  |                  |                 |         |  |  |

|                  | 000 = Interrupt source is disabled |                                      |                  |                  |                  |                 |         |  |  |

| bit 11           | -                                  | Unimplemented: Read as '0'           |                  |                  |                  |                 |         |  |  |

| bit 10-8         |                                    | SPI1 Event Int                       | , ,              |                  |                  |                 |         |  |  |

|                  | 111 = Interru                      | pt is Priority 7 (                   | highest priority | interrupt)       |                  |                 |         |  |  |

|                  | •                                  |                                      |                  |                  |                  |                 |         |  |  |

|                  | •<br>001 = Interru                 | pt is Priority 1                     |                  |                  |                  |                 |         |  |  |

|                  | 000 = Interru                      | pt source is dis                     | abled            |                  |                  |                 |         |  |  |

| bit 7            | Unimplemen                         | ted: Read as '                       | )'               |                  |                  |                 |         |  |  |

| bit 6-4          | SPF1IP<2:0>                        | : SPI1 Fault Inf                     | errupt Priority  | oits             |                  |                 |         |  |  |

|                  | 111 = Interru                      | pt is Priority 7 (                   | highest priority | interrupt)       |                  |                 |         |  |  |

|                  | •                                  |                                      |                  |                  |                  |                 |         |  |  |

|                  | •                                  |                                      |                  |                  |                  |                 |         |  |  |

|                  | 001 = Interru                      | pt is Priority 1<br>pt source is dis | abled            |                  |                  |                 |         |  |  |

|                  | -                                  | ted: Read as '                       |                  |                  |                  |                 |         |  |  |

| hit 3            |                                    | imer3 Interrupt                      |                  |                  |                  |                 |         |  |  |

|                  |                                    |                                      | •                | interrunt)       |                  |                 |         |  |  |

|                  | 111 = Interru                      | nt is Priority 7 (                   |                  |                  |                  |                 |         |  |  |

|                  | 111 = Interruj<br>•                | pt is Priority 7 (                   | nignest priority | interrupt)       |                  |                 |         |  |  |

| bit 3<br>bit 2-0 | 111 = Interruj<br>•                | pt is Priority 7 (                   | nignest priority | interrupt)       |                  |                 |         |  |  |

|                  | •<br>•<br>001 = Interru            |                                      |                  | interrupt)       |                  |                 |         |  |  |

### REGISTER 8-21: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0          | R/W-1             | R/W-0                                | R/W-0              | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |

|--------------|-------------------|--------------------------------------|--------------------|------------------|------------------|-----------------|---------|--|--|

| _            | CNIP2             | CNIP1                                | CNIP0              | _                | CMIP2            | CMIP1           | CMIP0   |  |  |

| bit 15       |                   |                                      |                    |                  |                  |                 | bit 8   |  |  |

| U-0          | R/W-1             | R/W-0                                | R/W-0              | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |

| —            | MI2C1P2           | MI2C1P1                              | MI2C1P0            | —                | SI2C1P2          | SI2C1P1         | SI2C1P0 |  |  |

| bit 7        |                   |                                      |                    |                  |                  |                 | bit C   |  |  |

| Legend:      |                   |                                      |                    |                  |                  |                 |         |  |  |

| R = Readat   | ole bit           | W = Writable                         | bit                | U = Unimple      | mented bit, read | d as '0'        |         |  |  |

| -n = Value a | at POR            | '1' = Bit is set                     |                    | '0' = Bit is cle | eared            | x = Bit is unkr | nown    |  |  |

| -:. 4 C      |                   | tad. Daad aa (                       | <u>.</u>           |                  |                  |                 |         |  |  |

| bit 15       | -                 | ited: Read as '                      |                    | rupt Drigrity b  | ita              |                 |         |  |  |

| bit 14-12    |                   |                                      | lotification Inter | -                | 115              |                 |         |  |  |

|              | ⊥⊥⊥ = mterru<br>• | puis Phonty 7 (                      | highest priority   | mterrupt)        |                  |                 |         |  |  |

|              | •                 |                                      |                    |                  |                  |                 |         |  |  |

|              | 001 = Interru     | pt is Priority 1                     |                    |                  |                  |                 |         |  |  |

|              | 000 = Interru     | pt source is dis                     | abled              |                  |                  |                 |         |  |  |

| bit 11       | Unimplemen        | Unimplemented: Read as '0'           |                    |                  |                  |                 |         |  |  |

| bit 10-8     | CMIP<2:0>:        | Comparator Int                       | errupt Priority b  | its              |                  |                 |         |  |  |

|              | 111 = Interru     | pt is Priority 7 (                   | highest priority   | interrupt)       |                  |                 |         |  |  |

|              | •                 |                                      |                    |                  |                  |                 |         |  |  |

|              | •                 | untin Duinuity (                     |                    |                  |                  |                 |         |  |  |

|              |                   | pt is Priority 1<br>pt source is dis | abled              |                  |                  |                 |         |  |  |

| bit 7        |                   | ited: Read as '                      |                    |                  |                  |                 |         |  |  |

| bit 6-4      | -                 |                                      | Event Interrupt    | Priority bits    |                  |                 |         |  |  |

|              |                   |                                      | highest priority   | •                |                  |                 |         |  |  |

|              | •                 |                                      | ingricor priority  | interrupt)       |                  |                 |         |  |  |

|              | •                 |                                      |                    |                  |                  |                 |         |  |  |

|              |                   | pt is Priority 1<br>pt source is dis | abled              |                  |                  |                 |         |  |  |

| bit 3        | Unimplemen        | ted: Read as '                       | 0'                 |                  |                  |                 |         |  |  |

| bit 2-0      | -                 |                                      | vent Interrupt F   | riority bits     |                  |                 |         |  |  |

|              |                   |                                      | highest priority   | -                |                  |                 |         |  |  |

|              | •                 |                                      | - · ·              | • •              |                  |                 |         |  |  |

|              | •                 |                                      |                    |                  |                  |                 |         |  |  |

|              | •                 |                                      |                    |                  |                  |                 |         |  |  |

|              |                   | pt is Priority 1<br>pt source is dis |                    |                  |                  |                 |         |  |  |

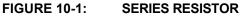

### 10.3 Ultra Low-Power Wake-up

The Ultra Low-Power Wake-up (ULPWU) on pin, RB0, allows a slow falling voltage to generate an interrupt without excess current consumption.

To use this feature:

- 1. Charge the capacitor on RB0 by configuring the RB0 pin to an output and setting it to '1'.

- 2. Stop charging the capacitor by configuring RB0 as an input.

- 3. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the ULPWCON register.

- 4. Configure Sleep mode.

- 5. Enter Sleep mode.

When the voltage on RB0 drops below VIL, the device wakes up and executes the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode.

The time-out is dependent on the discharge time of the RC circuit on RB0.

When the ULPWU module wakes the device from Sleep mode, the ULPWUIF bit (IFS5<0>) is set. Software can check this bit upon wake-up to determine the wake-up source. See Example 10-3 for initializing the ULPWU module.

A series resistor, between RB0 and the external capacitor, provides overcurrent protection for the RB0/AN0/ULPWU pin and enables software calibration of the time-out (see Figure 10-1).

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired delay in Sleep. This technique compensates for the affects of temperature, voltage and component accuracy. The peripheral can also be configured as a simple, programmable Low-Voltage Detect (LVD) or temperature sensor.

### EXAMPLE 10-3: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//*******************************

// 1. Charge the capacitor on RBO

TRISBbits.TRISB0 = 0;

LATBbits.LATB0 = 1:

for(i = 0; i < 10000; i++) Nop();</pre>

//*******

//2. Stop Charging the capacitor

// on RBO

//********************************

TRISBbits.TRISB0 = 1;

//3. Enable ULPWU Interrupt

IFS5bits.ULPWUIF = 0;

TEC5bits.ULPWUTE = 1:

IPC21bits.ULPWUIP = 0x7;

//********

//4. Enable the Ultra Low Power

11

Wakeup module and allow

11

capacitor discharge

ULPWCONbits.ULPEN = 1;

ULPWCONbit.ULPSINK = 1;

//********

//5. Enter Sleep Mode

//********************************

Sleep();

//for sleep, execution will

//resume here

```

| REGISTER     | R 10-3: ULP                                                                                                                                                        | WCON: ULPV       |                 | REGISTER         |                 |                 |         |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|------------------|-----------------|-----------------|---------|--|--|

| R/W-0        | U-0                                                                                                                                                                | R/W-0            | U-0             | U-0              | U-0             | U-0             | R/W-0   |  |  |

| ULPEN        | —                                                                                                                                                                  | ULPSIDL          | —               | —                | —               | —               | ULPSINK |  |  |

| bit 15       |                                                                                                                                                                    |                  |                 |                  |                 |                 | bit 8   |  |  |

|              |                                                                                                                                                                    |                  |                 |                  |                 |                 |         |  |  |

| U-0          | U-0                                                                                                                                                                | U-0              | U-0             | U-0              | U-0             | U-0             | U-0     |  |  |

| <br>bit 7    | _                                                                                                                                                                  |                  |                 | _                |                 |                 | bit C   |  |  |

|              |                                                                                                                                                                    |                  |                 |                  |                 |                 |         |  |  |

| Legend:      |                                                                                                                                                                    |                  |                 |                  |                 |                 |         |  |  |

| R = Readal   | ble bit                                                                                                                                                            | W = Writable b   | bit             | U = Unimpler     | nented bit, rea | d as '0'        |         |  |  |

| -n = Value a | at POR                                                                                                                                                             | '1' = Bit is set |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown    |  |  |

| bit 15       | <b>ULPEN:</b> ULF<br>1 = Module is<br>0 = Module is                                                                                                                |                  | able bit        |                  |                 |                 |         |  |  |

| bit 14       | Unimplemer                                                                                                                                                         | nted: Read as '  | )'              |                  |                 |                 |         |  |  |

| bit 13       | bit 13 ULPSIDL: ULPWU Stop in Idle Select bit<br>1 = Discontinues module operation when the device enters Idle mode<br>0 = Continues module operation in Idle mode |                  |                 |                  |                 |                 |         |  |  |

| bit 12-9     |                                                                                                                                                                    | nted: Read as '  |                 |                  |                 |                 |         |  |  |

| bit 8        | ULPSINK: U                                                                                                                                                         | LPWU Current     | Sink Enable bit |                  |                 |                 |         |  |  |

|              |                                                                                                                                                                    | sink is enabled  |                 |                  |                 |                 |         |  |  |

- 0 = Current sink is disabled

- bit 7-0 Unimplemented: Read as '0'

### **REGISTER 15-1:** OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)

### bit 2-0 OCM<2:0>: Output Compare x Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode on OCx

- 110 = Edge-Aligned PWM mode on OCx

- 101 = Double Compare Continuous Pulse mode: Initialize OCx pin low; toggle OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initialize OCx pin low; toggle OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare Continuous Pulse mode: Compare events continuously toggle the OCx pin

- 010 = Single Compare Single-Shot mode: Initialize OCx pin high; compare event forces the OCx pin low

- 001 = Single Compare Single-Shot mode: Initialize OCx pin low, compare event forces the OCx pin high

- 000 = Output compare channel is disabled

- **Note 1:** The comparator module used for Fault input varies with the OCx module. OC1 and OC2 use Comparator 1; OC3 and OC4 use Comparator 2; OC5 uses Comparator 3.

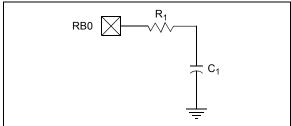

To set up the SPI1 module for the Enhanced Buffer Master (EBM) mode of operation:

- 1. If using interrupts:

- a) Clear the SPI1IF bit in the IFS0 register.

- b) Set the SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IPx bits in the IPC2 register.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 1.

- 3. Clear the SPIROV bit (SPI1STAT<6>).

- 4. Select Enhanced Buffer mode by setting the SPIBEN bit (SPI1CON2<0>).

- 5. Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

- 6. Write the data to be transmitted to the SPI1BUF register. Transmission (and reception) will start as soon as data is written to the SPI1BUF register.

To set up the SPI1 module for the Enhanced Buffer Slave mode of operation:

- 1. Clear the SPI1BUF register.

- 2. If using interrupts:

- a) Clear the SPI1IF bit in the IFS0 register.

- b) Set the SPI1IE bit in the IEC0 register.

- c) Write the respective SPI1IPx bits in the IPC2 register to set the interrupt priority.

- Write the desired settings to the SPI1CON1 and SPI1CON2 registers with the MSTEN bit (SPI1CON1<5>) = 0.

- 4. Clear the SMP bit.

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SS1 pin.

- 6. Clear the SPIROV bit (SPI1STAT<6>).

- Select Enhanced Buffer mode by setting the SPIBEN bit (SPI1CON2<0>).

- Enable SPI operation by setting the SPIEN bit (SPI1STAT<15>).

### FIGURE 16-2: SPI1 MODULE BLOCK DIAGRAM (ENHANCED BUFFER MODE)

## 22.1 A/D Control Registers

The 12-bit A/D Converter module uses up to 43 registers for its operation. All registers are mapped in the data memory space.

### 22.1.1 CONTROL REGISTERS

Depending on the specific device, the module has up to eleven control and status registers:

- AD1CON1: A/D Control Register 1

- AD1CON2: A/D Control Register 2

- AD1CON3: A/D Control Register 3

- AD1CON5: A/D Control Register 5

- AD1CHS: A/D Sample Select Register

- AD1CHITH and AD1CHITL: A/D Scan Compare Hit Registers

- AD1CSSL and AD1CSSH: A/D Input Scan Select Registers

- AD1CTMUENH and AD1CTMUENL: CTMU Enable Registers

The AD1CON1, AD1CON2 and AD1CON3 registers (Register 22-1, Register 22-2 and Register 22-3) control the overall operation of the A/D module. This includes enabling the module, configuring the conversion clock and voltage reference sources, selecting the sampling and conversion triggers, and manually controlling the sample/convert sequences. The AD1CON5 register (Register 22-4) specifically controls features of the Threshold Detect operation, including its function in power-saving modes.

The AD1CHS register (Register 22-5) selects the input channels to be connected to the S/H amplifier. It also allows the choice of input multiplexers and the selection of a reference source for differential sampling.

The AD1CHITH and AD1CHITL registers (Register 22-6 and Register 22-7) are semaphore registers used with Threshold Detect operations. The status of individual bits, or bit pairs in some cases,

indicate if a match condition has occurred. AD1CHITL is always implemented, whereas AD1CHITH may not be implemented in devices with 16 or fewer channels.

The AD1CSSH/L registers (Register 22-8 and Register 22-9) select the channels to be included for sequential scanning.

The AD1CTMUENH/L registers (Register 22-10 and Register 22-11) select the channel(s) to be used by the CTMU during conversions. Selecting a particular channel allows the A/D Converter to control the CTMU (particularly, its current source) and read its data through that channel. AD1CTMUENL is always implemented, whereas AD1CTMUENH may not be implemented in devices with 16 or fewer channels.

### 22.1.2 A/D RESULT BUFFERS

The module incorporates a multi-word, dual port RAM, called ADC1BUF. The buffer is composed of at least the same number of word locations as there are external analog channels for a particular device, with a maximum number of 32. The number of buffer addresses is always even. Each of the locations is mapped into the data memory space and is separately addressable. The buffer locations are referred to as ADC1BUF0 through ADC1BUFn (up to 31).

The A/D result buffers are both readable and writable. When the module is active (AD1CON<15> = 1), the buffers are read-only, and store the results of A/D conversions. When the module is inactive (AD1CON<15> = 0), the buffers are both readable and writable. In this state, writing to a buffer location programs a conversion threshold for Threshold Detect operations.

Buffer contents are not cleared when the module is deactivated with the ADON bit (AD1CON1<15>). Conversion results and any programmed threshold values are maintained when ADON is set or cleared.

## REGISTER 22-6: AD1CHITH: A/D SCAN COMPARE HIT REGISTER (HIGH WORD)<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   | U-0   |

|--------|-----|-----|-----|-----|-----|-------|-------|

| —      | —   | —   | —   | —   | _   |       | —     |

| bit 15 |     |     |     |     |     |       | bit 8 |

|        |     |     |     |     |     |       |       |

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|        |     | —   | —   | —   |     | CHH17 | CHH16 |

| bit 7  |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-2 Unimplemented: Read as '0'.

bit 1-0 CHH<17:16>: A/D Compare Hit bits

If CM<1:0> = 11:

- 1 = A/D Result Buffer x has been written with data or a match has occurred

- 0 = A/D Result Buffer x has not been written with data

- For All Other Values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

## REGISTER 22-7: AD1CHITL: A/D SCAN COMPARE HIT REGISTER (LOW WORD)<sup>(1)</sup>

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|

| CHH15        | CHH14 | CHH13 | CHH12 | CHH11 | CHH10 | CHH9  | CHH8  |

| bit 15 bit 8 |       |       |       |       |       | bit 8 |       |

|              |       |       |       |       |       |       |       |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| CHH7         | CHH6  | CHH5  | CHH4  | CHH3  | CHH2  | CHH1  | CHH0  |

| bit 7        | •     | •     | •     |       | •     | •     | bit 0 |

|              |       |       |       |       |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 CHH<15:0>: A/D Compare Hit bits

<u>If CM<1:0> = 11:</u>

- 1 = A/D Result Buffer x has been written with data or a match has occurred

- 0 = A/D Result Buffer x has not been written with data

- For all other values of CM<1:0>:

- 1 = A match has occurred on A/D Result Channel x

- 0 = No match has occurred on A/D Result Channel x

Note 1: Unimplemented channels are read as '0'.

| Assembly<br>Mnemonic | Assembly Syntax |             | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-----------------|-------------|------------------------------|---------------|----------------|--------------------------|

| TBLRDL               | TBLRDL          | Ws,Wd       | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| TBLWTH               | TBLWTH          | Ws,Wd       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| TBLWTL               | TBLWTL          | Ws,Wd       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| ULNK                 | ULNK            |             | Unlink Frame Pointer         | 1             | 1              | None                     |

| XOR                  | XOR             | f           | f = f .XOR. WREG             | 1             | 1              | N, Z                     |

|                      | XOR             | f,WREG      | WREG = f .XOR. WREG          | 1             | 1              | N, Z                     |

|                      | XOR             | #lit10,Wn   | Wd = lit10 .XOR. Wd          | 1             | 1              | N, Z                     |

|                      | XOR             | Wb,Ws,Wd    | Wd = Wb .XOR. Ws             | 1             | 1              | N, Z                     |

|                      | XOR             | Wb,#lit5,Wd | Wd = Wb .XOR. lit5           | 1             | 1              | N, Z                     |

| ZE                   | ZE              | Ws,Wnd      | Wnd = Zero-Extend Ws         | 1             | 1              | C, Z, N                  |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

|              |       |                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |     |       |                                                            |  |

|--------------|-------|----------------------------------|------------------------------------------------------|--------------------|-----|-------|------------------------------------------------------------|--|

| Param<br>No. | Sym   | Characteristic <sup>(1)</sup>    | Min                                                  | Тур <sup>(2)</sup> | Max | Units | Conditions                                                 |  |

| OS50         | Fplli | PLL Input Frequency<br>Range     | 4                                                    | —                  | 8   | MHz   | ECPLL, HSPLL modes, $-40^{\circ}C \le TA \le +85^{\circ}C$ |  |

| OS51         | Fsys  | PLL Output Frequency<br>Range    | 16                                                   | —                  | 32  | MHz   | $-40^{\circ}C \le TA \le +85^{\circ}C$                     |  |

| OS52         | TLOCK | PLL Start-up Time<br>(Lock Time) | _                                                    | 1                  | 2   | ms    |                                                            |  |

| OS53         | DCLK  | CLKO Stability (Jitter)          | -2                                                   | 1                  | 2   | %     | Measured over a 100 ms<br>period                           |  |

## TABLE 29-20: PLL CLOCK TIMING SPECIFICATIONS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 29-21: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHARACTERISTICS |                                              |     | Standard Operating Conditions:1.8V to 3.6V PIC24F32KA3XX<br>2.0V to 5.5V PIC24FV32KA3XXOperating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |       |                                        |                                                                                                                                                                        |  |  |  |

|--------------------|----------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Characteristic                               | Min | Тур                                                                                                                                                                                                                        | Max | Units | c                                      | onditions                                                                                                                                                              |  |  |  |

| F20                | Internal FRC Accuracy @ 8 MHz <sup>(1)</sup> |     |                                                                                                                                                                                                                            |     |       |                                        |                                                                                                                                                                        |  |  |  |

|                    | FRC                                          | -2  | _                                                                                                                                                                                                                          | +2  | %     | +25°C                                  | $\begin{array}{l} 3.0V \leq V\text{DD} \leq 3.6\text{V}, \mbox{ F device} \\ 3.2V \leq V\text{DD} \leq 5.5\text{V}, \mbox{ FV device} \end{array}$                     |  |  |  |

|                    |                                              | -5  | —                                                                                                                                                                                                                          | +5  | %     | $-40^{\circ}C \le TA \le +85^{\circ}C$ | $\begin{array}{l} 1.8V \leq V\text{DD} \leq 3.6\text{V}, \ \text{F} \ \text{device} \\ 2.0V \leq V\text{DD} \leq 5.5\text{V}, \ \text{FV} \ \text{device} \end{array}$ |  |  |  |

|                    | LPRC @ 31 kHz <sup>(2)</sup>                 | •   | •                                                                                                                                                                                                                          | •   | •     |                                        |                                                                                                                                                                        |  |  |  |

| F21                |                                              | -15 | _                                                                                                                                                                                                                          | 15  | %     |                                        |                                                                                                                                                                        |  |  |  |

**Note 1:** Frequency is calibrated at +25°C and 3.3V. The OSCTUN bits can be used to compensate for temperature drift.

2: The change of LPRC frequency as VDD changes.

## TABLE 29-22: INTERNAL RC OSCILLATOR SPECIFICATIONS

| AC CHARACTERISTICS |       |                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |            |  |  |

|--------------------|-------|-------------------------------|------------------------------------------------------|-----|-----|-------|------------|--|--|

| Param<br>No.       | Sym   | Characteristic <sup>(1)</sup> | Min                                                  | Тур | Мах | Units | Conditions |  |  |

|                    | TFRC  | FRC Start-up Time             | —                                                    | 5   | _   | μS    |            |  |  |

|                    | TLPRC | LPRC Start-up Time            | —                                                    | 70  | —   | μS    |            |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

## 31.0 PACKAGING INFORMATION

## 31.1 Package Marking Information

### 20-Lead PDIP (300 mil)

### 28-Lead SPDIP (.300")

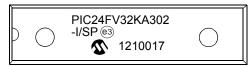

### Example

### 20-Lead SSOP (5.30 mm)

28-Lead SSOP (5.30 mm)

Example

## Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3                                                                                                                                                                     | Product-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ()<br>can be found on the outer packaging for this package. |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Note:   | In the event the full Microchip part number cannot be marked on one lin<br>will be carried over to the next line, thus limiting the number of availa<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                           |  |  |

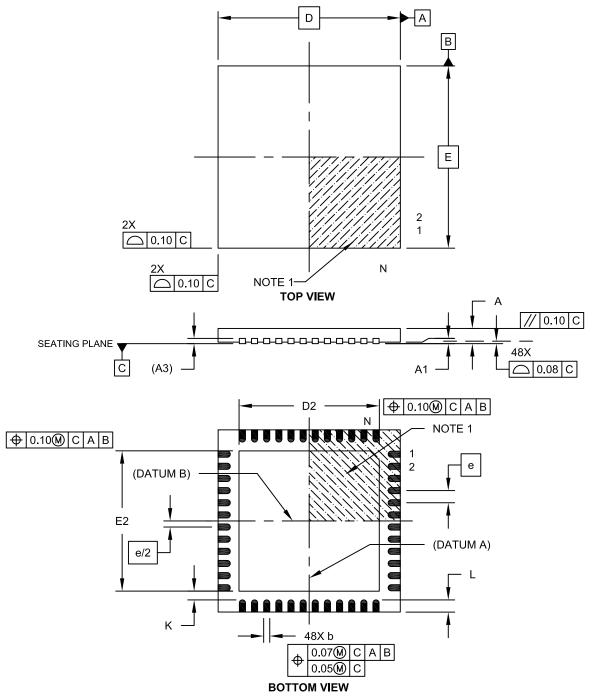

## 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-153A Sheet 1 of 2