Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 38                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |

| Data Converters            | A/D 10x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s105c6t6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 49.<br>Table 50.<br>Table 51. | ESD absolute maximum ratings<br>Electrical sensitivities<br>LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |     |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|

|                                     | mechanical data                                                                                                     |     |

| Table 52.                           | LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat package                                                           |     |

|                                     | mechanical data                                                                                                     | 95  |

| Table 53.                           | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package                                                             |     |

|                                     | mechanical data                                                                                                     |     |

| Table 54.                           | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat                                             |     |

|                                     | package mechanical data                                                                                             | 102 |

| Table 55.                           | SDIP32 package mechanical data                                                                                      |     |

| Table 56.                           | Thermal characteristics.                                                                                            | 106 |

| Table 57.                           | Document revision history                                                                                           | 116 |

| Device                                              | STM8S105C6                                                                                                                                    | STM8S105C4 | STM8S105S6 | STM8S105S4 | STM8S105K6 | STM8S105K4 |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|------------|------------|

| Pin count                                           | 48                                                                                                                                            | 48         | 44         | 44         | 32         | 32         |

| Maximum<br>number of<br>GPIOs                       | 38                                                                                                                                            | 38         | 34         | 34         | 25         | 25         |

| Ext. Interrupt<br>pins                              | 35                                                                                                                                            | 35         | 31         | 31         | 23         | 23         |

| Timer<br>CAPCOM<br>channels                         | 9                                                                                                                                             | 9          | 8          | 8          | 8          | 8          |

| Timer<br>complementar<br>y outputs                  | 3                                                                                                                                             | 3          | 3          | 3          | 3          | 3          |

| A/D Converter channels                              | 10                                                                                                                                            | 10         | 9          | 9          | 7          | 7          |

| High sink I/Os                                      | 16                                                                                                                                            | 16         | 15         | 15         | 12         | 12         |

| Medium<br>density Flash<br>Program<br>memory (byte) | 32К                                                                                                                                           | 16K        | 32K        | 16K        | 32K        | 16K        |

| Data<br>EEPROM<br>(bytes)                           | 1024                                                                                                                                          | 1024       | 1024       | 1024       | 1024       | 1024       |

| RAM (bytes)                                         | 2K                                                                                                                                            | 2K         | 2K         | 2K         | 2K         | 2K         |

| Peripheral set                                      | Advanced control timer (TIM1), General-purpose timers (TIM2 and TIM3), Basic timer (TIM4) SPI,<br>I2C, UART, Window WDG, Independent WDG, ADC |            |            |            |            |            |

| Table 1. STM8S105x4/6 access line feat | tures |

|----------------------------------------|-------|

# 4 **Product overview**

The following section provides an overview of the basic features of the device functional modules and peripherals.

For more detailed information please refer to the corresponding family reference manual (RM0016).

## 4.1 Central processing unit STM8

The 8-bit STM8 core is designed for code efficiency and performance.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing and 80 instructions.

### Architecture and registers

- Harvard architecture,

- 3-stage pipeline,

- 32-bit wide program memory bus single cycle fetching for most instructions,

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations,

- 8-bit accumulator,

- 24-bit program counter 16-Mbyte linear memory space,

- 16-bit stack pointer access to a 64 K-level stack,

- 8-bit condition code register 7 condition flags for the result of the last instruction.

## Addressing

- 20 addressing modes,

- Indexed indirect addressing mode for look-up tables located anywhere in the address space,

- Stack pointer relative addressing mode for local variables and parameter passing.

### Instruction set

- 80 instructions with 2-byte average instruction size,

- Standard data movement and logic/arithmetic functions,

- 8-bit by 8-bit multiplication,

- 16-bit by 8-bit and 16-bit by 16-bit division,

- Bit manipulation,

- Data transfer between stack and accumulator (push/pop) with direct stack access,

- Data transfer using the X and Y registers or direct memory-to-memory transfers.

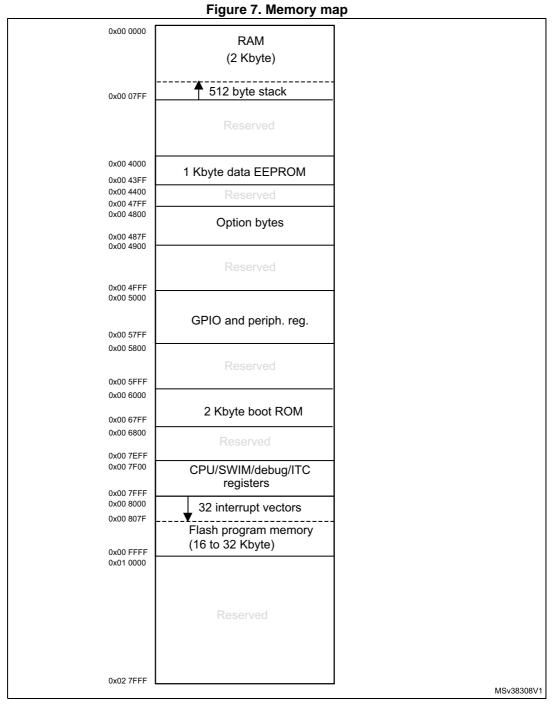

# 6 Memory and register map

## 6.1 Memory map

The following table lists the boundary addresses for each memory size. The top of the stack is at the RAM end address in each case.

| Address                | Block        | Register label | Register name                      | Reset status |

|------------------------|--------------|----------------|------------------------------------|--------------|

| 0x00 5208 to 0x00 520F | Reserved are | ea (8 byte)    |                                    | ·            |

| 0x00 5210              |              | I2C_CR1        | I2C control register 1             | 0x00         |

| 0x00 5211              |              | I2C_CR2        | I2C control register 2             | 0x00         |

| 0x00 5212              |              | I2C_FREQR      | I2C frequency register             | 0x00         |

| 0x00 5213              |              | I2C_OARL       | I2C Own address register low       | 0x00         |

| 0x00 5214              |              | I2C_OARH       | I2C Own address register<br>high   | 0x00         |

| 0x00 5215              |              | Reserved       |                                    |              |

| 0x00 5216              |              | I2C_DR         | I2C data register                  | 0x00         |

| 0x00 5217              | I2C          | I2C_SR1        | I2C status register 1              | 0x00         |

| 0x00 5218              |              | I2C_SR2        | I2C status register 2              | 0x00         |

| 0x00 5219              |              | I2C_SR3        | I2C status register 3              | 0x0X         |

| 0x00 521A              |              | I2C_ITR        | I2C interrupt control register     | 0x00         |

| 0x00 521B              |              | I2C_CCRL       | I2C Clock control register low     | 0x00         |

| 0x00 521C              |              | I2C_CCRH       | I2C Clock control register high    | 0x00         |

| 0x00 521D              |              | I2C_TRISER     | I2C TRISE register                 | 0x02         |

| 0x00 521E              |              | I2C_PECR       | I2C packet error checking register | 0x00         |

| 0x00 521F to 0x00 522F | Reserved are | ea (17 byte)   |                                    | •            |

| 0x00 5230 to 0x00 523F | Reserved are | ea (6 byte)    |                                    |              |

| 0x00 5240              |              | UART2_SR       | UART2 status register              | 0xC0         |

| 0x00 5241              |              | UART2_DR       | UART2 data register                | 0xXX         |

| 0x00 5242              |              | UART2_BRR1     | UART2 baud rate register 1         | 0x00         |

| 0x00 5243              |              | UART2_BRR2     | UART2 baud rate register 2         | 0x00         |

| 0x00 5244              |              | UART2_CR1      | UART2 control register 1           | 0x00         |

| 0x00 5245              |              | UART2_CR2      | UART2 control register 2           | 0x00         |

| 0x00 5246              | UART2        | UART2_CR3      | UART2 control register 3           | 0x00         |

| 0x00 5247              |              | UART2_CR4      | UART2 control register 4           | 0x00         |

| 0x00 5248              | 1            | UART2_CR5      | UART2 control register 5           | 0x00         |

| 0x00 5249              | 1            | UART2_CR6      | UART2 control register 6           | 0x00         |

| 0x00 524A              | 1            | UART2_GTR      | UART2 guard time register          | 0x00         |

| 0x00 524B              | ]            | UART2_PSCR     | UART2 prescaler register           | 0x00         |

| 0x00 524C to 0x00 524F | Reserved are | ea (4 byte)    |                                    |              |

| Table 8. General | hardware register | r map (continued) |

|------------------|-------------------|-------------------|

|                  | na ana o rogioto  | map (00mma0a)     |

| Table 8. Genera | l hardware registe  | er map (continued) |

|-----------------|---------------------|--------------------|

|                 | i na ana o i ogioto | , map (00mma0a)    |

| Address   | Block | Register label | Register name                          | Reset status |

|-----------|-------|----------------|----------------------------------------|--------------|

| 0x00 5250 |       | TIM1_CR1       | TIM1 control register 1                | 0x00         |

| 0x00 5251 |       | TIM1_CR2       | TIM1 control register 2                | 0x00         |

| 0x00 5252 |       | TIM1_SMCR      | TIM1 slave mode control register       | 0x00         |

| 0x00 5253 |       | TIM1_ETR       | TIM1 external trigger register         | 0x00         |

| 0x00 5254 |       | TIM1_IER       | TIM1 interrupt enable register         | 0x00         |

| 0x00 5255 |       | TIM1_SR1       | TIM1 status register 1                 | 0x00         |

| 0x00 5256 |       | TIM1_SR2       | TIM1 status register 2                 | 0x00         |

| 0x00 5257 |       | TIM1_EGR       | TIM1 event generation register         | 0x00         |

| 0x00 5258 |       | TIM1_CCMR1     | TIM1 capture/compare mode register 1   | 0x00         |

| 0x00 5259 |       | TIM1_CCMR2     | TIM1 capture/compare mode register 2   | 0x00         |

| 0x00 525A |       | TIM1_CCMR3     | TIM1 capture/compare mode register 3   | 0x00         |

| 0x00 525B |       | TIM1_CCMR4     | TIM1 capture/compare mode register 4   | 0x00         |

| 0x00 525C | TIM1  | TIM1_CCER1     | TIM1 capture/compare enable register 1 | 0x00         |

| 0x00 525D |       | TIM1_CCER2     | TIM1 capture/compare enable register 2 | 0x00         |

| 0x00 525E |       | TIM1_CNTRH     | TIM1 counter high                      | 0x00         |

| 0x00 525F |       | TIM1_CNTRL     | TIM1 counter low                       | 0x00         |

| 0x00 5260 |       | TIM1_PSCRH     | TIM1 prescaler register high           | 0x00         |

| 0x00 5261 |       | TIM1_PSCRL     | TIM1 prescaler register low            | 0x00         |

| 0x00 5262 |       | TIM1_ARRH      | TIM1 auto-reload register high         | 0xFF         |

| 0x00 5263 |       | TIM1_ARRL      | TIM1 auto-reload register low          | 0xFF         |

| 0x00 5264 |       | TIM1_RCR       | TIM1 repetition counter register       | 0x00         |

| 0x00 5265 |       | TIM1_CCR1H     | TIM1 capture/compare register 1 high   | 0x00         |

| 0x00 5266 |       | TIM1_CCR1L     | TIM1 capture/compare<br>register 1 low | 0x00         |

| 0x00 5267 |       | TIM1_CCR2H     | TIM1 capture/compare register 2 high   | 0x00         |

| 0x00 5268 |       | TIM1_CCR2L     | TIM1 capture/compare<br>register 2 low | 0x00         |

| 0x00 5269 |       | TIM1_CCR3H     | TIM1 capture/compare register 3 high   | 0x00         |

# 10.2 Absolute maximum ratings

Stresses above those listed as 'absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                           | Min                   | Max                                        | Unit |

|------------------------------------|-------------------------------------------------------------------|-----------------------|--------------------------------------------|------|

| $V_{DDx}$ - $V_{SS}$               | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                  | 6.5                                        | V    |

| V                                  | Input voltage on true open drain pins (PE1, PE2) <sup>(2)</sup>   | V <sub>SS</sub> - 0.3 | 6.5                                        | V    |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3                      | v    |

| V <sub>DDx</sub> - V <sub>DD</sub> | Variations between different power pins                           | -                     | 50                                         | mV   |

| $ V_{SSx} - V_{SS} $               | Variations between all the different ground pins                  | -                     | 50                                         | IIIV |

| V <sub>ESD</sub>                   | Electrostatic discharge voltage                                   |                       | ite maximum<br>cal sensitivity,<br>page 89 |      |

| Table 15. | Voltage | characteristics |

|-----------|---------|-----------------|

|-----------|---------|-----------------|

1. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

| Symbol                                   | Ratings                                                                                                          | Max. <sup>(1)</sup> | Unit |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------|------|

| I <sub>VDD</sub>                         | Total current into V <sub>DD</sub> power lines (source) <sup>(2)</sup>                                           | 100                 | mA   |

| I <sub>VSS</sub>                         | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>                                                 | 80                  |      |

|                                          | Output current sunk by any I/O and control pin                                                                   | 20                  |      |

| IIO                                      | Output current source by any I/Os and control pin                                                                | -20                 |      |

|                                          | Total output current sourced (sum of all I/O and control pins) for devices with two $V_{DDIO}\ pins^{(3)}$       | 200                 |      |

| Σl <sub>IO</sub>                         | Total output current sourced (sum of all I/O and control pins) for devices with one $V_{DDIO}\rm{pin}^{(3)}$     | 100                 |      |

|                                          | Total output current sunk (sum of all I/O and control pins) for devices with two ${\rm V}_{\rm SSIO}$ pins^{(3)} | 160                 |      |

|                                          | Total output current sunk (sum of all I/O and control pins) for devices with one $V_{SSIO}\text{pin}^{(3)}$      | 80                  |      |

|                                          | Injected current on NRST pin                                                                                     | ±4                  |      |

| I <sub>INJ(PIN)</sub> <sup>(4) (5)</sup> | Injected current on OSCIN pin                                                                                    | ±4                  |      |

|                                          | Injected current on any other pin <sup>(6)</sup>                                                                 | ±4                  |      |

| $\Sigma I_{INJ(PIN)}^{(4)}$              | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>                                          | ±20                 |      |

### Table 16. Current characteristics

1. Data based on characterization results, not tested in production.

All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external supply.

HSI internal RC/f<sub>CPU</sub>=  $f_{MASTER}$  = 16 MHz,  $V_{DD}$  = 5 V

Table 30. Peripheral current consumption

| Symbol                 | Parameter                                          | Тур | Unit |

|------------------------|----------------------------------------------------|-----|------|

| I <sub>DD(TIM1)</sub>  | TIM1 supply current <sup>(1)</sup>                 | 230 |      |

| I <sub>DD(TIM2)</sub>  | TIM2 supply current <sup>(1)</sup>                 | 115 |      |

| I <sub>DD(TIM3)</sub>  | TIM3 supply current <sup>(1)</sup>                 | 90  |      |

| I <sub>DD(TIM4)</sub>  | TIM4 supply current <sup>(1)</sup>                 | 30  |      |

| I <sub>DD(UART2)</sub> | UART2 supply current <sup>(2)</sup>                | 110 | μΑ   |

| I <sub>DD(SPI)</sub>   | SPI supply current <sup>(2)</sup>                  | 45  |      |

| I <sub>DD(I2C)</sub>   | I2C supply current <sup>(2)</sup>                  | 65  |      |

| I <sub>DD(ADC1)</sub>  | ADC1 supply current when converting <sup>(3)</sup> | 955 |      |

Data based on a differential I<sub>DD</sub> measurement between reset configuration and timer counter running at 16 MHz. No IC/OC programmed (no I/O pads toggling). Not tested in production.

2. Data based on a differential IDD measurement between the on-chip peripheral when kept under reset and not clocked and the on-chip peripheral when clocked and not kept under reset. No I/O pads toggling. Not tested in production.

3. Data based on a differential IDD measurement between reset configuration and continuous A/D conversions. Not tested in production.

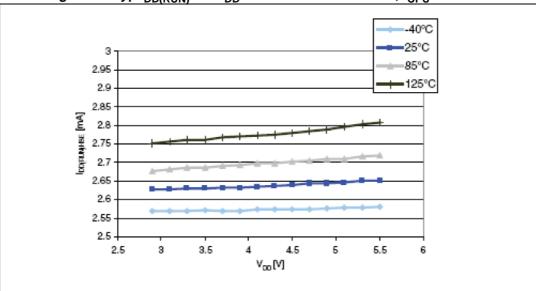

### **Current consumption curves**

The following figures show typical current consumption measured with code executing in RAM.

Figure 13. Typ  $I_{DD(RUN)}$  vs.  $V_{DD}$  HSE user external clock,  $f_{CPU}$  = 16 MHz

## HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol Parameter                    |                                             | Conditions Min                         |   | Тур | Мах                                             | Unit |

|-------------------------------------|---------------------------------------------|----------------------------------------|---|-----|-------------------------------------------------|------|

| f <sub>HSE</sub>                    | External high speed oscillator frequency    | -                                      | 1 | -   | 16                                              | MHz  |

| R <sub>F</sub>                      | Feedback resistor                           | -                                      | - | 220 | -                                               | kΩ   |

| C <sup>(1)</sup>                    | Recommended load capacitance <sup>(2)</sup> | -                                      | - | -   | 20                                              | pF   |

| 1                                   | HSE oscillator power consumption            | C = 20 pF<br>f <sub>OSC</sub> = 16 MHz | - | -   | 6 (start up)<br>1.6 (stabilized) <sup>(3)</sup> | mA   |

| IDD(HSE)                            |                                             | C = 10 pF<br>f <sub>OSC</sub> = 16 MHz | - | -   | 6 (start up)<br>1.2 (stabilized) <sup>(3)</sup> |      |

| 9 <sub>m</sub>                      | Oscillator<br>transconductance              | -                                      | 5 | -   | -                                               | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | V <sub>DD</sub> is stabilized          | - | 1   | -                                               | ms   |

|  | Table 32. | HSE | oscillator | characteristics |

|--|-----------|-----|------------|-----------------|

|--|-----------|-----|------------|-----------------|

1. C is approximately equivalent to 2 x crystal Cload.

2. The oscillator selection can be optimized in terms of supply current using a high quality resonator with small Rm value. Refer to crystal manufacturer for more details

3. Data based on characterization results, not tested in production.

t<sub>SU(HSE)</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 16 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

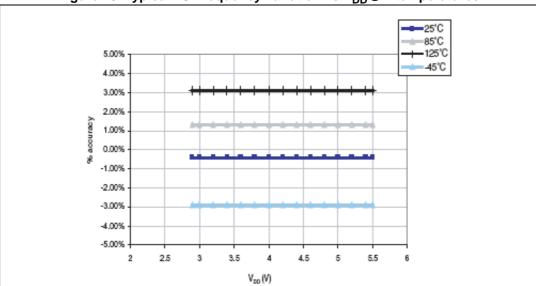

# Low speed internal RC oscillator (LSI)

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

| Table 34, LSI | oscillator | characteristics    |

|---------------|------------|--------------------|

|               | osomator   | 01101 00101 101100 |

| Symbol               | Parameter                        | Conditions | Min | Тур | Max              | Unit |

|----------------------|----------------------------------|------------|-----|-----|------------------|------|

| f <sub>LSI</sub>     | Frequency                        | -          | 110 | 128 | 150              | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time       | -          | -   | -   | 7 <sup>(1)</sup> | μs   |

| IDD(LSI)             | LSI oscillator power consumption | -          | -   | 5   | -                | μA   |

1. Guaranteed by design, not tested in production.

## 10.3.5 Memory characteristics

## **RAM and hardware registers**

### Table 35. RAM and hardware registers

| Symbol          | Parameter                          | Conditions           | Min                                | Unit |

|-----------------|------------------------------------|----------------------|------------------------------------|------|

| V <sub>RM</sub> | Data retention mode <sup>(1)</sup> | Halt mode (or reset) | V <sub>IT-max</sub> <sup>(2)</sup> | V    |

1. Minimum supply voltage without losing data stored in RAM (in halt mode or under reset) or in hardware registers (only in halt mode). Guaranteed by design, not tested in production.

2. Refer to Section 10.3: Operating conditions for the value of  $V_{IT-max}$ .

### Flash program memory/data EEPROM memory

| Symbol             | I Parameter Conditions                                                                         |                           | Min <sup>(1)</sup> | Тур | Max  | Unit  |

|--------------------|------------------------------------------------------------------------------------------------|---------------------------|--------------------|-----|------|-------|

| V <sub>DD</sub>    | Operating voltage<br>(all modes, execution/write/erase)                                        | f <sub>CPU</sub> ≤ 16 MHz | 2.95               | -   | 5.5  | V     |

| t <sub>prog</sub>  | Standard programming time (including<br>erase) for byte/word/block<br>(1 byte/4 byte/128 byte) | -                         | -                  | 6   | 6.6  |       |

| P 5                | Fast programming time for 1 block (128 byte)                                                   | -                         | -                  | 3   | 3.33 | ms    |

| t <sub>erase</sub> | Erase time for 1 block (128 byte)                                                              | -                         | 3 3.33             |     |      |       |

| N <sub>RW</sub>    | Erase/write cycles<br>(program memory) <sup>(2)</sup>                                          | T <sub>A</sub> = +85 °C   | 10k                | -   | -    | cycle |

|                    | Erase/write cycles (data memory) <sup>(2)</sup>                                                | T <sub>A</sub> = +125 °C  | 300k               | 1M  | -    |       |

| +                  | Data retention (program and data memory) after 10k erase/write cycles at $T_A$ = +55 °C        | T <sub>RET</sub> = 55 °C  | 20                 | -   | -    | Voor  |

| t <sub>RET</sub>   | Data retention (data memory) after<br>300k erase/write cycles at<br>T <sub>A</sub> = +125°C    | T <sub>RET</sub> = 85 °C  | 1                  | -   | -    | year  |

| I <sub>DD</sub>    | Supply current (Flash programming or erasing for 1 to 128 byte)                                | -                         | -                  | 2   | -    | mA    |

## Table 36. Flash program memory/data EEPROM memory

1. Data based on characterization results, not tested in production.

2. The physical granularity of the memory is 4 byte, so cycling is performed on 4 byte even when a write/erase operation addresses a single byte.

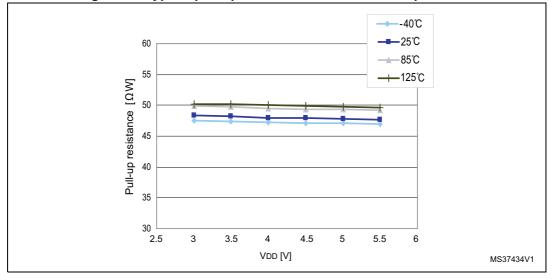

Figure 26. Typical pull-up resistance vs VDD @ 4 temperatures

| Table 38. Output driving current | (standard ports) |

|----------------------------------|------------------|

|----------------------------------|------------------|

| Symbol          | Parameter                                | Conditions                                         | Min                | Мах                | Unit |

|-----------------|------------------------------------------|----------------------------------------------------|--------------------|--------------------|------|

| V <sub>OL</sub> | Output low level with 8 pins sunk        | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | -                  | 2.0                |      |

|                 | Output low level with 4 pins sunk        | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | -                  | 1.0 <sup>(1)</sup> | V    |

|                 | Output high level with 8<br>pins sourced | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | 2.4                | -                  | V    |

| V <sub>OH</sub> | Output high level with 4 pins sourced    | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | 2.0 <sup>(1)</sup> | -                  |      |

1. Data based on characterization results, not tested in production

DocID14771 Rev 15

## 10.3.8 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                                    | Conditions             | Min                 | Тур | Max                  | Unit |

|-------------------------|----------------------------------------------|------------------------|---------------------|-----|----------------------|------|

| V <sub>IL(NRST)</sub>   | NRST input low level voltage <sup>(1)</sup>  | -                      | -0.3                | -   | $0.3 \times V_{DD}$  |      |

| V <sub>IH(NRST)</sub>   | NRST input high level voltage <sup>(1)</sup> | I <sub>OL</sub> = 2 mA | $0.7 \times V_{DD}$ | -   | V <sub>DD</sub> +0.3 | V    |

| V <sub>OL(NRST)</sub>   | NRST output low level voltage <sup>(1)</sup> | I <sub>OL</sub> = 3 mA | -                   | -   | 0.5                  |      |

| R <sub>PU(NRST)</sub>   | NRST pull-up resistor <sup>(2)</sup>         | -                      | 30                  | 55  | 80                   | kΩ   |

| t <sub>IFP(NRST)</sub>  | NRST input filtered pulse <sup>(3)</sup>     | -                      | -                   | -   | 75                   | ns   |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse <sup>(3)</sup> | -                      | 500                 | -   | -                    | 10   |

| t <sub>OP(NRST)</sub>   | NRST output pulse <sup>(3)</sup>             | -                      | 20                  | -   | -                    | μs   |

| Table 41. | NRST | pin | characteristics |

|-----------|------|-----|-----------------|

|           |      | P   | onaraotoriotioo |

1. Data based on characterization results, not tested in production.

2. The  $\mathsf{R}_{\mathsf{PU}}$  pull-up equivalent resistor is based on a resistive transistor.

3. Data guaranteed by design, not tested in production.

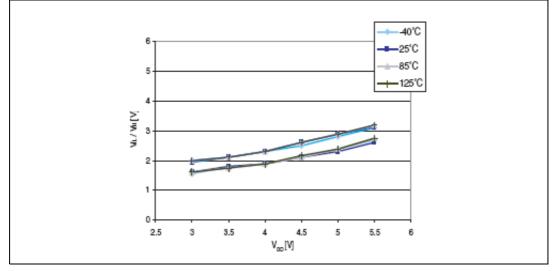

## Figure 37. Typical NRST $\rm V_{IL}$ and $\rm V_{IH}$ vs $\rm V_{DD}$ @ 4 temperatures

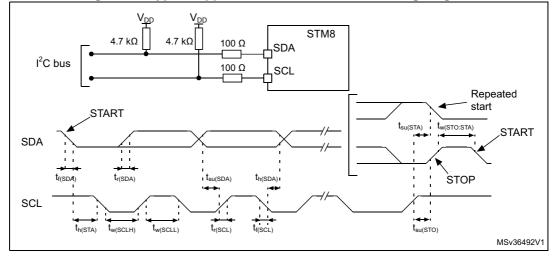

# 10.3.10 I<sup>2</sup>C interface characteristics

| Symbol                                     | Parameter                                                      | Standard                         | mode I <sup>2</sup> C | Fast mod           | Unit               |      |  |

|--------------------------------------------|----------------------------------------------------------------|----------------------------------|-----------------------|--------------------|--------------------|------|--|

| Symbol                                     | raiameter                                                      | Min <sup>(2)</sup>               | Max <sup>(2)</sup>    | Min <sup>(2)</sup> | Max <sup>(2)</sup> | Unit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                             | 4.7                              | -                     | 1.3                | -                  |      |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                            | 4.0                              | -                     | 0.6                | -                  | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                 | 250                              | -                     | 100                | -                  |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                             | ata hold time 0 <sup>(3)</sup> - |                       | 0 <sup>(4)</sup>   | 900 <sup>(3)</sup> |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time<br>(V <sub>DD</sub> = 3 to 5.5 V)        | -                                | 1000                  | -                  | 300 ns             |      |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time $(V_{DD} = 3 \text{ to } 5.5 \text{ V})$ | -                                | 300                   | -                  |                    |      |  |

| t <sub>h(STA)</sub>                        | START condition hold time                                      | 4.0                              | -                     | 0.6                | -                  |      |  |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time                            | 4.7                              | -                     | 0.6                | -                  |      |  |

| t <sub>su(STO)</sub>                       | STOP condition setup time                                      | 4.0                              | -                     | 0.6                | -                  | μs   |  |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free)                        | 4.7                              | -                     | 1.3                | -                  |      |  |

| Cb                                         | Capacitive load for each bus line                              | -                                | 400                   | -                  | 400                | pF   |  |

## Table 43. I<sup>2</sup>C characteristics

1.  $f_{MASTER}$ , must be at least 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz)

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

## Figure 44. Typical application with I<sup>2</sup>C bus and timing diagram

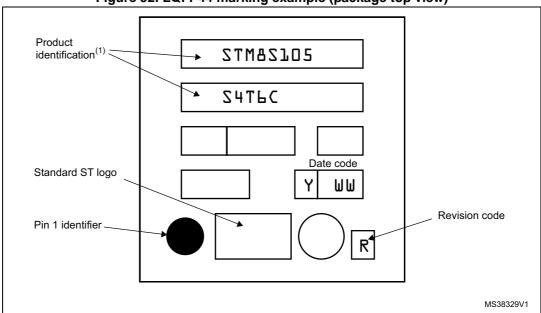

Figure 52. LQFP44 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

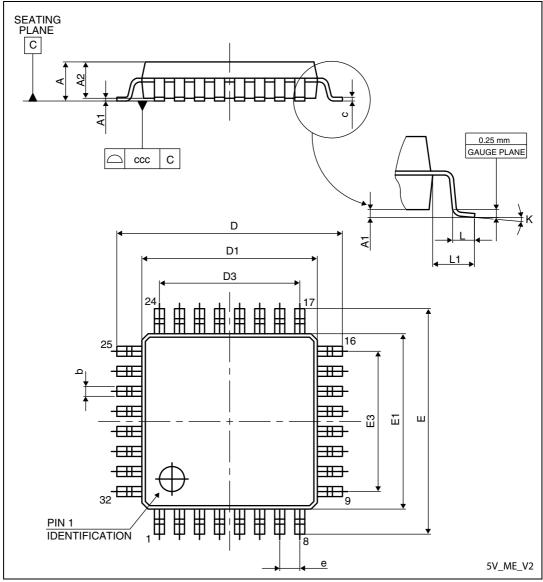

# 11.3 LQFP32 package information

Figure 53. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Dim.  |       | mm    |        |        | inches <sup>(1)</sup> |        |  |

|-------|-------|-------|--------|--------|-----------------------|--------|--|

| Dini. | Min   | Тур   | Max    | Min    | Тур                   | Max    |  |

| eB    | -     | -     | 12.700 | -      | -                     | 0.5000 |  |

| L     | 2.540 | 3.048 | 3.810  | 0.1000 | 0.1200                | 0.1500 |  |

### Table 55. SDIP32 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits

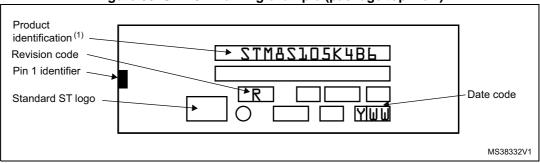

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

### Figure 60. SDIP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Sep-2010 | 10       | Table: Legend/Abbreviations for pinout tables: updated"reset state"; removed "HS", (T), and "[]".Section: Pin description for STM8S105 microcontrollers:added footnotes to the PF4 and PD1 pins.Table: I/O port hardware register map: changed resetstatus of Px_IDR from 0x00 to 0xXX.Table: General hardware register map: Standardized alladdress and reset state values; updated the reset statevalues of the RST_SR, CLK_SWCR, CLK_HSITRIMR,CLK_SWIMCCR, IWDG_KR, UART2_DR, andADC_DRx registers; replaced reserved address "0x005248" with the UART2_CR5.Section: Recommended reset pin protection: replaced0.01 µF with 0.1 µFUpdated Table: ADC accuracy with RAIN < 10 kohm ,                                                                                                                 |

| 04-Apr-2012 | 11       | Removed VFQFPN32 package.<br>Modified Section: Description.<br>Remove weak pull-up input for PE1 and PE2 in Table:<br>Pin description for STM8S105 microcontrollers<br>Updated Table: Interrupt mapping for TIM2 and TIM4.<br>Updated notes related to VCAP in xm-replace_text<br>General operating conditions.<br>Added values of $t_R/t_F$ for 50 pF load capacitance, and<br>updated note in Section: I/O static characteristics.<br>Updated typical and maximum values of RPU in Table:<br>I/O static characteristics and Table: RST pin<br>characteristics.<br>Changed SCK input to SCK output in Table: SPI serial<br>peripheral interface.<br>Added $\Theta_{JA}$ for UFQFPN32 and SDIP32 in Table:<br>Thermal characteristics, and updated Section: Selecting<br>the product temperature range |

| 28-Jun-2012 | 12       | Added UFQFPN package thickness in <i>Figure:</i><br><i>STM8S105xx</i> access line ordering information scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 57. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID14771 Rev 15