Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status                            |                                                 |

|-------------------------------------------|-------------------------------------------------|

| Product Status                            | Active                                          |

| Core Processor                            | STM8A                                           |

| Core Size                                 | 8-Bit                                           |

| Speed                                     | 16MHz                                           |

| Connectivity                              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART |

| Peripherals                               | Brown-out Detect/Reset, POR, PWM, WDT           |

| Number of I/O                             | 25                                              |

| Program Memory Size                       | 16KB (16K x 8)                                  |

| Program Memory Type                       | FLASH                                           |

| EEPROM Size                               | 1K x 8                                          |

| RAM Size                                  | 2K x 8                                          |

| Voltage - Supply (Vcc/Vdd)                | 2.95V ~ 5.5V                                    |

| Data Converters                           | A/D 7x10b                                       |

| Oscillator Type                           | Internal                                        |

| Operating Temperature                     | -40°C ~ 125°C (TA)                              |

| Mounting Type                             | Surface Mount                                   |

|                                           |                                                 |

| Package / Case                            | 32-UFQFN Exposed Pad                            |

| Package / Case<br>Supplier Device Package | 32-UFQFPN (5x5)                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 49.<br>Table 50.<br>Table 51. | ESD absolute maximum ratings<br>Electrical sensitivities<br>LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |     |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|

|                                     | mechanical data                                                                                                     |     |

| Table 52.                           | LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat package                                                           |     |

|                                     | mechanical data                                                                                                     | 95  |

| Table 53.                           | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package                                                             |     |

|                                     | mechanical data                                                                                                     |     |

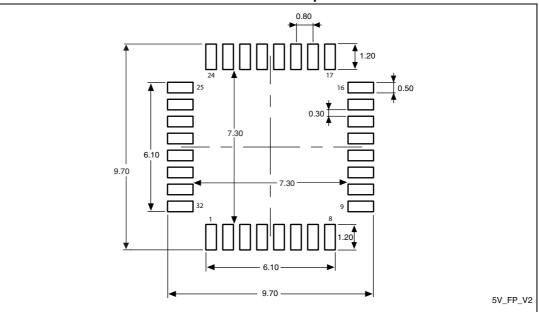

| Table 54.                           | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat                                             |     |

|                                     | package mechanical data                                                                                             | 102 |

| Table 55.                           | SDIP32 package mechanical data                                                                                      |     |

| Table 56.                           | Thermal characteristics.                                                                                            | 106 |

| Table 57.                           | Document revision history                                                                                           | 116 |

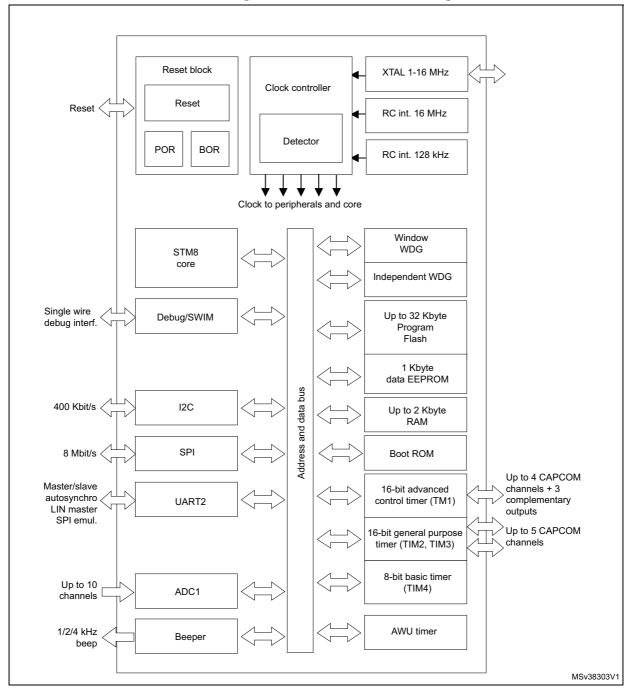

# 3 Block diagram

DocID14771 Rev 15

The IWDG time base spans from 60  $\mu$ s to 1 s.

### 4.8 Auto wakeup counter

- Used for auto wakeup from active halt mode,

- Clock source: Internal 128 kHz internal low frequency RC oscillator or external clock,

- LSI clock can be internally connected to TIM1 input capture channel 1 for calibration.

### 4.9 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

The beeper output port is only available through the alternate function remap option bit AFR7.

## 4.10 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- Four independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- Synchronization module to control the timer with external signals

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update, 1 x break

### 4.11 TIM2, TIM3 - 16-bit general purpose timers

- 16-bit auto reload (AR) up-counter

- 15-bit prescaler adjustable to fixed power of 2 ratios 1...32768

- Timers with 3 or 2 individually configurable capture/compare channels

- PWM mode

- Interrupt sources: 2 or 3 x input capture/output compare, 1 x overflow/update

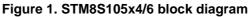

Figure 5. UFQFPN32/LQFP32 pinout

1. (HS) high sink capability.

2. [] alternate function remapping option (if the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

# 6.2.2 General hardware register map

|                        | Table 8. General hardware register map |                         |                                                  |                     |  |  |

|------------------------|----------------------------------------|-------------------------|--------------------------------------------------|---------------------|--|--|

| Address                | Block                                  | Register label          | Register name                                    | Reset status        |  |  |

| 0x00 5050 to 0x00 5059 | Reserved are                           | Reserved area (10 byte) |                                                  |                     |  |  |

| 0x00 505A              |                                        | FLASH_CR1               | Flash control register 1                         | 0x00                |  |  |

| 0x00 505B              |                                        | FLASH_CR2               | Flash control register 2                         | 0x00                |  |  |

| 0x00 505C              |                                        | FLASH_NCR2              | Flash complementary control register 2           | 0xFF                |  |  |

| 0x00 505D              | Flash                                  | FLASH_FPR               | Flash protection register                        | 0x00                |  |  |

| 0x00 505E              |                                        | FLASH_NFPR              | Flash complementary<br>protection register       | 0xFF                |  |  |

| 0x00 505F              |                                        | FLASH_IAPSR             | Flash in-application programming status register | 0x00                |  |  |

| 0x00 5060 to 0x00 5061 | Reserved are                           | ea (2 byte)             | ·                                                |                     |  |  |

| 0x00 5062              | Flash                                  | FLASH_PUKR              | Flash program memory<br>unprotection register    | 0x00                |  |  |

| 0x00 5063              | Reserved are                           | ea (1 byte)             |                                                  |                     |  |  |

| 0x00 5064              | Flash                                  | FLASH _DUKR             | Data EEPROM unprotection register                | 0x00                |  |  |

| 0x00 5065 to 0x00 509F | Reserved are                           | ea (59 byte)            |                                                  |                     |  |  |

| 0x00 50A0              |                                        | EXTI_CR1                | External interrupt control register 1            | 0x00                |  |  |

| 0x00 50A1              | - ITC                                  | EXTI_CR2                | External interrupt control register 2            | 0x00                |  |  |

| 0x00 50A2 to 0x00 50B2 | Reserved are                           | ea (17 byte)            |                                                  |                     |  |  |

| 0x00 50B3              | RST                                    | RST_SR                  | Reset status register                            | 0xXX <sup>(1)</sup> |  |  |

| 0x00 50B4 to 0x00 50BF | Reserved are                           | ea (12 byte)            |                                                  |                     |  |  |

| 0x00 50C0              | CLK                                    | CLK_ICKR                | Internal clock control register                  | 0x01                |  |  |

| 0x00 50C1              |                                        | CLK_ECKR                | External clock control register                  | 0x00                |  |  |

| 0x00 50C2              | Reserved are                           | ea (1 byte)             |                                                  |                     |  |  |

#### Table 8. General hardware register map

| Symbol                | Parameter                     | Conditions | Min  | Тур  | Max  | Unit |

|-----------------------|-------------------------------|------------|------|------|------|------|

| V <sub>IT+</sub>      | Power-on reset<br>threshold   | -          | 2.65 | 2.8  | 2.95 | V    |

| V <sub>IT-</sub>      | Brown-out reset<br>threshold  | -          | 2.58 | 2.65 | 2.88 | v    |

| V <sub>HYS(BOR)</sub> | Brown-out reset<br>hysteresis | -          | -    | 70   | -    | mV   |

Table 19. Operating conditions at power-up/power-down (continued)

1. Guaranteed by design, not tested in production.

| Symbol               | Parameter                              | Conditions                                                  |                                       | Тур  | Max <sup>(1)</sup> | Unit |

|----------------------|----------------------------------------|-------------------------------------------------------------|---------------------------------------|------|--------------------|------|

|                      |                                        | HSE crystal osc. (16 MHz)                                   | 2.8                                   | -    |                    |      |

|                      |                                        | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock<br>(16 MHz)       | 2.6  | 3.2                |      |

|                      | Supply current in                      |                                                             | HSI RC osc. (16 MHz)                  | 2.5  | 3.2                |      |

| I <sub>DD(RUN)</sub> | Run mode,<br>code                      | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSE user ext. clock<br>(16 MHz)       | 1.6  | 2.2                | mA   |

|                      | executed<br>from RAM                   |                                                             | HSI RC osc. (16 MHz)                  | 1.3  | 2.0                |      |

|                      |                                        | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8)                | 0.75 | -                  |      |

|                      |                                        | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.55 | -                  |      |

|                      |                                        | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE crystal osc. (16 MHz)             | 7.3  | -                  |      |

|                      |                                        |                                                             | HSE user ext. clock<br>(16 MHz)       | 7.0  | 8.0                |      |

|                      | Supply<br>current in                   |                                                             | HSI RC osc. (16 MHz)                  | 7.0  | 8.0                |      |

| I <sub>DD(RUN)</sub> | I <sub>DD(RUN)</sub> Run mode,<br>code | f <sub>CPU</sub> = f <sub>MASTER</sub> = 2 MHz              | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 1.5  | -                  | mA   |

| executed             | executed                               | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 1.35 | 2.0                |      |

|                      | from Flash                             | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 =<br>15.625 kHz | HSI RC osc. (16 MHz/8)                | 0.75 | -                  |      |

|                      |                                        | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.6  | -                  | 1    |

| Table 21. Total current consum | ption with code execution i | n run mode at $V_{DD} = 3.3 V$ |

|--------------------------------|-----------------------------|--------------------------------|

|--------------------------------|-----------------------------|--------------------------------|

1. Data based on characterization results, not tested in production.

2. Default clock configuration measured with all peripherals off.

#### Total current consumption in wait mode

| Table 22. Total current cons | sumption in wait mode at $V_{DD} = 5 V$ |

|------------------------------|-----------------------------------------|

|------------------------------|-----------------------------------------|

| Symbol   | Parameter                                 | Conditions                                                                                                   |                                                       | Тур                  | Max <sup>(1)</sup> | Unit |    |

|----------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------|--------------------|------|----|

|          | Supply<br>DD(WFI) current in<br>wait mode |                                                                                                              | HSE crystal osc. (16 MHz)                             | 2.15                 | -                  |      |    |

|          |                                           | t <sub>CPU</sub> = t <sub>MASTER</sub> = 16 MHz                                                              | HSE user ext. clock<br>(16 MHz)                       | 1.55                 | 2.0                |      |    |

|          |                                           |                                                                                                              | HSI RC osc. (16 MHz)                                  | 1.5                  | 1.9                |      |    |

| IDD(WFI) |                                           | wait mode $\frac{f_{CPU} = f_{MASTER} / 128 = 125 \text{ kHz}}{f_{CPU} = f_{MASTER} / 28 = 125 \text{ kHz}}$ | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz | HSI RC osc. (16 MHz) | 1.3                | -    | mA |

|          |                                           |                                                                                                              | HSI RC osc. (16 MHz/8) <sup>(2)</sup>                 | 0.7                  | -                  |      |    |

|          |                                           | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz                                                             | LSI RC osc. (128 kHz)                                 | 0.5                  | _                  |      |    |

1. Data based on characterization results, not tested in production.

2. Default clock configuration measured with all peripherals off.

|                         |                   |                                                      | Conditions                   |                              |     |                                |                                |      |

|-------------------------|-------------------|------------------------------------------------------|------------------------------|------------------------------|-----|--------------------------------|--------------------------------|------|

| Symbol                  | Parameter         | Main<br>voltage<br>regulator<br>(MVR) <sup>(2)</sup> | Flash mode <sup>(3)</sup>    | Clock source                 | Тур | Max at<br>85 °C <sup>(1)</sup> | Max at<br>85 °C <sup>(1)</sup> | Unit |

|                         |                   | Operating mode                                       | HSE crystal osc.<br>(16 MHz) | 680                          | -   | -                              |                                |      |

|                         |                   | Operating mode                                       | LSI RC osc. (128 kHz)        | 200                          | 320 | 400                            |                                |      |

|                         | Supply current in | On                                                   | Power down<br>mode           | HSE crystal osc.<br>(16 MHz) | 630 | -                              | -                              |      |

| DD(AH) active halt mode |                   | Power down<br>mode                                   | LSI RC osc. (128 kHz)        | 140                          | 270 | 350                            | μA                             |      |

|                         |                   |                                                      | Operating mode               | LSI RC osc. (128 kHz)        | 66  | 120                            | 220                            |      |

|                         |                   | Off                                                  | Power down<br>mode           | LSI RC osc. (128 kHz)        | 10  | 60                             | 150                            |      |

1. Data based on characterization results, not tested in production.

2. Configured by the REGAH bit in the CLK\_ICKR register.

3. Configured by the AHALT bit in the FLASH\_CR1 register.

#### Total current consumption in halt mode

#### Table 26. Total current consumption in halt mode at $V_{DD}$ = 5 V

|                        |                        |                                                     |     | 00                             |                                |      |

|------------------------|------------------------|-----------------------------------------------------|-----|--------------------------------|--------------------------------|------|

| Symbol                 | Parameter              | Conditions                                          | Тур | Max at<br>85 °C <sup>(1)</sup> | Max at<br>85 °C <sup>(1)</sup> | Unit |

|                        | Supply current in halt | Flash in operating mode, HSI clock after wakeup     | 62  | 90                             | 150                            |      |

| <sup>IDD(H)</sup> mode | mode                   | Flash in power-down mode,<br>HSI clock after wakeup | 6.5 | 25                             | 80                             | μA   |

1. Data based on characterization results, not tested in production.

| Table 27. Tota | I current consumption | in halt mode at $V_{DD}$ = 3.3 V |

|----------------|-----------------------|----------------------------------|

|----------------|-----------------------|----------------------------------|

| Symbol             | Parameter                   | Conditions                                          | Тур | Max at<br>85 °C <sup>(1)</sup> | Max at<br>85 °C <sup>(1)</sup> | Unit |  |

|--------------------|-----------------------------|-----------------------------------------------------|-----|--------------------------------|--------------------------------|------|--|

| I <sub>DD(H)</sub> | Supply current in halt mode | Flash in operating mode, HSI clock after wakeup     | 60  | 90                             | 150                            | μA   |  |

|                    |                             | Flash in power-down mode,<br>HSI clock after wakeup | 4.5 | 20                             | 80                             | μΑ   |  |

1. Data based on characterization results, not tested in production.

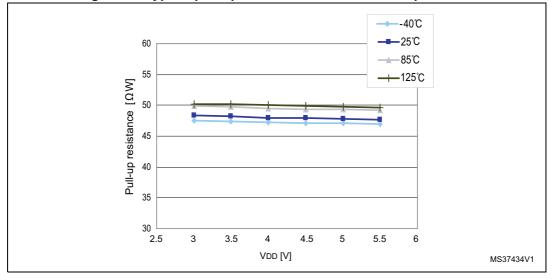

Figure 26. Typical pull-up resistance vs VDD @ 4 temperatures

| Table 38. Output driving current | (standard ports) |

|----------------------------------|------------------|

|----------------------------------|------------------|

| Symbol          | Parameter                                | Conditions                                         | Min                | Мах                | Unit |

|-----------------|------------------------------------------|----------------------------------------------------|--------------------|--------------------|------|

| V <sub>OL</sub> | Output low level with 8<br>pins sunk     | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | -                  | 2.0                |      |

|                 | Output low level with 4 pins sunk        | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | -                  | 1.0 <sup>(1)</sup> | V    |

|                 | Output high level with 8<br>pins sourced | I <sub>IO</sub> = 10 mA,<br>V <sub>DD</sub> = 5 V  | 2.4                | -                  | V    |

| V <sub>OH</sub> | Output high level with 4 pins sourced    | I <sub>IO</sub> = 4 mA,<br>V <sub>DD</sub> = 3.3 V | 2.0 <sup>(1)</sup> | -                  |      |

1. Data based on characterization results, not tested in production

| Symbol                                                                                | Parameter                    | Conditions <sup>(1)</sup>         | Min                      | Мах                      | Unit |

|---------------------------------------------------------------------------------------|------------------------------|-----------------------------------|--------------------------|--------------------------|------|

| t <sub>r(SCK</sub> )<br>t <sub>f(SCK)</sub>                                           | SPI clock rise and fall time | Capacitive load:<br>C = 30 pF     | -                        | 25                       |      |

| t <sub>su(NSS)</sub> <sup>(2)</sup>                                                   | NSS setup time               | Slave mode                        | 4 * t <sub>MASTER</sub>  | -                        |      |

| t <sub>h(NSS)</sub> <sup>(2)</sup>                                                    | NSS hold time                | Slave mode                        | 70                       | -                        |      |

| $ \begin{array}{c} t_{w(SCKH)} ^{(2)} \\ t_{w(SCKL)} ^{(2)} \end{array} \end{array} $ | SCK high and low time        | Master mode                       | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |      |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                                    | Data input setup time        | Master mode                       | 5                        | -                        |      |

| t <sub>su(MI)</sub> (2)<br>t <sub>su(SI)</sub> (2)                                    | Data input setup time        | Slave mode                        | 5                        | -                        |      |

| $t_{h(MI)}^{(2)}$                                                                     | Data input hold time         | Master mode                       | 7                        | -                        |      |

| t <sub>h(MI)</sub> (2)<br>t <sub>h(SI)</sub> (2)                                      |                              | Slave mode                        | 10                       | -                        | ns   |

| t <sub>a(SO)</sub> <sup>(2)(3)</sup>                                                  | Data output access time      | Slave mode                        | -                        | 3* t <sub>MASTER</sub>   |      |

| $t_{dis(SO)}^{(2)(4)}$                                                                | Data output disable time     | Slave mode                        | 25                       | -                        |      |

| t <sub>v(SO)</sub> <sup>(2)</sup>                                                     | Data output valid time       | Slave mode<br>(after enable edge) | -                        | 73                       |      |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                                     | Data output valid time       | Master mode (after enable edge)   | -                        | 36                       |      |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                                     | Data output hold time        | Slave mode (after enable edge)    | 28                       | -                        |      |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                                     | Data output hold time        | Master mode (after enable edge)   | 12                       | -                        |      |

Table 42. SPI characteristics (continued)

1. Parameters are given by selecting 10 MHz I/O output frequency.

2. Values based on design simulation and/or characterization results, and not tested in production.

3. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

4. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

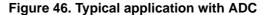

2. ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 10.3.6 does not affect the ADC accuracy.

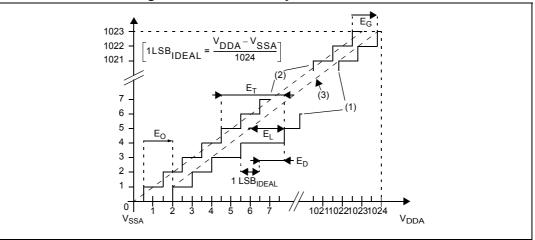

- 1. Example of an actual transfer curve

- 2. The ideal transfer curve

- 3. End point correlation line

E<sub>T</sub> = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.

**E**<sub>0</sub> = Offset error: deviation between the first actual transition and the first ideal one.

$E_G = Gain error: deviation between the last ideal transition and the last actual one.$  $<math>E_D = Differential linearity error: maximum deviation between actual steps and the ideal one.$  $<math>E_L = Integral linearity error: maximum deviation between any actual transition and the end point correlation line.$

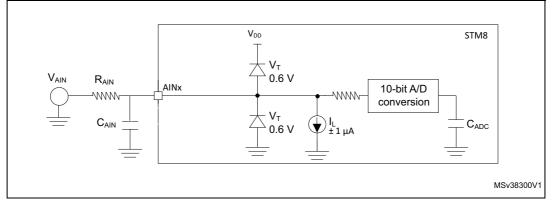

1. Legend: R<sub>AIN</sub> = external resistance, C<sub>AIN</sub> = capacitors, C<sub>samp</sub> = internal sample and hold capacitor.

#### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin), and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------|-----------------------|-------------------------|----------------------|

|        |                       | $T_A = 25 \ ^\circ C$   |                      |

| LU     | Static latch-up class | T <sub>A</sub> = 85 °C  | А                    |

|        |                       | T <sub>A</sub> = 125 °C |                      |

| Table | 50. | Electrical | sensitivities |

|-------|-----|------------|---------------|

|-------|-----|------------|---------------|

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

| Cumhal | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.300       | 0.370 | 0.450 | 0.0118                | 0.0146 | 0.0177 |

| С      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.600 | -     | -                     | 0.2205 | -      |

| E      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -           | 5.600 | -     | -                     | 0.2205 | -      |

| е      | -           | 0.800 | -     | -                     | 0.0315 | -      |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| ССС    | -           | -     | 0.100 | -                     | -      | 0.0039 |

| Table 53. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 54. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

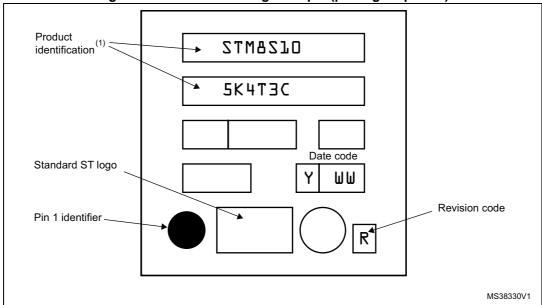

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 55. LQFP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

DocID14771 Rev 15

| Dim. |       | mm    |        |        | inches <sup>(1)</sup> |        |  |

|------|-------|-------|--------|--------|-----------------------|--------|--|

|      | Min   | Тур   | Max    | Min    | Тур                   | Max    |  |

| eB   | -     | -     | 12.700 | -      | -                     | 0.5000 |  |

| L    | 2.540 | 3.048 | 3.810  | 0.1000 | 0.1200                | 0.1500 |  |

#### Table 55. SDIP32 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits

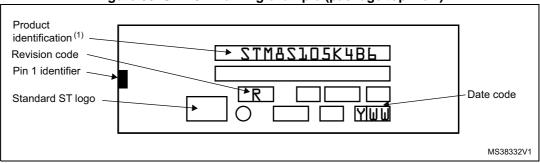

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

#### Figure 60. SDIP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 13.1 STM8S105 FASTROM microcontroller option list

(last update: September 2010)

| Customer                              |  |

|---------------------------------------|--|

| Address                               |  |

| Contact                               |  |

| Phone number                          |  |

| FASTROM code reference <sup>(1)</sup> |  |

1. The FASTROM code name is assigned by STMicroelectronics.

The preferable format for programing code is .Hex (.s19 is accepted)

If data EEPROM programing is required, a separate file must be sent with the requested data.

Note:

See the option byte section in the datasheet for authorized option byte combinations and a detailed explanation.

#### Device type/memory size/package (check only one option)

| FASTROM device | 16 Kbyte     | 32 Kbyte      |

|----------------|--------------|---------------|

| LQFP32         | []STM8S105K4 | [] STM8S105K6 |

| LQFP44         | []STM8S105S4 | [] STM8S105S6 |

| LQFP48         | []STM8S105C4 | [] STM8S105C6 |

#### Conditioning (check only one option)

[] Tape and reel or [] Tray

#### Special marking (check only one option)

[] No [] Yes

Authorized characters are letters, digits, '.', '-', '/' and spaces only. Maximum character counts are:

| LQFP32: 2 lines of 7 characters max: " | " and " | " |

|----------------------------------------|---------|---|

| LQFP44: 2 lines of 7 characters max: " | " and " |   |

| LQFP48: 2 lines of 8 characters max: " | " and " | " |

#### **Temperature range**

[] -40°C to +85°C or [] -40°C to +125°C

# 14 STM8 development tools

Development tools for the STM8 microcontrollers include the full-featured STice emulation system supported by a complete software tool package including C compiler, assembler and integrated development environment with high-level language debugger. In addition, the STM8 is to be supported by a complete range of tools including starter kits, evaluation boards and a low-cost in-circuit debugger/programmer.

### 14.1 Emulation and in-circuit debugging tools

The STice emulation system offers a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8 application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including profiling and coverage to help detect and eliminate bottlenecks in application execution and dead code when fine tuning an application.

In addition, STice offers in-circuit debugging and programming of STM8 microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows you to order exactly what you need to meet your development requirements and to adapt your emulation system to support existing and future ST microcontrollers.

#### 14.1.1 STice key features

- Occurrence and time profiling and code coverage (new features),

- Advanced breakpoints with up to 4 levels of conditions,

- Data breakpoints,

- Program and data trace recording up to 128 KB records,

- Read/write on the fly of memory during emulation,

- In-circuit debugging/programming via SWIM protocol,

- 8-bit probe analyzer,

- 1 input and 2 output triggers,

- Power supply follower managing application voltages between 1.62 to 5.5 V,

- Modularity that allows you to specify the components you need to meet your development requirements and adapt to future requirements.

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

# 15 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                       |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Jun-2018 | 1        | Initial release.                                                                                                                                                                                                                                                                              |

| 23-Jun-2018 | 2        | Corrected the number of high sink outputs to 9 in I/Os in <i>Features</i> .<br>Updated part numbers in <i>STM8S105xx access line features</i> .                                                                                                                                               |

| 12-Aug-2008 | 3        | Updated the part numbers in <i>STM8S105xx access line features</i> .<br>USART renamed UART1, LINUART renamed UART2.<br>Added <i>Table: Pin-to-pin comparison of pin 7 to 12 in 32-pin access line devices</i> .                                                                               |

| 17-Sep-2008 | 4        | Removed STM8S102xx and STM8S104xx root part<br>numbers corresponding to devices without data<br>EEPROM.<br>Updated STM8S103 pinout section<br>Added low and medium density Flash memory<br>categories.<br>Added Note 1 in Section: Current characteristics.<br>Updated Section: Option bytes. |

| 05-Feb-2009 | 5        | Updated STM8S103 pinout.<br>Updated number of High Sink I/Os in the pinout section.<br>TSSOP20 pinout modified (PD4 moved to pin 1 etc.)<br>Added WFQFN20 package<br>Updated Section: Option bytes.<br>Added Section: Memory and register map.                                                |

| 27-Feb-2009 | 6        | Removed STM8S103x products (separate STM8S103<br>datasheet created).<br>Updated Section: Electrical characteristics.                                                                                                                                                                          |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-May-2009 | 7        | Added SDIP32 silhouette and package to <i>Features</i> and<br><i>Section: SDIP32 package mechanical data</i> ; updated<br><i>Section: Pinout and pin description.</i><br>Updated VDD range (2.95 V to 5.5 V) on Features.<br>Amended name of package VQFPN32.<br>Added Table 5 on page 22.<br>Updated <i>Section: Auto wakeup counter.</i><br>Updated pins 25, 30, and 31 in <i>Section: Pinout and pin<br/>description.</i><br>Removed Table 7: Pin-to-pin comparison of pin 7 to 12<br>in 32-pin access line devices.<br>Added <i>Table: Description of alternate function</i><br><i>remapping bits</i> [7:0] of OPT2.<br><i>Section: Electrical characteristics:</i> Updated VCAP<br>specifications; updated Table 15, Table 18, Table 20,<br>Table 21, Table 22, Table 23, Table 24, Table 25, Table<br>26, Table 27, Table 29, Table 35, and Table 42; added<br>current consumption curves; removed Figure 20: typical<br>HSE frequency vs fcpu @ 4 temperatures; updated<br>Figure 13, Figure 14, Figure 15, Figure 16 and Figure<br>17; modified HSI accuracy in Table 33; added Figure<br>44; modified f <sub>SCK</sub> , t <sub>V(SO)</sub> and t <sub>V(MO)</sub> in Table 42; updated<br>figures and tables of High speed internal RC oscillator<br>(HSI); replaced Figure 23, Figure 24, Figure 26, and<br>Figure 39.<br><i>Section Package information:</i> updated <i>Section: Thermal<br/>characteristics</i> and removed Table 57: Junction<br>temperature range. Updated <i>Section: STM8S105xx</i><br>access line ordering information scheme. |

| 10-Jun-2009 | 8        | Document status changed from "preliminary data" to<br>"datasheet".<br>Standardized the name of the VFQFPN package.<br>Removed 'wpu' from I2C pins Section: Pinout and pin<br>description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Sep-2010 | 10       | Table: Legend/Abbreviations for pinout tables: updated"reset state"; removed "HS", (T), and "[]".Section: Pin description for STM8S105 microcontrollers:added footnotes to the PF4 and PD1 pins.Table: I/O port hardware register map: changed resetstatus of Px_IDR from 0x00 to 0xXX.Table: General hardware register map: Standardized alladdress and reset state values; updated the reset statevalues of the RST_SR, CLK_SWCR, CLK_HSITRIMR,CLK_SWIMCCR, IWDG_KR, UART2_DR, andADC_DRx registers; replaced reserved address "0x005248" with the UART2_CR5.Section: Recommended reset pin protection: replaced0.01 µF with 0.1 µFUpdated Figure: Typical application with I2C bus andtiming diagram.Updated Table: ADC accuracy with RAIN < 10 kohm ,                                              |

| 04-Apr-2012 | 11       | Removed VFQFPN32 package.<br>Modified Section: Description.<br>Remove weak pull-up input for PE1 and PE2 in Table:<br>Pin description for STM8S105 microcontrollers<br>Updated Table: Interrupt mapping for TIM2 and TIM4.<br>Updated notes related to VCAP in xm-replace_text<br>General operating conditions.<br>Added values of $t_R/t_F$ for 50 pF load capacitance, and<br>updated note in Section: I/O static characteristics.<br>Updated typical and maximum values of RPU in Table:<br>I/O static characteristics and Table: RST pin<br>characteristics.<br>Changed SCK input to SCK output in Table: SPI serial<br>peripheral interface.<br>Added $\Theta_{JA}$ for UFQFPN32 and SDIP32 in Table:<br>Thermal characteristics, and updated Section: Selecting<br>the product temperature range |

| 28-Jun-2012 | 12       | Added UFQFPN package thickness in <i>Figure:</i><br><i>STM8S105xx</i> access line ordering information scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 57. Document revision history (continued)