Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 16MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                          |

| Data Converters            | A/D 9x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s105s6t6c |

|                            |                                                                       |

List of tables STM8S105x4/6

| Table 49. | ESD absolute maximum ratings                                            | 89  |

|-----------|-------------------------------------------------------------------------|-----|

| Table 50. | Electrical sensitivities                                                | 90  |

| Table 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                 |     |

|           | mechanical data                                                         | 92  |

| Table 52. | LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat package               |     |

|           | mechanical data                                                         | 95  |

| Table 53. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package                 |     |

|           | mechanical data                                                         | 99  |

| Table 54. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |     |

|           | package mechanical data                                                 | 102 |

| Table 55. | SDIP32 package mechanical data                                          | 104 |

| Table 56. | Thermal characteristics                                                 | 106 |

| Table 57  | Document revision history                                               | 116 |

STM8S105x4/6 List of figures

# List of figures

| Figure 1.  | STM8S105x4/6 block diagram                                                                 |    |

|------------|--------------------------------------------------------------------------------------------|----|

| Figure 2.  | Flash memory organization                                                                  |    |

| Figure 3.  | LQFP48 pinout                                                                              | 23 |

| Figure 4.  | LQFP44 pinout                                                                              | 24 |

| Figure 5.  | UFQFPN32/LQFP32 pinout                                                                     | 25 |

| Figure 6.  | SDIP32 pinout                                                                              |    |

| Figure 7.  | Memory map                                                                                 |    |

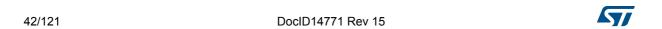

| Figure 8.  | Supply current measurement conditions                                                      |    |

| Figure 9.  | Pin loading conditions                                                                     |    |

| Figure 10. | Pin input voltage                                                                          |    |

| -          | f <sub>CPUmax</sub> versus V <sub>DD</sub>                                                 |    |

| Figure 11. |                                                                                            |    |

| Figure 12. | External capacitor C <sub>EXT</sub>                                                        | 00 |

| Figure 13. | Typ $I_{DD(RUN)}$ vs. $V_{DD}$ HSE user external clock, $f_{CPU}$ = 16 MHz                 | 62 |

| Figure 14. | Typ $I_{DD(RUN)}$ vs. $f_{CPU}$ HSE user external clock, $V_{DD}$ = 5 V                    | 63 |

| Figure 15. | Typ $I_{DD(RUN)}$ vs. $V_{DD}$ HSI RC osc, $f_{CPU}$ = 16 MHz                              | 63 |

| Figure 16. | Typ I <sub>DD(WFI)</sub> vs. V <sub>DD</sub> HSE external clock, f <sub>CPU</sub> = 16 MHz | 64 |

| Figure 17. | Typ $I_{DD(WFI)}$ vs. $f_{CPU}$ HSE external clock, $V_{DD}$ = 5 V                         | 64 |

| Figure 18. | Typ I <sub>DD(WFI)</sub> vs. V <sub>DD</sub> HSI RC osc., f <sub>CPU</sub> = 16 MHz        | 65 |

| Figure 19. | HSE external clock source                                                                  | 66 |

| Figure 20. | HSE oscillator circuit diagram                                                             | 68 |

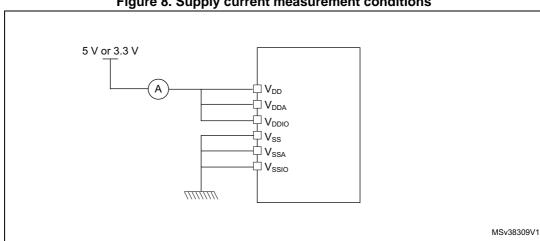

| Figure 21. | Typical HSI accuracy @ V <sub>DD</sub> = 5 V vs 5 temperatures                             | 69 |

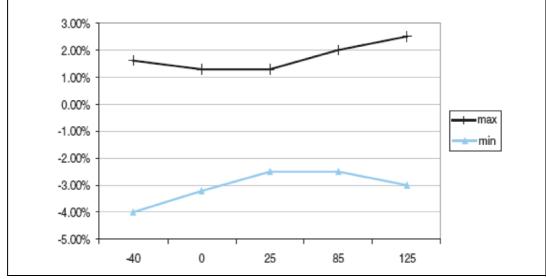

| Figure 22. | Typical HSI frequency variation vs V <sub>DD</sub> @ 4 temperatures                        |    |

| Figure 23. | Typical LSI frequency variation vs V <sub>DD</sub> @ 4 temperatures                        |    |

| Figure 24. | Typical V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ 4 temperatures            |    |

| Figure 25. | Typical pull-up current vs V <sub>DD</sub> @ 4 temperatures                                |    |

| Figure 26. | Typical pull-up resistance vs VDD @ 4 temperatures                                         |    |

| Figure 27. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 3.3 V (standard ports)                            |    |

| Figure 28. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 5.0 V (standard ports)                            |    |

| Figure 29. | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (true open drain ports)                                   |    |

| Figure 30. | Typ. $V_{OL}$ @ $V_{DD}$ = 5.0 V (true open drain ports)                                   |    |

| Figure 31. | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (high sink ports)                                         |    |

| Figure 31. | Typ. $V_{OL}$ @ $V_{DD}$ = 5.0 V (high sink ports)                                         |    |

| -          |                                                                                            |    |

| Figure 33. | Typ. $V_{DD} - V_{OH} @ V_{DD} = 3.3 \text{ V (standard ports)}$                           |    |

| Figure 34. | Typ. $V_{DD} - V_{OH} @ V_{DD} = 5.0 \text{ V (standard ports)}$                           |    |

| Figure 35. | Typ. $V_{DD} - V_{OH} @ V_{DD} = 3.3 \text{ V (high sink ports)}$                          |    |

| Figure 36. | Typ. $V_{DD} - V_{OH} @ V_{DD} = 5.0 \text{ V (high sink ports)}$                          |    |

| Figure 37. | Typical NRST V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ 4 temperatures       | 78 |

| Figure 38. | Typical NRST pull-up resistance R <sub>PU</sub> vs V <sub>DD</sub> @ 4 temperatures        | 79 |

| Figure 39. | Typical NRST pull-up current $I_{pu}$ vs $V_{DD}$ @ 4 temperatures                         | 79 |

| Figure 40. | Recommended reset pin protection                                                           |    |

| Figure 41. | SPI timing diagram where slave mode and CPHA = 0                                           |    |

| Figure 42. | SPI timing diagram where slave mode and CPHA = 1                                           |    |

| Figure 43. | SPI timing diagram - master mode                                                           |    |

| Figure 44. | Typical application with I <sup>2</sup> C bus and timing diagram                           |    |

| Figure 45. | ADC accuracy characteristics                                                               |    |

| Figure 46. | Typical application with ADC                                                               |    |

| Figure 47. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                            | 91 |

| Figure 48. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                                    |    |

Description STM8S105x4/6

# 2 Description

The STM8S105x4/6 access line 8-bit microcontrollers offer from 16 to 32 Kbyte Flash program memory, plus integrated true data EEPROM. The STM8S microcontroller family reference manual (RM0016) refers to devices in this family as medium-density. All devices of the STM8S105x4/6 access line provide the following benefits: reduced system cost, performance and robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, watchdog and brown-out reset.

Device performance is ensured by a 16 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across common family product architecture with compatible pinout, memory map and modular peripherals.

Product longevity is ensured in the STM8S family thanks to their advanced core which is made in a state-of-the-art technology for applications with 2.95 V to 5.5 V operating supply.

Full documentation is offered as well as a wide choice of development tools.

Table 8. General hardware register map (continued)

| Address                | Block        | Register label | Register name                          | Reset status |

|------------------------|--------------|----------------|----------------------------------------|--------------|

| 0x00 5300              |              | TIM2_CR1       | TIM2 control register 1                | 0x00         |

| 0x00 5301              |              | TIM2_IER       | TIM2 Interrupt enable register         | 0x00         |

| 0x00 5302              |              | TIM2_SR1       | TIM2 status register 1                 | 0x00         |

| 0x00 5303              | 1            | TIM2_SR2       | TIM2 status register 2                 | 0x00         |

| 0x00 5304              |              | TIM2_EGR       | TIM2 event generation register         | 0x00         |

| 0x00 5305              |              | TIM2_CCMR1     | TIM2 capture/compare mode register 1   | 0x00         |

| 0x00 5306              |              | TIM2_CCMR2     | TIM2 capture/compare mode register 2   | 0x00         |

| 0x00 5307              |              | TIM2_CCMR3     | TIM2 capture/compare mode register 3   | 0x00         |

| 0x00 5308              |              | TIM2_CCER1     | TIM2 capture/compare enable register 1 | 0x00         |

| 0x00 5309              |              | TIM2_CCER2     | TIM2 capture/compare enable register 2 | 0x00         |

| 0x00 530A              |              | TIM2_CNTRH     | TIM2 counter high                      | 0x00         |

| 0x00 530B              | TIM2         | TIM2_CNTRL     | TIM2 counter low                       | 0x00         |

| 0x00 530C              |              | TIM2_PSCR      | IM2 prescaler register                 | 0x00         |

| 0x00 530D              |              | TIM2_ARRH      | TIM2 auto-reload register high         | 0xFF         |

| 0x00 530E              |              | TIM2_ARRL      | TIM2 auto-reload register low          | 0xFF         |

| 0x00 530F              |              | TIM2_CCR1H     | TIM2 capture/compare register 1 high   | 0x00         |

| 0x00 5310              |              | TIM2_CCR1L     | TIM2 capture/compare register 1 low    | 0x00         |

| 0x00 5311              |              | TIM2_CCR2H     | TIM2 capture/compare reg. 2 high       | 0x00         |

| 0x00 5312              |              | TIM2_CCR2L     | TIM2 capture/compare register 2 low    | 0x00         |

| 0x00 5313              |              | TIM2_CCR3H     | TIM2 capture/compare register 3 high   | 0x00         |

| 0x00 5314              |              | TIM2_CCR3L     | TIM2 capture/compare register 3 low    | 0x00         |

| 0x00 5315 to 0x00 531F | Reserved are | ea (11 byte)   |                                        |              |

# 6.2.3 CPU/SWIM/debug module/interrupt controller registers

Table 9. CPU/SWIM/debug module/interrupt controller registers

| Address                | Block              | Block Register label Register name         |                                        | Reset<br>status |

|------------------------|--------------------|--------------------------------------------|----------------------------------------|-----------------|

| 0x00 7F00              |                    | А                                          | Accumulator                            | 0x00            |

| 0x00 7F01              |                    | PCE                                        | Program counter extended               | 0x00            |

| 0x00 7F02              |                    | PCH                                        | Program counter high                   | 0x00            |

| 0x00 7F03              |                    | PCL                                        | Program counter low                    | 0x00            |

| 0x00 7F04              |                    | XH                                         | X index register high                  | 0x00            |

| 0x00 7F05              | CPU <sup>(1)</sup> | XL                                         | X index register low                   | 0x00            |

| 0x00 7F06              |                    | YH                                         | Y index register high                  | 0x00            |

| 0x00 7F07              |                    | YL                                         | Y index register low                   | 0x00            |

| 0x00 7F08              |                    | SPH                                        | Stack pointer high                     | 0x03            |

| 0x00 7F09              |                    | SPL                                        | Stack pointer low                      | 0xFF            |

| 0x00 7F0A              |                    | CCR                                        | Condition code register                | 0x28            |

| 0x00 7F0B to 0x00 7F5F | Reserved area      | (85 byte)                                  |                                        | 1               |

| 0x00 7F60              | CPU                | CFG_GCR                                    | Global configuration register          | 0x00            |

| 0x00 7F70              |                    | ITC_SPR1                                   | Interrupt software priority register 1 | 0xFF            |

| 0x00 7F71              |                    | ITC_SPR2                                   | Interrupt software priority register 2 | 0xFF            |

| 0x00 7F72              |                    | ITC_SPR3                                   | Interrupt software priority register 3 | 0xFF            |

| 0x00 7F73              | ITC                | ITC_SPR4                                   | Interrupt software priority register 4 | 0xFF            |

| 0x00 7F74              | ITC                | ITC_SPR5                                   | Interrupt software priority register 5 | 0xFF            |

| 0x00 7F75              |                    | ITC_SPR6                                   | Interrupt software priority register 6 | 0xFF            |

| 0x00 7F76              |                    | ITC_SPR7                                   | Interrupt software priority register 7 | 0xFF            |

| 0x00 7F77              |                    | ITC_SPR8                                   | Interrupt software priority register 8 | 0xFF            |

| 0x00 7F78 to 0x00 7F79 | Reserved area      | (2 byte)                                   | •                                      |                 |

| 0x00 7F80              | SWIM               | SWIM_CSR SWIM control status register 0x00 |                                        | 0x00            |

| 0x00 7F81 to 0x00 7F8F | Reserved area      | (15 byte)                                  | •                                      | 1               |

Unique ID STM8S105x4/6

# 9 Unique ID

The devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single byte and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while

using and combining this unique ID with software cryptographic primitives and

protocols before programming the internal memory.

- To activate secure boot processes

Table 14. Unique ID registers (96 bits)

| Address | Content description | Unique ID bits |             |   |       |        |   |   |   |

|---------|---------------------|----------------|-------------|---|-------|--------|---|---|---|

|         |                     | 7              | 6           | 5 | 4     | 3      | 2 | 1 | 0 |

| 0x48CD  | X co-ordinate on    |                |             |   | U_ID  | [7:0]  |   |   |   |

| 0x48CE  | the wafer           |                |             |   | U_ID  | [15:8] |   |   |   |

| 0x48CF  | Y co-ordinate on    |                |             |   | U_ID[ | 23:16] |   |   |   |

| 0x48D0  | the wafer           |                | U_ID[31:24] |   |       |        |   |   |   |

| 0x48D1  | Wafer number        |                |             |   | U_ID[ | 39:32] |   |   |   |

| 0x48D2  |                     |                |             |   | U_ID[ | 47:40] |   |   |   |

| 0x48D3  | U_ID[55:48]         |                |             |   |       |        |   |   |   |

| 0x48D4  |                     |                |             |   | U_ID[ | 63:56] |   |   |   |

| 0x48D5  | Lot number          |                |             |   | U_ID[ | 71:64] |   |   |   |

| 0x48D6  |                     | U_ID[79:72]    |             |   |       |        |   |   |   |

| 0x48D7  |                     | U_ID[87:80]    |             |   |       |        |   |   |   |

| 0x48D8  |                     |                |             |   | U_ID[ | 95:88] |   |   |   |

#### **Electrical characteristics** 10

#### 10.1 **Parameter conditions**

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 10.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A$  = 25 °C, and  $T_A$  =  $T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm$  3  $\Sigma$ ).

#### 10.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  = 5.0 V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm$  2  $\Sigma$ ).

#### 10.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 10.1.4 Typical current consumption

For typical current consumption measurements, VDD, VDDIO and VDDA are connected together in the configuration shown in the following figure.

Figure 8. Supply current measurement conditions

# 10.3.4 Internal clock sources and timing characteristics

Subject to general operating conditions for  $V_{DD}$  and  $T_{A}$ .

# High speed internal RC oscillator (HSI)

Table 33. HSI oscillator characteristics

| Symbol               | Parameter                                        | Conditions                                                                                                                 | Min                 | Тур | Max                | Unit |  |

|----------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------|-----|--------------------|------|--|

| f <sub>HSI</sub>     | Frequency                                        | -                                                                                                                          | -                   | 16  | -                  | MHz  |  |

| ACC <sub>HS</sub>    | Accuracy of HSI oscillator                       | User-trimmed with CLK_HSITRIMR register for given V <sub>DD</sub> and T <sub>A</sub> conditions <sup>(1)</sup>             | -                   | -   | 1 <sup>(2)</sup>   |      |  |

|                      |                                                  | $V_{DD} = 5 \text{ V},$<br>$T_A = 25 \text{ °C}^{(3)}$                                                                     | -1.0                | -   | 1.0                | %    |  |

|                      | HSI oscillator accuracy (factory calibrated)     | $V_{DD}$ = 5 V,<br>-25°C ≤ $T_{A}$ ≤ 85 °C                                                                                 | -2.0                | -   | 2.0                |      |  |

|                      |                                                  | $2.95 \text{ V} \le \text{ V}_{DD} \le 5.5 \text{ V},$<br>$-40^{\circ}\text{C} \le \text{ T}_{A} \le 125 ^{\circ}\text{C}$ | -3.0 <sup>(3)</sup> | -   | 3.0 <sup>(3)</sup> |      |  |

| t <sub>su(HSI)</sub> | HSI oscillator wakeup time including calibration | -                                                                                                                          | -                   | -   | 1.0 <sup>(2)</sup> | μs   |  |

| I <sub>DD(HSI)</sub> | HSI oscillator power consumption                 | -                                                                                                                          | -                   | 170 | 250 <sup>(3)</sup> | μΑ   |  |

- 1. Refer to application note.

- 2. Guaranteed by design, not tested in production.

- 3. Data based on characterization results, not tested in production.

Figure 21. Typical HSI accuracy @ V<sub>DD</sub> = 5 V vs 5 temperatures

# Low speed internal RC oscillator (LSI)

Subject to general operating conditions for  $V_{DD}$  and  $T_{A}. \\$

Table 34. LSI oscillator characteristics

| Symbol               | Parameter                        | Conditions | Min | Тур | Max              | Unit |

|----------------------|----------------------------------|------------|-----|-----|------------------|------|

| f <sub>LSI</sub>     | Frequency                        | -          | 110 | 128 | 150              | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time       | -          | -   | -   | 7 <sup>(1)</sup> | μs   |

| IDD(LSI)             | LSI oscillator power consumption | -          | -   | 5   | -                | μΑ   |

<sup>1.</sup> Guaranteed by design, not tested in production.

Figure 23. Typical LSI frequency variation vs  $V_{DD}$ @ 4 temperatures

Electrical characteristics STM8S105x4/6

#### 10.3.12 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709 (EMC design guide for STM microcontrollers).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring. See application note AN1015 (Software techniques for improving microcontroller EMC performance).

Table 47. EMS data

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                                                   | Level/class        |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD}$ = 5 V, $T_A$ = 25 °C,<br>$f_{MASTER}$ = 16 MHz (HSI clock),<br>Conforms to IEC 1000-4-2                             | 2/B <sup>(1)</sup> |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{DD} = 5 \text{ V}, T_A = 25 ^{\circ}\text{C},$<br>$f_{MASTER} = 16 \text{ MHz (HSI clock)},$<br>Conforms to IEC 1000-4-4 | 4/A <sup>(1)</sup> |

Data obtained with HSI clock configuration, after applying the hardware recommendations described in AN2860 (EMC guidelines for STM8S microcontrollers).

### **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm IEC 61967-2 which specifies the board and the loading of each pin.

**Conditions** Max f<sub>HSE</sub>/f<sub>CPU</sub><sup>(1)</sup> **Symbol Parameter** Unit Monitored **General conditions** frequency band 8 MHz/ 8 MHz/ 8 MHz 16 MHz 0.1 MHz to 30 MHz 13 14  $V_{DD} = 5 V$ ,  $T_A = 25 \, ^{\circ}C$ Peak level 30 MHz to 130 MHz dBuV 23 19  $S_{\text{EMI}}$ LQFP48 package. 130 MHz to 1 GHz -4.0 -4.0 Conforming to IEC 61967-2 EMI level 2.0 EMI level 1.5

Table 48. EMI data

### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD, DLU and LU) using specific measurement methods, the product is stressed to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts x (n+1) supply pin). One model can be simulated: Human body model. This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

Table 49. ESD absolute maximum ratings

| Symbol                | Ratings                                               | Conditions                                          | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-----------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (Human body model)    | T <sub>A</sub> = 25°C, conforming to<br>JESD22-A114 | Α     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to SD22-C101      | IV    | 1000                            | V    |

<sup>1.</sup> Data based on characterization results, not tested in production

<sup>1.</sup> Data based on characterization results, not tested in production.

Electrical characteristics STM8S105x4/6

### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance.

- A supply overvoltage (applied to each power supply pin), and

- A current injection (applied to each input, output and configurable I/O pin) are performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

Table 50. Electrical sensitivities

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

Package information STM8S105x4/6

Table 51. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol | Min   | Тур         | Max   | Min                   | Тур    | Max    |  |

| Α      | -     | -           | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -     | 5.500       | -     | -                     | 0.2165 | -      |  |

| E      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| E3     | -     | 5.500       | -     | -                     | 0.2165 | -      |  |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |  |

| k      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |  |

| ccc    | -     | -           | 0.080 | -                     | -      | 0.0031 |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

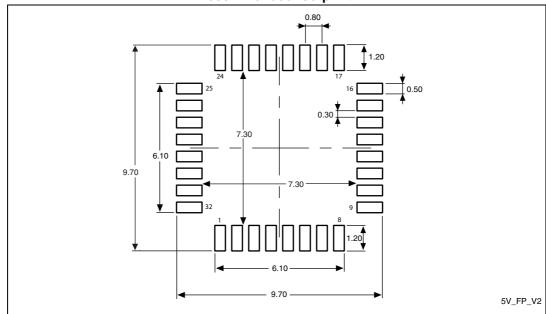

Table 53. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol | Min   | Тур         | Max   | Min                   | Тур    | Max    |  |

| А      | -     | -           | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.300 | 0.370       | 0.450 | 0.0118                | 0.0146 | 0.0177 |  |

| С      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -     | 5.600       | -     | -                     | 0.2205 | -      |  |

| Е      | 8.800 | 9.000       | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| E3     | -     | 5.600       | -     | -                     | 0.2205 | -      |  |

| е      | -     | 0.800       | -     | -                     | 0.0315 | -      |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |  |

| k      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |  |

| ccc    | -     | -           | 0.100 | -                     | -      | 0.0039 |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Package information STM8S105x4/6

Figure 54. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

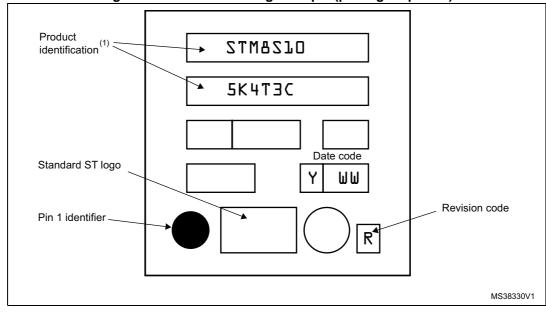

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 55. LQFP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

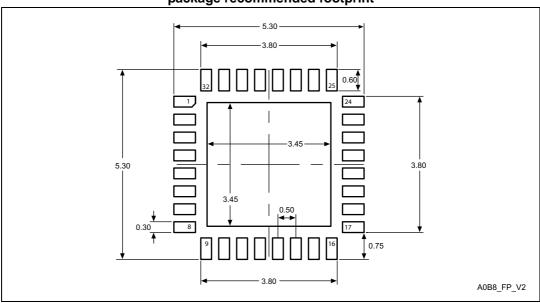

Package information STM8S105x4/6

Table 54. UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat package mechanical data

| paolago moonamoa aaa |             |       |       |                       |        |        |

|----------------------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol               | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|                      | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| Α                    | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1                   | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| A3                   | -           | 0.152 | -     | -                     | 0.0060 | -      |

| b                    | 0.180       | 0.230 | 0.280 | 0.0071                | 0.0091 | 0.0110 |

| D                    | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |

| D1                   | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |

| D2                   | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |

| E                    | 4.900       | 5.000 | 5.100 | 0.1929                | 0.1969 | 0.2008 |

| E1                   | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |

| E2                   | 3.400       | 3.500 | 3.600 | 0.1339                | 0.1378 | 0.1417 |

| е                    | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L                    | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| ddd                  | -           | -     | 0.080 | -                     | -      | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 57. UFQFPN32 - 32-pin, 5 x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat package recommended footprint

<sup>1.</sup> Dimensions are expressed in millimeters.

Table 55. SDIP32 package mechanical data (continued)

| Dim. | mm    |       |        | inches <sup>(1)</sup> |        |        |

|------|-------|-------|--------|-----------------------|--------|--------|

|      | Min   | Тур   | Max    | Min                   | Тур    | Max    |

| eB   | -     | -     | 12.700 | -                     | -      | 0.5000 |

| L    | 2.540 | 3.048 | 3.810  | 0.1000                | 0.1200 | 0.1500 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits

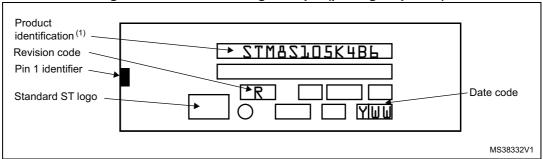

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 60. SDIP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet

qualified and therefore not yet ready to be used in production and any consequences deriving from such

usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering

samples in production. ST Quality has to be contacted prior to any decision to use these Engineering

samples to run qualification activity.

Thermal characteristics STM8S105x4/6

## 12 Thermal characteristics

The maximum junction temperature ( $T_{Jmax}$ ) of the device must never exceed the values specified in *Table 18: General operating conditions*, otherwise the functionality of the device cannot be guaranteed.

The maximum junction temperature  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$$

#### Where:

- T<sub>Amax</sub> is the maximum ambient temperature in °C

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance in ° C/W

- $P_{Dmax}$  is the sum of  $P_{INTmax}$  and  $P_{I/Omax}$  ( $P_{Dmax} = P_{INTmax} + P_{I/Omax}$ )

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum power dissipation on output pins Where:

$P_{I/Omax} = \Sigma \left( V_{OL} * I_{OL} \right) + \Sigma ((V_{DD} - V_{OH}) * I_{OH}),$  taking into account the actual  $V_{OL} / I_{OL}$  and  $V_{OH} / I_{OH}$  of the I/Os at low and high level in the application.

| Symbol            | Parameter                                             | Value | Unit |

|-------------------|-------------------------------------------------------|-------|------|

|                   | Thermal resistance junction-ambient LQFP48 - 7x7 mm   |       |      |

|                   | Thermal resistance junction-ambient LQFP44 - 10x10 mm |       |      |

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient LQFP32 - 7x7 mm   |       | °C/W |

|                   | Thermal resistance junction-ambient UFQFPN32 - 5x5 mm |       |      |

|                   | Thermal resistance junction-ambient                   |       |      |

Table 56. Thermal characteristics<sup>(1)</sup>

SDIP32 - 400 ml

#### 12.1 Reference document

JESD51-2 integrated circuits thermal test method environment conditions - natural convection (still air). Available from www.jedec.org.

Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

Ordering information STM8S105x4/6

OPT5 crystal oscillator stabilization HSECNT (check only one option)

| [] 2048 HSE cycles                                                |  |  |  |  |

|-------------------------------------------------------------------|--|--|--|--|

| [] 128 HSE cycles                                                 |  |  |  |  |

| []8 HSE cycles                                                    |  |  |  |  |

| [] 0.5 HSE cycles                                                 |  |  |  |  |

| OTP6 is reserved                                                  |  |  |  |  |

| OTP7 is reserved                                                  |  |  |  |  |

| OTPBL bootloader option byte (check only one option)              |  |  |  |  |

| Refer to the UM0560 (STM8L/S bootloader manual) for more details. |  |  |  |  |

| [ ] Disable (00h)                                                 |  |  |  |  |

| [] Enable (55h)                                                   |  |  |  |  |

|                                                                   |  |  |  |  |

| Comments:                                                         |  |  |  |  |

| Supply operating range in the application:                        |  |  |  |  |

| Notes:                                                            |  |  |  |  |

| Date:                                                             |  |  |  |  |

| Signature:                                                        |  |  |  |  |

### 14.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST Visual Develop (STVD) IDE and the ST Visual Programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8, which are available in a free version that outputs up to 16 Kbytes of code.

#### 14.2.1 STM8 toolset

The STM8 toolset with STVD integrated development environment and STVP programming software is available for free download at <a href="https://www.st.com">www.st.com</a>. This package includes:

### ST visual develop

Full-featured integrated development environment from STMicroelectronics, featuring:

- · Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

#### ST visual programmer (STVP)

Easy-to-use, unlimited graphical interface allowing read, write and verification of the STM8 Flash program memory, data EEPROM and option bytes. STVP also offers project mode for the saving of programming configurations and the automation of programming sequences.

### 14.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of user applications directly from an easy-to-use graphical interface.

Available toolchains include:

#### C compiler for STM8

Available in a free version that outputs up to 16 Kbytes of code. For more information, see www.cosmic-software.com.

#### STM8 assembler linker

Free assembly toolchain included in the STVD toolset, used to assemble and link the user application source code.