# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Not For New Designs                                                   |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 400MHz                                                                |

| Co-Processors/DSP               | -                                                                     |

| RAM Controllers                 | DDR, SDRAM                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100Mbps (1)                                                        |

| SATA                            | -                                                                     |

| USB                             | USB 1.1 (2)                                                           |

| Voltage - I/O                   | 2.5V, 3.3V                                                            |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                       |

| Security Features               | -                                                                     |

| Package / Case                  | 272-BBGA                                                              |

| Supplier Device Package         | 272-PBGA (27x27)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc5200vr400b |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1.2.1** System Oscillator Electrical Characteristics

Table 8. System Oscillator Electrical Characteristics

| Characteristic           | Sym                   | Notes | Min  | Typical | Max  | Unit | SpecID |

|--------------------------|-----------------------|-------|------|---------|------|------|--------|

| SYS_XTAL frequency       | f <sub>sys_xtal</sub> |       | 15.6 | 33.3    | 35.0 | MHz  | O1.1   |

| Oscillator start-up time | t <sub>up_osc</sub>   |       |      | —       | 10   | ms   | 01.2   |

# **1.2.2 RTC Oscillator Electrical Characteristics**

**Table 9. RTC Oscillator Electrical Characteristics**

| Characteristic     | Sym                   | Notes | Min | Typical | Max | Unit | SpecID |

|--------------------|-----------------------|-------|-----|---------|-----|------|--------|

| RTC_XTAL frequency | f <sub>rtc_xtal</sub> |       |     | 32.768  |     | kHz  | O2.1   |

### **1.2.3** System PLL Electrical Characteristics

| Characteristic              | Sym                   | Notes | Min  | Typical | Max  | Unit | SpecID |

|-----------------------------|-----------------------|-------|------|---------|------|------|--------|

| SYS_XTAL frequency          | f <sub>sys_xtal</sub> | (1)   | 15.6 | 33.3    | 35.0 | MHz  | O3.1   |

| SYS_XTAL cycle time         | t <sub>sys_xtal</sub> | (1)   | 66.6 | 30.0    | 28.5 | ns   | O3.2   |

| SYS_XTAL clock input jitter | t <sub>jitter</sub>   | (2)   | —    | —       | 150  | ps   | O3.3   |

| System VCO frequency        | f <sub>VCOsys</sub>   | (1)   | 250  | 533     | 800  | MHz  | O3.4   |

| System PLL relock time      | t <sub>lock</sub>     | (3)   | —    | —       | 100  | μS   | O3.5   |

<sup>1</sup> The SYS\_XTAL frequency and PLL Configuration bits must be chosen such that the resulting system frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies.

<sup>2</sup> This represents total input jitter—short term and long term combined—and is guaranteed by design. Two different types of jitter can exist on the input to CORE\_SYSCLK, systemic and true random jitter. True random jitter is rejected. Systemic jitter is passed into and through the PLL to the internal clock circuitry.

<sup>3</sup> Relock time is guaranteed by design and characterization. PLL-relock time is the maximum amount of time required for the PLL lock after a stable VDD and CORE\_SYSCLKare reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep modes.

# 1.2.4 e300 Core PLL Electrical Characteristics

The internal clocking of the e300 core is generated from and synchronized to the system clock by means of a voltage-controlled core PLL.

- Input conditions: All Inputs: tr, tf <= 1 ns

- Output Loading: All Outputs: 50 pF

# 1.3.2 AC Operating Frequency Data

Table 12 provides the operating frequency information for the MPC5200B.

#### **Table 12. Clock Frequencies**

|   |                            | Min  | Max | Units | SpecID |

|---|----------------------------|------|-----|-------|--------|

| 1 | e300 Processor Core        | —    | 400 | MHz   | A1.1   |

| 2 | SDRAM Clock                | _    | 133 | MHz   | A1.2   |

| 3 | XL Bus Clock               | —    | 133 | MHz   | A1.3   |

| 4 | IP Bus Clock               | —    | 133 | MHz   | A1.4   |

| 5 | PCI / Local Plus Bus Clock | —    | 66  | MHz   | A1.5   |

| 6 | PLL Input Range            | 15.6 | 35  | MHz   | A1.6   |

### 1.3.3 Clock AC Specifications

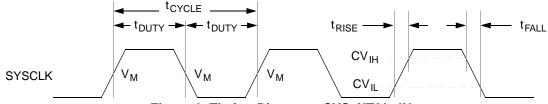

Figure 2. Timing Diagram—SYS\_XTAL\_IN

#### Table 13. SYS\_XTAL\_IN Timing

| Sym                | Description                                                       |            | Max  | Units       | SpecID |

|--------------------|-------------------------------------------------------------------|------------|------|-------------|--------|

| t <sub>CYCLE</sub> | SYS_XTAL_IN cycle time. <sup>(1)</sup>                            |            | 64.1 | ns          | A2.1   |

| t <sub>RISE</sub>  | SYS_XTAL_IN rise time.                                            | _          | 5.0  | ns          | A2.2   |

| t <sub>FALL</sub>  | SYS_XTAL_IN fall time.                                            | _          | 5.0  | ns          | A2.3   |

| t <sub>DUTY</sub>  | SYS_XTAL_IN duty cycle (measured at $V_M$ ). <sup>(2)</sup>       |            | 60.0 | %           | A2.4   |

| CVIH               | SYS_XTAL_IN input voltage high                                    |            | _    | V           | A2.5   |

| CVIL               | SYS_XTAL_IN input voltage low                                     |            | 0.8  | V           | A2.6   |

| 1                  | -<br>The SVS_XTAL_IN frequency and system PLL_CEG[0_6] settings r | nuet ha cl |      | ch that the |        |

—The SYS\_XTAL\_IN frequency and system PLL\_CFG[0–6] settings must be chosen such that the resulting system frequencies do not exceed their respective maximum or minimum operating frequencies. See the *MPC5200B* User's Manual (MPC5200BUM).

$^2~$  SYS\_XTAL\_IN duty cycle is measured at V\_M.

### 1.3.4 Resets

The MPC5200B has three reset pins:

- PORRESET—Power on Reset

- HRESET—Hard Reset

- SRESET—Software Reset

These signals are asynchronous I/O signals and can be asserted at any time. The input side uses a Schmitt trigger and requires the same input characteristics as other MPC5200B inputs, as specified in the DC Electrical Specifications section. Table 14 specifies the pulse widths of the Reset inputs.

| Name     | Description    | Min Pulse Width                            | Max Pulse<br>Width | Reference Clock | SpecID |

|----------|----------------|--------------------------------------------|--------------------|-----------------|--------|

| PORRESET | Power On Reset | $t_{VDD\_stable} + t_{up\_osc} + t_{lock}$ |                    | SYS_XTAL_IN     | A3.1   |

| HRESET   | Hardware Reset | 4 clock cycles                             | —                  | SYS_XTAL_IN     | A3.2   |

| SRESET   | Software Reset | 4 clock cycles                             | _                  | SYS_XTAL_IN     | A3.3   |

Table 14. Reset Pulse Width

For **PORRESET** the value of the minimum pulse width reflects the power on sequence. If **PORRESET** is asserted afterwards its minimum pulse width equals the minimum given for **HRESET** related to the same reference clock.

The t<sub>VDD stable</sub> describes the time which is needed to get all power supplies stable.

For t<sub>lock</sub> refer to the Oscillator/PLL section of this specification for further details.

For t<sub>up osc.</sub> refer to the Oscillator/PLL section of this specification for further details.

Following the deassertion of PORRESET, HRESET and SRESET remain low for 4096 reference clock cycles.

The deassertion of HRESET for at least the minimum pulse width forces the internal resets to be active for an additional 4096 clock cycles.

#### NOTE

As long as VDD is not stable the HRESET output is not stable.

Table 15. Reset Rise/Fall Timing

| Description        | Min | Max | Unit | SpecID |

|--------------------|-----|-----|------|--------|

| PORRESET fall time | —   | 1   | ms   | A3.4   |

| PORRESET rise time | —   | 1   | ms   | A3.5   |

| HRESET fall time   | —   | 1   | ms   | A3.6   |

| HRESET rise time   | —   | 1   | ms   | A3.7   |

| SRESET fall time   | —   | 1   | ms   | A3.8   |

| SRESET rise time   | —   | 1   | ms   | A3.9   |

### NOTE

Make sure that the **PORRESET** does not carry any glitches. The MPC5200B has no filter to prevent them from getting into the chip. **HRESET** and **SRESET** must have a monotonous rise time. The assertion of **HRESET** becomes active at Power on Reset without any SYS\_XTAL clock.

2) The interrupt latency descriptions in the table above are related to non competitive, non masked but enabled external interrupt sources. Take care of interrupt prioritization which may increase the latencies.

Because all external interrupt signals are synchronized into the internal processor bus clock domain, each of these signals has to exceed a minimum pulse width of more than one IP\_CLK cycle.

| Name                                  | Min Pulse Width | Max Pulse Width | Reference Clock | SpecID |

|---------------------------------------|-----------------|-----------------|-----------------|--------|

| All external interrupts (IRQs, GPIOs) | > 1 clock cycle | _               | IP_CLK          | A4.22  |

#### Table 17. Minimum Pulse Width for External Interrupts to be Recognized

NOTES:

- 1) The frequency of the IP\_CLK depends on the register settings in Clock Distribution Module. See the MPC5200B User's Manual (MPC5200BUM) for further information.

- 2) If the same interrupt occurs a second time while its interrupt service routine has not cleared the former one, the second interrupt is not recognized at all.

Besides synchronization, prioritization, and mapping the latency of an external interrupt to the start of its associated interrupt service routine also depends on the following conditions: To get a minimum interrupt service response time, it is recommended to enable the instruction cache and set up the maximum core clock, XL bus, and IP bus frequencies (depending on board design and programming). In addition, it is advisable to execute an interrupt handler, which has been implemented in assembly code.

### 1.3.6 SDRAM

### 1.3.6.1 Memory Interface Timing-Standard SDRAM Read Command

| Sym                   | Description                                                            | Min                              | Мах                              | Units | SpecID |

|-----------------------|------------------------------------------------------------------------|----------------------------------|----------------------------------|-------|--------|

| t <sub>mem_clk</sub>  | MEM_CLK period                                                         | 7.5                              | _                                | ns    | A5.1   |

| t <sub>valid</sub>    | Control Signals, Address and MBA Valid after<br>rising edge of MEM_CLK | _                                | t <sub>mem_clk</sub> × 0.5 + 0.4 | ns    | A5.2   |

| t <sub>hold</sub>     | Control Signals, Address and MBA Hold after<br>rising edge of MEM_CLK  | t <sub>mem_clk</sub> × 0.5       | —                                | ns    | A5.3   |

| DM <sub>valid</sub>   | DQM valid after rising edge of MEM_CLK                                 | —                                | $t_{mem\_clk} \times 0.25 + 0.4$ | ns    | A5.4   |

| DM <sub>hold</sub>    | DQM hold after rising edge of MEM_CLK                                  | $t_{mem\_clk} \times 0.25 - 0.7$ | _                                | ns    | A5.5   |

| data <sub>setup</sub> | MDQ setup to rising edge of MEM_CLK                                    | —                                | 0.3                              | ns    | A5.6   |

| data <sub>hold</sub>  | MDQ hold after rising edge of MEM_CLK                                  | 0.2                              |                                  | ns    | A5.7   |

#### Table 18. Standard SDRAM Memory Read Timing

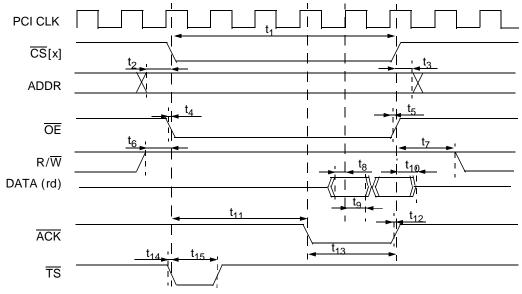

| Sym             | Description                         | Min                 | Max                           | Units | Notes | SpecID |

|-----------------|-------------------------------------|---------------------|-------------------------------|-------|-------|--------|

| t <sub>10</sub> | DATA input setup before CS negation | 8.5                 | _                             | ns    | _     | A7.12  |

| t <sub>11</sub> | DATA input hold after CS negation   | 0                   | (DC + 1) × t <sub>PCIck</sub> | ns    | (6)   | A7.13  |

| t <sub>12</sub> | ACK assertion after CS assertion    | t <sub>PClck</sub>  | _                             | ns    | (3)   | A7.14  |

| t <sub>13</sub> | ACK negation after CS negation      |                     | t <sub>PCIck</sub>            | ns    | (3)   | A7.15  |

| t <sub>14</sub> | TS assertion before CS assertion    | —                   | 6.9                           | ns    | (4)   | A7.16  |

| t <sub>15</sub> | TS pulse width                      | t <sub>PClck</sub>  | t <sub>PCIck</sub>            | ns    | (4)   | A7.17  |

| t <sub>16</sub> | TSIZ valid before CS assertion      | t <sub>IPBIck</sub> |                               | ns    | (5)   | A7.18  |

| t <sub>17</sub> | TSIZ hold after CS negation         | t <sub>IPBIck</sub> | _                             | ns    | (5)   | A7.19  |

| t <sub>18</sub> | ACK change before PCI clock         | _                   | 2.0                           | ns    | (1)   | A7.20  |

| t <sub>19</sub> | ACK change after PCI clock          |                     | 4.4                           | ns    | (1)   | A7.21  |

#### Table 24. Non-MUXed Mode Timing (continued)

NOTES:

1. ACK can shorten the CS pulse width.

Wait States (WS) can be programmed in the Chip Select X Register, Bit field WaitP and WaitX. It can be specified from 0–65535.

2. In Large Flash and MOST Graphics mode the shared PCI/ATA pins, used as address lines, are released at the same moment as the CS. This can cause the address to change before CS is deasserted.

- 3. ACK is input and can be used to shorten the CS pulse width.

- 4. Only available in Large Flash and MOST Graphics mode.

- 5. Only available in MOST Graphics mode.

6. Deadcycles are only used, if no arbitration to an other module (ATA or PCI) of the shared local bus happens. If arbitration happens the bus can be driven within 4 IPB clocks by an other modules.

| Sym             | Description                              | Min                                                                    | Max                                               | Units | Notes   | SpecID |

|-----------------|------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------|-------|---------|--------|

| t <sub>9</sub>  | DATA hold after rising edge of PCI clock | 0                                                                      |                                                   | ns    |         | A7.32  |

| t <sub>10</sub> | DATA hold after CS negation              | 0                                                                      | (DC + 1) × t <sub>PClck</sub>                     | ns    | (4)     | A7.33  |

| t <sub>11</sub> | ACK assertion after CS assertion         | —                                                                      | $(WS + 1) \times t_{PClck}$                       | ns    | _       | A7.34  |

| t <sub>12</sub> | ACK negation before CS negation          | —                                                                      | 7.0                                               | ns    | (3)     | A7.35  |

| t <sub>13</sub> | ACK pulse width                          | $4^{\text{LB}} \times 2 \times (32/\text{DS}) \times t_{\text{PClck}}$ | $4^{LB} \times 2 \times (32/DS) \times t_{PCIck}$ | ns    | (2),(3) | A7.36  |

| t <sub>14</sub> | CS assertion after TS assertion          | —                                                                      | 2.5                                               | ns    | _       | A7.37  |

| t <sub>15</sub> | TS pulse width                           | t <sub>PClck</sub>                                                     | t <sub>PClck</sub>                                | ns    | —       | A7.38  |

### Table 25. Burst Mode Timing (continued)

NOTES:

- 1. Wait States (WS) can be programmed in the Chip Select X Register, Bit field WaitP and WaitX. It can be specified from 0–65535.

- 2. Example:

Long Burst is used, this means the CS related BERx and SLB bits of the Chip Select Burst Control Register are set and a burst on the internal XLB is executed. => LB = 1

Data bus width is 8 bit.  $\Rightarrow$  DS = 8

$=> 4^1 \times 2 \times (32/8) = 32 =>$  ACK is asserted for 32 PCI cycles to transfer one cache line.

Wait State is set to 10. => WS = 10

$1 + 10 + 32 = 43 \Rightarrow CS$  is asserted for 43 PCI cycles.

- 3. ACK is output and indicates the burst.

- 4. Deadcycles are only used, if no arbitration to an other module (ATA or PCI) of the shared local bus happens. If arbitration happens the bus can be driven within 4 IPB clocks by an other modules.

Figure 12. Timing Diagram—Burst Mode

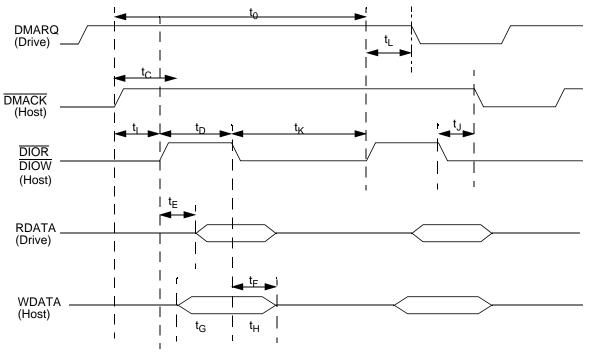

All ATA transfers are programmed in terms of system clock cycles (IP bus clocks) in the ATA Host Controller timing registers. This puts constraints on the ATA protocols and their respective timing modes in which the ATA Controller can communicate with the drive.

Faster ATA modes (i.e., UDMA 0, 1, 2) are supported when the system is running at a sufficient frequency to provide adequate data transfer rates. Adequate data transfer rates are a function of the following:

- The MPC5200B operating frequency (IP bus clock frequency)

- Internal MPC5200B bus latencies

- Other system load dependent variables

The ATA clock is the same frequency as the IP bus clock in MPC5200B. See the MPC5200B User's Manual (MPC5200B).

### NOTE

All output timing numbers are specified for nominal 50 pF loads.

| Sym             | PIO Timing Parameter                  | Min/Max<br>(ns) | Mode 0<br>(ns) | Mode 1<br>(ns) | Mode 2<br>(ns) | Mode 3<br>(ns) | Mode 4<br>(ns) | SpecID |

|-----------------|---------------------------------------|-----------------|----------------|----------------|----------------|----------------|----------------|--------|

| t <sub>0</sub>  | Cycle Time                            | min             | 600            | 383            | 240            | 180            | 120            | A8.1   |

| t <sub>1</sub>  | Address valid to DIOR/DIOW setup      | min             | 70             | 50             | 30             | 30             | 25             | A8.2   |

| t <sub>2</sub>  | DIOR/DIOW pulse width 16-bit<br>8-bit | min<br>min      | 165<br>290     | 125<br>290     | 100<br>290     | 80<br>80       | 70<br>70       | A8.3   |

| t <sub>2i</sub> | DIOR/DIOW recovery time               | min             |                | —              | —              | 70             | 25             | A8.4   |

| t <sub>3</sub>  | DIOW data setup                       | min             | 60             | 45             | 30             | 30             | 20             | A8.5   |

| t <sub>4</sub>  | DIOW data hold                        | min             | 30             | 20             | 15             | 10             | 10             | A8.6   |

| t <sub>5</sub>  | DIOR data setup                       | min             | 50             | 35             | 20             | 20             | 20             | A8.7   |

| t <sub>6</sub>  | DIOR data hold                        | min             | 5              | 5              | 5              | 5              | 5              | A8.8   |

| t <sub>9</sub>  | DIOR/DIOW to address valid hold       | min             | 20             | 15             | 10             | 10             | 10             | A8.9   |

| t <sub>A</sub>  | IORDY setup                           | max             | 35             | 35             | 35             | 35             | 35             | A8.10  |

| t <sub>B</sub>  | IORDY pulse width                     | max             | 1250           | 1250           | 1250           | 1250           | 1250           | A8.11  |

### Figure 15. Multiword DMA Timing

### NOTE

The direction of signal assertion is towards the top of the page, and the direction of negation is towards the bottom of the page, irrespective of the electrical properties of the signal.

| Sym               | MODE 0<br>(ns) |     |     |     | MODE 2<br>(ns) |     | Comment                                                                                                                                 | SpecID |

|-------------------|----------------|-----|-----|-----|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|--------|

|                   | Min            | Max | Min | Мах | Min            | Мах |                                                                                                                                         |        |

| t <sub>CYC</sub>  | 114            | _   | 75  |     | 55             | _   | Cycle time allowing for asymmetry and clock<br>variations from STROBE edge to STROBE edge                                               | A8.26  |

| t <sub>2CYC</sub> | 235            | _   | 156 | —   | 117            |     | Two-cycle time allowing for clock variations, from rising edge to next rising edge or from falling edge to next falling edge of STROBE. | A8.27  |

| t <sub>DS</sub>   | 15             |     | 10  | —   | 7              | _   | Data setup time at recipient.                                                                                                           | A8.28  |

| t <sub>DH</sub>   | 5              | _   | 5   | —   | 5              | _   | Data hold time at recipient.                                                                                                            | A8.29  |

| t <sub>DVS</sub>  | 70             |     | 48  | —   | 34             | _   | Data valid setup time at sender, to STROBE edge.                                                                                        | A8.30  |

| t <sub>DVH</sub>  | 6              |     | 6   | —   | 6              | _   | Data valid hold time at sender, from STROBE edge.                                                                                       | A8.31  |

| t <sub>FS</sub>   | 0              | 230 | 0   | 200 | 0              | 170 | First STROBE time for drive to first negate DSTROBE from STOP during a data-in burst.                                                   | A8.32  |

| t <sub>LI</sub>   | 0              | 150 | 0   | 150 | 0              | 150 | Limited Interlock time.                                                                                                                 | A8.33  |

| t <sub>MLI</sub>  | 20             | —   | 20  | —   | 20             |     | Interlock time with minimum.                                                                                                            | A8.34  |

| t <sub>UI</sub>   | 0              | —   | 0   | —   | 0              |     | Unlimited interlock time.                                                                                                               | A8.35  |

| Table 29. | Ultra | DMA | Timing | Specification |

|-----------|-------|-----|--------|---------------|

|-----------|-------|-----|--------|---------------|

| Sym | Description              | Min | Max | Units         | SpecID |

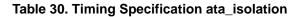

|-----|--------------------------|-----|-----|---------------|--------|

| 1   | ata_isolation setup time | 7   | —   | IP Bus cycles | A8.48  |

| 2   | ata_isolation hold time  | —   | 19  | IP Bus cycles | A8.49  |

### 1.3.10 Ethernet

AC Test Timing Conditions:

• Output Loading All Outputs: 25 pF

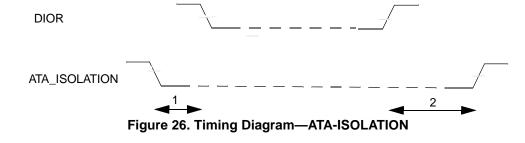

#### Table 31. MII Rx Signal Timing

| Sym            | Description                            | Min | Max | Unit                         | SpecID |

|----------------|----------------------------------------|-----|-----|------------------------------|--------|

| t <sub>1</sub> | RXD[3:0], RX_DV, RX_ER to RX_CLK setup | 10  |     | ns                           | A9.1   |

| t <sub>2</sub> | RX_CLK to RXD[3:0], RX_DV, RX_ER hold  | 10  | —   | ns                           | A9.2   |

| t <sub>3</sub> | RX_CLK pulse width high                | 35% | 65% | RX_CLK Period <sup>(1)</sup> | A9.3   |

| t <sub>4</sub> | RX_CLK pulse width low                 | 35% | 65% | RX_CLK Period <sup>(1)</sup> | A9.4   |

<sup>1</sup> RX\_CLK shall have a frequency of 25% of data rate of the received signal. See the IEEE 802.3 Specification.

Figure 27. Ethernet Timing Diagram—MII Rx Signal

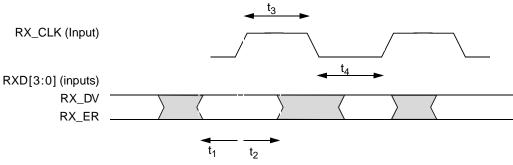

Figure 31. Timing Diagram—USB Output Line

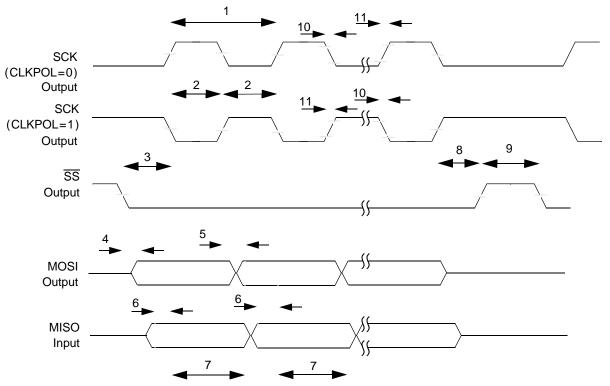

### 1.3.12 SPI

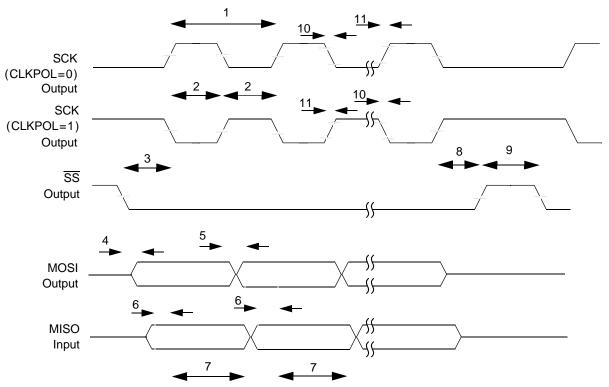

Table 36. Timing Specifications — SPI Master Mode, Format 0 (CPHA = 0)

| Sym | Description                                              | Min  | Max  | Units                       | SpecID |

|-----|----------------------------------------------------------|------|------|-----------------------------|--------|

| 1   | Cycle time                                               | 4    | 1024 | IP-Bus Cycle <sup>(1)</sup> | A11.1  |

| 2   | Clock high or low time                                   | 2    | 512  | IP-Bus Cycle <sup>(1)</sup> | A11.2  |

| 3   | Slave select to clock delay                              | 15.0 | —    | ns                          | A11.3  |

| 4   | Output Data valid after Slave Select ( $\overline{SS}$ ) | —    | 20.0 | ns                          | A11.4  |

| 5   | Output Data valid after SCK                              | —    | 20.0 | ns                          | A11.5  |

| 6   | Input Data setup time                                    | 20.0 | —    | ns                          | A11.6  |

| 7   | Input Data hold time                                     | 20.0 | —    | ns                          | A11.7  |

| 8   | Slave disable lag time                                   | 15.0 | —    | ns                          | A11.8  |

| 9   | Sequential transfer delay                                | 1    | —    | IP-Bus Cycle <sup>(1)</sup> | A11.9  |

| 10  | Clock falling time                                       | _    | 7.9  | ns                          | A11.10 |

| 11  | Clock rising time                                        | —    | 7.9  | ns                          | A11.11 |

<sup>1</sup> Inter Peripheral Clock is defined in the MPC5200B User's Manual (MPC5200BUM).

### NOTE

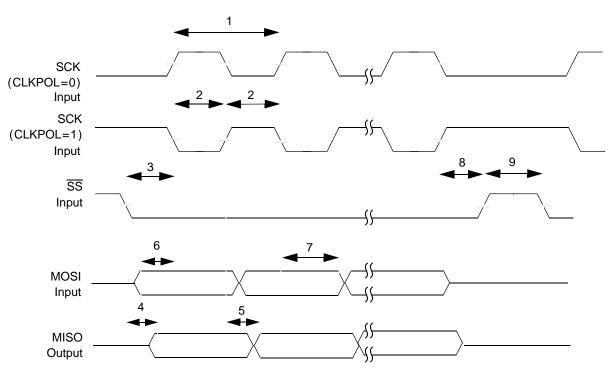

Table 37. Timing Specifications — SPI Slave Mode, Format 0 (CPHA = 0)

| Sym | Description                                            | Min  | Max  | Units                       | SpecID |

|-----|--------------------------------------------------------|------|------|-----------------------------|--------|

| 1   | Cycle time                                             | 4    | 1024 | IP-Bus Cycle <sup>(1)</sup> | A11.12 |

| 2   | Clock high or low time                                 | 2    | 512  | IP-Bus Cycle <sup>(1)</sup> | A11.13 |

| 3   | Slave select to clock delay                            | 15.0 | —    | ns                          | A11.14 |

| 4   | Output Data valid after Slave Select $(\overline{SS})$ | —    | 50.0 | ns                          | A11.15 |

| 5   | Output Data valid after SCK                            | —    | 50.0 | ns                          | A11.16 |

| 6   | Input Data setup time                                  | 50.0 | —    | ns                          | A11.17 |

| 7   | Input Data hold time                                   | 0.0  | —    | ns                          | A11.18 |

| 8   | Slave disable lag time                                 | 15.0 | —    | ns                          | A11.19 |

| 9   | Sequential Transfer delay                              | 1    | —    | IP-Bus Cycle <sup>(1)</sup> | A11.20 |

<sup>1</sup> Inter Peripheral Clock is defined in the MPC5200B User's Manual (MPC5200BUM).

### NOTE

MPC5200B Data Sheet, Rev. 4

Figure 33. Timing Diagram — SPI Slave Mode, Format 0 (CPHA = 0)

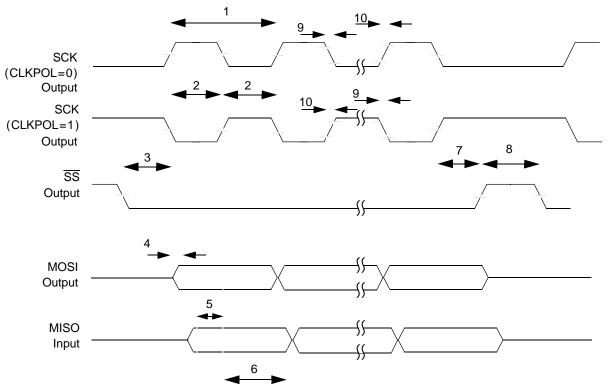

| Та  | Table 38. Timing Specifications — SPI Master Mode, Format 1 (CPHA = 1) |      |      |                             |        |  |  |  |

|-----|------------------------------------------------------------------------|------|------|-----------------------------|--------|--|--|--|

| Sym | Description                                                            | Min  | Max  | Units                       | SpecID |  |  |  |

| 1   | Cycle time                                                             | 4    | 1024 | IP-Bus Cycle <sup>(1)</sup> | A11.21 |  |  |  |

| 2   | Clock high or low time                                                 | 2    | 512  | IP-Bus Cycle <sup>(1)</sup> | A11.22 |  |  |  |

| 3   | Slave select to clock delay                                            | 15.0 | —    | ns                          | A11.23 |  |  |  |

| 4   | Output data valid                                                      | —    | 20.0 | ns                          | A11.24 |  |  |  |

| 5   | Input Data setup time                                                  | 20.0 | —    | ns                          | A11.25 |  |  |  |

| 6   | Input Data hold time                                                   | 20.0 |      | ns                          | A11.26 |  |  |  |

| 7   | Slave disable lag time                                                 | 15.0 | —    | ns                          | A11.27 |  |  |  |

| 8   | Sequential Transfer delay                                              | 1    |      | IP-Bus Cycle <sup>(1)</sup> | A11.28 |  |  |  |

| 9   | Clock falling time                                                     | —    | 7.9  | ns                          | A11.29 |  |  |  |

| 10  | Clock rising time                                                      | _    | 7.9  | ns                          | A11.30 |  |  |  |

Inter Peripheral Clock is defined in the MPC5200B User's Manual (MPC5200BUM).

### NOTE

Output timing is specified at a nominal 50 pF load.

1

Figure 34. Timing Diagram — SPI Master Mode, Format 1 (CPHA = 1)

| Sym | Description                 | Min  | Max  | Units                       | SpecID |

|-----|-----------------------------|------|------|-----------------------------|--------|

| 1   | Cycle time                  | 4    | 1024 | IP-Bus Cycle <sup>(1)</sup> | A11.31 |

| 2   | Clock high or low time      | 2    | 512  | IP-Bus Cycle <sup>(1)</sup> | A11.32 |

| 3   | Slave select to clock delay | 15.0 |      | ns                          | A11.33 |

| 4   | Output data valid           | _    | 50.0 | ns                          | A11.34 |

| 5   | Input Data setup time       | 50.0 | _    | ns                          | A11.35 |

| 6   | Input Data hold time        | 0.0  | _    | ns                          | A11.36 |

| 7   | Slave disable lag time      | 15.0 | —    | ns                          | A11.37 |

| 8   | Sequential Transfer delay   | 1    | —    | IP-Bus Cycle <sup>(1)</sup> | A11.38 |

<sup>1</sup> Inter Peripheral Clock is defined in the MPC5200B User's Manual (MPC5200BUM).

### NOTE

MPC5200B Data Sheet, Rev. 4

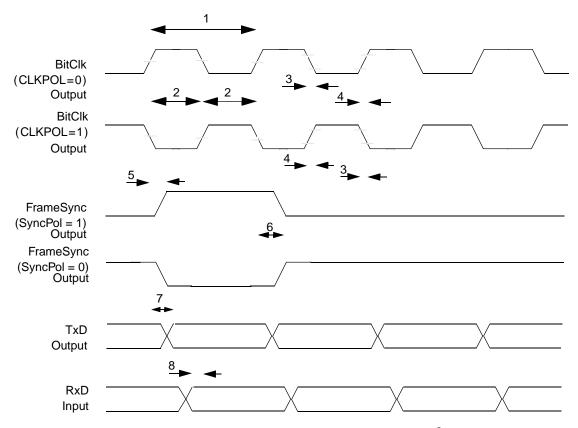

# 1.3.16 PSC

# 1.3.16.1 Codec Mode (8-,16-, 24-, and 32-bit)/I<sup>2</sup>S Mode

### Table 42. Timing Specifications—8-, 16-, 24-, and 32-bit CODEC / I<sup>2</sup>S Master Mode

| Sym | Description                                      |     | Тур | Мах | Units            | SpecID |

|-----|--------------------------------------------------|-----|-----|-----|------------------|--------|

| 1   | Bit Clock cycle time, programmed in CCS register |     | —   | _   | ns               | A15.1  |

| 2   | Clock duty cycle                                 |     | 50  | _   | % <sup>(1)</sup> | A15.2  |

| 3   | Bit Clock fall time                              |     | _   | 7.9 | ns               | A15.3  |

| 4   | Bit Clock rise time                              |     | —   | 7.9 | ns               | A15.4  |

| 5   | FrameSync valid after clock edge                 | _   | —   | 8.4 | ns               | A15.5  |

| 6   | FrameSync invalid after clock edge               | —   | —   | 8.4 | ns               | A15.6  |

| 7   | Output Data valid after clock edge               | —   | —   | 9.3 | ns               | A15.7  |

| 8   | Input Data setup time                            | 6.0 | —   | _   | ns               | A15.8  |

<sup>1</sup> Bit Clock cycle time.

### NOTE

Output timing is specified at a nominal 50 pF load.

Figure 37. Timing Diagram — 8-, 16-, 24-, and 32-bit CODEC /  $I^2S$  Master Mode

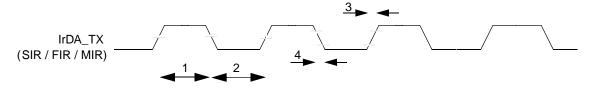

Figure 40. Timing Diagram — IrDA Transmit Line

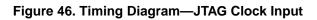

### 1.3.16.4 SPI Mode

### Table 46. Timing Specifications — SPI Master Mode, Format 0 (CPHA = 0)

| Sym | Description                                                            |      | Max | Units | SpecID |

|-----|------------------------------------------------------------------------|------|-----|-------|--------|

| 1   | SCK cycle time, programable in the PSC CCS register                    |      | —   | ns    | A15.26 |

| 2   | SCK pulse width, 50% SCK duty cycle                                    | 15.0 |     | ns    | A15.27 |

| 3   | Slave select clock delay, programable in the PSC CCS register          | 30.0 | —   | ns    | A15.28 |

| 4   | Output Data valid after Slave Select $(\overline{SS})$                 |      | 8.9 | ns    | A15.29 |

| 5   | Output Data valid after SCK                                            |      | 8.9 | ns    | A15.30 |

| 6   | Input Data setup time                                                  |      | —   | ns    | A15.31 |

| 7   | Input Data hold time                                                   |      | _   | ns    | A15.32 |

| 8   | Slave disable lag time                                                 |      | 8.9 | ns    | A15.33 |

| 9   | Sequential Transfer delay, programable in the PSC CTUR / CTLR register |      | —   | ns    | A15.34 |

| 10  | Clock falling time                                                     |      | 7.9 | ns    | A15.35 |

| 11  | Clock rising time                                                      | _    | 7.9 | ns    | A15.36 |

### NOTE

Table 47. Timing Specifications — SPI Slave Mode, Format 0 (CPHA = 0)

| Sym | Description                                                            |      | Max  | Units | SpecID |

|-----|------------------------------------------------------------------------|------|------|-------|--------|

| 1   | SCK cycle time, programable in the PSC CCS register                    |      |      | ns    | A15.37 |

| 2   | SCK pulse width, 50% SCK duty cycle                                    | 15.0 | _    | ns    | A15.38 |

| 3   | Slave select clock delay                                               |      | _    | ns    | A15.39 |

| 4   | Input Data setup time                                                  |      | _    | ns    | A15.40 |

| 5   | Input Data hold time                                                   |      | _    | ns    | A15.41 |

| 6   | Output data valid after SS                                             |      | 14.0 | ns    | A15.42 |

| 7   | Output data valid after SCK                                            |      | 14.0 | ns    | A15.43 |

| 8   | Slave disable lag time                                                 |      | _    | ns    | A15.44 |

| 9   | Minimum Sequential Transfer delay = $2 \times IP$ Bus clock cycle time |      | _    | _     | A15.45 |

### NOTE

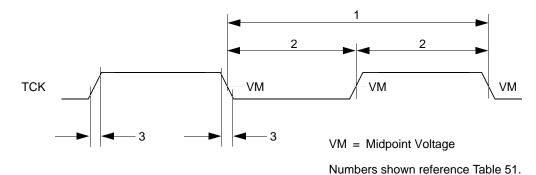

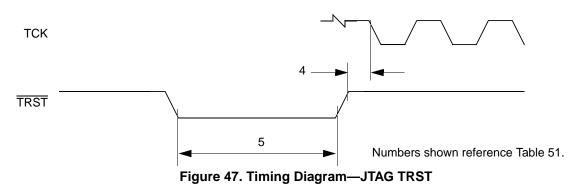

# 1.3.18 IEEE 1149.1 (JTAG) AC Specifications

### Table 51. JTAG Timing Specification

| Sym | Characteristic                                       | Min  | Max | Unit | SpecID |

|-----|------------------------------------------------------|------|-----|------|--------|

| —   | TCK frequency of operation.                          | 0    | 25  | MHz  | A17.1  |

| 1   | TCK cycle time.                                      | 40   | —   | ns   | A17.2  |

| 2   | TCK clock pulse width measured at 1.5V.              | 1.08 | —   | ns   | A17.3  |

| 3   | TCK rise and fall times.                             | 0    | 3   | ns   | A17.4  |

| 4   | TRST setup time to tck falling edge <sup>(1)</sup> . | 10   | —   | ns   | A17.5  |

| 5   | TRST assert time.                                    | 5    | —   | ns   | A17.6  |

| 6   | Input data setup time <sup>(2)</sup> .               | 5    | —   | ns   | A17.7  |

| 7   | Input data hold time <sup>(2)</sup> .                | 15   | —   | ns   | A17.8  |

| 8   | TCK to output data valid <sup>(3)</sup> .            | 0    | 30  | ns   | A17.9  |

| 9   | TCK to output high impedance <sup>(3)</sup> .        | 0    | 30  | ns   | A17.10 |

| 10  | TMS, TDI data setup time.                            | 5    | —   | ns   | A17.11 |

| 11  | TMS, TDI data hold time.                             | 1    | —   | ns   | A17.12 |

| 12  | TCK to TDO data valid.                               | 0    | 15  | ns   | A17.13 |

| 13  | TCK to TDO high impedance.                           | 0    | 15  | ns   | A17.14 |

<sup>1</sup> TRST is an asynchronous signal. The setup time is for test purposes only.

<sup>2</sup> Non-test, other than TDI and TMS, signal input timing with respect to TCK.

<sup>3</sup> Non-test, other than TDO, signal output timing with respect to TCK.

| Table 52. MPC5200B Plnout Listing (continued) |       |        |                 |                       |               |                  |  |  |

|-----------------------------------------------|-------|--------|-----------------|-----------------------|---------------|------------------|--|--|

| Name                                          | Alias | Туре   | Power Supply    | Output Driver<br>Type | Input<br>Type | Pull-up/<br>down |  |  |

| TIMER_1                                       |       | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| TIMER_2                                       | MOSI  | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| TIMER_3                                       | MISO  | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| TIMER_4                                       | SS    | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| TIMER_5                                       | SCK   | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| TIMER_6                                       |       | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| TIMER_7                                       |       | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

|                                               |       |        | Clock           |                       | L             |                  |  |  |

| SYS_XTAL_IN                                   |       | Input  | VDD_IO          |                       |               |                  |  |  |

| SYS_XTAL_OUT                                  |       | Output | VDD_IO          |                       |               |                  |  |  |

| RTC_XTAL_IN                                   |       | Input  | VDD_IO          |                       |               |                  |  |  |

| RTC_XTAL_OUT                                  |       | Output | VDD_IO          |                       |               |                  |  |  |

|                                               |       |        | Misc            | L                     | L             |                  |  |  |

| PORRESET                                      |       | Input  | VDD_IO          | DRV4                  | Schmitt       |                  |  |  |

| HRESET                                        |       | I/O    | VDD_IO          | DRV8_OD <sup>1</sup>  | Schmitt       |                  |  |  |

| SRESET                                        |       | I/O    | VDD_IO          | DRV8_OD <sup>1</sup>  | Schmitt       |                  |  |  |

| IRQ0                                          |       | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| IRQ1                                          |       | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| IRQ2                                          |       | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| IRQ3                                          |       | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

|                                               |       | Tes    | t/Configuration |                       |               |                  |  |  |

| SYS_PLL_TPA                                   |       | I/O    | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| TEST_MODE_0                                   |       | Input  | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| TEST_MODE_1                                   |       | Input  | VDD_IO          | DRV4                  | TTL           |                  |  |  |

| TEST_SEL_0                                    |       | I/O    | VDD_IO          | DRV4                  | TTL           | PULLUP           |  |  |

| TEST_SEL_1                                    |       | I/O    | VDD_IO          | DRV8                  | TTL           |                  |  |  |

| JTAG_TCK                                      | TCK   | Input  | VDD_IO          | DRV4                  | Schmitt       | PULLUP           |  |  |

| JTAG_TDI                                      | TDI   | Input  | VDD_IO          | DRV4                  | TTL           | PULLUP           |  |  |

| JTAG_TDO                                      | TDO   | I/O    | VDD_IO          | DRV8                  | TTL           |                  |  |  |

| JTAG_TMS                                      | TMS   | Input  | VDD_IO          | DRV4                  | TTL           | PULLUP           |  |  |

| JTAG_TRST                                     | TRST  | Input  | VDD_IO          | DRV4                  | TTL           | PULLUP           |  |  |

| Power and Ground                              |       |        |                 |                       |               |                  |  |  |

| VDD_IO                                        |       |        |                 |                       |               |                  |  |  |

### Table 52. MPC5200B Pinout Listing (continued)

Normally this interface is implemented, using a COP (common on-chip processor) connector. The COP allows a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the MPC5200B.

## 3.4.2 e300 COP/BDM Interface

There are two possibilities to connect the JTAG interface: using it with a COP connector and without a COP connector.

### 3.4.2.1 Boards Interfacing the JTAG Port via a COP Connector

The MPC5200B functional pin interface and internal logic provides access to the embedded e300 processor core through the Freescale (formerly Motorola) standard COP/BDM interface. Table 53 gives the COP/BDM interface signals. The pin order shown reflects only the COP/BDM connector order.

| BDM<br>Pin # | MPC5200B<br>I/O Pin | BDM<br>Connector    | Internal<br>Pull Up/Down | External<br>Pull Up/Down | I/O <sup>1</sup> |

|--------------|---------------------|---------------------|--------------------------|--------------------------|------------------|

| 16           | _                   | GND                 | _                        | _                        | _                |

| 15           | TEST_SEL_0          | ckstp_out           | _                        | _                        | I                |

| 14           | _                   | KEY                 | _                        | _                        | _                |

| 13           | HRESET              | hreset              | —                        | 10k Pull-Up              | 0                |

| 12           | _                   | GND                 | —                        | _                        | —                |

| 11           | SRESET              | sreset              | _                        | 10k Pull-Up              | 0                |

| 10           | _                   | N/C                 | —                        | _                        | —                |

| 9            | JTAG_TMS            | tms                 | 100k Pull-Up             | 10k Pull-Up              | 0                |

| 8            | —                   | N/C                 | —                        | —                        | —                |

| 7            | JTAG_TCK            | tck                 | 100k Pull-Up             | 10k Pull-Up              | 0                |

| 6            | _                   | VDD <sup>2</sup>    | —                        |                          | —                |

| 5            | _                   | halted <sup>3</sup> | _                        |                          | I                |

| 4            | JTAG_TRST           | trst                | 100k Pull-Up             | 10k Pull-Up              | 0                |

| 3            | JTAG_TDI            | tdi                 | 100k Pull-Up             | 10k Pull-Up              | 0                |

| 2            |                     | qack <sup>4</sup>   | _                        | —                        | 0                |

| 1            | JTAG_TDO            | tdo                 | —                        | —                        | I                |

Table 53. COP/BDM Interface Signals

<sup>1</sup> With respect to the emulator tool's perspective, Input is really an output from the embedded e300 core and output is really an input to the core.

<sup>2</sup> From the board under test, power sense for chip power.

<sup>3</sup> HALTED is not available from e300 core.

<sup>4</sup> Input to the e300 core to enable/disable soft-stop condition during breakpoints. MPC5200B internally ties CORE\_QACK to GND in its normal/functional mode (always asserted).

For a board with a COP (common on-chip processor) connector, which accesses the JTAG interface and which needs to reset the JTAG module, simply wiring JTAG\_TRST and PORRESET is not recommended.

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MPC5200BDS Rev. 4 02/2010 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008, 2010. All rights reserved.