# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 400MHz                                                                  |

| Co-Processors/DSP               | -                                                                       |

| RAM Controllers                 | DDR, SDRAM                                                              |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100Mbps (1)                                                          |

| SATA                            | -                                                                       |

| USB                             | USB 1.1 (2)                                                             |

| Voltage - I/O                   | 2.5V, 3.3V                                                              |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                         |

| Security Features               | -                                                                       |

| Package / Case                  | 272-BBGA                                                                |

| Supplier Device Package         | 272-PBGA (27x27)                                                        |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc5200vr400br2 |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Characteristic                                         | Condition                                                                   | Sym                | Min  | Max | Unit | SpecID |

|--------------------------------------------------------|-----------------------------------------------------------------------------|--------------------|------|-----|------|--------|

| Input leakage current                                  | RTC_XTAL_IN<br>Vin = 0 or VDD_IO                                            | I <sub>IN</sub>    | _    | ±10 | μΑ   | D3.15  |

| Input current, pullup resistor                         | PULLUP<br>VDD_IO<br>Vin = 0                                                 | I <sub>INpu</sub>  | 40   | 109 | μΑ   | D3.16  |

| Input current, pullup resistor<br>— memory I/O buffers | PULLUP_MEM<br>VDD_IO_MEM <sub>SDR</sub><br>Vin = 0                          | I <sub>INpu</sub>  | 41   | 111 | μA   | D3.17  |

| Input current, pulldown<br>resistor                    | PULLDOWN<br>VDD_IO<br>Vin = VDD_IO                                          | I <sub>INpd</sub>  | 36   | 106 | μΑ   | D3.18  |

| Output high voltage                                    | IOH is driver dependent <sup>(2)</sup><br>VDD_IO, VDD_IO_MEM <sub>SDR</sub> | V <sub>OH</sub>    | 2.4  | —   | V    | D3.19  |

| Output high voltage                                    | IOH is driver dependent <sup>(2)</sup><br>VDD_IO_MEM <sub>DDR</sub>         | V <sub>OHDDR</sub> | 1.7  | _   | V    | D3.20  |

| Output low voltage                                     | IOL is driver dependent <sup>(2)</sup><br>VDD_IO, VDD_IO_MEM <sub>SDR</sub> | V <sub>OL</sub>    | —    | 0.4 | V    | D3.21  |

| Output low voltage                                     | IOL is driver dependent <sup>(2)</sup><br>VDD_IO_MEM <sub>DDR</sub>         | V <sub>OLDDR</sub> | _    | 0.4 | V    | D3.22  |

| DC Injection Current Per<br>Pin <sup>(3)</sup>         |                                                                             | I <sub>CS</sub>    | -1.0 | 1.0 | mA   | D3.23  |

| Capacitance                                            | Vin = 0 V, f = 1 MHz                                                        | C <sub>in</sub>    |      | 15  | pF   | D3.24  |

| Table 3. DC Electrical Specifications (continued) |

|---------------------------------------------------|

|---------------------------------------------------|

<sup>1</sup> Leakage current is measured with output drivers disabled and pull-up/pull-downs inactive.

<sup>2</sup> See Table 4 for the typical drive capability of a specific signal pin based on the type of output driver associated with that pin as listed in Table 52.

<sup>3</sup> All injection current is transferred to VDD\_IO/VDD\_IO\_MEM. An external load is required to dissipate this current to maintain the power supply within the specified voltage range. Total injection current for all digital input-only and all digital input/output pins must not exceed 10 mA. Exceeding this limit can cause disruption of normal operation.

| Driver Type | Supply Voltage     | I <sub>ОН</sub> | I <sub>OL</sub> | Unit | SpecID |

|-------------|--------------------|-----------------|-----------------|------|--------|

| DRV4        | VDD_IO = 3.3 V     | 4               | 4               | mA   | D3.25  |

| DRV8        | VDD_IO = 3.3 V     | 8               | 8               | mA   | D3.26  |

| DRV8_OD     | VDD_IO = 3.3 V     | —               | 8               | mA   | D3.27  |

| DRV16_MEM   | VDD_IO_MEM = 3.3 V | 16              | 16              | mA   | D3.28  |

| DRV16_MEM   | VDD_IO_MEM = 2.5 V | 16              | 16              | mA   | D3.29  |

| PCI         | VDD_IO = 3.3 V     | 16              | 16              | mA   | D3.30  |

| Table 4. Drive Capabilit | y of MPC5200B Output Pins |

|--------------------------|---------------------------|

| Tuble H Brite Supublic   |                           |

| Core Power Supply (VDD_CORE) |                         |                                        |                |         |        |  |

|------------------------------|-------------------------|----------------------------------------|----------------|---------|--------|--|

|                              | SYS_XTAL/XLB/P          |                                        |                |         |        |  |

| Mode                         | 33/66/33/33/264         | 33/132/66/132/396                      | Unit           | Notes   | SpecID |  |

|                              | Тур                     | Тур                                    |                |         |        |  |

| Operational                  | 727.5                   | 1080                                   | mW             | (1),(2) | D5.1   |  |

| Doze                         | _                       | 600                                    | mW             | (1),(3) | D5.2   |  |

| Nap                          | _                       | 225                                    | mW             | (1),(4) | D5.3   |  |

| Sleep                        | _                       | 225                                    | mW             | (1),(5) | D5.4   |  |

| Deep-Sleep                   | 52.5                    | 52.5                                   | mW             | (1),(6) | D5.5   |  |

|                              | PLL Power Supplies (SYS | PLL_AVDD, CORE_PLL_AVD                 | D)             | I       |        |  |

| Mode                         | т                       | ӯҏ                                     | Unit           | Notes   |        |  |

| Typical                      |                         | 2                                      | mW             | (7)     | D5.6   |  |

| 1                            | Unloaded I/O Power Sup  | plies (VDD_IO, VDD_MEM_IO <sup>8</sup> | <sup>3</sup> ) |         |        |  |

| Mode                         | т                       | ӯҏ                                     | Unit           | Notes   |        |  |

| Typical                      | ;                       | 33                                     | mW             | (9)     | D5.7   |  |

#### Table 6. Power Dissipation

<sup>1</sup> Typical core power is measured at VDD\_CORE = 1.5 V, Tj = 25 °C

<sup>2</sup> Operational power is measured while running an entirely cache-resident program with floating-point multiplication instructions in parallel with a continuous PCI transaction via BestComm.

<sup>3</sup> Doze power is measured with the e300 core in Doze mode, the system oscillator, System PLL and Core PLL are active, all other system modules are inactive

<sup>4</sup> Nap power is measured with the e300 core in Nap mode, the system oscillator, System PLL and Core PLL are active, all other system modules are inactive

<sup>5</sup> Sleep power is measured with the e300 core in Sleep mode, the system oscillator, System PLL and Core PLL are active, all other system modules are inactive

<sup>6</sup> Deep-Sleep power is measured with the e300 core in Sleep mode, the system oscillator, System PLL, Core PLL and all other system modules are inactive

$^7$  Typical PLL power is measured at SYS\_PLL\_AVDD = CORE\_PLL\_AVDD = 1.5 V, Tj = 25  $^\circ\text{C}$

<sup>8</sup> IO power figures given in the table represent the worst case scenario. For the VDD\_MEM\_IO rail connected to 2.5 V the IO power is expected to be lower and bounded by the worst case with VDD\_MEM\_IO connected to 3.3 V.

<sup>9</sup> Unloaded typical I/O power is measured in Deep-Sleep mode at VDD\_IO = VDD\_MEM\_IO<sub>SDR</sub>= 3.3 V, Tj = 25 °C

# 1.1.6 Thermal Characteristics

| Rating                                    | Board Layers               | Sym                   | Value | Unit | Notes   | SpecID |

|-------------------------------------------|----------------------------|-----------------------|-------|------|---------|--------|

| Junction to Ambient<br>Natural Convection | Single layer board<br>(1s) | R <sub>θJA</sub>      | 30    | °C/W | (1),(2) | D6.1   |

| Junction to Ambient<br>Natural Convection | Four layer board (2s2p)    | R <sub>θJMA</sub>     | 22    | °C/W | (1),(3) | D6.2   |

| Junction to Ambient (@200<br>ft/min)      | Single layer board<br>(1s) | R <sub>θJMA</sub>     | 24    | °C/W | (1),(3) | D6.3   |

| Junction to Ambient (@200<br>ft/min)      | Four layer board<br>(2s2p) | R <sub>θJMA</sub>     | 19    | °C/W | (1),(3) | D6.4   |

| Junction to Board                         | —                          | $R_{\theta J B}$      | 14    | °C/W | (4)     | D6.5   |

| Junction to Case                          | —                          | $R_{	extsf{	heta}JC}$ | 8     | °C/W | (5)     | D6.6   |

| Junction to Package Top                   | Natural Convection         | $\Psi_{JT}$           | 2     | °C/W | (6)     | D6.7   |

Table 7. Thermal Resistance Data

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- <sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- <sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

- <sup>4</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- <sup>5</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- <sup>6</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

### 1.1.6.1 Heat Dissipation

An estimation of the chip-junction temperature, T<sub>J</sub>, can be obtained from the following equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

Eqn. 3

where:

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$P_D$  = power dissipation in package (W)

The junction to ambient thermal resistance is an industry standard value, which provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board, and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is correct depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

Historically, the thermal resistance has frequently been expressed as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

# **1.2.1** System Oscillator Electrical Characteristics

Table 8. System Oscillator Electrical Characteristics

| Characteristic           | Sym                   | Notes | Min  | Typical | Max  | Unit | SpecID |

|--------------------------|-----------------------|-------|------|---------|------|------|--------|

| SYS_XTAL frequency       | f <sub>sys_xtal</sub> |       | 15.6 | 33.3    | 35.0 | MHz  | O1.1   |

| Oscillator start-up time | t <sub>up_osc</sub>   |       |      | —       | 10   | ms   | 01.2   |

# **1.2.2 RTC Oscillator Electrical Characteristics**

**Table 9. RTC Oscillator Electrical Characteristics**

| Characteristic     | Sym                   | Notes | Min | Typical | Max | Unit | SpecID |

|--------------------|-----------------------|-------|-----|---------|-----|------|--------|

| RTC_XTAL frequency | f <sub>rtc_xtal</sub> |       |     | 32.768  |     | kHz  | O2.1   |

### **1.2.3** System PLL Electrical Characteristics

| Characteristic              | Sym                   | Notes | Min  | Typical | Max  | Unit | SpecID |

|-----------------------------|-----------------------|-------|------|---------|------|------|--------|

| SYS_XTAL frequency          | f <sub>sys_xtal</sub> | (1)   | 15.6 | 33.3    | 35.0 | MHz  | O3.1   |

| SYS_XTAL cycle time         | t <sub>sys_xtal</sub> | (1)   | 66.6 | 30.0    | 28.5 | ns   | O3.2   |

| SYS_XTAL clock input jitter | t <sub>jitter</sub>   | (2)   | —    | —       | 150  | ps   | O3.3   |

| System VCO frequency        | f <sub>VCOsys</sub>   | (1)   | 250  | 533     | 800  | MHz  | O3.4   |

| System PLL relock time      | t <sub>lock</sub>     | (3)   | —    | —       | 100  | μS   | O3.5   |

<sup>1</sup> The SYS\_XTAL frequency and PLL Configuration bits must be chosen such that the resulting system frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies.

<sup>2</sup> This represents total input jitter—short term and long term combined—and is guaranteed by design. Two different types of jitter can exist on the input to CORE\_SYSCLK, systemic and true random jitter. True random jitter is rejected. Systemic jitter is passed into and through the PLL to the internal clock circuitry.

<sup>3</sup> Relock time is guaranteed by design and characterization. PLL-relock time is the maximum amount of time required for the PLL lock after a stable VDD and CORE\_SYSCLKare reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep modes.

# 1.2.4 e300 Core PLL Electrical Characteristics

The internal clocking of the e300 core is generated from and synchronized to the system clock by means of a voltage-controlled core PLL.

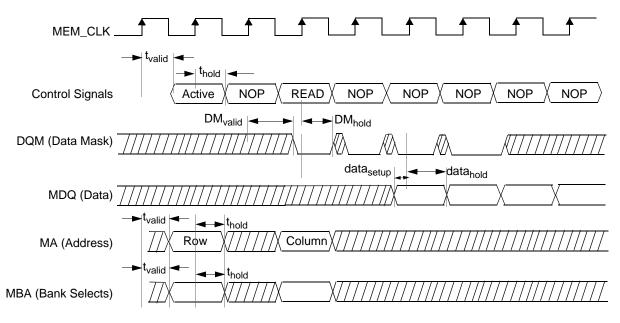

NOTE: Control Signals are composed of RAS, CAS, MEM\_WE, MEM\_CS, MEM\_CS1 and CLK\_EN

#### Figure 5. Timing Diagram—Standard SDRAM Memory Read Timing

### 1.3.6.2 Memory Interface Timing-Standard SDRAM Write Command

In Standard SDRAM, all signals are activated on the MEM\_CLK from the Memory Controller and captured on the MEM\_CLK clock at the memory device.

| Sym                   | Description                                                            | Min                              | Мах                              | Units | SpecID |

|-----------------------|------------------------------------------------------------------------|----------------------------------|----------------------------------|-------|--------|

| t <sub>mem_clk</sub>  | MEM_CLK period                                                         | 7.5                              | _                                | ns    | A5.8   |

| t <sub>valid</sub>    | Control Signals, Address and MBA Valid<br>after rising edge of MEM_CLK | _                                | t <sub>mem_clk</sub> × 0.5 + 0.4 | ns    | A5.9   |

| t <sub>hold</sub>     | Control Signals, Address and MBA Hold after rising edge of MEM_CLK     | t <sub>mem_clk</sub> × 0.5       | —                                | ns    | A5.10  |

| DM <sub>valid</sub>   | DQM valid after rising edge of MEM_CLK                                 | —                                | $t_{mem\_clk} \times 0.25 + 0.4$ | ns    | A5.11  |

| DM <sub>hold</sub>    | DQM hold after rising edge of Mem_clk                                  | $t_{mem\_clk} \times 0.25 - 0.7$ | —                                | ns    | A5.12  |

| data <sub>valid</sub> | MDQ valid after rising edge of MEM_CLK                                 | —                                | $t_{mem_clk} \times 0.75 + 0.4$  | ns    | A5.13  |

| data <sub>hold</sub>  | MDQ hold after rising edge of MEM_CLK                                  | $t_{mem\_clk} \times 0.75 - 0.7$ | —                                | ns    | A5.14  |

Table 19. Standard SDRAM Write Timing

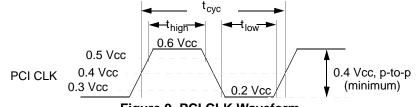

Figure 9. PCI CLK Waveform

#### Table 22. PCI CLK Specifications

| Sym               | Description                        | 66 MHz |     | 33 MHz |     | MHz 33 MHz |         | Units  | Notes | SpecID |

|-------------------|------------------------------------|--------|-----|--------|-----|------------|---------|--------|-------|--------|

| Sym               | Description                        | Min    | Max | Min    | Max | Units      | NOLES   | Specin |       |        |

| t <sub>cyc</sub>  | PCI CLK Cycle Time                 | 15     | 30  | 30     | —   | ns         | (1),(3) | A6.1   |       |        |

| t <sub>high</sub> | PCI CLK High Time                  | 6      | —   | 11     | —   | ns         | _       | A6.2   |       |        |

| t <sub>low</sub>  | PCI CLK Low Time                   | 6      | —   | 11     | —   | ns         | _       | A6.3   |       |        |

| —                 | PCI CLK Slew Rate                  | 1.5    | 4   | 1      | 4   | V/ns       | (2)     | A6.4   |       |        |

| —                 | PCI Clock Jitter<br>(peak to peak) | —      | 200 |        | 200 | ps         |         | _      |       |        |

#### NOTES:

1. In general, all 66 MHz PCI components must work with any clock frequency up to 66 MHz. CLK requirements vary depending upon whether the clock frequency is above 33 MHz.

- 2. Rise and fall times are specified in terms of the edge rate measured in V/ns. This slew rate must be met across the minimum peak-to-peak portion of the clock waveform as shown in Figure 9.

- 3. The minimum clock period must not be violated for any single clock cycle, i.e., accounting for all system jitter.

**Table 23. PCI Timing Parameters**

| Sym                    | Description                                  | 66 I | 66 MHz |       | 33 MHz |       | Notes       | SpecID |

|------------------------|----------------------------------------------|------|--------|-------|--------|-------|-------------|--------|

| Oym                    | Description                                  | Min  | Max    | Min   | Max    | Units | Notes       | Opecid |

| t <sub>val</sub>       | CLK to Signal Valid Delay —<br>bused signals | 2    | 6      | 2     | 11     | ns    | (1),(2),(3) | A6.5   |

| t <sub>val</sub> (ptp) | CLK to Signal Valid Delay — point to point   | 2    | 6      | 2     | 12     | ns    | (1),(2),(3) | A6.6   |

| t <sub>on</sub>        | Float to Active Delay                        | 2    | —      | 2     | _      | ns    | (1)         | A6.7   |

| t <sub>off</sub>       | Active to Float Delay                        |      | 14     |       | 28     | ns    | (1)         | A6.8   |

| t <sub>su</sub>        | Input Setup Time to CLK —<br>bused signals   | 3    |        | 7     | —      | ns    | (3),(4)     | A6.9   |

| t <sub>su</sub> (ptp)  | Input Setup Time to CLK — point to point     | 5    |        | 10,12 |        | ns    | (3),(4)     | A6.10  |

| t <sub>h</sub>         | Input Hold Time from CLK                     | 0    | —      | 0     | —      | ns    | (4)         | A6.11  |

#### NOTES:

1. See the timing measurement conditions in the PCI Local Bus Specification. It is important that all driven signal transitions drive to their Voh or Vol level within one Tcyc.

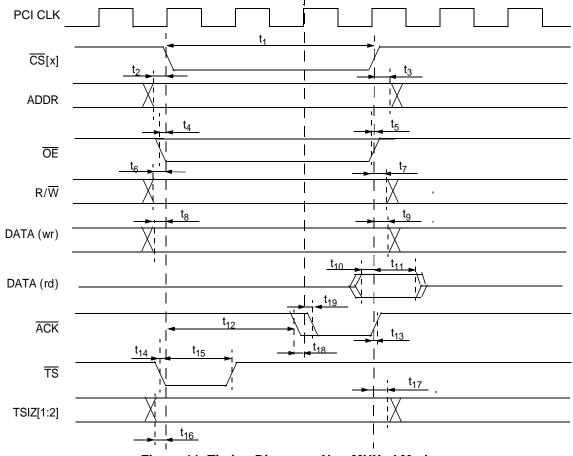

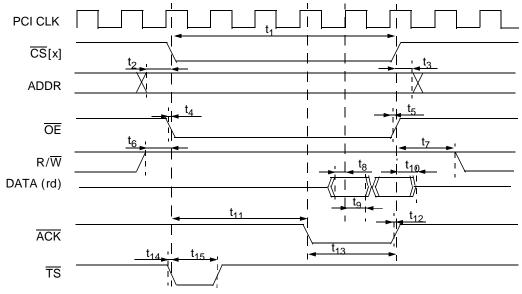

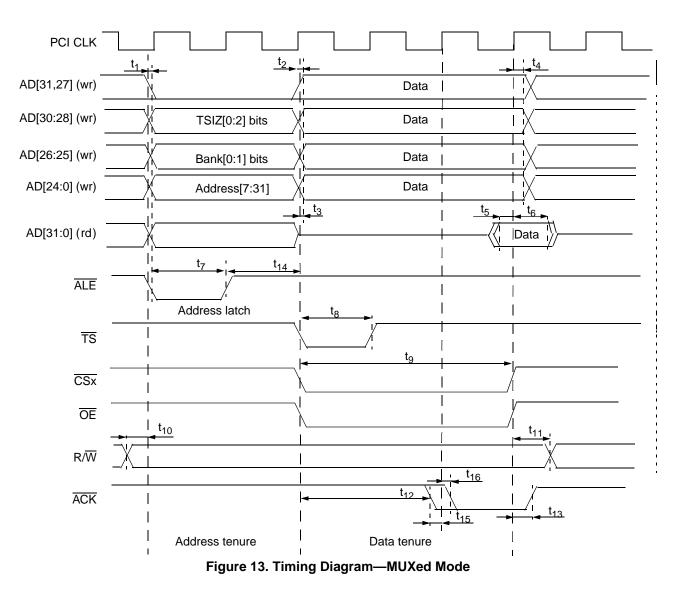

Figure 11. Timing Diagram—Non-MUXed Mode

## 1.3.8.2 Burst Mode

Table 25. Burst Mode Timing

| Sym              | Description                                | Min                                                              | Max                                                                                                                      | Units | Notes   | SpecID |

|------------------|--------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------|---------|--------|

| t <sub>CSA</sub> | PCI CLK to CS assertion                    | 4.6                                                              | 10.6                                                                                                                     | ns    |         | A7.22  |

| t <sub>CSN</sub> | PCI CLK to CS negation                     | 2.9                                                              | 7.0                                                                                                                      | ns    | —       | A7.23  |

| t <sub>1</sub>   | CS pulse width                             | (1 + WS + 4 <sup>LB</sup> × 2<br>× (32/DS)) × t <sub>PCIck</sub> | $\begin{array}{c} (1 + \text{WS} + 4^{\text{LB}} \times 2 \times \\ (32/\text{DS})) \times t_{\text{PClck}} \end{array}$ | ns    | (1),(2) | A7.24  |

| t <sub>2</sub>   | ADDR valid before CS assertion             | t <sub>IPBIck</sub>                                              | t <sub>PClck</sub>                                                                                                       | ns    |         | A7.25  |

| t <sub>3</sub>   | ADDR hold after CS negation                | -0.7                                                             | —                                                                                                                        | ns    | _       | A7.26  |

| t <sub>4</sub>   | OE assertion before CS assertion           | —                                                                | 4.8                                                                                                                      | ns    | _       | A7.27  |

| t <sub>5</sub>   | OE negation before CS negation             | _                                                                | 2.7                                                                                                                      | ns    |         | A7.28  |

| t <sub>6</sub>   | RW valid before CS assertion               | t <sub>PClck</sub>                                               | _                                                                                                                        | ns    | _       | A7.29  |

| t <sub>7</sub>   | RW hold after CS negation                  | t <sub>PClck</sub>                                               | —                                                                                                                        | ns    | —       | A7.30  |

| t <sub>8</sub>   | DATA setup before rising edge of PCI clock | 3.6                                                              | —                                                                                                                        | ns    | —       | A7.31  |

| Sym             | Description                              | Min                                               | Max                                               | Units | Notes   | SpecID |

|-----------------|------------------------------------------|---------------------------------------------------|---------------------------------------------------|-------|---------|--------|

| t <sub>9</sub>  | DATA hold after rising edge of PCI clock | 0                                                 |                                                   | ns    |         | A7.32  |

| t <sub>10</sub> | DATA hold after CS negation              | 0                                                 | (DC + 1) × t <sub>PClck</sub>                     | ns    | (4)     | A7.33  |

| t <sub>11</sub> | ACK assertion after CS assertion         | —                                                 | $(WS + 1) \times t_{PClck}$                       | ns    | _       | A7.34  |

| t <sub>12</sub> | ACK negation before CS negation          | —                                                 | 7.0                                               | ns    | (3)     | A7.35  |

| t <sub>13</sub> | ACK pulse width                          | $4^{LB} \times 2 \times (32/DS) \times t_{PClck}$ | $4^{LB} \times 2 \times (32/DS) \times t_{PCIck}$ | ns    | (2),(3) | A7.36  |

| t <sub>14</sub> | CS assertion after TS assertion          | —                                                 | 2.5                                               | ns    | _       | A7.37  |

| t <sub>15</sub> | TS pulse width                           | t <sub>PClck</sub>                                | t <sub>PClck</sub>                                | ns    | —       | A7.38  |

#### Table 25. Burst Mode Timing (continued)

NOTES:

- 1. Wait States (WS) can be programmed in the Chip Select X Register, Bit field WaitP and WaitX. It can be specified from 0–65535.

- 2. Example:

Long Burst is used, this means the CS related BERx and SLB bits of the Chip Select Burst Control Register are set and a burst on the internal XLB is executed. => LB = 1

Data bus width is 8 bit.  $\Rightarrow$  DS = 8

$=> 4^1 \times 2 \times (32/8) = 32 =>$  ACK is asserted for 32 PCI cycles to transfer one cache line.

Wait State is set to 10. => WS = 10

$1 + 10 + 32 = 43 \Rightarrow CS$  is asserted for 43 PCI cycles.

- 3. ACK is output and indicates the burst.

- 4. Deadcycles are only used, if no arbitration to an other module (ATA or PCI) of the shared local bus happens. If arbitration happens the bus can be driven within 4 IPB clocks by an other modules.

Figure 12. Timing Diagram—Burst Mode

MPC5200B Data Sheet, Rev. 4

# 1.3.9 ATA

The MPC5200B ATA Controller is completely software programmable. It can be programmed to operate with ATA protocols using their respective timing, as described in the ANSI ATA-4 specification. The ATA interface is completely asynchronous in nature. Signal relationships are based on specific fixed timing in terms of timing units (nanoseconds).

ATA data setup and hold times, with respect to Read/Write strobes, are software programmable inside the ATA Controller. Data setup and hold times are implemented using counters. The counters count the number of ATA clock cycles needed to meet the ANSI ATA-4 timing specifications. For details, see the ANSI ATA-4 specification and how to program an ATA Controller and ATA drive for different ATA protocols and their respective timing. See the *MPC5200B User's Manual (MPC5200BUM)*.

The MPC5200B ATA Host Controller design makes data available coincidentally with the active edge of the WRITE strobe in PIO and Multiword DMA modes.

- Write data is latched by the drive at the inactive edge of the WRITE strobe. This gives ample setup time beyond that required by the ATA-4 specification.

- Data is held unchanged until the next active edge of the WRITE strobe. This gives ample hold time beyond that required by the ATA-4 specification.

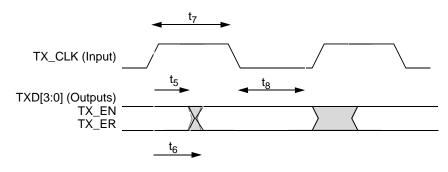

| Sym            | Description                                             | Min | Max | Unit                         | SpecID |

|----------------|---------------------------------------------------------|-----|-----|------------------------------|--------|

| t <sub>5</sub> | TX_CLK rising edge to TXD[3:0], TX_EN, TX_ER<br>invalid | 5   | _   | ns                           | A9.5   |

| t <sub>6</sub> | TX_CLK rising edge to TXD[3:0], TX_EN, TX_ER valid      | _   | 25  | ns                           | A9.6   |

| t <sub>7</sub> | TX_CLK pulse width high                                 | 35% | 65% | TX_CLK Period <sup>(1)</sup> | A9.7   |

| t <sub>8</sub> | TX_CLK pulse width low                                  | 35% | 65% | TX_CLK Period <sup>(1)</sup> | A9.8   |

#### Table 32. MII Tx Signal Timing

<sup>1</sup> The TX\_CLK frequency shall be 25% of the nominal transmit frequency, e.g., a PHY operating at 100 Mb/s must provide a TX\_CLK frequency of 25 MHz and a PHY operating at 10 Mb/s must provide a TX\_CLK frequency of 2.5 MHz. See the IEEE 802.3 Specification.

#### Figure 28. Ethernet Timing Diagram—MII Tx Signal

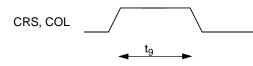

#### Table 33. MII Async Signal Timing

| Sym            | Description                  | Min | Мах | Unit          | SpecID |

|----------------|------------------------------|-----|-----|---------------|--------|

| t <sub>9</sub> | CRS, COL minimum pulse width | 1.5 |     | TX_CLK Period | A9.9   |

Figure 29. Ethernet Timing Diagram—MII Async

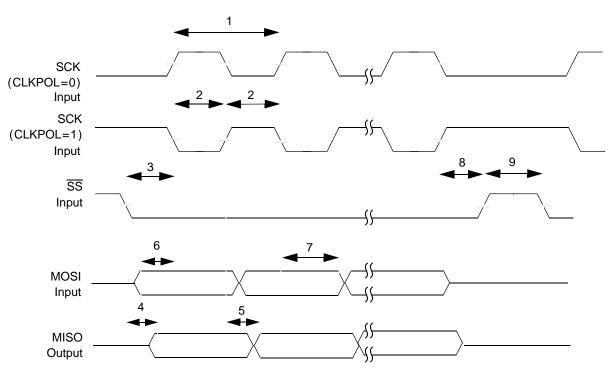

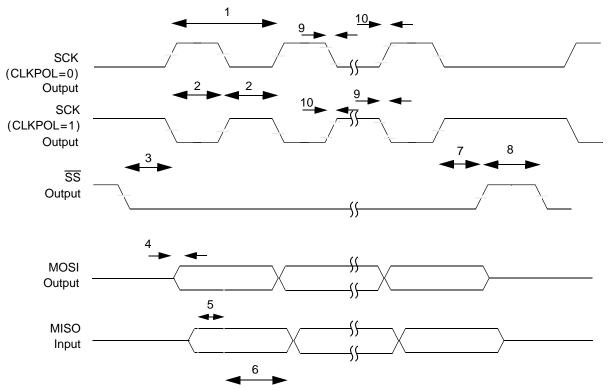

Figure 33. Timing Diagram — SPI Slave Mode, Format 0 (CPHA = 0)

| Та  | Table 38. Timing Specifications — SPI Master Mode, Format 1 (CPHA = 1) |      |      |                             |        |  |  |  |

|-----|------------------------------------------------------------------------|------|------|-----------------------------|--------|--|--|--|

| Sym | Description                                                            | Min  | Max  | Units                       | SpecID |  |  |  |

| 1   | Cycle time                                                             | 4    | 1024 | IP-Bus Cycle <sup>(1)</sup> | A11.21 |  |  |  |

| 2   | Clock high or low time                                                 | 2    | 512  | IP-Bus Cycle <sup>(1)</sup> | A11.22 |  |  |  |

| 3   | Slave select to clock delay                                            | 15.0 | —    | ns                          | A11.23 |  |  |  |

| 4   | Output data valid                                                      | —    | 20.0 | ns                          | A11.24 |  |  |  |

| 5   | Input Data setup time                                                  | 20.0 | —    | ns                          | A11.25 |  |  |  |

| 6   | Input Data hold time                                                   | 20.0 |      | ns                          | A11.26 |  |  |  |

| 7   | Slave disable lag time                                                 | 15.0 | —    | ns                          | A11.27 |  |  |  |

| 8   | Sequential Transfer delay                                              | 1    | —    | IP-Bus Cycle <sup>(1)</sup> | A11.28 |  |  |  |

| 9   | Clock falling time                                                     | —    | 7.9  | ns                          | A11.29 |  |  |  |

| 10  | Clock rising time                                                      |      | 7.9  | ns                          | A11.30 |  |  |  |

Inter Peripheral Clock is defined in the MPC5200B User's Manual (MPC5200BUM).

#### NOTE

Output timing is specified at a nominal 50 pF load.

1

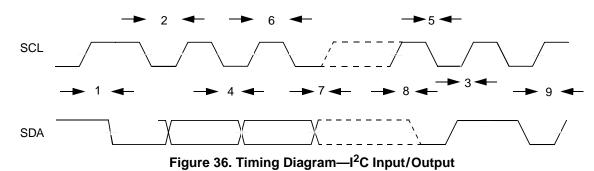

| Sym              | Description                                                    | Min | Мах | Units                       | SpecID |

|------------------|----------------------------------------------------------------|-----|-----|-----------------------------|--------|

| 1 <sup>(1)</sup> | Start condition hold time                                      | 6   | —   | IP-Bus Cycle <sup>(3)</sup> | A13.8  |

| 2 <sup>(1)</sup> | Clock low time                                                 | 10  | —   | IP-Bus Cycle <sup>(3)</sup> | A13.9  |

| 3 <sup>(2)</sup> | SCL/SDA rise time                                              |     | 7.9 | ns                          | A13.10 |

| 4 <sup>(1)</sup> | Data hold time                                                 | 7   | —   | IP-Bus Cycle <sup>(3)</sup> | A13.11 |

| 5 <sup>(1)</sup> | SCL/SDA fall time                                              |     | 7.9 | ns                          | A13.12 |

| 6 <sup>(1)</sup> | Clock high time                                                | 10  | —   | IP-Bus Cycle <sup>(3)</sup> | A13.13 |

| 7 <sup>(1)</sup> | Data setup time                                                | 2   |     | IP-Bus Cycle <sup>(3)</sup> | A13.14 |

| 8 <sup>(1)</sup> | Start condition setup time (for repeated start condition only) | 20  | —   | IP-Bus Cycle <sup>(3)</sup> | A13.15 |

| 9 <sup>(1)</sup> | Stop condition setup time                                      | 10  | —   | IP-Bus Cycle <sup>(3)</sup> | A13.16 |

<sup>1</sup> Programming IFDR with the maximum frequency (IFDR=0x20) results in the minimum output timings listed. The I<sup>2</sup>C interface is designed to scale the data transition time, moving it to the middle of the SCL low period. The actual position is affected by the prescale and division values programmed in IFDR.

<sup>2</sup> Because SCL and SDA are open-drain-type outputs, which the processor can only actively drive low, the time SCL or SDA takes to reach a high level depends on external signal capacitance and pull-up resistor values.

<sup>3</sup> Inter Peripheral Clock is defined in the MPC5200B User's Manual (MPC5200BUM).

#### NOTE

Output timing is specified at a nominal 50 pF load.

### 1.3.15 J1850

See the MPC5200B User's Manual (MPC5200BUM).

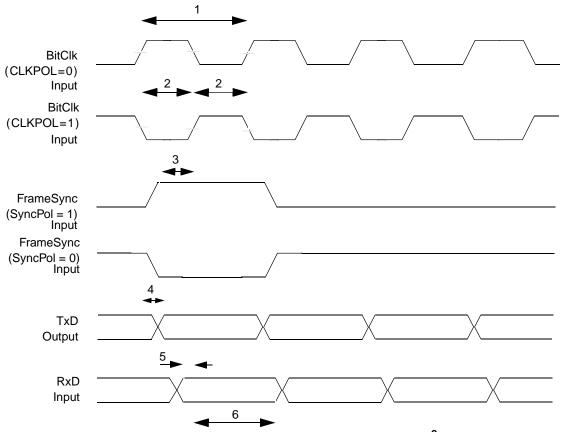

| Sym     | Description                        | Min  | Тур | Max  | Units            | SpecID |

|---------|------------------------------------|------|-----|------|------------------|--------|

| 1       | Bit Clock cycle time               | 40.0 | —   | —    | ns               | A15.9  |

| 2       | Clock duty cycle                   |      | 50  | —    | % <sup>(1)</sup> | A15.10 |

| 3       | FrameSync setup time               | 1.0  | —   | _    | ns               | A15.11 |

| 4       | Output Data valid after clock edge | —    | —   | 14.0 | ns               | A15.12 |

| 5       | Input Data setup time              | 1.0  | —   | _    | ns               | A15.13 |

| 6       | Input Data hold time               | 1.0  | —   | —    | ns               | A15.14 |

| 1 Bit C | lock cycle time                    | •    | •   | •    | •                | •      |

# Table 43. Timing Specifications — 8-, 16-, 24-, and 32-bit CODEC / $\rm I^2S$ Slave Mode

Bit Clock cycle time.

#### NOTE

Output timing is specified at a nominal 50 pF load.

Figure 38. Timing Diagram — 8-, 16-, 24-, and 32-bit CODEC / I<sup>2</sup>S Slave Mode

MPC5200B Data Sheet, Rev. 4

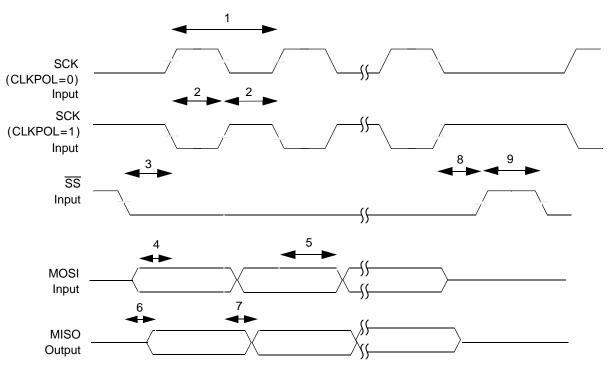

Figure 42. Timing Diagram — SPI Slave Mode, Format 0 (CPHA = 0)

| Table 48. Timing Specifications - | – SPI Master Mode, Format 1 (0 | CPHA = 1) |

|-----------------------------------|--------------------------------|-----------|

|-----------------------------------|--------------------------------|-----------|

| Sym | Description                                                            | Min  | Max | Units | SpecID |

|-----|------------------------------------------------------------------------|------|-----|-------|--------|

| 1   | SCK cycle time, programable in the PSC CCS register                    | 30.0 | —   | ns    | A15.46 |

| 2   | SCK pulse width, 50% SCK duty cycle                                    | 15.0 | _   | ns    | A15.47 |

| 3   | Slave select clock delay, programable in the PSC CCS register          | 30.0 | —   | ns    | A15.48 |

| 4   | Output data valid                                                      | _    | 8.9 | ns    | A15.49 |

| 5   | Input Data setup time                                                  | 6.0  | —   | ns    | A15.50 |

| 6   | Input Data hold time                                                   | 1.0  | —   | ns    | A15.51 |

| 7   | Slave disable lag time                                                 | _    | 8.9 | ns    | A15.52 |

| 8   | Sequential Transfer delay, programable in the PSC CTUR / CTLR register | 15.0 | —   | ns    | A15.53 |

| 9   | Clock falling time                                                     | _    | 7.9 | ns    | A15.54 |

| 10  | Clock rising time                                                      |      | 7.9 | ns    | A15.55 |

### NOTE

Output timing is specified at a nominal 50 pF load.

| Table 49. Timing Specifications — SPI Slave Mode, Format 1 ( | (CPHA = 1)                                     | ) |

|--------------------------------------------------------------|------------------------------------------------|---|

|                                                              | <b>O</b> I I I I I I I I I I I I I I I I I I I | , |

| Sym | Description                                                             |      | Max  | Units | SpecID |

|-----|-------------------------------------------------------------------------|------|------|-------|--------|

| 1   | SCK cycle time, programable in the PSC CCS register                     | 30.0 |      | ns    | A15.56 |

| 2   | SCK pulse width, 50% SCK duty cycle                                     | 15.0 |      | ns    | A15.57 |

| 3   | Slave select clock delay                                                | 0.0  | _    | ns    | A15.58 |

| 4   | Output data valid                                                       |      | 14.0 | ns    | A15.59 |

| 5   | Input Data setup time                                                   | 2.0  | _    | ns    | A15.60 |

| 6   | Input Data hold time                                                    | 1.0  | _    | ns    | A15.61 |

| 7   | Slave disable lag time                                                  |      | _    | ns    | A15.62 |

| 8   | Minimum Sequential Transfer delay = $2 \times IP$ -Bus clock cycle time | 30.0 | _    | ns    | A15.63 |

### NOTE

Output timing is specified at a nominal 50 pF load.

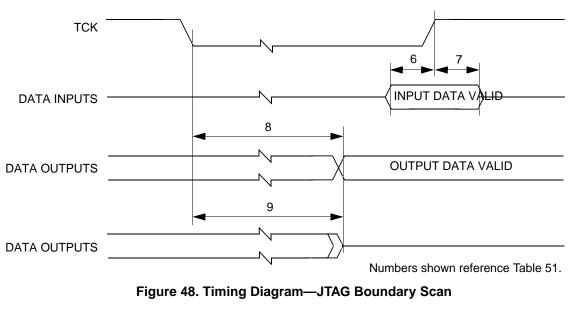

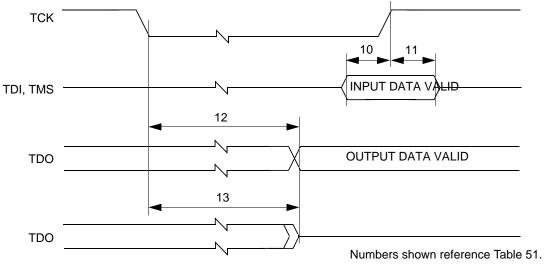

Figure 49. Timing Diagram—Test Access Port

# 2 Package Description

# 2.1 Package Parameters

The MPC5200B uses a 27 mm x 27 mm TE-PBGA package. The package parameters are as provided in the following list:

- Package outline: 27 mm x 27 mm

- Interconnects: 2

- Pitch: 1.27 mm

| Name          | Alias                   | Туре | Power Supply | Output Driver<br>Type | Input<br>Type | Pull-up/<br>down |

|---------------|-------------------------|------|--------------|-----------------------|---------------|------------------|

| PCI_TRDY      |                         | I/O  | VDD_IO       | PCI                   | PCI           |                  |

|               |                         |      | Local Plus   | •                     |               |                  |

| LP_ACK        |                         | I/O  | VDD_IO       | DRV8                  | TTL           | PULLUP           |

| LP_ALE        |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| LP_OE         |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| LP_RW         |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| LP_TS         |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| LP_CS0        |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| LP_CS1        |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| LP_CS2        |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| LP_CS3        |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| LP_CS4        |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| LP_CS5        |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

|               |                         |      | ATA          |                       |               |                  |

| ATA_DACK      |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| ATA_DRQ       |                         | I/O  | VDD_IO       | DRV8                  | TTL           | PULLDOWN         |

| ATA_INTRQ     |                         | I/O  | VDD_IO       | DRV8                  | TTL           | PULLDOWN         |

| ATA_IOCHRDY   |                         | I/O  | VDD_IO       | DRV8                  | TTL           | PULLUP           |

| ATA_IOR       |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| ATA_IOW       |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

| ATA_ISOLATION |                         | I/O  | VDD_IO       | DRV8                  | TTL           |                  |

|               |                         |      | Ethernet     |                       |               |                  |

| ETH_0         | TX, TX_EN               | I/O  | VDD_IO       | DRV4                  | TTL           |                  |

| ETH_1         | RTS, TXD[0]             | I/O  | VDD_IO       | DRV4                  | TTL           |                  |

| ETH_2         | USB_TXP, RTX,<br>TXD[1] | I/O  | VDD_IO       | DRV4                  | TTL           |                  |

| ETH_3         | USB_PRTPWR,<br>TXD[2]   | I/O  | VDD_IO       | DRV4                  | TTL           |                  |

| ETH_4         | USB_SPEED,<br>TXD[3]    | I/O  | VDD_IO       | DRV4                  | TTL           |                  |

| ETH_5         | USB_SUPEND,<br>TX_ER    | I/O  | VDD_IO       | DRV4                  | TTL           |                  |

| ETH_6         | USB_OE, RTS,<br>MDC     | I/O  | VDD_IO       | DRV4                  | TTL           |                  |

| ETH_7         | TXN, MDIO               | I/O  | VDD_IO       | DRV4                  | TTL           |                  |

### Table 52. MPC5200B Pinout Listing (continued)

| Name   | Alias                       | Туре | Power Supply     | Output Driver<br>Type | Input<br>Type | Pull-up/<br>down |

|--------|-----------------------------|------|------------------|-----------------------|---------------|------------------|

| ETH_8  | RX_DV                       | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| ETH_9  | CD, RX_CLK                  | I/O  | VDD_IO           | DRV4                  | Schmitt       |                  |

| ETH_10 | CTS, COL                    | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| ETH_11 | TX_CLK                      | I/O  | VDD_IO           | DRV4                  | Schmitt       |                  |

| ETH_12 | RXD[0]                      | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| ETH_13 | USB_RXD, CTS,<br>RXD[1]     | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| ETH_14 | USB_RXP,<br>UART_RX, RXD[2] | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| ETH_15 | USB_RXN, RX,<br>RXD[3]      | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| ETH_16 | USB_OVRCNT,<br>CTS, RX_ER   | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| ETH_17 | CD, CRS                     | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

|        |                             |      | IRDA             |                       |               |                  |

| PSC6_0 | IRDA_RX, RxD                | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| PSC6_1 | Frame, CTS                  | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| PSC6_2 | IRDA_TX, TxD                | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| PSC6_3 | IR_USB_CLK,BitC<br>Ik, RTS  | I/O  | VDD_IO           | DRV4                  | Schmitt       |                  |

|        |                             |      | USB              |                       |               |                  |

| USB_0  | USB_OE                      | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| USB_1  | USB_TXN                     | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| USB_2  | USB_TXP                     | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| USB_3  | USB_RXD                     | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| USB_4  | USB_RXP                     | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| USB_5  | USB_RXN                     | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| USB_6  | USB_PRTPWR                  | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| USB_7  | USB_SPEED                   | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| USB_8  | USB_SUPEND                  | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

| USB_9  | USB_OVRCNT                  | I/O  | VDD_IO           | DRV4                  | TTL           |                  |

|        |                             |      | l <sup>2</sup> C |                       |               |                  |

| I2C_0  | SCL                         | I/O  | VDD_IO           | DRV4                  | Schmitt       |                  |

| I2C_1  | SDA                         | I/O  | VDD_IO           | DRV4                  | Schmitt       |                  |

| I2C_2  | SCL                         | I/O  | VDD_IO           | DRV4                  | Schmitt       |                  |

#### Table 52. MPC5200B Pinout Listing (continued)

MPC5200B Data Sheet, Rev. 4

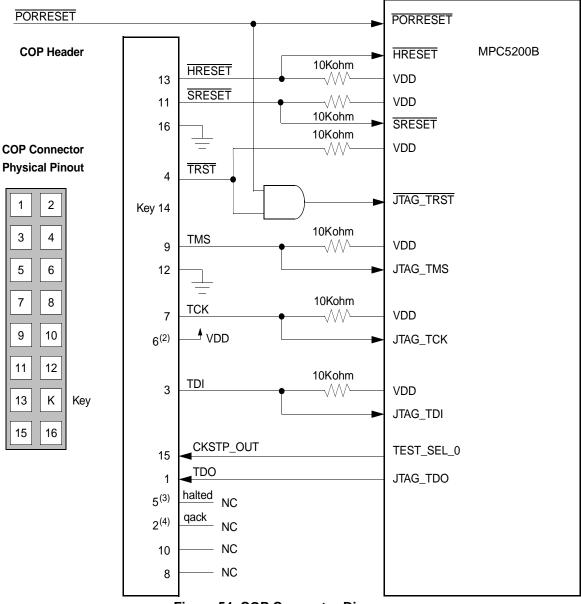

Normally this interface is implemented, using a COP (common on-chip processor) connector. The COP allows a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the MPC5200B.

# 3.4.2 e300 COP/BDM Interface

There are two possibilities to connect the JTAG interface: using it with a COP connector and without a COP connector.

## 3.4.2.1 Boards Interfacing the JTAG Port via a COP Connector

The MPC5200B functional pin interface and internal logic provides access to the embedded e300 processor core through the Freescale (formerly Motorola) standard COP/BDM interface. Table 53 gives the COP/BDM interface signals. The pin order shown reflects only the COP/BDM connector order.

| BDM<br>Pin # | MPC5200B<br>I/O Pin | BDM<br>Connector    | Internal<br>Pull Up/Down | External<br>Pull Up/Down | I/O <sup>1</sup> |

|--------------|---------------------|---------------------|--------------------------|--------------------------|------------------|

| 16           | _                   | GND                 | _                        |                          | _                |

| 15           | TEST_SEL_0          | ckstp_out           | _                        | _                        | I                |

| 14           | _                   | KEY                 | _                        | _                        | _                |

| 13           | HRESET              | hreset              | —                        | 10k Pull-Up              | 0                |

| 12           | _                   | GND                 | —                        | _                        | —                |

| 11           | SRESET              | sreset              | _                        | 10k Pull-Up              | 0                |

| 10           | _                   | N/C                 | —                        | _                        | —                |

| 9            | JTAG_TMS            | tms                 | 100k Pull-Up             | 10k Pull-Up              | 0                |

| 8            | —                   | N/C                 | —                        | —                        | —                |

| 7            | JTAG_TCK            | tck                 | 100k Pull-Up             | 10k Pull-Up              | 0                |

| 6            | _                   | VDD <sup>2</sup>    | —                        |                          | —                |

| 5            | _                   | halted <sup>3</sup> | _                        |                          | I                |

| 4            | JTAG_TRST           | trst                | 100k Pull-Up             | 10k Pull-Up              | 0                |

| 3            | JTAG_TDI            | tdi                 | 100k Pull-Up             | 10k Pull-Up              | 0                |

| 2            |                     | qack <sup>4</sup>   | _                        | —                        | 0                |

| 1            | JTAG_TDO            | tdo                 | —                        | —                        | I                |

Table 53. COP/BDM Interface Signals

<sup>1</sup> With respect to the emulator tool's perspective, Input is really an output from the embedded e300 core and output is really an input to the core.

<sup>2</sup> From the board under test, power sense for chip power.

<sup>3</sup> HALTED is not available from e300 core.

<sup>4</sup> Input to the e300 core to enable/disable soft-stop condition during breakpoints. MPC5200B internally ties CORE\_QACK to GND in its normal/functional mode (always asserted).

For a board with a COP (common on-chip processor) connector, which accesses the JTAG interface and which needs to reset the JTAG module, simply wiring JTAG\_TRST and PORRESET is not recommended.

To reset the MPC5200B via the COP connector, the HRESET pin of the COP should be connected to the HRESET pin of the MPC5200B. The circuitry shown in Figure 54 allows the COP to assert HRESET or JTAG\_TRST separately, while any other board sources can drive PORRESET.

Figure 54. COP Connector Diagram

### **3.4.2.2 Boards Without COP Connector**

If the JTAG interface is not used, JTAG\_TRST should be tied to PORRESET, so that it is asserted when the system reset signal (PORRESET) is asserted. This ensures that the JTAG scan chain is initialized during power on. Figure 55 shows the connection of the JTAG interface without COP connector.

MPC5200B Data Sheet, Rev. 4