Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core ProcessorSTM8Core Size8-BitSpeed16MHzConnectivityIPC, IrDA, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, IR, LCD, POR, PWM, WDTNumber of I/O54Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size256 x 8Nutage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                           | Details                    |                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------|

| Core Size8-BitSpeed16MHzConnectivityI*C, IrDA, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, IR, LCD, POR, PWM, WDTNumber of I/O54Program Memory Size64KB (64K × 8)Program Memory TypeFLASHEEPROM Size256 × 8RAM Size4K × 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10) | Product Status             | Active                                                                 |

| Speed16MHzConnectivityPC, IrDA, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, IR, LCD, POR, PWM, WDTNumber of I/O54Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size256 x 8RAM Size4K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                             | Core Processor             | STM8                                                                   |

| ProductivityPC, IrDA, SPI, UART/USARTPeripheralsBrown-out Detect/Reset, DMA, IR, LCD, POR, PWM, WDTNumber of I/O54Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size256 x 8RAM Size4K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                       | Core Size                  | 8-Bit                                                                  |

| PeripheralsBrown-out Detect/Reset, DMA, IR, LCD, POR, PWM, WDTNumber of I/O54Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size256 x 8RAM Size4K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                            | Speed                      | 16MHz                                                                  |

| Number of I/O54Program Memory Size64KB (64K × 8)Program Memory TypeFLASHEEPROM Size256 × 8RAM Size4K × 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type64-LQFPSuppler Device Package64-LQFP (10x10)                                                                                                                                                        | Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                |

| Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size256 x 8RAM Size4K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                                                         | Peripherals                | Brown-out Detect/Reset, DMA, IR, LCD, POR, PWM, WDT                    |

| Program Memory TypeFLASHEEPROM Size256 x 8RAM Size4K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                            | Number of I/O              | 54                                                                     |

| EEPROM Size256 x 8RAM Size4K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                                                                                                                  | Program Memory Size        | 64KB (64K x 8)                                                         |

| RAM Size4K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                                                                                                                                    | Program Memory Type        | FLASH                                                                  |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                    | EEPROM Size                | 256 x 8                                                                |

| Data ConvertersA/D 28x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                         | RAM Size                   | 4K x 8                                                                 |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                  | Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Operating Temperature     -40°C ~ 85°C (TA)       Mounting Type     Surface Mount       Package / Case     64-LQFP       Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                                                                                                | Data Converters            | A/D 28x12b                                                             |

| Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                               | Oscillator Type            | Internal                                                               |

| Package / Case     64-LQFP       Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                        | Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                                         | Mounting Type              | Surface Mount                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Package / Case             | 64-LQFP                                                                |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l052r8t6tr                                                                                                                                                                                                                                                                                                                                                                 | Supplier Device Package    | 64-LQFP (10x10)                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l052r8t6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This document describes the features, pinout, mechanical data and ordering information of the high density value line STM8L052R8 microcontroller with a Flash memory density of 64 Kbytes.

For further details on the whole STMicroelectronics high density family please refer to *Section 2.2: Ultra low power continuum*.

For detailed information on device operation and registers, refer to the reference manual (RM0031).

For information on to the Flash program memory and data EEPROM, refer to the programming manual (PM0054).

For information on the debug module and SWIM (single wire interface module), refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

For information on the STM8 core, refer to the STM8 CPU programming manual (PM0044).

High density value line devices provide the following benefits:

- Integrated system

- 64 Kbytes of high density embedded Flash program memory

- 256 bytes of data EEPROM

- 4 Kbytes of RAM

- Internal high speed and low-power low speed RC

- Embedded reset

- Ultra low power consumption

- 1 µA in Active-halt mode

- Clock gated system and optimized power management

- Capability to execute from RAM for Low power wait mode and low power run mode

- Advanced features

- Up to 16 MIPS at 16 MHz CPU clock frequency

- Direct memory access (DMA) for memory-to-memory or peripheral-to-memory access

- Short development cycles

- Application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals

- Wide choice of development tools

These features make the value line STM8L05xxx ultra low power microcontroller family suitable for a wide range of consumer and mass market applications.

Refer to *Table 1: High density value line STM8L05xxx low power device features and peripheral counts* and *Section 3: Functional overview* for an overview of the complete range of peripherals proposed in this family.

*Figure 1* shows the block diagram of the high density value line STM8L05xxx family.

# 2 Description

The high density value line STM8L05xxx devices are members of the STM8L ultra low power 8-bit family.

The value line STM8L05xxx ultra low power family features the enhanced STM8 CPU core providing increased processing power (up to 16 MIPS at 16 MHz) while maintaining the advantages of a CISC architecture with improved code density, a 24-bit linear addressing space and an optimized architecture for low power operations.

The family includes an integrated debug module with a hardware interface (SWIM) which allows non-intrusive In-application debugging and ultra-fast Flash programming.

High density value line STM8L05xxx microcontrollers feature embedded data EEPROM and low-power, low-voltage, single-supply program Flash memory.

All devices offer 12-bit ADC, real-time clock, four 16-bit timers, one 8-bit timer as well as standard communication interface such as two SPIs, I2C, three USARTs and 8x24 or 4x28-segment LCD. The 8x24 or 4x 28-segment LCD is available on the high density value line STM8L05xxx.

The STM8L05xxx family operates from 1.8 V to 3.6 V and is available in the -40 to +85 °C temperature range.

The modular design of the peripheral set allows the same peripherals to be found in different ST microcontroller families including 32-bit families. This makes any transition to a different family very easy, and simplified even more by the use of a common set of development tools.

All value line STM8L ultra low power products are based on the same architecture with the same memory mapping and a coherent pinout.

# 3.2 Central processing unit STM8

## 3.2.1 Advanced STM8 Core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16-Mbyte linear memory space

- 16-bit stack pointer access to a 64-Kbyte level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for lookup tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

## 3.2.2 Interrupt controller

The high density value line STM8L05xxx devices feature a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 32 interrupt vectors with hardware priority

- Up to 40 external interrupt sources on 11 vectors

- Trap and reset interrupts

# 3.9 Analog-to-digital converter

- 12-bit analog-to-digital converter (ADC1) with 27 channels (including 4 fast channels) and internal reference voltage

- Conversion time down to 1 µs with f<sub>SYSCLK</sub>= 16 MHz

- Programmable resolution

- Programmable sampling time

- Single and continuous mode of conversion

- Scan capability: automatic conversion performed on a selected group of analog inputs

- Analog watchdog: interrupt generation when the converted voltage is outside the programmed threshold

- Triggered by timer

Note: ADC1 can be served by DMA1.

# 3.10 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports. TIM4 and ADC1 DMA channels can also be remapped.

The highly flexible routing interface allows application software to control the routing of different I/Os to the TIM1 timer input captures. It also controls the routing of internal analog signals to ADC1 and the internal reference voltage  $V_{\text{REFINT}}$ .

# 3.11 Timers

The high density value line STM8L05xxx devices contain one advanced control timer (TIM1), three 16-bit general purpose timers (TIM2, TIM3 and TIM5) and one 8-bit basic timer (TIM4).

All the timers can be served by DMA1.

*Table 2* compares the features of the advanced control, general-purpose and basic timers.

| Timer | Counter resolution | Counter<br>type | Prescaler factor                  | DMA1<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |  |  |  |

|-------|--------------------|-----------------|-----------------------------------|-------------------------------|-----------------------------|--------------------------|--|--|--|

| TIM1  |                    | Any power of 2  |                                   | 3 + 1                         | 3                           |                          |  |  |  |

| TIM2  | 16-bit             |                 | up/down                           | up/down                       | up/down                     |                          |  |  |  |

| TIM3  | IM3                |                 |                                   | Yes                           | 2                           | None                     |  |  |  |

| TIM5  |                    |                 |                                   |                               |                             |                          |  |  |  |

| TIM4  | 8-bit              | up              | Any power of 2<br>from 1 to 32768 |                               | 0                           |                          |  |  |  |

Table 2. Timer feature comparison

| Table 4. High density value line STM8L05xxx pin description (continued) |                                                                                     |      |                   |          |      |                |                  |      |    |                                |                                                                                                                 |  |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|-------------------|----------|------|----------------|------------------|------|----|--------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| Pin<br>number                                                           |                                                                                     |      |                   | I        | nput | :              | 0                | utpu | It |                                |                                                                                                                 |  |

| LQFP64                                                                  | Pin name                                                                            | Type | I/O level         | floating | ndw  | Ext. interrupt | High sink/source | OD   | ЬР | Main function<br>(after reset) | Default alternate function                                                                                      |  |

| 42                                                                      | PF5/LCD_SEG37/<br>LCD_COM5 <sup>(5)</sup>                                           | I/O  | FT <sup>(2)</sup> | x        | Х    | х              | HS               | х    | х  | Port F5                        | LCD_SEG37/<br>LCD COM5 <sup>(5)</sup>                                                                           |  |

| 43                                                                      | PF6/LCD_SEG38/<br>LCD_COM6 <sup>(5)</sup>                                           | I/O  | FT <sup>(2)</sup> | x        | х    | х              | HS               | х    | х  | Port F6                        | LCD_SEG38/<br>LCD COM6 <sup>(5)</sup>                                                                           |  |

| 44                                                                      | PF7/LCD_SEG39/<br>LCD_COM7 <sup>(5)</sup>                                           | I/O  | FT <sup>(2)</sup> | x        | х    | х              | HS               | х    | х  | Port F7                        | LCD_SEG39/<br>LCD COM7 <sup>(5)</sup>                                                                           |  |

| 18                                                                      | VLCD                                                                                | S    | -                 | -        | -    | -              | -                | -    | -  | LCD booster external capacitor |                                                                                                                 |  |

| 11                                                                      | V <sub>DD1</sub>                                                                    | S    | -                 | -        | -    | -              | -                | -    | -  | Digital power supply           |                                                                                                                 |  |

| 10                                                                      | V <sub>SS1</sub>                                                                    | -    | -                 | -        | -    | -              | -                | -    | -  | I/O grour                      | nd                                                                                                              |  |

| 12                                                                      | V <sub>DDA</sub>                                                                    | S    | -                 | -        | I    | I              | -                | -    | -  | Analog s                       | upply voltage                                                                                                   |  |

| 13                                                                      | V <sub>REF+</sub>                                                                   | S    | -                 | -        | I    | I              | -                | -    | I  | ADC1 po                        | ositive voltage reference                                                                                       |  |

| 14                                                                      | PG0/USART3_RX/<br>[TIM2_BKIN]                                                       | I/O  | FT <sup>(2)</sup> | x        | х    | х              | HS               | х    | х  | Port G0                        | USART3 receive /<br>[Timer 2 - break input]                                                                     |  |

| 15                                                                      | PG1/USART3_TX/<br>[TIM3_BKIN]                                                       | I/O  | FT <sup>(2)</sup> | x        | Х    | Х              | HS               | х    | х  | Port G1                        | USART3 transmit /<br>[Timer 3 -break input]                                                                     |  |

| 16                                                                      | PG2/USART3_CK                                                                       | I/O  | FT <sup>(2)</sup> | x        | х    | х              | HS               | Х    | х  | Port G2                        | USART 3 synchronous<br>clock                                                                                    |  |

| 17                                                                      | PG3 <i>[TIM3_ETR]</i>                                                               | I/O  | FT <sup>(2)</sup> | X        | Х    | Х              | HS               | Х    | Х  | Port G3                        | [Timer 3 - trigger]                                                                                             |  |

| 9                                                                       | $V_{SSA}/V_{REF}$                                                                   | S    | -                 | -        | -    | -              | -                | -    |    |                                | round voltage /<br>gative voltage reference                                                                     |  |

| 55                                                                      | V <sub>DD2</sub>                                                                    | S    | -                 | -        | I    | I              | -                | -    | I  | IOs supply voltage             |                                                                                                                 |  |

| 56                                                                      | V <sub>SS2</sub>                                                                    | S    | -                 | -        | -    | -              | -                | -    | -  | IOs ground voltage             |                                                                                                                 |  |

| 1                                                                       | PA0 <sup>(6)</sup> /[USART1_CK] <sup>(8)</sup> /<br>SWIM/BEEP/IR_TIM <sup>(7)</sup> | I/O  | -                 | х        | х    | х              | HS               | x    | х  | Port A0                        | [USART1 synchronous<br>clock] <sup>(8)</sup> / SWIM input and<br>output /Beep output<br>/ Infrared Timer output |  |

| 29                                                                      | V <sub>DD3</sub>                                                                    | S    | -                 | -        | -    | -              | -                | -    | -  | IOs supp                       | ly voltage                                                                                                      |  |

| 30                                                                      | V <sub>SS3</sub>                                                                    | S    | -                 | -        | -    | -              | -                | -    | I  | IOs grou                       | Os ground voltage                                                                                               |  |

### Table 4. High density value line STM8L05xxx pin description (continued)

At power-up, the PA1/NRST pin is a reset input pin with pull-up. To be used as a general purpose pin (PA1), it can be configured only as output open-drain or push-pull, not as a general purpose input. Refer to Section Configuring NRST/PA1 pin as general purpose output in the STM8L15x and STM8L16x reference manual (RM0031).

| Address                   | Block  | Register label | Register name                                                              | Reset<br>status     |

|---------------------------|--------|----------------|----------------------------------------------------------------------------|---------------------|

| 0x00 50C0                 |        | CLK_CKDIVR     | Clock master divider register                                              | 0x03                |

| 0x00 50C1                 |        | CLK_CRTCR      | Clock RTC register                                                         | 0x00 <sup>(1)</sup> |

| 0x00 50C2                 |        | CLK_ICKR       | Internal clock control register                                            | 0x11                |

| 0x00 50C3                 |        | CLK_PCKENR1    | Peripheral clock gating register 1                                         | 0x00                |

| 0x00 50C4                 |        | CLK_PCKENR2    | Peripheral clock gating register 2                                         | 0x00                |

| 0x00 50C5                 |        | CLK_CCOR       | Configurable clock control register                                        | 0x00                |

| 0x00 50C6                 |        | CLK_ECKR       | External clock control register                                            | 0x00                |

| 0x00 50C7                 |        | CLK_SCSR       | System clock status register                                               | 0x01                |

| 0x00 50C8                 | CLK    | CLK_SWR        | System clock switch register                                               | 0x01                |

| 0x00 50C9                 |        | CLK_SWCR       | Clock switch control register                                              | 0xX0                |

| 0x00 50CA                 |        | CLK_CSSR       | Clock security system register                                             | 0x00                |

| 0x00 50CB                 |        | CLK_CBEEPR     | Clock BEEP register                                                        | 0x00                |

| 0x00 50CC                 |        | CLK_HSICALR    | HSI calibration register                                                   | 0xXX                |

| 0x00 50CD                 |        | CLK_HSITRIMR   | HSI clock calibration trimming register                                    | 0x00                |

| 0x00 50CE                 |        | CLK_HSIUNLCKR  | HSI unlock register                                                        | 0x00                |

| 0x00 50CF                 |        | CLK_REGCSR     | Main regulator control status register                                     | 0bxx11100           |

| 0x00 50D0                 |        | CLK_PCKENR3    | CLK_PCKENR3 Peripheral clock gating register 3                             |                     |

| 0x00 50D1 to<br>0x00 50D2 |        | F              | Reserved area (2 bytes)                                                    | ·                   |

| 0x00 50D3                 |        | WWDG_CR        | WWDG control register                                                      | 0x7F                |

| 0x00 50D4                 | - WWDG | WWDG_WR        | WWDR window register                                                       | 0x7F                |

| 0x00 50D5 to<br>00 50DF   |        | R              | Reserved area (11 bytes)                                                   |                     |

| 0x00 50E0                 |        | IWDG_KR        | IWDG key register                                                          | 0xXX                |

| 0x00 50E1                 | IWDG   | IWDG_PR        | IWDG prescaler register                                                    | 0x00                |

| 0x00 50E2                 |        | IWDG_RLR       | IWDG reload register                                                       | 0xFF                |

| 0x00 50E3 to<br>0x00 50EF |        | R              | eserved area (13 bytes)                                                    |                     |

| 0x00 50F0                 |        | BEEP_CSR1      | BEEP control/status register 1                                             | 0x00                |

| 0x00 50F1<br>0x00 50F2    | BEEP   |                | BEEP_CSR1     BEEP control/status register 1       Reserved area (2 bytes) |                     |

| 0x00 50F3                 | 1      | BEEP_CSR2      | BEEP control/status register 2                                             | 0x1F                |

| 0x00 50F4 to<br>0x00 513F |        | R              | teserved area (76 bytes)                                                   |                     |

Table 7. General hardware register map (continued)

| Address                   | Block                   | Register Label                              | Register Name                             | Reset<br>Status |  |

|---------------------------|-------------------------|---------------------------------------------|-------------------------------------------|-----------------|--|

| 0x00 7F90                 |                         | DM_BK1RE                                    | DM breakpoint 1 register extended byte    | 0xFF            |  |

| 0x00 7F91                 |                         | DM_BK1RH                                    | DM breakpoint 1 register high byte        | 0xFF            |  |

| 0x00 7F92                 |                         | DM_BK1RL                                    | DM breakpoint 1 register low byte         | 0xFF            |  |

| 0x00 7F93                 |                         | DM_BK2RE                                    | DM breakpoint 2 register extended byte    | 0xFF            |  |

| 0x00 7F94                 |                         | DM_BK2RH DM breakpoint 2 register high byte |                                           | 0xFF            |  |

| 0x00 7F95                 | DM                      | DM_BK2RL                                    | BK2RL DM breakpoint 2 register low byte   |                 |  |

| 0x00 7F96                 |                         | DM_CR1                                      | DM Debug module control register 1        | 0x00            |  |

| 0x00 7F97                 |                         | DM_CR2                                      | DM Debug module control register 2        | 0x00            |  |

| 0x00 7F98                 |                         | DM_CSR1                                     | DM Debug module control/status register 1 | 0x10            |  |

| 0x00 7F99                 |                         | DM_CSR2                                     | DM Debug module control/status register 2 | 0x00            |  |

| 0x00 7F9A                 |                         | DM_ENFCTR                                   | M_ENFCTR DM enable function register      |                 |  |

| 0x00 7F9B to<br>0x00 7F9F | Reserved area (5 bytes) |                                             |                                           |                 |  |

## Table 8. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

| IRQ<br>No. | Source<br>block        | Description                                                                                                             | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-<br>halt mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |  |  |

|------------|------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|--|--|

| 21         | TIM3/USART3            | TIM3 update/overflow/<br>trigger/break USART3<br>transmission<br>complete/transmit data<br>register empty<br>interrupt  | -                           | -                                      | Yes                                  | Yes <sup>(5)</sup>                                  | 0x00 805C         |  |  |

| 22         | TIM3/USART3            | TIM3<br>capture/compareUSART3<br>Receive register<br>data full/overrun/idle line<br>detected/parity error/<br>interrupt | -                           | -                                      | Yes                                  | Yes <sup>(5)</sup>                                  | 0x00 8060         |  |  |

| 23         | TIM1                   | Update /overflow/trigger/<br>COM                                                                                        | -                           | -                                      | -                                    | Yes <sup>(5)</sup>                                  | 0x00 8064         |  |  |

| 24         | TIM1                   | Capture/compare                                                                                                         | -                           | -                                      | -                                    | Yes <sup>(5)</sup>                                  | 0x00 8068         |  |  |

| 25         | TIM4                   | TIM4 update/overflow/<br>trigger                                                                                        | -                           | -                                      | Yes                                  | Yes <sup>(5)</sup>                                  | 0x00 806C         |  |  |

| 26         | SPI1                   | End of Transfer                                                                                                         | Yes                         | Yes                                    | Yes                                  | Yes <sup>(5)</sup>                                  | 0x00 8070         |  |  |

| 27         | USART1/TIM5            | USART1 transmission<br>complete/transmit data<br>register empty/<br>TIM5 update/overflow/<br>trigger/break              | -                           | -                                      | Yes                                  | Yes <sup>(5)</sup>                                  | 0x00 8074         |  |  |

| 28         | USART1/TIM5            | USART1 received data<br>ready/overrun error/<br>idle line detected/parity<br>error/TIM5<br>capture/compare              | -                           | -                                      | Yes                                  | Yes <sup>(5)</sup>                                  | 0x00 8078         |  |  |

| 29         | I <sup>2</sup> C1/SPI2 | I <sup>2</sup> C1 interrupt <sup>(4)</sup> /SPI2                                                                        | Yes                         | Yes                                    | Yes                                  | Yes <sup>(5)</sup>                                  | 0x00 807C         |  |  |

#### Table 9. Interrupt mapping (continued)

1. The Low power wait mode is entered when executing a WFE instruction in Low power run mode.

2. The TLI interrupt is the logic OR between TIM2 overflow interrupt, and TIM4 overflow interrupts.

The interrupt from PVD is logically OR-ed with Port E and F interrupts. Register EXTI\_CONF allows to select between Port E and Port F interrupt (see External interrupt port select register (EXTI\_CONF) in the RM0031).

4. The device is woken up from Halt or Active-halt mode only when the address received matches the interface address.

5. In WFE mode, this interrupt is served if it has been previously enabled. After processing the interrupt, the processor goes back to WFE mode. When this interrupt is configured as a wakeup event, the CPU wakes up and resumes processing.

| Table 11. Option byte description |                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Option<br>byte no.                | Option description                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| OPT0                              | <b>ROP[7:0]</b> Memory readout protection (ROP)<br>0xAA: Disable readout protection (write access via SWIM protocol)<br>Refer to Readout protection section in the STM8L reference manual (RM0031).                                                                                                                                                                 |  |  |  |  |  |

| OPT1                              | UBC[7:0] Size of the user boot code area<br>UBC[7:0] Size of the user boot code area<br>0x00: No UBC<br>0x01: Page 0 reserved for the UBC and write protected.<br><br>0xFF: Page 0 to 254 reserved for the UBC and write-protected.<br>Refer to User boot code section in the STM8L reference manual (RM0031).                                                      |  |  |  |  |  |

| OPT2                              | PCODESIZE[7:0] Size of the proprietary code area<br>0x00: No proprietary code area<br>0x01: Page 0 reserved for the proprietary code and read/write protected.<br><br>0xFF: Page 0 to 254 reserved for the proprietary code and read/write protected.<br>Refer to Proprietary code area (PCODE) section in the STM8L reference manual<br>(RM0031) for more details. |  |  |  |  |  |

|                                   | IWDG_HW: Independent watchdog         0: Independent watchdog activated by software         1: Independent watchdog activated by hardware         IWDG_HALT: Independent watchdog off in Halt/Active-halt         0: Independent watchdog continues running in Halt/Active-halt mode         1: Independent watchdog stopped in Halt/Active-halt mode               |  |  |  |  |  |

| OPT3                              | WWDG_HW: Window watchdog         0: Window watchdog activated by software         1: Window watchdog activated by hardware         WWDG_HALT: Window window watchdog reset on Halt/Active-halt         0: Window watchdog stopped in Halt mode         1: Window watchdog generates a reset when MCU enters Halt mode                                               |  |  |  |  |  |

| ΟΡΤ4                              | HSECNT: Number of HSE oscillator stabilization clock cycles<br>0x00 - 1 clock cycle<br>0x01 - 16 clock cycles<br>0x10 - 512 clock cycles<br>0x11 - 4096 clock cycles                                                                                                                                                                                                |  |  |  |  |  |

| OPT4                              | LSECNT: Number of LSE oscillator stabilization clock cycles<br>0x00 - 1 clock cycle<br>0x01 - 16 clock cycles<br>0x10 - 512 clock cycles<br>0x11 - 4096 clock cycles                                                                                                                                                                                                |  |  |  |  |  |

### Table 11. Option byte description

| Symbol                              | Ratings                                                                     | Max.     | Unit |

|-------------------------------------|-----------------------------------------------------------------------------|----------|------|

| I <sub>VDD</sub>                    | Total current into V <sub>DD</sub> power line (source)                      | 80       |      |

| I <sub>VSS</sub>                    | Total current out of V <sub>SS</sub> ground line (sink)                     | 80       |      |

| I <sub>VSS</sub><br>I <sub>IO</sub> | Output current sunk by IR_TIM pin<br>(with high sink LED driver capability) | 80       |      |

|                                     | Output current sunk by any other I/O and control pin                        | 25       |      |

|                                     | Output current sourced by any I/Os and control pin                          | - 25     | mA   |

|                                     | Injected current on true open-drain pins (PC0 and PC1) <sup>(1)</sup>       | - 5 / +0 |      |

| I <sub>INJ(PIN)</sub>               | Injected current on five-volt tolerant (FT) pins <sup>(1)</sup>             | - 5 / +0 |      |

|                                     | Injected current on any other pin <sup>(2)</sup>                            | - 5 / +5 |      |

| $\Sigma I_{INJ(PIN)}$               | Total injected current (sum of all I/O and control pins) $^{(3)}$           | ± 25     |      |

#### Table 13. Current characteristics

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 12*. for maximum allowed input voltage values.

2. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 12*. for maximum allowed input voltage values.

3. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 14. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | C    |

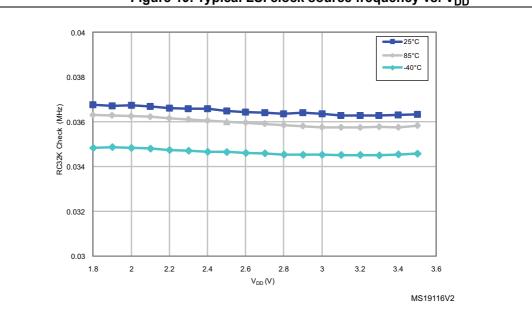

Figure 19. Typical LSI clock source frequency vs.  $V_{\text{DD}}$

### 8.3.5 Memory characteristics

$T_A$  = -40 to 85 °C unless otherwise specified.

Table 32. RAM and hardware registers

| Symbol          | Parameter                          | Conditions           | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------|----------------------|------|------|------|------|

| V <sub>RM</sub> | Data retention mode <sup>(1)</sup> | Halt mode (or Reset) | 1.8  | -    | -    | V    |

1. Minimum supply voltage without losing data stored in RAM (in Halt mode or under Reset) or in hardware registers (only in Halt mode). Guaranteed by characterization results.

## 8.3.6 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error, out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation, LCD levels, etc.).

The test results are given in the following table.

|                  |                                                                                                                                               | Functional s       |                    |      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                   | Negative injection | Positive injection | Unit |

|                  | Injected current on true open-drain pins                                                                                                      | -5                 | +0                 |      |

| I <sub>INJ</sub> | Injected current on all 5 V tolerant (FT) pins                                                                                                | -5                 | +0                 | mA   |

|                  | Negative<br>injection     Positive<br>injection       Injected current on true open-drain pins     -5       +0     Height of current on clips |                    |                    |      |

### Table 34. I/O current injection susceptibility

## 8.3.7 I/O port pin characteristics

### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

### **Electrical parameters**

| Symbol                                                                                           | Parameter                                             | Conditions <sup>(1)</sup>                                                                        | Min.                   | Тур.                                                            | Max.                  | Unit |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------|-----------------------|------|

|                                                                                                  |                                                       | Input voltage on true<br>open-drain pins (PC0<br>and PC1)                                        | Vss-0.3                | -                                                               | 0.3 x V <sub>DD</sub> |      |

| $V_{IL}$                                                                                         | Input low level voltage <sup>(2)</sup>                | Input voltage on five-<br>volt tolerant (FT) pins                                                | Vss-0.3                | -                                                               | 0.3 x V <sub>DD</sub> | V    |

|                                                                                                  |                                                       | Input voltage on any other pin                                                                   | Vss-0.3                | -                                                               | 0.3 x V <sub>DD</sub> |      |

|                                                                                                  |                                                       | Input voltage on true<br>open-drain pins (PC0<br>and PC1)<br>with V <sub>DD</sub> < 2 V          | 0.70 x V <sub>DD</sub> | -                                                               | 5.2                   |      |

|                                                                                                  |                                                       | Input voltage on true open-drain pins (PC0 and PC1) with $V_{DD} \ge 2 V$                        | 0.70 X VDD             | -                                                               | 5.5                   |      |

| V <sub>IH</sub>                                                                                  | Input high level voltage <sup>(2)</sup>               | Input voltage on five-<br>volt tolerant (FT) pins<br>with V <sub>DD</sub> < 2 V                  | 0.70 x V               | -                                                               | 5.2                   | V    |

| V <sub>IH</sub> Inp<br>V <sub>hys</sub> Scr<br>I <sub>lkg</sub> Inp<br>R <sub>PU</sub> We<br>res |                                                       | Input voltage on five-<br>volt tolerant (FT) pins<br>with $V_{DD} \ge 2 V$                       | 0.70 x V <sub>DD</sub> | -                                                               | 5.5                   |      |

| V <sub>IH</sub> Input high                                                                       |                                                       | Input voltage on any other pin                                                                   | 0.70 x V <sub>DD</sub> | - V <sub>DD</sub> +0.3                                          |                       |      |

| N/                                                                                               | <b>a</b>                                              | Standard I/Os                                                                                    | -                      | 200                                                             | -                     |      |

| V hys                                                                                            | Schmitt trigger voltage hysteresis <sup>(3)</sup>     | True open drain I/Os                                                                             | -                      | 200                                                             | -                     | - mV |

|                                                                                                  |                                                       | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os                               | -                      | $ \begin{array}{c cccc}  & & & & & & & & & & & & & & & & & & &$ |                       |      |

| l <sub>ikg</sub>                                                                                 | Input leakage current <sup>(4)</sup>                  | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>True open drain I/Os                        | -                      | -                                                               | 200 <sup>(5)</sup>    | nA   |

|                                                                                                  |                                                       | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>PA0 with high sink LED<br>driver capability | -                      | -                                                               | 200 <sup>(5)</sup>    |      |

| R <sub>PU</sub>                                                                                  | Weak pull-up equivalent<br>resistor <sup>(2)(6)</sup> | V <sub>IN</sub> =V <sub>SS</sub>                                                                 | 30                     | 45                                                              | 60                    | kΩ   |

| C <sub>IO</sub>                                                                                  | I/O pin capacitance                                   | -                                                                                                | -                      | 5                                                               | -                     | pF   |

### Table 35. I/O static characteristics

1. V\_{DD} = 3.0 V, T\_A = -40 to 85 °C unless otherwise specified.

2. Guaranteed by characterization results.

3. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

5. Not tested in production.

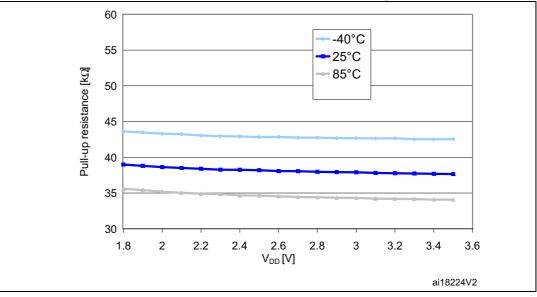

R<sub>PU</sub> pull-up equivalent resistor based on a resistive transistor (corresponding I<sub>PU</sub> current characteristics described in Figure 23).

| Symbol                | Parameter                                       | Conditions                                                       | Min.                      | Тур. | Max.            | Unit |

|-----------------------|-------------------------------------------------|------------------------------------------------------------------|---------------------------|------|-----------------|------|

| V <sub>IL(NRST)</sub> | NRST input low level voltage (1)                | -                                                                | $V_{SS}$                  | -    | 0.8             |      |

| V <sub>IH(NRST)</sub> | NRST input high level voltage <sup>(1)</sup>    | -                                                                | 1.4                       | -    | V <sub>DD</sub> |      |

| Vermeen               |                                                 | $I_{OL}$ = 2 mA<br>for 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V | -                         |      |                 | V    |

| V <sub>OL(NRST)</sub> | NRST output low level voltage <sup>(1)</sup>    | I <sub>OL</sub> = 1.5 mA<br>for V <sub>DD</sub> < 2.7 V          | -                         | -    | 0.4             |      |

| V <sub>HYST</sub>     | NRST input hysteresis <sup>(3)</sup>            | -                                                                | 10%V <sub>DD</sub><br>(2) | -    | -               | mV   |

| R <sub>PU(NRST)</sub> | NRST pull-up equivalent resistor <sup>(1)</sup> | -                                                                | 30                        | 45   | 60              | kΩ   |

| V <sub>F(NRST)</sub>  | NRST input filtered pulse <sup>(3)</sup>        | -                                                                | -                         | -    | 50              | ne   |

| V <sub>NF(NRST)</sub> | NRST input not filtered pulse <sup>(3)</sup>    | -                                                                | 300                       | -    | -               | ns   |

Table 39. NRST pin characteristics

1. Guaranteed by characterization results.

2. 200 mV min.

3. Guaranteed by design.

Figure 30. Typical NRST pull-up resistance  $R_{PU}$  vs.  $V_{DD}$

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

## I<sup>2</sup>C - Inter IC control interface

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{SYSCLK}},$  and  $T_{\text{A}}$  unless otherwise specified.

The STM8L I<sup>2</sup>C interface (I2C1) meets the requirements of the Standard I<sup>2</sup>C communication protocol described in the following table with the restriction mentioned below:

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

| Table 41. I2C characteristics              |                                         |                     |                       |                                           |                     |      |  |

|--------------------------------------------|-----------------------------------------|---------------------|-----------------------|-------------------------------------------|---------------------|------|--|

| Symbol                                     | Parameter                               | Standard            | mode I <sup>2</sup> C | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                     | Unit |  |

| Symbol                                     | Falameter                               | Min. <sup>(2)</sup> |                       | Min. <sup>(2)</sup>                       | Max. <sup>(2)</sup> | onit |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                 | -                     | 1.3                                       | -                   |      |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                 | -                     | 0.6                                       | -                   | μs   |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                 | -                     | 100                                       | -                   |      |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0                   | -                     | 0                                         | 900                 |      |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                   | 1000                  | -                                         | 300                 | ns   |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   | -                   | 300                   | -                                         | 300                 |      |  |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                 | -                     | 0.6                                       | -                   |      |  |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                 | -                     | 0.6                                       | -                   | - µs |  |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                 | -                     | 0.6                                       | -                   | μs   |  |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                 | -                     | 1.3                                       | -                   | μs   |  |

| Cb                                         | Capacitive load for each bus line       | -                   | 400                   | -                                         | 400                 | pF   |  |

Table 41. I2C characteristics

1.  $f_{SYSCLK}$  must be at least equal to 8 MHz to achieve max fast I<sup>2</sup>C speed (400 kHz).

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

Note: For speeds around 200 kHz, the achieved speed can have a  $\pm$ 5% tolerance. For other speed ranges, the achieved speed can have a  $\pm$ 2% tolerance. The above variations depend on the accuracy of the external components used.

## 8.3.9 LCD controller

In the following table, data are guaranteed by design, not tested in production.

| Symbol            | Parameter                                              | Min. | Тур.                 | Max.              | Unit |  |

|-------------------|--------------------------------------------------------|------|----------------------|-------------------|------|--|

| V <sub>LCD</sub>  | LCD external voltage                                   | -    | -                    | 3.6               |      |  |

| V <sub>LCD0</sub> | LCD internal reference voltage 0                       | -    | 2.6                  | -                 |      |  |

| V <sub>LCD1</sub> | LCD internal reference voltage 1                       | -    | 2.7                  | -<br>-<br>- V     |      |  |

| V <sub>LCD2</sub> | LCD internal reference voltage 2                       | -    | 2.8                  |                   |      |  |

| V <sub>LCD3</sub> | LCD internal reference voltage 3                       | -    | 3.0                  |                   |      |  |

| V <sub>LCD4</sub> | LCD internal reference voltage 4                       | -    | 3.1                  | -                 |      |  |

| $V_{LCD5}$        | LCD internal reference voltage 5                       | -    | 3.2                  | -                 |      |  |

| $V_{LCD6}$        | LCD internal reference voltage 6                       | -    | 3.4                  | -                 |      |  |

| V <sub>LCD7</sub> | LCD internal reference voltage 7                       | -    | 3.5                  | -                 |      |  |

| C <sub>EXT</sub>  | V <sub>LCD</sub> external capacitance                  | 0.1  | 1                    | 2                 | μF   |  |

| 1                 | Supply current <sup>(1)</sup> at $V_{DD}$ = 1.8 V      | -    | 3                    | -                 | μΑ   |  |

| I <sub>DD</sub>   | Supply current <sup>(1)</sup> at V <sub>DD</sub> = 3 V | -    | 3                    | -                 |      |  |

| $R_{HN}^{(2)}$    | High value resistive network (low drive)               | -    | 6.6                  | -                 | MΩ   |  |

| $R_{LN}^{(3)}$    | Low value resistive network (high drive)               | -    | 240                  | -                 | kΩ   |  |

| V <sub>33</sub>   | Segment/Common higher level voltage                    | -    | -                    | V <sub>LCDx</sub> |      |  |

| V <sub>34</sub>   | Segment/Common 3/4 level voltage                       | -    | 3/4V <sub>LCDx</sub> | -                 |      |  |

| V <sub>23</sub>   | Segment/Common 2/3 level voltage                       | -    | 2/3V <sub>LCDx</sub> | -                 |      |  |

| V <sub>12</sub>   | Segment/Common 1/2 level voltage                       | -    | 1/2V <sub>LCDx</sub> | -                 | V    |  |

| V <sub>13</sub>   | Segment/Common 1/3 level voltage                       | -    | 1/3V <sub>LCDx</sub> | -                 |      |  |

| V <sub>14</sub>   | Segment/Common 1/4 level voltage                       | -    | 1/4V <sub>LCDx</sub> | -                 |      |  |

| V <sub>0</sub>    | Segment/Common lowest level voltage                    | 0    | -                    | -                 |      |  |

| Table | 42. | LCD | characteristics |

|-------|-----|-----|-----------------|

|       |     |     |                 |

1. LCD enabled with 3 V internal booster (LCD\_CR1 = 0x08), 1/4 duty, 1/3 bias, division ratio= 64, all pixels active, no LCD connected.

2.  $\ensuremath{\mathsf{R}_{\mathsf{HN}}}$  is the total high value resistive network.

3.  $\ R_{LN}$  is the total low value resistive network.

### **VLCD** external capacitor

The application can achieve a stabilized LCD reference voltage by connecting an external capacitor  $C_{EXT}$  to the  $V_{LCD}$  pin.  $C_{EXT}$  is specified in *Table 42*.

# 8.3.11 12-bit ADC1 characteristics

In the following table, data are guaranteed by design, not tested in production.

| Table 44. ADC1 characteristics |                                    |                                                  |                  |                  |                                 |                       |  |

|--------------------------------|------------------------------------|--------------------------------------------------|------------------|------------------|---------------------------------|-----------------------|--|

| Symbol                         | Parameter                          | Conditions                                       | Min.             | Тур.             | Max.                            | Unit                  |  |

| $V_{DDA}$                      | Analog supply voltage              | -                                                | 1.8              | -                | 3.6                             | V                     |  |

| M                              | Reference supply                   | 2.4 V ≤V <sub>DDA</sub> ≤ 3.6 V                  | 2.4              | -                | V <sub>DDA</sub>                | V                     |  |

| $V_{REF}$ +                    | voltage                            | 1.8 V≤V <sub>DDA</sub> ≤ 2.4 V                   |                  | V <sub>DDA</sub> | •                               | V                     |  |

| V <sub>REF-</sub>              | Lower reference voltage            | -                                                |                  | $V_{SSA}$        |                                 | V                     |  |

| I <sub>VDDA</sub>              | Current on the VDDA input pin      | -                                                | -                | 1000             | 1450                            | μA                    |  |

| I                              | Current on the VREF+<br>input pin  | -                                                | -                | 400              | 700<br>(peak) <sup>(1)</sup>    | μA                    |  |

| I <sub>VREF+</sub>             |                                    | -                                                | -                | 400              | 450<br>(average) <sup>(1)</sup> | μA                    |  |

| V <sub>AIN</sub>               | Conversion voltage range           | -                                                | 0 <sup>(2)</sup> | -                | V <sub>REF+</sub>               | -                     |  |

| T <sub>A</sub>                 | Temperature range                  | -                                                | -40              | -                | 85                              | °C                    |  |

| R <sub>AIN</sub>               | External resistance on             | on PF0/1/2/3 fast<br>channels                    | -                | -                | 50 <sup>(3)</sup>               | kΩ                    |  |

|                                | V <sub>AIN</sub>                   | on all other channels                            | -                | -                |                                 |                       |  |

| C <sub>ADC</sub>               | Internal sample and hold capacitor | on PF0/1/2/3 fast<br>channels                    | -                | 16               | -                               | pF                    |  |

|                                |                                    | on all other channels                            | -                |                  | -                               |                       |  |

| fere                           | ADC sampling clock<br>frequency    | 2.4 V≤V <sub>DDA</sub> ≤3.6 V<br>without zooming | 0.320            | -                | 16                              | MHz                   |  |

| f <sub>ADC</sub>               |                                    | 1.8 V≤V <sub>DDA</sub> ≤2.4 V<br>with zooming    | 0.320            | -                | 8                               | MHz                   |  |

| f <sub>CONV</sub>              | 12-bit conversion rate             | V <sub>AIN</sub> on PF0/1/2/3 fast<br>channels   | -                | -                | 1 <sup>(3)(4)</sup>             | MHz                   |  |

|                                |                                    | V <sub>AIN</sub> on all other<br>channels        | -                | -                | 760 <sup>(3)(4)</sup>           | kHz                   |  |

| f <sub>TRIG</sub>              | External trigger<br>frequency      | -                                                | -                | -                | t <sub>conv</sub>               | 1/f <sub>ADC</sub>    |  |

| t <sub>LAT</sub>               | External trigger latency           | -                                                | -                | -                | 3.5                             | 1/f <sub>SYSCLK</sub> |  |

| Table 44 | . ADC1 | characteristics |

|----------|--------|-----------------|

|          |        | onulationstics  |

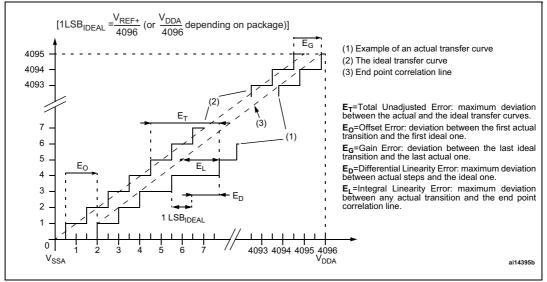

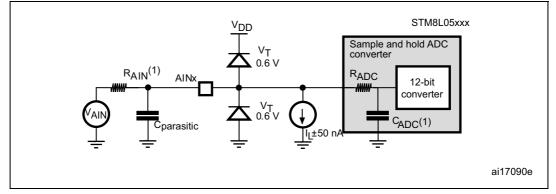

#### Figure 37. ADC1 accuracy characteristics

#### Figure 38. Typical connection diagram using the ADC

- 1. Refer to Table 44 for the values of  $R_{AIN}$  and  $C_{ADC}$ .

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in Figure 39 or Figure 40, depending on whether  $V_{\text{REF+}}$  is connected to  $V_{\text{DDA}}$  or not. Good quality ceramic 10 nF capacitors should be used. They should be placed as close as possible to the chip.

## 8.3.12 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### Functional EMS (electromagnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol                                                                               | Parameter                                                                            | Conditions                                                                                                                            |           |    |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------|----|--|--|

| V <sub>FESD</sub>                                                                    | Voltage limits to be applied on<br>any I/O pin to induce a functional<br>disturbance | $V_{DD} = 3.3 \text{ V},  \text{T}_{\text{A}} = +25 ^{\circ}\text{C},$<br>$f_{\text{CPU}} = 16 \text{ MHz},$<br>conforms to IEC 61000 |           | 2B |  |  |