# Infineon Technologies - SAF-XC878CM-13FFI 3V3 AA Datasheet

Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                            |

| Core Processor             | XC800                                                                               |

| Core Size                  | 8-Bit                                                                               |

| Speed                      | 27MHz                                                                               |

| Connectivity               | CANbus, SPI, SSI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                               |

| Number of I/O              | 40                                                                                  |

| Program Memory Size        | 52KB (52K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 3.25K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                           |

| Data Converters            | A/D 8x10b                                                                           |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 64-LQFP                                                                             |

| Supplier Device Package    | PG-LQFP-64-4                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc878cm-13ffi-3v3-aa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2011-03

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2011 Infineon Technologies AG

All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

8-Bit

XC87xCLM

8-Bit Single-Chip Microcontroller

Data Sheet V1.5 2011-03

Microcontrollers

# **Table of Contents**

# **Table of Contents**

| 1               | Summary of Features                                 | . 1 |

|-----------------|-----------------------------------------------------|-----|

| <b>2</b><br>2.1 | General Device Information                          | . 6 |

| 2.2             | Logic Symbol                                        | . 7 |

| 2.3             | Pin Configuration                                   | . 8 |

| 2.4             | Pin Definitions and Functions                       | 10  |

| 3               | Functional Description                              | 21  |

| 3.1             | Processor Architecture                              | 21  |

| 3.2             | Memory Organization                                 | 22  |

| 3.2.1           | Memory Protection Strategy                          | 24  |

| 3.2.1.1         | Flash Memory Protection                             | 24  |

| 3.2.2           | Special Function Register                           | 26  |

| 3.2.2.1         | Address Extension by Mapping                        | 26  |

| 3.2.2.2         | Address Extension by Paging                         | 28  |

| 3.2.3           | Bit Protection Scheme                               | 32  |

| 3.2.3.1         | Password Register                                   | 33  |

| 3.2.4           | XC87x Register Overview                             |     |

| 3.2.4.1         | CPU Registers                                       | 34  |

| 3.2.4.2         | MDU Registers                                       | 35  |

| 3.2.4.3         | CORDIC Registers                                    | 36  |

| 3.2.4.4         | System Control Registers                            |     |

| 3.2.4.5         | WDT Registers                                       |     |

| 3.2.4.6         | Port Registers                                      | 40  |

| 3.2.4.7         | ADC Registers                                       |     |

| 3.2.4.8         | Timer 2 Compare/Capture Unit Registers              |     |

| 3.2.4.9         | Timer 21 Registers                                  | 49  |

| 3.2.4.10        | CCU6 Registers                                      | 50  |

| 3.2.4.11        | UART1 Registers                                     | 54  |

| 3.2.4.12        | SSC Registers                                       | 54  |

| 3.2.4.13        | MultiCAN Registers                                  | 55  |

| 3.2.4.14        | OCDS Registers                                      | 55  |

| 3.2.4.15        | Flash Registers                                     | 57  |

| 3.3             | Flash Memory                                        | 58  |

| 3.3.1           | Flash Bank Pagination                               | 60  |

| 3.4             | Interrupt System                                    | 61  |

| 3.4.1           | Interrupt Source                                    | 61  |

| 3.4.2           | Interrupt Source and Vector                         |     |

| 3.4.3           | Interrupt Priority                                  | 69  |

| 3.5             | Parallel Ports                                      | 70  |

| 3.6             | Power Supply System with Embedded Voltage Regulator | 72  |

### **Summary of Features**

**Table 2 Device Profile** (cont'd)

| Sales Type           | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|----------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAF-XC874CM-16FVA 5V | Flash          | 64                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC874CM-13FVA 5V | Flash          | 52                            | 5.0                    | -40 to 85                | Automotive         |

| SAK-XC874LM-16FVA 5V | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874CM-16FVA 5V | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874-16FVA 5V   | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874LM-13FVA 5V | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874CM-13FVA 5V | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874-13FVA 5V   | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

As this document refers to all the derivatives, some description may not apply to a specific product. For simplicity, all versions are referred to by the term XC87x throughout this document.

### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery

For the available ordering codes for the XC87x, please refer to your responsible sales representative or your local distributor.

### **General Device Information**

# 2 General Device Information

**Chapter 2** contains the block diagram, pin configurations, definitions and functions of the XC87x.

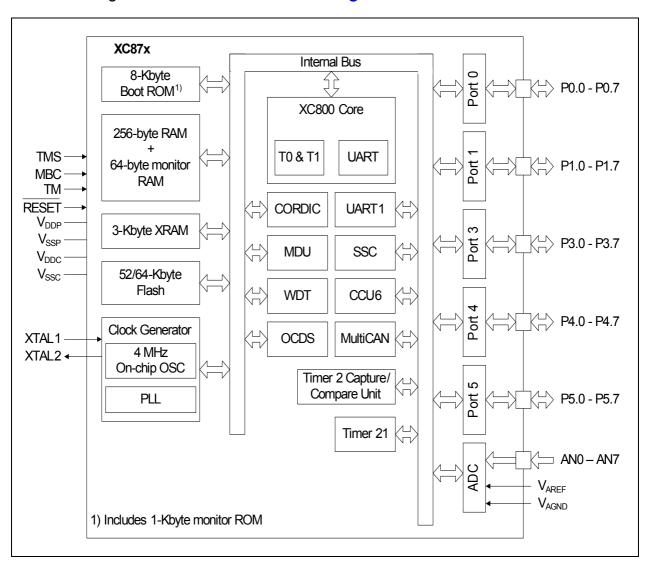

# 2.1 Block Diagram

The block diagram of the XC87x is shown in Figure 2.

Figure 2 XC87x Block Diagram

#### **General Device Information**

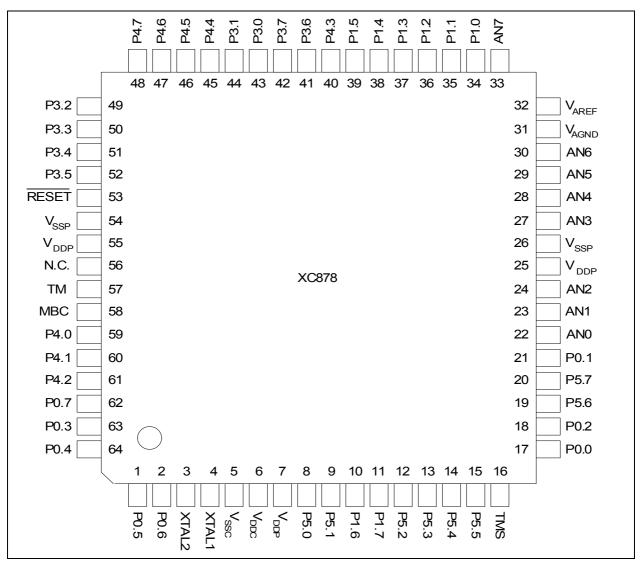

# 2.3 Pin Configuration

The pin configuration of the XC878, which is based on the PG-LQFP-64, is shown in **Figure 4**, while that of the XC874, which is based on the PG-VQFN-48 package, is shown in **Figure 5**.

Figure 4 XC878 Pin Configuration, PG-LQFP-64 Package (top view)

### **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | t Function                                                                                                                                                  |                                                                                                                                                                                                        |  |  |  |  |

|--------|--------------------------------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P5     |                                      | I/O  |                | Port 5 Port 5 is an 8-bit bidirectional general purpose I/O port. It can be used as alternate functions for UART, UART1, T2CCU, JTAG and Externa Interface. |                                                                                                                                                                                                        |  |  |  |  |

| P5.0   | 8/-                                  |      | PU             | EXINT1_1<br>A0                                                                                                                                              | External Interrupt Input 1 Address Line 0 Output                                                                                                                                                       |  |  |  |  |

| P5.1   | 9/-                                  |      | PU             | EXINT2_1<br>A1                                                                                                                                              | External Interrupt Input 2 Address Line 1 Output                                                                                                                                                       |  |  |  |  |

| P5.2   | 12/-                                 |      | PU             | RXD_2<br>T2CC2_2/<br>EXINT5_3<br>A2                                                                                                                         | UART Receive Data Input<br>External Interrupt Input 5/T2CCU<br>Capture/Compare Channel 2<br>Address Line 2 Output                                                                                      |  |  |  |  |

| P5.3   | 13/-                                 |      | PU             | CCPOS0_0<br>EXINT1_0<br>T12HR_2<br>CC61_3<br>TXD_2<br>T2CC5_2<br>A3                                                                                         | CCU6 Hall Input 0 External Interrupt Input 1 CCU6 Timer 12 Hardware Run Input Input of Capture/Compare channel 1 UART Transmit Data Output/Clock Output Compare Output Channel 5 Address Line 3 Output |  |  |  |  |

| P5.4   | 14/-                                 |      | PU             | CCPOS1_0<br>EXINT2_0<br>T13HR_2<br>CC62_3<br>RXDO_2<br>T2CC4_2<br>A4                                                                                        | CCU6 Hall Input 1 External Interrupt Input 2 CCU6 Timer 13 Hardware Run Input Input of Capture/Compare channel 2 UART Transmit Data Output Compare Output Channel 4 Address Line 4 Output              |  |  |  |  |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OP    | [7:6] | w    | <ul> <li>Operation</li> <li>0X Manual page mode. The value of STNR is ignored and PAGE is directly written.</li> <li>10 New page programming with automatic page saving. The value written to the bit positions of PAGE is stored. In parallel, the previous contents of PAGE are saved in the storage bit field STx indicated by STNR.</li> <li>11 Automatic restore page action. The value written to the bit positions PAGE is ignored and instead, PAGE is overwritten by the contents of the storage bit field STx indicated by STNR.</li> </ul> |

| 0     | 3     | r    | Reserved Returns 0 if read; should be written with 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### 3.2.3 Bit Protection Scheme

The bit protection scheme prevents direct software writing of selected bits (i.e., protected bits) using the PASSWD register. When the bit field MODE is  $11_{\rm B}$ , writing  $10011_{\rm B}$  to the bit field PASS opens access to writing of all protected bits, and writing  $10101_{\rm B}$  to the bit field PASS closes access to writing of all protected bits. In both cases, the value of the bit field MODE is not changed even if PASSWD register is written with  $98_{\rm H}$  or  $A8_{\rm H}$ . It can only be changed when bit field PASS is written with  $11000_{\rm B}$ , for example, writing  $D0_{\rm H}$  to PASSWD register disables the bit protection scheme.

Note that access is opened for maximum 32 CCLKs if the "close access" password is not written. If "open access" password is written again before the end of 32 CCLK cycles, there will be a recount of 32 CCLK cycles. The protected bits include the N- and K-Divider bits, NDIV and KDIV; the Watchdog Timer enable bit, WDTEN; and the power-down and slow-down enable bits, PD and SD.

### 3.2.4 XC87x Register Overview

The SFRs of the XC87x are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.15**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

# 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

Table 5 CPU Register Overview

| Addr            | Register Name                                           | Bit       | 7              | 6            | 5    | 4    | 3         | 2    | 1    | 0    |  |  |

|-----------------|---------------------------------------------------------|-----------|----------------|--------------|------|------|-----------|------|------|------|--|--|

| RMAP =          | = 0 or 1                                                |           | l              | I            | l    | l    | I         |      | l    | l    |  |  |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                               | Bit Field | SP             |              |      |      |           |      |      |      |  |  |

|                 | Stack Pointer Register                                  | Туре      | rw             |              |      |      |           |      |      |      |  |  |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                              | Bit Field | DPL7           | DPL6         | DPL5 | DPL4 | DPL3      | DPL2 | DPL1 | DPL0 |  |  |

|                 | Data Pointer Register Low                               | Туре      | rw             | rw           | rw   | rw   | rw        | rw   | rw   | rw   |  |  |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                              | Bit Field | DPH7           | DPH6         | DPH5 | DPH4 | DPH3      | DPH2 | DPH1 | DPH0 |  |  |

|                 | Data Pointer Register High                              | Туре      | rw             | rw           | rw   | rw   | rw        | rw   | rw   | rw   |  |  |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                             | Bit Field | SMOD           |              | 0    |      | GF1       | GF0  | 0    | IDLE |  |  |

|                 | Power Control Register                                  | Туре      | rw             |              | r    |      | rw        | rw   | r    | rw   |  |  |

| 88 <sub>H</sub> | TCON Reset: 00 <sub>H</sub>                             | Bit Field | TF1            | TR1          | TF0  | TR0  | IE1       | IT1  | IE0  | IT0  |  |  |

|                 | Timer Control Register                                  | Туре      | rwh            | rw           | rwh  | rw   | rwh       | rw   | rwh  | rw   |  |  |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub> Timer Mode Register         | Bit Field | GATE<br>1      | T1S          | T1   | 1M   | GATE<br>0 | T0S  | TO   | M    |  |  |

|                 |                                                         | Туре      | rw             | rw           | r    | W    | rw        | rw   | r    | W    |  |  |

| 8A <sub>H</sub> | TL0 Reset: 00 <sub>H</sub>                              | Bit Field |                |              |      | V    | AL        |      | •    |      |  |  |

|                 | Timer 0 Register Low                                    | Туре      |                |              |      | rv   | vh        |      |      |      |  |  |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                              | Bit Field |                |              |      | V    | /AL       |      |      |      |  |  |

|                 | Timer 1 Register Low                                    | Туре      |                |              |      | rv   | vh        |      |      |      |  |  |

| 8C <sub>H</sub> | TH0 Reset: 00 <sub>H</sub>                              | Bit Field |                |              |      | V    | AL        |      |      |      |  |  |

|                 | Timer 0 Register High                                   | Туре      |                |              |      | rv   | vh        |      |      |      |  |  |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                              | Bit Field |                |              |      | V    | AL        |      |      |      |  |  |

|                 | Timer 1 Register High                                   | Туре      |                |              |      | rv   | vh        |      |      |      |  |  |

| 94 <sub>H</sub> | MEX1 Reset: 00 <sub>H</sub>                             | Bit Field |                | C            | В    |      |           | N    | IB   |      |  |  |

|                 | Memory Extension Register 1                             | Туре      |                |              | r    |      |           | r    | W    |      |  |  |

| 95 <sub>H</sub> | MEX2 Reset: 00 <sub>H</sub>                             | Bit Field | eld MCM MCB IB |              |      |      |           |      |      |      |  |  |

|                 | Memory Extension Register 2                             | Туре      | rw rw rw       |              |      |      |           |      |      |      |  |  |

| 96 <sub>H</sub> | MEX3 Reset: 00 <sub>H</sub> Memory Extension Register 3 | Bit Field | MCB1<br>9      | 0 MXB1 MXM N |      |      | MXB       |      |      |      |  |  |

|                 |                                                         | Туре      | rw             |              | r    | rw   | rw        |      | rw   |      |  |  |

Table 11

ADC Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7               | 6      | 5 | 4   | 3              | 2 | 1    | 0         |

|-----------------|----------------------------------------------------------------------|-----------|-----------------|--------|---|-----|----------------|---|------|-----------|

| RMAP =          | = 0, PAGE 2                                                          | L         |                 |        |   |     | ı              |   | ı    | I         |

| CAH             | ADC_RESR0L Reset: 00H                                                | Bit Field | RES             | SULT   | 0 | VF  | DRC            |   | CHNR |           |

|                 | Result Register 0 Low                                                | Туре      | r               | h      | r | rh  | h rh rh        |   |      |           |

| СВН             | ADC_RESR0H Reset: 00 <sub>H</sub>                                    | Bit Field |                 |        | • | RES | SULT           |   |      |           |

|                 | Result Register 0 High                                               | Туре      |                 |        |   | ı   | ·h             |   |      |           |

| сс <sub>Н</sub> | ADC_RESR1L Reset: 00H                                                | Bit Field | RESULT 0        |        |   | VF  | DRC            |   |      |           |

|                 | Result Register 1 Low                                                | Туре      | r               | h .    | r | rh  | rh             |   | rh   |           |

| CDH             | ADC_RESR1H Reset: 00H                                                | Bit Field | d RESULT        |        |   |     |                |   |      |           |

|                 | Result Register 1 High                                               | Туре      |                 |        |   | 1   | <sup>-</sup> h |   |      |           |

| CEH             | ADC_RESR2L Reset: 00H                                                | Bit Field | RES             | SULT   | 0 | VF  | DRC            |   | CHNR |           |

|                 | Result Register 2 Low                                                | Туре      | r               | h .    | r | rh  | rh             |   | rh   |           |

| CF <sub>H</sub> | ADC_RESR2H Reset: 00H                                                | Bit Field | ld RESULT       |        |   |     |                |   |      |           |

|                 | Result Register 2 High                                               | Туре      |                 |        |   | 1   | h .            |   |      |           |

| D2 <sub>H</sub> | ADC_RESR3L Reset: 00H                                                | Bit Field | RES             | SULT   | 0 | VF  | DRC            |   | CHNR |           |

|                 | Result Register 3 Low                                                | Туре      | r               | h .    | r | rh  | rh             |   | rh   |           |

| D3 <sub>H</sub> | ADC_RESR3H Reset: 00H                                                | Bit Field |                 |        |   | RES | SULT           |   |      |           |

|                 | Result Register 3 High                                               | Туре      |                 |        |   | ı   | h              |   |      |           |

| RMAP =          | = 0, PAGE 3                                                          |           |                 |        |   |     |                |   |      |           |

| CA <sub>H</sub> | ADC_RESRA0L Reset: 00H                                               | Bit Field |                 | RESULT |   | VF  | DRC            |   | CHNR |           |

|                 | Result Register 0, View A Low                                        | Туре      |                 | rh     |   | rh  | rh             |   | rh   |           |

| СВН             | ADC_RESRA0H Reset: 00 <sub>H</sub>                                   | Bit Field |                 |        |   | RES | SULT           |   |      |           |

|                 | Result Register 0, View A High                                       | Туре      |                 |        |   | ı   | h              |   |      |           |

| сс <sub>Н</sub> | ADC_RESRA1L Reset: 00H                                               | Bit Field |                 | RESULT |   | VF  | DRC            |   | CHNR |           |

|                 | Result Register 1, View A Low                                        | Туре      |                 | rh     |   | rh  | rh             |   | rh   |           |

| CDH             | ADC_RESRA1H Reset: 00H                                               | Bit Field |                 |        |   | RES | SULT           |   |      |           |

|                 | Result Register 1, View A High                                       | Туре      |                 |        |   |     | h .            |   |      |           |

| CEH             | ADC_RESRA2L Reset: 00H                                               | Bit Field |                 | RESULT |   | VF  | DRC            |   | CHNR |           |

|                 | Result Register 2, View A Low                                        | Туре      |                 | rh     |   | rh  | rh             |   | rh   |           |

| CF <sub>H</sub> | ADC_RESRA2H Reset: 00 <sub>H</sub>                                   | Bit Field |                 |        |   | RES | SULT           |   |      |           |

|                 | Result Register 2, View A High                                       | Туре      |                 |        |   |     | h .            |   |      |           |

| D2 <sub>H</sub> | ADC_RESRA3L Reset: 00H                                               | Bit Field |                 | RESULT |   | VF  | DRC            |   | CHNR |           |

|                 | Result Register 3, View A Low                                        | Туре      | rh rh rh rh     |        |   |     |                |   |      |           |

| D3 <sub>H</sub> | ADC_RESRA3H Reset: 00 <sub>H</sub><br>Result Register 3, View A High | Bit Field | it Field RESULT |        |   |     |                |   |      |           |

|                 | Tresuit register 3, view A right                                     | Туре      |                 |        |   | 1   | h              |   |      |           |

| RMAP =          | = 0, PAGE 4                                                          |           |                 | 1      |   |     |                |   |      |           |

| CA <sub>H</sub> | ADC_RCR0 Reset: 00 <sub>H</sub> Result Control Register 0            | Bit Field | VFCT<br>R       | WFR    | 0 | IEN |                | 0 |      | DRCT<br>R |

|                 |                                                                      | Туре      | rw              | rw     | r | rw  |                | r |      | rw        |

# 3.2.4.10 CCU6 Registers

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

Table 14 CCU6 Register Overview

| Addr            | Register Name                                                             | Bit       | 7          | 6          | 5            | 4          | 3          | 2          | 1          | 0          |

|-----------------|---------------------------------------------------------------------------|-----------|------------|------------|--------------|------------|------------|------------|------------|------------|

| RMAP =          | = 0                                                                       | •         |            | •          |              |            |            |            |            | •          |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00H                                                      | Bit Field | С          | )P         | ST           | NR         | 0          |            | PAGE       |            |

|                 | Page Register                                                             | Туре      | ١          | N          | ١            | V          | r          | rwh        |            |            |

| RMAP =          | = 0, PAGE 0                                                               |           | •          |            | •            |            | •          | •          |            |            |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00H                                                   | Bit Field |            |            |              | CC6        | 3SL        |            |            |            |

|                 | Capture/Compare Shadow Register for Channel CC63 Low                      | Туре      |            |            |              | r          | W          |            |            |            |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00H                                                   | Bit Field |            |            |              | CC6        | 3SH        |            |            |            |

|                 | Capture/Compare Shadow Register for Channel CC63 High                     | Туре      |            |            |              | r          | W          |            |            |            |

| 9CH             | CCU6_TCTR4L Reset: 00 <sub>H</sub> Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR | (            | )          | DT<br>RES  | T12<br>RES | T12R<br>S  | T12R<br>R  |

|                 |                                                                           | Туре      | W          | W          | ı            | r          | W          | W          | W          | W          |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub> Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |              | 0          |            | T13<br>RES | T13R<br>S  | T13R<br>R  |

|                 |                                                                           | Туре      | W          | W          |              | r          |            | W          | W          | W          |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub> Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          |              |            | MCI        | MPS        |            |            |

|                 | Register Low                                                              | Туре      | W          | r          |              |            | r          | W          |            |            |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub> Multi-Channel Mode Output Shadow     | Bit Field | STRH<br>P  | 0          |              | CURHS      |            |            | EXPHS      |            |

|                 | Register High                                                             | Туре      | W          | r          |              | rw         |            | rw         |            |            |

| A4 <sub>H</sub> | CCU6_ISRL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status         | Bit Field | RT12<br>PM | RT12<br>OM | RCC6<br>2F   | RCC6<br>2R | RCC6<br>1F | RCC6<br>1R | RCC6<br>0F | RCC6<br>0R |

|                 | Reset Register Low                                                        | Туре      | W          | W          | W            | W          | W          | W          | W          | W          |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWH<br>E     | RCHE       | 0          | RTRP<br>F  | RT13<br>PM | RT13<br>CM |

|                 | Reset Register High                                                       | Туре      | W          | W          | W            | W          | r          | W          | W          | w          |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub> Compare State Modification Register | Bit Field | 0          | MCC6<br>3S |              | 0          |            | MCC6<br>2S | MCC6<br>1S | MCC6<br>0S |

|                 | Low                                                                       | Туре      | r          | W          |              | r          |            | W          | W          | W          |

| A7 <sub>H</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub> Compare State Modification Register | Bit Field | 0          | MCC6<br>3R | 0 MCC6<br>2R |            |            | MCC6<br>1R | MCC6<br>0R |            |

|                 | High                                                                      | Туре      | r          | W          | r w w        |            | W          | W          |            |            |

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00H                                                   | Bit Field |            |            |              | CC6        | 0SL        |            |            |            |

|                 | Capture/Compare Shadow Register for Channel CC60 Low                      | Туре      |            |            |              | rv         | vh         |            |            |            |

| FBH             | CCU6_CC60SRH Reset: 00 <sub>H</sub>                                       | Bit Field |            |            |              | CC6        | 0SH        |            |            |            |

|                 | Capture/Compare Shadow Register for Channel CC60 High                     | Туре      |            |            |              | rv         | vh         |            |            |            |

# Table 14 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                  | Bit       | 7               | 6               | 5           | 4           | 3           | 2           | 1           | 0           |  |  |

|-----------------|--------------------------------------------------------------------------------|-----------|-----------------|-----------------|-------------|-------------|-------------|-------------|-------------|-------------|--|--|

| FDH             | CCU6_CC61RH Reset: 00H                                                         | Bit Field |                 | l.              |             | CC6         | 1VH         | l.          | l.          |             |  |  |

|                 | Capture/Compare Register for Channel CC61 High                                 | Туре      |                 |                 |             | r           | h           |             |             |             |  |  |

| FE <sub>H</sub> | CCU6_CC62RL Reset: 00H                                                         | Bit Field |                 |                 |             | CC6         | 2VL         |             |             |             |  |  |

|                 | Capture/Compare Register for Channel CC62 Low                                  | Туре      |                 |                 |             | r           | h           |             |             |             |  |  |

| FF <sub>H</sub> | CCU6_CC62RH Reset: 00H                                                         | Bit Field |                 | CC62VH          |             |             |             |             |             |             |  |  |

|                 | Capture/Compare Register for Channel CC62 High                                 | Туре      |                 |                 |             | r           | h           |             |             |             |  |  |

| RMAP =          | = 0, PAGE 2                                                                    |           |                 |                 |             |             |             |             |             |             |  |  |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00H                                                       | Bit Field |                 | MSE             | EL61        |             |             | MSE         | EL60        |             |  |  |

|                 | T12 Capture/Compare Mode Select Register Low                                   | Туре      |                 | r               | w           |             |             | r           | w           |             |  |  |

| 9B <sub>H</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub>                                           | Bit Field | DBYP            |                 | HSYNC       |             |             | MSE         | EL62        |             |  |  |

|                 | T12 Capture/Compare Mode Select<br>Register High                               | Туре      | rw              |                 | rw          |             |             | r           | w           |             |  |  |

| 9CH             | CCU6_IENL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Enable Register Low | Bit Field | ENT1<br>2<br>PM | ENT1<br>2<br>OM | ENCC<br>62F | ENCC<br>62R | ENCC<br>61F | ENCC<br>61R | ENCC<br>60F | ENCC<br>60R |  |  |

|                 |                                                                                | Туре      | rw              | rw              | rw          | rw          | rw          | rw          | rw          | rw          |  |  |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Enable              | Bit Field | EN<br>STR       | EN<br>IDLE      | EN<br>WHE   | EN<br>CHE   | 0           | EN<br>TRPF  | ENT1<br>3PM | ENT1<br>3CM |  |  |

|                 | Register High                                                                  | Туре      | rw              | rw              | rw          | rw          | r           | rw          | rw          | rw          |  |  |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub>                                               | Bit Field | INP             | CHE             | INPO        | CC62        | INPO        | CC61        | INPO        | CC60        |  |  |

|                 | Capture/Compare Interrupt Node Pointer Register Low                            | Туре      | r               | w               | r           | w           | r           | w           | r           | w           |  |  |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub>                                               | Bit Field | (               | )               | INPT13      |             | INPT12      |             | INP         | ERR         |  |  |

|                 | Capture/Compare Interrupt Node Pointer Register High                           | Туре      | !               | r               | rw          |             | rw          |             | rw          |             |  |  |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status              | Bit Field | ST12<br>PM      | ST12<br>OM      | SCC6<br>2F  | SCC6<br>2R  | SCC6<br>1F  | SCC6<br>1R  | SCC6<br>0F  | SCC6<br>0R  |  |  |

|                 | Set Register Low                                                               | Туре      | W               | W               | w           | W           | W           | W           | W           | W           |  |  |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status              | Bit Field | SSTR            | SIDLE           | SWHE        | SCHE        | SWH<br>C    | STRP<br>F   | ST13<br>PM  | ST13<br>CM  |  |  |

|                 | Set Register High                                                              | Туре      | W               | W               | w           | W           | W           | W           | W           | W           |  |  |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub> Passive State Level Register                  | Bit Field | PSL63           | 0               |             |             | P           | SL          |             |             |  |  |

|                 | Passive State Level Register                                                   | Туре      | rwh             | r               |             |             | rv          | vh          |             |             |  |  |

| A7 <sub>H</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub> Multi-Channel Mode Control Register         | Bit Field | (               | )               | SW          | SYN         | 0           |             | SWSEL       |             |  |  |

|                 | Wulti-Charmer Wode Control Negister                                            | Туре      | ı               | r               | r           | W           | r           |             | rw          |             |  |  |

| FA <sub>H</sub> | CCU6_TCTR2L Reset: 00 <sub>H</sub> Timer Control Register 2 Low                | Bit Field | 0               | T13             | TED T       |             | T13TEC      |             | T13<br>SSC  | T12<br>SSC  |  |  |

|                 |                                                                                | Туре      | r               | r               | W           |             | rw          |             | rw          | rw          |  |  |

| FB <sub>H</sub> | CCU6_TCTR2H Reset: 00 <sub>H</sub> Timer Control Register 2 High               | Bit Field |                 |                 | 0           |             | T13F        | RSEL        | T12F        | RSEL        |  |  |

|                 | Timor Control Negister 2 High                                                  | Туре      |                 |                 | r           |             | rw rw       |             |             |             |  |  |

| FC <sub>H</sub> | CCU6_MODCTRL Reset: 00 <sub>H</sub> Modulation Control Register Low            | Bit Field | MCM<br>EN       | 0               | T12MODEN    |             |             |             |             |             |  |  |

|                 |                                                                                | Туре      | rw              | r               |             |             | r           | W           |             |             |  |  |

# 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 15 UART1 Register Overview

| Addr            | Register Name                                                   | Bit       | 7   | 6   | 5   | 4          | 3     | 2     | 1   | 0    |

|-----------------|-----------------------------------------------------------------|-----------|-----|-----|-----|------------|-------|-------|-----|------|

| RMAP =          | = 1                                                             |           | I.  | ı   | Į.  | ı          | Į.    | ı     |     | l .  |

| C8H             | SCON Reset: 00 <sub>H</sub>                                     | Bit Field | SM0 | SM1 | SM2 | REN        | TB8   | RB8   | TI  | RI   |

|                 | Serial Channel Control Register                                 | Туре      | rw  | rw  | rw  | rw         | rw    | rwh   | rwh | rwh  |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                                     | Bit Field |     |     |     | V          | AL    |       |     |      |

|                 | Serial Data Buffer Register                                     | Туре      |     |     |     | rv         | vh    |       |     |      |

| CA <sub>H</sub> | BCON Reset: 00 <sub>H</sub>                                     | Bit Field |     | (   | )   |            |       | BRPRE |     | R    |

|                 | Baud Rate Control Register                                      | Туре      |     |     | r   |            |       | rw    |     | rw   |

| СВН             | BG Reset: 00 <sub>H</sub>                                       | Bit Field |     |     |     | BR_V       | 'ALUE |       |     |      |

|                 | Baud Rate Timer/Reload Register                                 | Туре      | rwh |     |     |            |       |       |     |      |

| ССН             | FDCON Reset: 00 <sub>H</sub>                                    | Bit Field |     |     | 0   |            |       | NDOV  | FDM | FDEN |

|                 | Fractional Divider Control Register                             | Туре      |     |     | r   |            |       | rwh   | rw  | rw   |

| CDH             | FDSTEP Reset: 00 <sub>H</sub>                                   | Bit Field |     |     |     | ST         | EP    |       |     |      |

|                 | Fractional Divider Reload Register                              | Туре      |     |     |     | r          | W     |       |     |      |

| CEH             | FDRES Reset: 00 <sub>H</sub>                                    | Bit Field |     |     |     | RES        | SULT  |       |     |      |

|                 | Fractional Divider Result Register                              | Туре      | rh  |     |     |            |       |       |     |      |

| CF <sub>H</sub> | SCON1 Reset: 07 <sub>H</sub><br>Serial Channel Control Register | Bit Field |     |     |     | NDOV<br>EN | TIEN  | RIEN  |     |      |

|                 | 1                                                               | Туре      |     |     | r   |            |       | rw    | rw  | rw   |

# 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

Table 16 SSC Register Overview

| Addr            | Register Name                            | Bit       | 7  | 6  | 5  | 4    | 3   | 2   | 1   | 0   |  |

|-----------------|------------------------------------------|-----------|----|----|----|------|-----|-----|-----|-----|--|

| RMAP =          | 0                                        |           |    |    |    |      |     |     |     |     |  |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00H                     | Bit Field |    |    | 0  |      |     | CIS | SIS | MIS |  |

|                 | Port Input Select Register               | Туре      |    |    | r  |      |     | rw  | rw  | rw  |  |

| $AA_H$          | SSC_CONL Reset: 00H                      | Bit Field | LB | РО | PH | НВ   |     | ВМ  |     |     |  |

|                 | Control Register Low<br>Programming Mode | Туре      | rw | rw | rw | rw   |     | r   | W   |     |  |

| $AA_H$          | SSC_CONL Reset: 00H                      | Bit Field |    | (  | )  |      |     | В   | BC  |     |  |

|                 | Control Register Low<br>Operating Mode   | Туре      | r  |    |    |      |     | rh  |     |     |  |

| AB <sub>H</sub> | SSC_CONH Reset: 00H                      |           | EN | MS | 0  | AREN | BEN | PEN | REN | TEN |  |

|                 | Control Register High Programming Mode   | Туре      | rw | rw | r  | rw   | rw  | rw  | rw  | rw  |  |

#### 3.7 Reset Control

The XC87x has five types of reset: power-on reset, hardware reset, watchdog timer reset, power-down wake-up reset, and brownout reset.

When the XC87x is first powered up, the status of certain pins (see **Table 25**) must be defined to ensure proper start operation of the device. At the end of a reset sequence, the sampled values are latched to select the desired boot option, which cannot be modified until the next power-on reset or hardware reset. This guarantees stable conditions during the normal operation of the device.

The second type of reset in XC87x is the hardware reset. This reset function can be used during normal operation or when the chip is in power-down mode. A reset input pin RESET is provided for the hardware reset.

The Watchdog Timer (WDT) module is also capable of resetting the device if it detects a malfunction in the system.

Another type of reset that needs to be detected is a reset while the device is in power-down mode (wake-up reset). While the contents of the static RAM are undefined after a power-on reset, they are well defined after a wake-up reset from power-down mode.

### 3.7.1 Module Reset Behavior

**Table 24** lists the functions of the XC87x and the various reset types that affect these functions. The symbol "■" signifies that the particular function is reset to its default state.

Table 24 Effect of Reset on Device Functions

| Module/<br>Function   | Wake-Up<br>Reset                     | Watchdog<br>Reset         | Hardware<br>Reset         | Power-On<br>Reset         | Brownout<br>Reset         |

|-----------------------|--------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| CPU Core              |                                      |                           |                           |                           |                           |

| Peripherals           |                                      |                           |                           |                           |                           |

| On-Chip<br>Static RAM | Not affected,<br>Reliable            | Not affected,<br>Reliable | Not affected,<br>Reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected              |                           |                           |                           |

| Port Pins             |                                      |                           |                           |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected              | Not affected              |                           |                           |

| FLASH                 |                                      |                           |                           |                           |                           |

| NMI                   | Disabled                             | Disabled                  |                           |                           |                           |

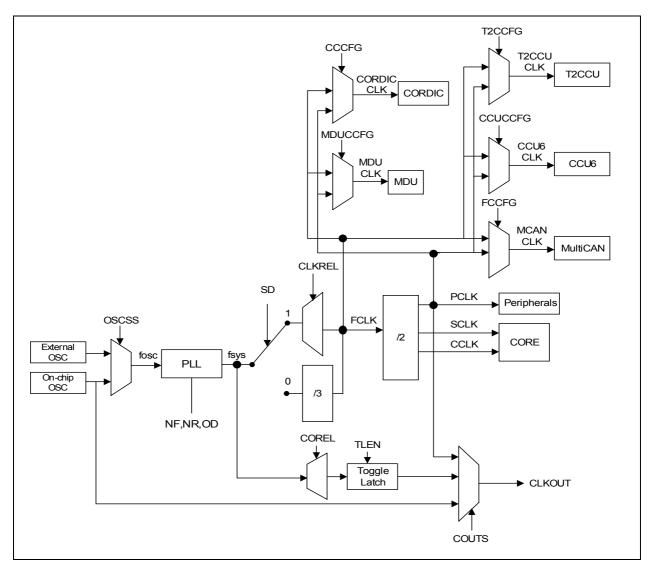

Figure 22 Clock Generation from  $f_{\rm sys}$

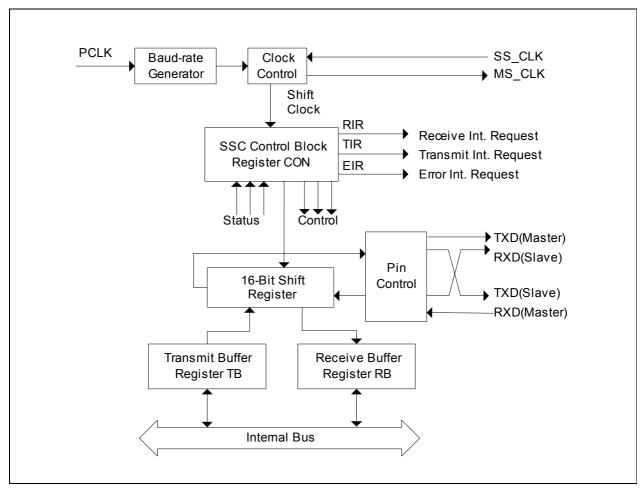

Figure 28 SSC Block Diagram

### 3.19 Timer 2 Capture/Compare Unit

The T2CCU (Timer 2 Capture/Compare Unit) consists of the standard Timer 2 unit and a Capture/compare unit (CCU). The Capture/Compare Timer (CCT) is part of the CCU. Control is available in the T2CCU to select individually for each of its 16-bit capture/compare channel, either the Timer 2 or the Capture/Compare Timer (CCT) as the time base. Both timers have a resolution of 16 bits. The clock frequency of T2CCU,  $f_{T2CCU}$ , could be set at PCLK frequency or 2 times the PCLK frequency.

The T2CCU can be used for various digital signal generation and event capturing like pulse generation, pulse width modulation, pulse width measuring etc. Target applications include various automotive control as well as industrial (frequency generation, digital-to-analog conversion, process control etc.).

#### **T2CCU Features**

- Option to select individually for each channel, either Timer 2 or Capture/Compare Timer as time base

- Extremely flexible Capture/Compare Timer count rate by cascading with Timer 2

- Capture/Compare Timer may be 'reset' immediately by triggering overflow event

- 16-bit resolution

- Six compare channels in total

- Four capture channels multiplexed with the compare channels, in total

- Shadow register for each compare register

- Transfer via software control or on timer overflow.

- Compare Mode 0: Compare output signal changes from the inactive level to active level on compare match. Returns to inactive level on timer overflow.

- Active level can be defined by register bit for channel groups A and B.

- Support of 0% to 100% duty cycle in compare mode 0.

- Compare Mode 1: Full control of the software on the compare output signal level, for the next compare match.

- Concurrent Compare Mode with channel 0

- Capture Mode 0: Capture on any external event (rising/falling/both edge) at the 4 pins T2CC0 to T2CC3.

- Capture Mode 1: Capture upon writing to the low byte of the corresponding channel capture register.

- Capture mode 0 or 1 can be established independently on the 4 capture channels.

Data Sheet 98 V1.5, 2011-03

### 3.20 Capture/Compare Unit 6

The Capture/Compare Unit 6 (CCU6) provides two independent timers (T12, T13), which can be used for Pulse Width Modulation (PWM) generation, especially for AC-motor control. The CCU6 also supports special control modes for block commutation and multi-phase machines.

The timer T12 can function in capture and/or compare mode for its three channels. The timer T13 can work in compare mode only.

The multi-channel control unit generates output patterns, which can be modulated by T12 and/or T13. The modulation sources can be selected and combined for the signal modulation.

#### **Timer T12 Features**

- Three capture/compare channels, each channel can be used either as a capture or as a compare channel

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and lowside switches)

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Dead-time control for each channel to avoid short-circuits in the power stage

- Concurrent update of the required T12/13 registers

- Generation of center-aligned and edge-aligned PWM

- Supports single-shot mode

- Supports many interrupt request sources

- Hysteresis-like control mode

#### **Timer T13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock frequency

- Can be synchronized to T12

- Interrupt generation at period-match and compare-match

- Supports single-shot mode

#### **Additional Features**

- Implements block commutation for Brushless DC-drives

- Position detection via Hall-sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- Control modes for multi-channel AC-drives

- Output levels can be selected and adapted to the power stage

The block diagram of the CCU6 module is shown in Figure 29.

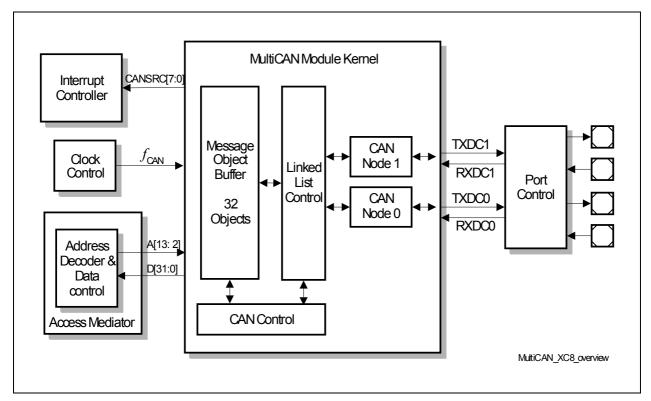

### 3.21 Controller Area Network (MultiCAN)

The MultiCAN module contains two Full-CAN nodes operating independently or exchanging data and remote frames via a gateway function. Transmission and reception of CAN frames is handled in accordance to CAN specification V2.0 B active. Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

Both CAN nodes share a common set of message objects, where each message object may be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects may be combined to build gateways between the CAN nodes or to setup a FIFO buffer.

The message objects are organized in double chained lists, where each CAN node has it's own list of message objects. A CAN node stores frames only into message objects that are allocated to the list of the CAN node. It only transmits messages from objects of this list. A powerful, command driven list controller performs all list operations.

The bit timings for the CAN nodes are derived from the peripheral clock ( $f_{\text{CAN}}$ ) and are programmable up to a data rate of 1 MBaud. A pair of receive and transmit pins connects each CAN node to a bus transceiver.

Figure 30 Overview of the MultiCAN

#### **Features**

Compliant to ISO 11898.

### **Package and Quality Declaration**

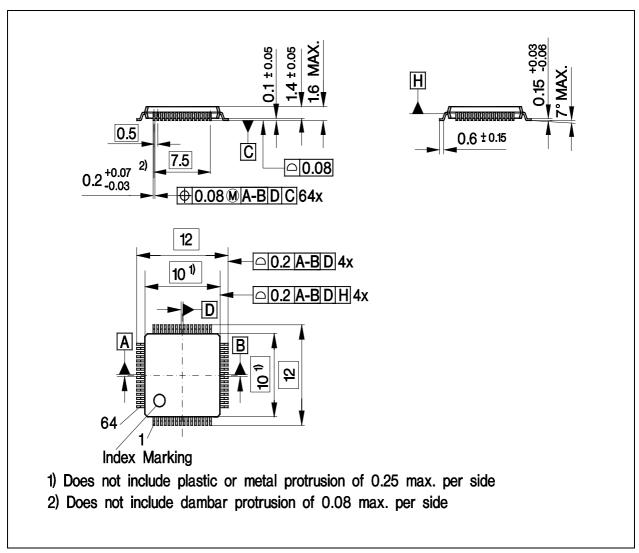

# 5.2 Package Outline

Figure 47 shows the package outlines of the XC878.

Figure 47 PG-LQFP-64-4 Package Outline