Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D.A. II.                   |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Details                    |                                                                                   |

| Product Status             | Discontinued at Digi-Key                                                          |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 27MHz                                                                             |

| Connectivity               | SPI, SSI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 40                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 3.25K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP                                                                           |

| Supplier Device Package    | PG-LQFP-64-4                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc878m-16ffi-5v-aa |

#### **General Device Information**

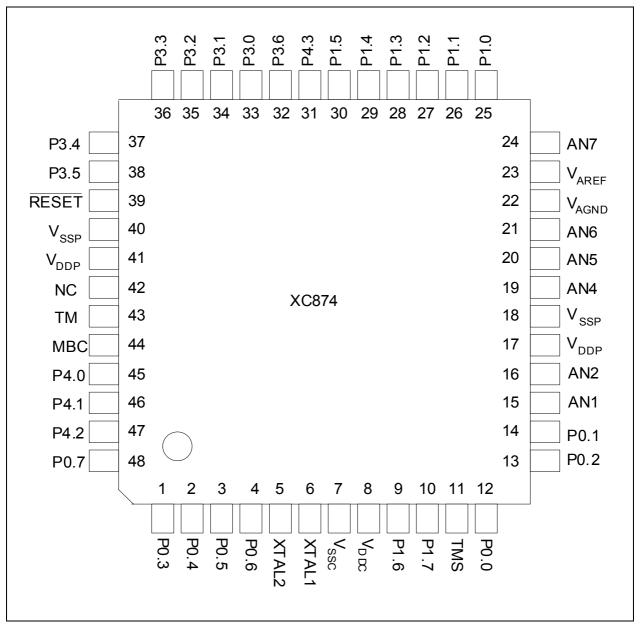

Figure 5 XC874 Pin Configuration, PG-VQFN-48 Package (top view)

## **General Device Information**

Table 3

Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                                                                                                                                                                                                                                   |                                                                                                                                                            |  |  |  |

|--------|--------------------------------------|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| P4     |                                      | I/O  |                | Port 4 Port 4 is an 8-bit bidirectional general purpo I/O port. It can be used as alternate function for CCU6, Timer 0, Timer 1, T2CCU, Timer 2 MultiCAN and External Bus Interface.  Note: External Bus Interface is not available XC874. |                                                                                                                                                            |  |  |  |

| P4.0   | 59/45                                |      | Hi-Z           | RXDC0_3<br>CC60_1<br>T2CC0_0/<br>EXINT3_1<br>D0                                                                                                                                                                                            | MultiCAN Node 0 Receiver Input Output of Capture/Compare channel 0 External Interrupt Input 3/T2CCU Capture/Compare Channel 0 Data Line 0 Input/Output     |  |  |  |

| P4.1   | 60/46                                |      | Hi-Z           | TXDC0_3 COUT60_1 T2CC1_0/ EXINT4_1 D1                                                                                                                                                                                                      | MultiCAN Node 0 Transmitter Output Output of Capture/Compare channel 0 External Interrupt Input 4/T2CCU Capture/Compare Channel 1 Data Line 1 Input/Output |  |  |  |

| P4.2   | 61/47                                |      | PU             | EXINT6_1<br>T21_0<br>D2                                                                                                                                                                                                                    | External Interrupt Input 6 Timer 21 Input Data Line 2 Input/Output                                                                                         |  |  |  |

| P4.3   | 40/31                                |      | Hi-Z           | T2EX_1<br>EXF21_1<br>COUT63_2<br>D3                                                                                                                                                                                                        | Timer 2 External Trigger Input Timer 21 External Flag Output Output of Capture/Compare channel 3 Data Line 3 Input/Output                                  |  |  |  |

| P4.4   | 45/-                                 |      | Hi-Z           | CCPOS0_3<br>T0_0<br>CC61_4<br>T2CC2_0/<br>EXINT5_1<br>D4                                                                                                                                                                                   | CCU6 Hall Input 0 Timer 0 Input Output of Capture/Compare channel 1 External Interrupt Input 5/T2CCU Capture/Compare Channel 2 Data Line 4 Input/Output    |  |  |  |

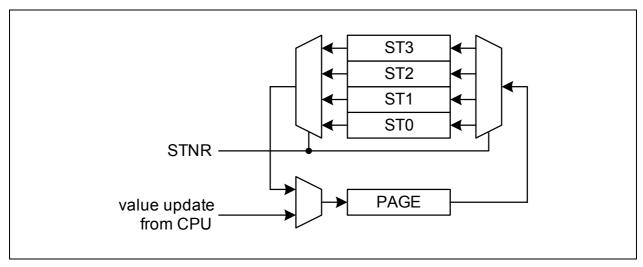

- Overwrite the contents of PAGE with the contents of STx, ignoring the value written to the bit positions of PAGE

- (this is done at the end of the interrupt routine to restore the previous page setting before the interrupt occurred)

Figure 11 Storage Elements for Paging

With this mechanism, a certain number of interrupt routines (or other routines) can perform page changes without reading and storing the previously used page information. The use of only write operations makes the system simpler and faster. Consequently, this mechanism significantly improves the performance of short interrupt routines.

The XC87x supports local address extension for:

- Parallel Ports

- Analog-to-Digital Converter (ADC)

- Capture/Compare Unit 6 (CCU6)

- System Control Registers

Data Sheet 30 V1.5, 2011-03

Table 7

CORDIC Register Overview (cont'd)

| Addr            | Register Name                                          | Bit       | 7                                             | 6         | 5         | 4    | 3          | 2   | 1         | 0   |  |  |

|-----------------|--------------------------------------------------------|-----------|-----------------------------------------------|-----------|-----------|------|------------|-----|-----------|-----|--|--|

| 9C <sub>H</sub> | CD_CORDYL Reset: 00H                                   | Bit Field |                                               | DATAL     |           |      |            |     |           |     |  |  |

|                 | CORDIC Y Data Low Byte                                 | Туре      |                                               | rw        |           |      |            |     |           |     |  |  |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00H                                   | Bit Field |                                               |           |           | DA   | ГАН        |     |           |     |  |  |

|                 | CORDIC Y Data High Byte                                | Туре      | rw                                            |           |           |      |            |     |           |     |  |  |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00H                                   | Bit Field |                                               |           |           | DA   | TAL        |     |           |     |  |  |

|                 | CORDIC Z Data Low Byte                                 | Туре      |                                               |           |           | r    | w          |     |           |     |  |  |

| 9F <sub>H</sub> | CD_CORDZH Reset: 00H                                   | Bit Field |                                               |           |           | DA   | ГАН        |     |           |     |  |  |

|                 | CORDIC Z Data High Byte                                | Туре      |                                               |           |           | r    | w          |     |           |     |  |  |

| A0 <sub>H</sub> | CD_STATC Reset: 00 <sub>H</sub> CORDIC Status and Data | Bit Field | KEEP<br>Z                                     | KEEP<br>Y | KEEP<br>X | DMAP | INT_E<br>N | EOC | ERRO<br>R | BSY |  |  |

|                 | Control Register                                       | Туре      | rw                                            | rw        | rw        | rw   | rw         | rwh | rh        | rh  |  |  |

| A1 <sub>H</sub> | CD_CON Reset: 00 <sub>H</sub> CORDIC Control Register  | Bit Field | ield MPS X_USI ST_M ROTV MODE ST<br>GN ODE EC |           |           |      |            | ST  |           |     |  |  |

|                 |                                                        | Туре      | n                                             | N         | rw        | rw   | rw         | r   | W         | rwh |  |  |

# 3.2.4.4 System Control Registers

The system control SFRs can be accessed in the mapped memory area (RMAP = 0).

Table 8 SCU Register Overview

| Addr            | Register Name                                                    | Bit       | 7 | 6           | 5            | 4            | 3            | 2            | 1            | 0           |

|-----------------|------------------------------------------------------------------|-----------|---|-------------|--------------|--------------|--------------|--------------|--------------|-------------|

| RMAP =          | : 0 or 1                                                         | •         |   | •           | •            |              | •            | •            |              |             |

| 8F <sub>H</sub> | SYSCON0 Reset: 04 <sub>H</sub><br>System Control Register 0      | Bit Field | 0 |             |              | IMOD<br>E    |              | 1            | 0            | RMAP        |

|                 |                                                                  | Туре      |   | r           |              | rw           | r            | r            | r            | rw          |

| RMAP =          | 0                                                                |           |   |             |              |              |              |              |              |             |

| BFH             | SCU_PAGE Reset: 00H                                              | Bit Field | С | )P          | ST           | NR           | 0            |              | PAGE         |             |

|                 | Page Register                                                    | Туре      | 1 | N           | ١            | V            | r            |              | rwh          |             |

| RMAP =          | 0, PAGE 0                                                        |           |   |             |              |              |              |              |              |             |

| вз <sub>Н</sub> | MODPISEL Reset: 00 <sub>H</sub> Peripheral Input Select Register | Bit Field | 0 | URRIS<br>H  | JTAGT<br>DIS | JTAGT<br>CKS | EXINT<br>2IS | EXINT<br>1IS | EXINT<br>0IS | URRIS       |

|                 |                                                                  | Туре      | r | rw          | rw           | rw           | rw           | rw           | rw           | rw          |

| <sup>B4</sup> H | IRCON0 Reset: 00 <sub>H</sub> Interrupt Request Register 0       | Bit Field | 0 | EXINT<br>6  | EXINT<br>5   | EXINT<br>4   | EXINT 3      | EXINT<br>2   | EXINT<br>1   | EXINT<br>0  |

|                 |                                                                  | Туре      | r | rwh         | rwh          | rwh          | rwh          | rwh          | rwh          | rwh         |

| в5 <sub>Н</sub> | IRCON1 Reset: 00 <sub>H</sub> Interrupt Request Register 1       | Bit Field | 0 | CANS<br>RC2 | CANS<br>RC1  | ADCS<br>R1   | ADCS<br>R0   | RIR          | TIR          | EIR         |

|                 |                                                                  | Туре      | r | rwh         | rwh          | rwh          | rwh          | rwh          | rwh          | rwh         |

| в6 <sub>Н</sub> | IRCON2 Reset: 00 <sub>H</sub> Interrupt Request Register 2       | Bit Field | _ | 0           |              | CANS<br>RC3  |              | 0            |              | CANS<br>RC0 |

|                 |                                                                  | Туре      |   | r           |              | rwh          |              | r            |              | rwh         |

## 3.2.4.5 WDT Registers

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 9 WDT Register Overview

| Addr            | Register Name                                        | Bit       | 7       | 6  | 5          | 4         | 3   | 2         | 1         | 0         |  |

|-----------------|------------------------------------------------------|-----------|---------|----|------------|-----------|-----|-----------|-----------|-----------|--|

| RMAP =          | : 1                                                  |           |         | •  |            | •         |     | •         |           |           |  |

| ввн             | WDTCON Reset: 00 <sub>H</sub> Watchdog Timer Control | Bit Field | (       | )  | WINB<br>EN | WDTP<br>R | 0   | WDTE<br>N | WDTR<br>S | WDTI<br>N |  |

|                 | Register                                             | Туре      | r       |    | rw         | rh        | r   | rw        | rwh       | rw        |  |

| всн             | WDTREL Reset: 00 <sub>H</sub>                        | Bit Field |         |    |            | WDT       | REL |           |           |           |  |

|                 | Watchdog Timer Reload<br>Register                    | Туре      |         |    |            | r         | w   |           |           |           |  |

| BD <sub>H</sub> | WDTWINB Reset: 00H                                   | Bit Field | WDTWINB |    |            |           |     |           |           |           |  |

|                 | Watchdog Window-Boundary Count Register              | Туре      |         |    |            | r         | w   |           |           |           |  |

| BE <sub>H</sub> | WDTL Reset: 00 <sub>H</sub>                          | Bit Field |         |    |            | W         | DT  |           |           |           |  |

|                 | Watchdog Timer Register Low Type                     |           |         | rh |            |           |     |           |           |           |  |

| BF <sub>H</sub> | WDTH Reset: 00 <sub>H</sub>                          |           |         |    |            | W         | DT  |           |           |           |  |

|                 | Watchdog Timer Register High                         | Туре      |         |    |            | r         | h   |           |           |           |  |

# 3.2.4.6 Port Registers

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

Table 10 Port Register Overview

| Addr            | Register Name         |                    | Bit       | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------|-----------------------|--------------------|-----------|-----|-----|-----|-----|-----|-----|-----|-----|

| RMAP =          | = 0                   |                    |           |     | •   |     |     |     |     |     |     |

| B2 <sub>H</sub> | PORT_PAGE Reset: 00H  |                    | Bit Field | 0   | P   | ST  | NR  | 0   |     |     |     |

|                 | Page Register         |                    | Туре      | ٧   | v   | V   | V   | r   |     | rwh |     |

| RMAP =          | 0, PAGE 0             |                    |           |     |     |     |     |     |     |     |     |

| 80 <sub>H</sub> | P0_DATA Rese          | t: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P0 Data Register      |                    | Туре      | rwh |

| 86 <sub>H</sub> |                       | t: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P0 Direction Register |                    | Туре      | rw  |

| 90 <sub>H</sub> | P1_DATA Rese          | t: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P1 Data Register      |                    | Туре      | rwh |

| 91 <sub>H</sub> |                       | t: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P1 Direction Register |                    | Туре      | rw  |

| 92 <sub>H</sub> |                       | t: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P5 Data Register      |                    | Туре      | rwh |

| 93 <sub>H</sub> |                       | t: 00 <sub>H</sub> | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P5 Direction Register |                    | Туре      | rw  |

## Table 12 T2CCU Register Overview (cont'd)

| Addr            | Register Name                                             | Bit       | 7            | 6    | 5          | 4          | 3          | 2           | 1          | 0          |

|-----------------|-----------------------------------------------------------|-----------|--------------|------|------------|------------|------------|-------------|------------|------------|

| C5 <sub>H</sub> | T2CCU_CCTH Reset: 00H                                     | Bit Field |              |      |            | C          | CT         |             |            |            |

|                 | T2CCU Capture/Compare Timer Register High                 | Туре      |              |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CCTCON Reset: 00 <sub>H</sub> T2CCU CaptureCcompare | Bit Field |              | ССТ  | PRE        |            | CCTO<br>VF | CCTO<br>VEN | TIMSY<br>N | CCTS<br>T  |

|                 | Timer Control Register                                    | Туре      |              | r    | W          |            | rwh        | rw          | rw         | rw         |

| RMAP =          | : 0, PAGE 2                                               |           |              |      |            |            |            |             |            |            |

| C0H             | T2CCU_COSHDWReset: 00 <sub>H</sub> T2CCU Capture/compare  | Bit Field | ENSH<br>DW   | TXOV | COOU<br>T5 | COOU<br>T4 | COOU<br>T3 | COOU<br>T2  | COOU<br>T1 | COOU<br>T0 |

|                 | Enable Register                                           | Туре      | rwh          | rwh  | rwh        | rwh        | rwh        | rwh         | rwh        | rwh        |

| C1 <sub>H</sub> | T2CCU_CC0L Reset: 00 <sub>H</sub> T2CCU Capture/Compare   | Bit Field |              |      |            | CC/        | /ALL       |             |            |            |

|                 | Register 0 Low                                            | Туре      | rwh          |      |            |            |            |             |            |            |

| C2 <sub>H</sub> | T2CCU_CC0H Reset: 00H                                     | Bit Field |              |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 0 High                  | Туре      | rwh          |      |            |            |            |             |            |            |

| C3 <sub>H</sub> | T2CCU_CC1L Reset: 00H                                     | Bit Field |              |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 1 Low                   | Туре      | rwh          |      |            |            |            |             |            |            |

| C4 <sub>H</sub> | T2CCU_CC1H Reset: 00 <sub>H</sub> T2CCU Capture/compare   | Bit Field |              |      |            | CCV        | /ALH       |             |            |            |

|                 | Register 1 High                                           | Туре      |              |      |            | rv         | vh         |             |            |            |

| C5 <sub>H</sub> | T2CCU_CC2L Reset: 00H                                     | Bit Field |              |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 2 Low                   | Туре      |              |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CC2H Reset: 00 <sub>H</sub>                         | Bit Field |              |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 2 High                  | Туре      |              |      |            | rv         | vh         |             |            |            |

| RMAP =          | : 0, PAGE 3                                               |           |              |      |            |            |            |             |            |            |

| C0H             | T2CCU_COCON Reset: 00 <sub>H</sub> T2CCU Compare Control  | Bit Field | CCM5         | CCM4 | CM5F       | CM4F       | POLB       | POLA        | CON        | ИOD        |

|                 | Register                                                  | Туре      | rw           | rw   | rwh        | rwh        | rw         | rw          | r          | W          |

| C1 <sub>H</sub> | T2CCU_CC3L Reset: 00H                                     | Bit Field |              |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 3 Low                   | Туре      |              |      |            | rv         | vh         |             |            |            |

| C2 <sub>H</sub> | T2CCU_CC3H Reset: 00H                                     | Bit Field |              |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 3 High                  | Туре      |              |      |            | rv         | vh         |             |            |            |

| СЗН             | T2CCU_CC4L Reset: 00H                                     | Bit Field |              |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 4 Low                   | Туре      | rwh          |      |            |            |            |             |            |            |

| C4 <sub>H</sub> | T2CCU_CC4H Reset: 00H                                     | Bit Field |              |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 4 High                  | Туре      |              |      |            | rv         | vh         |             |            |            |

| C5 <sub>H</sub> | T2CCU_CC5L Reset: 00H                                     | Bit Field | field CCVALL |      |            |            |            |             |            |            |

|                 | T2CCU Capture/compare<br>Register 5 Low                   | Туре      |              |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CC5H Reset: 00 <sub>H</sub>                         | Bit Field |              |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 5 High                  | Туре      |              |      |            | rv         | vh         |             |            |            |

## Table 14 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                                  | Bit       | 7               | 6               | 5           | 4           | 3           | 2           | 1           | 0           |  |  |

|-----------------|--------------------------------------------------------------------------------|-----------|-----------------|-----------------|-------------|-------------|-------------|-------------|-------------|-------------|--|--|

| FDH             | CCU6_CC61RH Reset: 00H                                                         | Bit Field |                 | l               |             | CC6         | 1VH         |             |             |             |  |  |

|                 | Capture/Compare Register for Channel CC61 High                                 | Туре      |                 |                 |             | r           | h           |             |             |             |  |  |

| FEH             | CCU6_CC62RL Reset: 00H                                                         | Bit Field |                 |                 |             | CC6         | S2VL        |             |             |             |  |  |

|                 | Capture/Compare Register for Channel CC62 Low                                  | Туре      |                 | rh              |             |             |             |             |             |             |  |  |

| FFH             | CCU6_CC62RH Reset: 00H                                                         | Bit Field |                 | CC62VH          |             |             |             |             |             |             |  |  |

|                 | Capture/Compare Register for<br>Channel CC62 High                              | Туре      |                 |                 |             | r           | h           |             |             |             |  |  |

| RMAP =          | = 0, PAGE 2                                                                    |           |                 |                 |             |             |             |             |             |             |  |  |

| 9A <sub>H</sub> | CCU6_T12MSELL Reset: 00 <sub>H</sub> T12 Capture/Compare Mode Select           | Bit Field |                 | MSE             | EL61        |             |             | MSE         | EL60        |             |  |  |

|                 | Register Low                                                                   | Туре      |                 | r               | W           |             |             | r           | W           |             |  |  |

| 9B <sub>H</sub> | CCU6_T12MSELH Reset: 00 <sub>H</sub> T12 Capture/Compare Mode Select           | Bit Field | DBYP            |                 | HSYNC       |             |             | MSE         | EL62        |             |  |  |

|                 | Register High                                                                  | Туре      | rw              |                 | rw          |             |             | r           | W           |             |  |  |

| 9C <sub>H</sub> | CCU6_IENL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Enable Register Low | Bit Field | ENT1<br>2<br>PM | ENT1<br>2<br>OM | ENCC<br>62F | ENCC<br>62R | ENCC<br>61F | ENCC<br>61R | ENCC<br>60F | ENCC<br>60R |  |  |

|                 |                                                                                | Туре      | rw              | rw              | rw          | rw          | rw          | rw          | rw          | rw          |  |  |

| 9D <sub>H</sub> | CCU6_IENH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Enable              | Bit Field | EN<br>STR       | EN<br>IDLE      | EN<br>WHE   | EN<br>CHE   | 0           | EN<br>TRPF  | ENT1<br>3PM | ENT1<br>3CM |  |  |

|                 | Register High                                                                  | Туре      | rw              | rw              | rw          | rw          | r           | rw          | rw          | rw          |  |  |

| 9E <sub>H</sub> | CCU6_INPL Reset: 40 <sub>H</sub>                                               | Bit Field | INP             | CHE             | INPO        | CC62        | INPO        | CC61        | INPO        | CC60        |  |  |

|                 | Capture/Compare Interrupt Node Pointer Register Low                            | Туре      | n               | W               | r           | w           | r           | w           | rw          |             |  |  |

| 9F <sub>H</sub> | CCU6_INPH Reset: 39 <sub>H</sub>                                               | Bit Field | (               | )               | INPT13      |             | INPT12      |             | INP         | ERR         |  |  |

|                 | Capture/Compare Interrupt Node Pointer Register High                           | Туре      | !               | r               | r           | w           | r           | W           | r           | w           |  |  |

| A4 <sub>H</sub> | CCU6_ISSL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status              | Bit Field | ST12<br>PM      | ST12<br>OM      | SCC6<br>2F  | SCC6<br>2R  | SCC6<br>1F  | SCC6<br>1R  | SCC6<br>0F  | SCC6<br>0R  |  |  |

|                 | Set Register Low                                                               | Туре      | W               | w               | W           | W           | w           | w           | w           | W           |  |  |

| A5 <sub>H</sub> | CCU6_ISSH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status              | Bit Field | SSTR            | SIDLE           | SWHE        | SCHE        | SWH<br>C    | STRP<br>F   | ST13<br>PM  | ST13<br>CM  |  |  |

|                 | Set Register High                                                              | Туре      | W               | w               | w           | W           | W           | W           | W           | W           |  |  |

| A6 <sub>H</sub> | CCU6_PSLR Reset: 00 <sub>H</sub> Passive State Level Register                  | Bit Field | PSL63           | 0               |             |             | P           | SL          |             |             |  |  |

|                 | Passive State Level Register                                                   | Туре      | rwh             | r               |             |             | rv          | vh          |             |             |  |  |

| A7 <sub>H</sub> | CCU6_MCMCTR Reset: 00 <sub>H</sub> Multi-Channel Mode Control Register         | Bit Field | (               | )               | SW          | SYN         | 0           |             | SWSEL       |             |  |  |

|                 | Wulli-Chaille Wode Control Negister                                            | Туре      | ı               | r               | r           | W           | r           |             | rw          |             |  |  |

| FA <sub>H</sub> | CCU6_TCTR2L Reset: 00 <sub>H</sub> Timer Control Register 2 Low                | Bit Field | 0               | T13             | TED         |             | T13TEC      |             | T13<br>SSC  | T12<br>SSC  |  |  |

|                 |                                                                                | Туре      | r               | r               | W           |             | rw          |             | rw          | rw          |  |  |

| FB <sub>H</sub> | CCU6_TCTR2H Reset: 00 <sub>H</sub> Timer Control Register 2 High               | Bit Field |                 |                 | 0           |             | T13F        | RSEL        | T12F        | RSEL        |  |  |

|                 | Timor Control Negrater 2 High                                                  | Туре      |                 |                 | r           |             | rw rw       |             |             |             |  |  |

| FC <sub>H</sub> | CCU6_MODCTRL Reset: 00 <sub>H</sub> Modulation Control Register Low            | Bit Field | MCM<br>EN       | 0               |             |             | T12M        | ODEN        |             |             |  |  |

|                 |                                                                                | Туре      | rw              | r               |             |             | r           | w           |             |             |  |  |

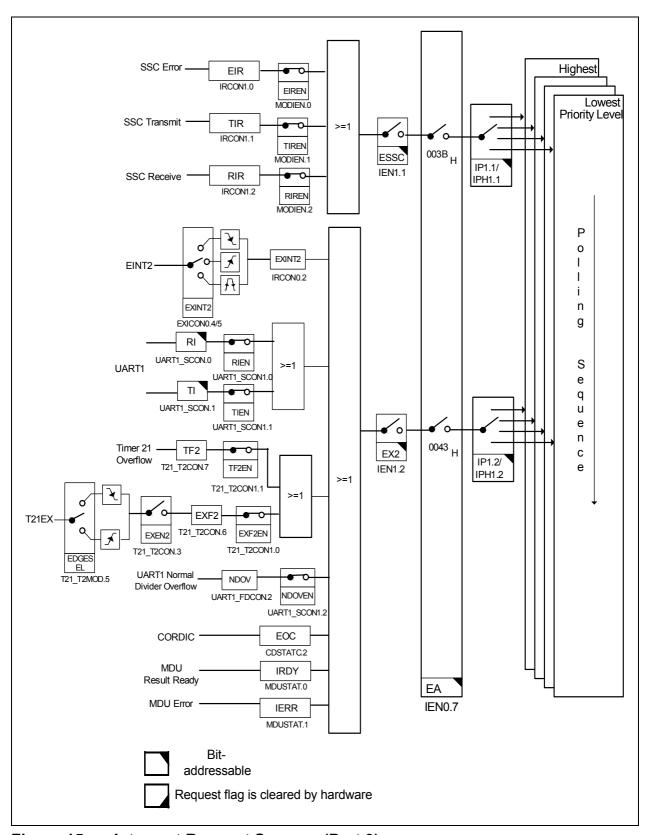

Figure 15 Interrupt Request Sources (Part 3)

#### 3.5 Parallel Ports

The XC87x has 40 port pins organized into five parallel ports: Port 0 (P0), Port 1 (P1), Port 3 (P3), Port 4 (P4) and Port 5 (P5). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. These ports are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected.

#### **Bidirectional Port Features**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- Configurable open drain mode

- Configurable drive strength

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

### 3.7.2 Booting Scheme

When the XC87x is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. **Table 25** shows the available boot options in the XC87x.

Table 25 XC87x Boot Selection 1)

| MBC | TMS | P0.0 | Type of Mode                                                                                                                                 | PC Start Value    |

|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1   | 0   | Х    | User Mode <sup>2)</sup> ; on-chip OSC/PLL non-bypassed                                                                                       | 0000 <sub>H</sub> |

| 0   | 0   | X    | BSL Mode; (LIN Mode <sup>3)</sup> , UART/ MultiCAN Mode <sup>4)5)</sup> and Alternate BSL Mode <sup>6)</sup> ); on-chip OSC/PLL non-bypassed | 0000 <sub>H</sub> |

| 0   | 1   | 0    | OCDS Mode; on-chip OSC/PLL non-<br>bypassed                                                                                                  | 0000 <sub>H</sub> |

| 1   | 1   | 0    | User (JTAG) Mode <sup>7)</sup> ; on-chip OSC/PLL non-bypassed (normal)                                                                       | 0000 <sub>H</sub> |

- 1) In addition to the pins MBC, TMS and P0.0, TM pin also requires an external pull down for all the boot options.

- 2) BSL mode is automatically entered if no valid password is installed and data at memory address 0000H equals zero.

- 3) If a device is programmed as LIN, LIN BSL is always used instead of UART/MultiCAN.

- 4) UART or MultiCAN BSL is decoded by firmware based on the protocol for product variant with MultiCAN. If no MultiCAN and LIN variant, UART BSL is used.

- 5) In MultiCAN BSL mode, the clock source is switched to XTAL by firmware, bypassing the on-chip oscillator. This avoids any frequency invariance with the on-chip oscillator and allows other frequency clock input, thus ensuring accurate baud rate detection (especially at high bit rates).

- 6) Alternate BSL Mode is a user defined BSL code programmed in Flash. It is entered if the AltBSLPassword is valid.

- 7) Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

Note: The boot options are valid only with the default set of UART and JTAG pins.

Data Sheet 74 V1.5, 2011-03

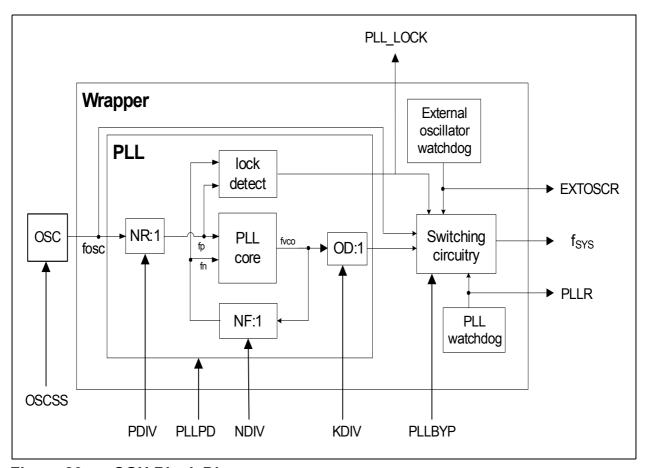

Figure 20 CGU Block Diagram

### **Direct Drive (PLL Bypass Operation)**

During PLL bypass operation, the system clock has the same frequency as the external clock source.

(3.1)

$$f_{SYS} = f_{OSC}$$

### **PLL Mode**

The CPU clock is derived from the oscillator clock, divided by the NR factor (PDIV), multiplied by the NF factor (NDIV), and divided by the OD factor (KDIV). PLL output must

### 3.9 Power Saving Modes

The power saving modes of the XC87x provide flexible power consumption through a combination of techniques, including:

- Stopping the CPU clock

- · Stopping the clocks of individual system components

- Reducing clock speed of some peripheral components

- Power-down of the entire system with fast restart capability

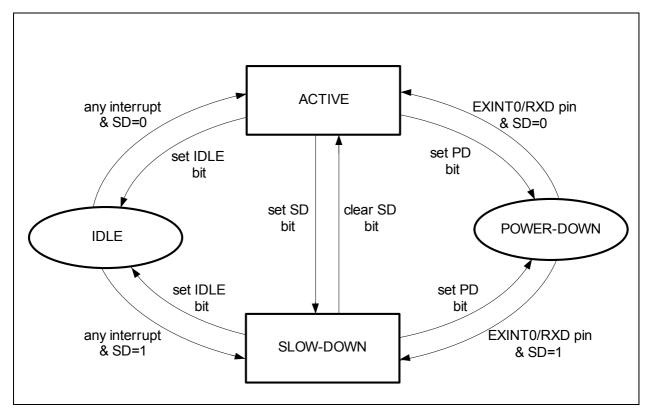

After a reset, the active mode (normal operating mode) is selected by default (see **Figure 23**) and the system runs in the main system clock frequency. From active mode, different power saving modes can be selected by software. They are:

- Idle mode

- Slow-down mode

- Power-down mode

Figure 23 Transition between Power Saving Modes

Note: SAK product variant does not support power-down mode.

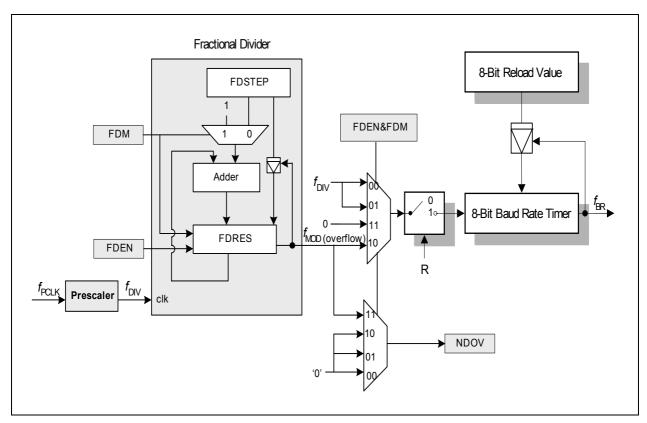

fractional divider) for generating a wide range of baud rates based on its input clock  $f_{PCLK}$ , see **Figure 26**.

Figure 26 Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.14**.

The baud rate ( $f_{BR}$ ) value is dependent on the following parameters:

- Input clock  $f_{PCLK}$

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP

(to be considered only if fractional divider is enabled and operating in fractional divider mode)

- 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

Data Sheet 89 V1.5, 2011-03

The following formulas calculate the final baud rate without and with the fractional divider respectively:

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR\_VALUE + 1)}$$

where  $2^{BRPRE} \times (BR\_VALUE + 1) > 1$

baud rate =

$$\frac{f_{PCLK}}{16 \times 2^{BRPRE} \times (BR\_VALUE + 1)} \times \frac{STEP}{256}$$

(3.5)

The maximum baud rate that can be generated is limited to  $f_{\rm PCLK}/32$ . Hence, for a module clock of 24 MHz, the maximum achievable baud rate is 0.75 MBaud.

Standard LIN protocol can support a maximum baud rate of 20 kHz, the baud rate accuracy is not critical and the fractional divider can be disabled. Only the prescaler is used for auto baud rate calculation. For LIN fast mode, which supports the baud rate of 20 kHz to 57.6 kHz, the higher baud rates require the use of the fractional divider for greater accuracy.

**Table 31** lists the various commonly used baud rates with their corresponding parameter settings and deviation errors. The fractional divider is disabled and a module clock of 24 MHz is used.

Table 31 Typical Baud rates for UART with Fractional Divider disabled

| Baud rate  | Prescaling Factor (2BRPRE)  | Reload Value<br>(BR_VALUE + 1) | Deviation Error |

|------------|-----------------------------|--------------------------------|-----------------|

| 19.2 kBaud | 1 (BRPRE=000 <sub>B</sub> ) | 78 (4E <sub>H</sub> )          | 0.17 %          |

| 9600 Baud  | 1 (BRPRE=000 <sub>B</sub> ) | 156 (9C <sub>H</sub> )         | 0.17 %          |

| 4800 Baud  | 2 (BRPRE=001 <sub>B</sub> ) | 156 (9C <sub>H</sub> )         | 0.17 %          |

| 2400 Baud  | 4 (BRPRE=010 <sub>B</sub> ) | 156 (9C <sub>H</sub> )         | 0.17 %          |

The fractional divider allows baud rates of higher accuracy (lower deviation error) to be generated. **Table 32** lists the resulting deviation errors from generating a baud rate of 57.6 kHz, using different module clock frequencies. The fractional divider is enabled (fractional divider mode) and the corresponding parameter settings are shown.

Data Sheet 90 V1.5, 2011-03

needed for the handshaking between the master and slave tasks is provided by the master task through the header portion of the frame.

The header consists of a break and synch pattern followed by an identifier. Among these three fields, only the break pattern cannot be transmitted as a normal 8-bit UART data. The break must contain a dominant value of 13 bits or more to ensure proper synchronization of slave nodes.

In the LIN communication, a slave task is required to be synchronized at the beginning of the protected identifier field of frame. For this purpose, every frame starts with a sequence consisting of a break field followed by a synch byte field. This sequence is unique and provides enough information for any slave task to detect the beginning of a new frame and be synchronized at the start of the identifier field.

Upon entering LIN communication, a connection is established and the transfer speed (baud rate) of the serial communication partner (host) is automatically synchronized in the following steps:

STEP 1: Initialize interface for reception and timer for baud rate measurement

STEP 2: Wait for an incoming LIN frame from host

STEP 3: Synchronize the baud rate to the host

STEP 4: Enter for Master Request Frame or for Slave Response Frame

Note: Re-synchronization and setup of baud rate are always done for **every** Master Request Header or Slave Response Header LIN frame.

Data Sheet 93 V1.5, 2011-03

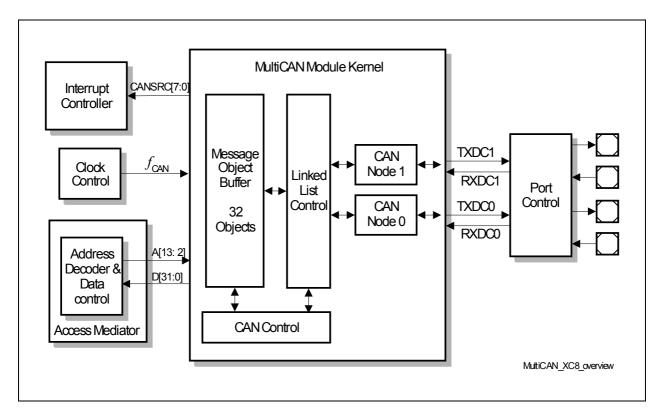

### 3.21 Controller Area Network (MultiCAN)

The MultiCAN module contains two Full-CAN nodes operating independently or exchanging data and remote frames via a gateway function. Transmission and reception of CAN frames is handled in accordance to CAN specification V2.0 B active. Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

Both CAN nodes share a common set of message objects, where each message object may be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects may be combined to build gateways between the CAN nodes or to setup a FIFO buffer.

The message objects are organized in double chained lists, where each CAN node has it's own list of message objects. A CAN node stores frames only into message objects that are allocated to the list of the CAN node. It only transmits messages from objects of this list. A powerful, command driven list controller performs all list operations.

The bit timings for the CAN nodes are derived from the peripheral clock ( $f_{\text{CAN}}$ ) and are programmable up to a data rate of 1 MBaud. A pair of receive and transmit pins connects each CAN node to a bus transceiver.

Figure 30 Overview of the MultiCAN

#### **Features**

Compliant to ISO 11898.

#### **Electrical Parameters**

### 4 Electrical Parameters

**Chapter 4** provides the characteristics of the electrical parameters which are implementation-specific for the XC87x.

#### 4.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 4.2** and **Section 4.3**.

### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XC87x and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

### · cc

These parameters indicate Controller Characteristics, which are distinctive features of the XC87x and must be regarded for a system design.

#### SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the XC87x is designed in.

Data Sheet 108 V1.5, 2011-03

#### **Electrical Parameters**

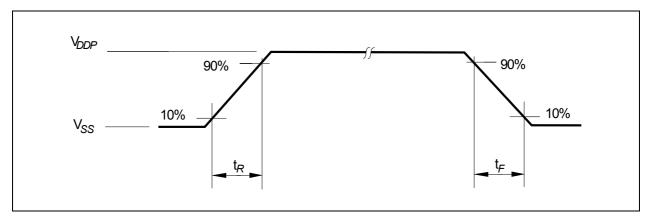

## 4.3.2 Output Rise/Fall Times

Table 47 provides the characteristics of the output rise/fall times in the XC87x.

Table 47 Output Rise/Fall Times Parameters (Operating Conditions apply)

| •                          |                                 |                 |      | ` • | •                         | ,    |                 |  |

|----------------------------|---------------------------------|-----------------|------|-----|---------------------------|------|-----------------|--|

| Parameter                  | Symbol                          | Limit<br>Values |      |     |                           | Unit | Test Conditions |  |

|                            |                                 | min.            | max. |     |                           |      |                 |  |

| $V_{\rm DDP}$ = 5V Range   |                                 | •               |      | •   |                           |      |                 |  |

| Rise/fall times            | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns  | 20 pF. <sup>1) 2)3)</sup> |      |                 |  |

| $V_{\rm DDP}$ = 3.3V Range |                                 |                 |      |     |                           |      |                 |  |

| Rise/fall times            | t <sub>R</sub> , t <sub>F</sub> | _               | 10   | ns  | 20 pF. <sup>1) 2)4)</sup> |      |                 |  |

- 1) Rise/Fall time measurements are taken with 10% 90% of pad supply.

- 2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

- 3) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF 100pF @ 0.125 ns/pF.

- 4) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF 100pF @ 0.225 ns/pF.

Figure 39 Rise/Fall Times Parameters

#### **Electrical Parameters**

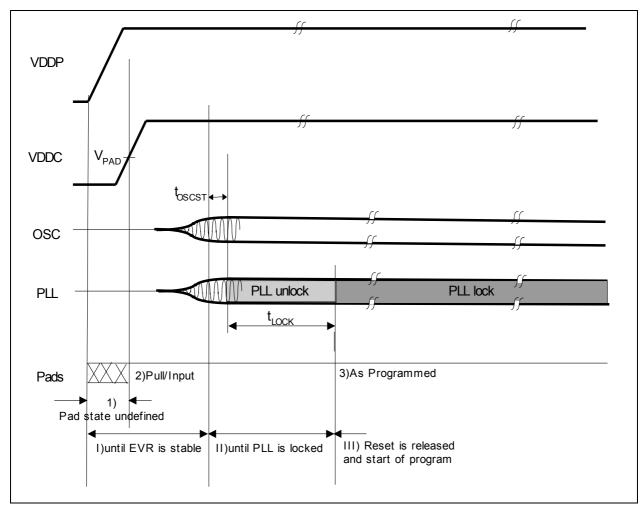

### 4.3.3 Power-on Reset and PLL Timing

Table 48 provides the characteristics of the power-on reset and PLL timing in the XC87x.

Table 48 Power-On Reset and PLL Timing (Operating Conditions apply)

| Parameter                        | Symbol      | nbol Limit Values |      |      | Unit | <b>Test Conditions</b> |      |

|----------------------------------|-------------|-------------------|------|------|------|------------------------|------|

|                                  |             |                   | min. | typ. | max. |                        |      |

| On-Chip Oscillator start-up time | $t_{OSCST}$ | CC                | _    | -    | 500  | ns                     | 1)   |

| PLL lock-in in time              | $t_{LOCK}$  | CC                | _    | _    | 200  | μS                     | 1)   |

| PLL accumulated jitter           | $D_{P}$     |                   | _    | _    | 1.8  | ns                     | 1)2) |

- 1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

- 2) PLL lock at 144 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 72 and P = 1.

Figure 40 Power-on Reset Timing

Data Sheet 124 V1.5, 2011-03

### **Package and Quality Declaration**

# 5 Package and Quality Declaration

**Chapter 5** provides the information of the XC87x package and reliability section.

## 5.1 Package Parameters

**Table 56** provides the thermal characteristics of the package used in XC878 and XC874.

Table 56 Thermal Characteristics of the Packages

| Parameter                                      | Symbol    |    | Limit Values |      | Unit | Notes |

|------------------------------------------------|-----------|----|--------------|------|------|-------|

|                                                |           |    | Min.         | Max. |      |       |

| PG-LQFP-64-4 (XC878)                           |           |    |              | 1    | 1    | - 1   |

| Thermal resistance junction case <sup>1)</sup> | $R_{TJC}$ | CC | -            | 13.8 | K/W  | -     |

| Thermal resistance junction lead <sup>1)</sup> | $R_{TJL}$ | CC | -            | 34.6 | K/W  | -     |

| PG-VQFN-48-22 (XC874)                          |           |    |              |      |      |       |

| Thermal resistance junction case <sup>1)</sup> | $R_{TJC}$ | CC | -            | 16.6 | K/W  | -     |

| Thermal resistance junction lead <sup>1)</sup> | $R_{TJL}$ | CC | -            | 30.7 | K/W  | -     |

<sup>1)</sup> The thermal resistances between the case and the ambient  $(R_{\mathsf{TCA}})$ , the lead and the ambient  $(R_{\mathsf{TLA}})$  are to be combined with the thermal resistances between the junction and the case  $(R_{\mathsf{TJC}})$ , the junction and the lead  $(R_{\mathsf{TJL}})$  given above, in order to calculate the total thermal resistance between the junction and the ambient  $(R_{\mathsf{TJA}})$ . The thermal resistances between the case and the ambient  $(R_{\mathsf{TCA}})$ , the lead and the ambient  $(R_{\mathsf{TLA}})$  depend on the external system (PCB, case) characteristics, and are under user responsibility.

- a) simply adding only the two thermal resistances (junction lead and lead ambient), or

- b) by taking all four resistances into account, depending on the precision needed.

Data Sheet 133 V1.5, 2011-03

The junction temperature can be calculated using the following equation:  $T_J = T_A + R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient. This total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by