Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

|                            |                                                                                   |

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 27MHz                                                                             |

| Connectivity               | LINbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 40                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 3.25K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 48-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | PG-VQFN-48-22                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc874lm16fva5vackxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

8-Bit

# XC87xCLM

8-Bit Single-Chip Microcontroller

Data Sheet V1.5 2011-03

Microcontrollers

#### XC87x Data Sheet

Revision History: V1.5 2011-03

Previous Versions: V1.4

Subjects (major changes since last revision) Page

Changes from V1.4 2010-08 to V1.5 2011-03

A new variant, SAF-XC874CM-13FVA 5V, has been added in Table 2. Page 3

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

**Data Sheet** V1.5, 2011-03

Table 4 Flash Protection Modes (cont'd)

| Flash<br>Protection                      | Without hardware protection             | With hardware protect                                                                                                                         | tion                                                                |

|------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| P-Flash<br>program<br>and erase          | Possible                                | Possible only on the condition that MSB - 1 of password is set to 1                                                                           | Possible only on the condition that MSB - 1 of password is set to 1 |

| D-Flash<br>contents<br>can be read<br>by | Read instructions in any program memory | Read instructions in any program memory                                                                                                       | Read instructions in<br>the P-Flash or D-<br>Flash                  |

| External access to D-Flash               | Not possible                            | Not possible                                                                                                                                  | Not possible                                                        |

| D-Flash<br>program                       | Possible                                | Possible                                                                                                                                      | Possible, on the condition that MSB - 1 of password is set to 1     |

| D-Flash<br>erase                         | Possible                                | Possible, on these conditions:  • MISC_CON.DFLASH EN bit is set to 1 prior to each erase operation; or  • the MSB - 1 of password is set to 1 | Possible, on the condition that MSB - 1 of password is set to 1     |

BSL mode 6, which is used for enabling Flash protection, can also be used for disabling Flash protection. Here, the programmed password must be provided by the user. To disable the flash protection, a password match is required. A password match triggers an automatic erase of the protected P-Flash and D-Flash contents, including the programmed password. With a valid password, the Flash hardware protection is then enabled or disabled upon next reset. For the other protection strategies, no reset is necessary.

Although no protection scheme can be considered infallible, the XC87x memory protection strategy provides a very high level of protection for a general purpose microcontroller.

Note: If ROM read-out protection is enabled, only read instructions in the ROM memory can target the ROM contents.

Data Sheet 25 V1.5, 2011-03

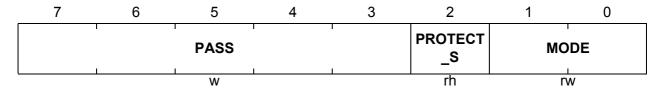

# 3.2.3.1 Password Register

### **PASSWD**

Password Register Reset Value: 07<sub>H</sub>

| Field     | Bits     | Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE      | [1:0] rw |      | Bit Protection Scheme Control Bits  O Scheme disabled - direct access to the protected bits is allowed.  11 Scheme enabled - the bit field PASS has to be written with the passwords to open and close the access to protected bits. (default)  Others:Scheme Enabled.  These two bits cannot be written directly. To change the value between 11 <sub>B</sub> and 00 <sub>B</sub> , the bit field PASS must be written with 11000 <sub>B</sub> ; only then, will the MODE[1:0] be registered. |

| PROTECT_S | 2        | rh   | Bit Protection Signal Status Bit This bit shows the status of the protection.  O Software is able to write to all protected bits.  Software is unable to write to any protected bits.                                                                                                                                                                                                                                                                                                          |

| PASS      | [7:3]    | W    | Password Bits The Bit Protection Scheme only recognizes three patterns.  11000 <sub>B</sub> Enables writing of the bit field MODE.  10011 <sub>B</sub> Opens access to writing of all protected bits.  10101 <sub>B</sub> Closes access to writing of all protected bits                                                                                                                                                                                                                       |

### 3.2.4 XC87x Register Overview

The SFRs of the XC87x are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.15**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

# 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

Table 5 CPU Register Overview

| Addr            | Register Name                                           | Bit       | 7                           | 6    | 5    | 4    | 3         | 2     | 1    | 0    |

|-----------------|---------------------------------------------------------|-----------|-----------------------------|------|------|------|-----------|-------|------|------|

| RMAP =          | 0 or 1                                                  | 1         | ı                           | I.   | I.   | I.   | I.        | Į.    | Į.   |      |

| 81 <sub>H</sub> | SP Reset: 07 <sub>H</sub>                               | Bit Field |                             |      |      | S    | Р         |       |      |      |

|                 | Stack Pointer Register                                  | Туре      |                             |      |      | r    | w         |       |      |      |

| 82 <sub>H</sub> | DPL Reset: 00 <sub>H</sub>                              | Bit Field | DPL7                        | DPL6 | DPL5 | DPL4 | DPL3      | DPL2  | DPL1 | DPL0 |

|                 | Data Pointer Register Low                               | Туре      | rw                          | rw   | rw   | rw   | rw        | rw    | rw   | rw   |

| 83 <sub>H</sub> | DPH Reset: 00 <sub>H</sub>                              | Bit Field | DPH7                        | DPH6 | DPH5 | DPH4 | DPH3      | DPH2  | DPH1 | DPH0 |

|                 | Data Pointer Register High                              | Туре      | rw                          | rw   | rw   | rw   | rw        | rw    | rw   | rw   |

| 87 <sub>H</sub> | PCON Reset: 00 <sub>H</sub>                             | Bit Field | SMOD                        |      | 0    |      | GF1       | GF0   | 0    | IDLE |

|                 | Power Control Register                                  | Туре      | rw                          |      | r    |      | rw        | rw    | r    | rw   |

| 88 <sub>H</sub> | TCON Reset: 00 <sub>H</sub>                             | Bit Field | TF1                         | TR1  | TF0  | TR0  | IE1       | IT1   | IE0  | IT0  |

|                 | Timer Control Register                                  | Туре      | rwh                         | rw   | rwh  | rw   | rwh       | rw    | rwh  | rw   |

| 89 <sub>H</sub> | TMOD Reset: 00 <sub>H</sub><br>Timer Mode Register      | Bit Field | GATE<br>1                   | T1S  | T1   | IM   | GATE<br>0 | T0S   | TO   | OM   |

|                 |                                                         | Туре      | rw                          | rw   | r    | W    | rw        | rw rv |      | w    |

| 8A <sub>H</sub> | TL0 Reset: 00 <sub>H</sub>                              | Bit Field |                             |      |      | V    | ٩L        |       |      |      |

|                 | Timer 0 Register Low                                    | Туре      |                             |      |      | rv   | vh        |       |      |      |

| 8B <sub>H</sub> | TL1 Reset: 00 <sub>H</sub>                              | Bit Field |                             |      |      | V    | ٩L        |       |      |      |

|                 | Timer 1 Register Low                                    | Туре      |                             |      |      | rv   | vh        |       |      |      |

| 8C <sub>H</sub> | THO Reset: 00 <sub>H</sub>                              | Bit Field |                             |      |      | V    | ٩L        |       |      |      |

|                 | Timer 0 Register High                                   | Туре      |                             |      |      | rv   | vh        |       |      |      |

| 8D <sub>H</sub> | TH1 Reset: 00 <sub>H</sub>                              | Bit Field |                             |      |      | V    | ٩L        |       |      |      |

|                 | Timer 1 Register High                                   | Туре      |                             |      |      | rv   | vh        |       |      |      |

| 94 <sub>H</sub> | MEX1 Reset: 00 <sub>H</sub>                             | Bit Field |                             | С    | В    |      |           | N     | IB   |      |

|                 | Memory Extension Register 1                             | Туре      |                             |      | r    |      |           | r     | W    |      |

| 95 <sub>H</sub> | MEX2 Reset: 00 <sub>H</sub>                             | Bit Field | ield MCM MCB IB             |      |      |      |           |       |      |      |

|                 | Memory Extension Register 2                             | Туре      | rw                          |      | rw   |      | rw        |       |      |      |

| 96 <sub>H</sub> | MEX3 Reset: 00 <sub>H</sub> Memory Extension Register 3 | Bit Field | Field MCB1 0 MXB1 MXM MXB 9 |      |      |      |           |       |      |      |

|                 |                                                         | Туре      | rw                          |      | r    | rw   | rw        |       | rw   |      |

Table 5 CPU Register Overview (cont'd)

| Addr            | Register Name                                                  | Bit       | 7           | 6           | 5           | 4           | 3    | 2    | 1         | 0          |  |

|-----------------|----------------------------------------------------------------|-----------|-------------|-------------|-------------|-------------|------|------|-----------|------------|--|

| 97 <sub>H</sub> | MEXSP Reset: 7FH                                               | Bit Field | 0           |             |             | •           | MXSP | •    |           |            |  |

|                 | Memory Extension Stack<br>Pointer Register                     | Туре      | ŗ           | r rwh       |             |             |      |      |           |            |  |

| 98 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                                    | Bit Field | SM0         | SM1         | SM2         | REN         | TB8  | RB8  | TI        | RI         |  |

|                 | Serial Channel Control Register                                | Туре      | rw          | rw          | rw          | rw          | rw   | rwh  | rwh       | rwh        |  |

| 99 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                                    | Bit Field |             |             |             | V           | AL   |      |           |            |  |

|                 | Serial Data Buffer Register                                    | Туре      |             |             |             | rv          | vh   | h    |           |            |  |

| A2 <sub>H</sub> | EO Reset: 00 <sub>H</sub> Extended Operation Register          | Bit Field |             | 0           |             | TRAP_<br>EN |      | 0    |           | DPSE<br>L0 |  |

|                 |                                                                | Туре      |             | r           |             | rw          |      | r    |           | rw         |  |

| A8 <sub>H</sub> | IEN0 Reset: 00 <sub>H</sub>                                    | Bit Field | EA          | 0           | ET2         | ES          | ET1  | EX1  | ET0       | EX0        |  |

|                 | Interrupt Enable Register 0                                    | Туре      | rw          | r           | rw          | rw          | rw   | rw   | rw        | rw         |  |

| B8 <sub>H</sub> | IP Reset: 00 <sub>H</sub>                                      | Bit Field | (           | )           | PT2         | PS          | PT1  | PX1  | PT0       | PX0        |  |

|                 | Interrupt Priority Register                                    | Туре      | 1           | ſ           | rw          | rw          | rw   | rw   | rw        | rw         |  |

| в9 <sub>Н</sub> | IPH Reset: 00 <sub>H</sub>                                     | Bit Field | d 0         |             | PT2H        | PSH         | PT1H | PX1H | PT0H      | PX0H       |  |

|                 | Interrupt Priority High Register                               | Туре      | l           | ſ           | rw          | rw          | rw   | rw   | rw        | rw         |  |

| D0 <sub>H</sub> | PSW Reset: 00 <sub>H</sub>                                     | Bit Field | CY          | AC          | F0          | RS1         | RS0  | OV   | F1        | Р          |  |

|                 | Program Status Word Register                                   | Туре      | rwh         | rwh         | rw          | rw          | rw   | rwh  | rw        | rh         |  |

| E0 <sub>H</sub> | ACC Reset: 00 <sub>H</sub>                                     | Bit Field | ACC7        | ACC6        | ACC5        | ACC4        | ACC3 | ACC2 | ACC1      | ACC0       |  |

|                 | Accumulator Register                                           | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw         |  |

| E8 <sub>H</sub> | IEN1 Reset: 00 <sub>H</sub> Interrupt Enable Register 1        | Bit Field | ECCIP<br>3  | ECCIP<br>2  | ECCIP<br>1  | ECCIP<br>0  | EXM  | EX2  | ESSC      | EADC       |  |

|                 |                                                                | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw         |  |

| F0 <sub>H</sub> | B Reset: 00 <sub>H</sub>                                       | Bit Field | B7          | B6          | B5          | B4          | В3   | B2   | B1        | В0         |  |

|                 | B Register                                                     | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw         |  |

| F8 <sub>H</sub> | IP1 Reset: 00 <sub>H</sub> Interrupt Priority 1 Register       | Bit Field | PCCIP<br>3  | PCCIP<br>2  | PCCIP<br>1  | PCCIP<br>0  | PXM  | PX2  | PSSC      | PADC       |  |

|                 |                                                                | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw         |  |

| F9 <sub>H</sub> | IPH1 Reset: 00 <sub>H</sub> Interrupt Priority 1 High Register | Bit Field | PCCIP<br>3H | PCCIP<br>2H | PCCIP<br>1H | PCCIP<br>0H | PXMH | PX2H | PSSC<br>H | PADC<br>H  |  |

|                 |                                                                | Туре      | rw          | rw          | rw          | rw          | rw   | rw   | rw        | rw         |  |

# 3.2.4.2 MDU Registers

The MDU SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 6 MDU Register Overview

| Addr            | Register Name                  | Bit       | 7 | 6 | 5 | 4 | 3 | 2   | 1    | 0    |

|-----------------|--------------------------------|-----------|---|---|---|---|---|-----|------|------|

| RMAP =          | 1                              |           |   |   |   |   |   |     |      |      |

| во <sub>Н</sub> | MDUSTAT Reset: 00 <sub>H</sub> | Bit Field |   |   | 0 |   |   | BSY | IERR | IRDY |

|                 | MDU Status Register            | Туре      |   |   | r |   |   | rh  | rwh  | rwh  |

Table 10

Port Register Overview (cont'd)

| Addr            | Register Name                                                   | Bit       | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------|-----------------------------------------------------------------|-----------|-----|-----|-----|-----|-----|-----|-----|-----|

| во <sub>Н</sub> | P3_DATA Reset: 00 <sub>H</sub>                                  | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P3 Data Register                                                | Туре      | rwh |

| B1 <sub>H</sub> | P3_DIR Reset: 00 <sub>H</sub>                                   | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P3 Direction Register                                           | Туре      | rw  |

| C8 <sub>H</sub> | P4_DATA Reset: 00 <sub>H</sub>                                  | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P4 Data Register                                                | Туре      | rwh |

| C9H             | P4_DIR Reset: 00 <sub>H</sub>                                   | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P4 Direction Register                                           | Туре      | rw  |

| RMAP =          | = 0, PAGE 1                                                     |           |     | _   |     | _   |     |     |     |     |

| 80 <sub>H</sub> | P0_PUDSEL Reset: FF <sub>H</sub><br>P0 Pull-Up/Pull-Down Select | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | Register                                                        | Туре      | rw  |

| 86 <sub>H</sub> | P0_PUDEN Reset: C4 <sub>H</sub>                                 | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P0 Pull-Up/Pull-Down Enable Register                            | Туре      | rw  |

| 90 <sub>H</sub> | P1_PUDSEL Reset: FF <sub>H</sub>                                | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P1 Pull-Up/Pull-Down Select Register                            | Туре      | rw  |

| 91 <sub>H</sub> | P1_PUDEN Reset: FF <sub>H</sub>                                 | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P1 Pull-Up/Pull-Down Enable Register                            | Туре      | rw  |

| 92 <sub>H</sub> | P5_PUDSEL Reset: FF <sub>H</sub>                                | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P5 Pull-Up/Pull-Down Select Register                            | Туре      | rw  |

| 93 <sub>H</sub> | P5_PUDEN Reset: FF <sub>H</sub>                                 | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P5 Pull-Up/Pull-Down Enable Register                            | Туре      | rw  |

| B0 <sub>H</sub> | P3_PUDSEL Reset: BF <sub>H</sub>                                | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P3 Pull-Up/Pull-Down Select Register                            | Туре      | rw  |

| B1 <sub>H</sub> | P3_PUDEN Reset: 40 <sub>H</sub>                                 | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P3 Pull-Up/Pull-Down Enable Register                            | Туре      | rw  |

| C8H             | P4_PUDSEL Reset: FF <sub>H</sub>                                | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P4 Pull-Up/Pull-Down Select Register                            | Туре      | rw  |

| C9 <sub>H</sub> | P4_PUDEN Reset: 04 <sub>H</sub>                                 | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P4 Pull-Up/Pull-Down Enable Register                            | Туре      | rw  |

| RMAP =          | = 0, PAGE 2                                                     |           |     |     |     |     |     |     |     |     |

| 80 <sub>H</sub> | P0_ALTSEL0 Reset: 00 <sub>H</sub>                               | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| "               | P0 Alternate Select 0 Register                                  | Туре      | rw  |

| 86 <sub>H</sub> | P0_ALTSEL1 Reset: 00 <sub>H</sub>                               | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|                 | P0 Alternate Select 1 Register                                  | Туре      | rw  |

| 90 <sub>H</sub> | P1_ALTSEL0 Reset: 00H                                           | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

| 1               | P1 Alternate Select 0 Register                                  | Туре      | rw  |

# Table 14 CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                        | Bit       | 7          | 6            | 5                  | 4          | 3            | 2          | 1            | 0          |

|-----------------|----------------------------------------------------------------------|-----------|------------|--------------|--------------------|------------|--------------|------------|--------------|------------|

| FD <sub>H</sub> | CCU6_MODCTRH Reset: 00 <sub>H</sub> Modulation Control Register High | Bit Field | ECT1<br>3O | 0            |                    |            | T13M         | ODEN       |              |            |

|                 |                                                                      | Туре      | rw         | r            |                    |            | r            | W          |              |            |

| FE <sub>H</sub> | CCU6_TRPCTRL Reset: 00 <sub>H</sub> Trap Control Register Low        | Bit Field |            |              | 0 TRPM TRPI<br>2 1 |            |              |            |              | TRPM<br>0  |

|                 |                                                                      | Туре      |            |              | r                  |            |              | rw         | rw           | rw         |

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub> Trap Control Register High       | Bit Field | TRPP<br>EN | TRPE<br>N13  |                    |            | TRI          | PEN        |              |            |

|                 |                                                                      | Туре      | rw         | rw           |                    |            | r            | W          |              |            |

| RMAP =          | = 0, PAGE 3                                                          |           |            |              |                    |            |              |            |              |            |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00H                                              | Bit Field | 0          | R            |                    |            | MC           | MP         |              |            |

|                 | Multi-Channel Mode Output Register Low                               | Туре      | r          | rh           |                    |            | r            | h          |              |            |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00H                                              | Bit Field | (          | )            |                    | CURH       |              |            | EXPH         |            |

|                 | Multi-Channel Mode Output Register<br>High                           | Туре      |            | r            |                    | rh         |              |            | rh           |            |

| 9CH             | CCU6_ISL Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status     | Bit Field | T12<br>PM  | T12<br>OM    | ICC62<br>F         | ICC62<br>R | ICC61<br>F   | ICC61<br>R | ICC60<br>F   | ICC60<br>R |

|                 | Register Low                                                         | Туре      | rh         | rh           | rh                 | rh         | rh           | rh         | rh           | rh         |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub> Capture/Compare Interrupt Status     | Bit Field | STR        | IDLE         | WHE                | CHE        | TRPS         | TRPF       | T13<br>PM    | T13<br>CM  |

|                 | Register High                                                        | Туре      | rh         | rh           | rh                 | rh         | rh           | rh         | rh           | rh         |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00H                                              | Bit Field | IST        | RP           | ISC                | C62        | ISC          | C61        | ISCC60       |            |

|                 | Port Input Select Register 0 Low                                     | Туре      | r          | W            | r                  | W          | r            | W          | r            | W          |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00H                                              | Bit Field | IST1       | 2HR          | ISP                | OS2        | ISP          | OS1        | ISPOS0       |            |

|                 | Port Input Select Register 0 High                                    | Туре      | r          | rw rw        |                    | rw rw      |              | r          | w            |            |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00H                                               | Bit Field |            |              |                    | )          |              |            | IST1         | 3HR        |

|                 | Port Input Select Register 2                                         | Туре      |            |              |                    | r          |              |            | r            | W          |

| FA <sub>H</sub> | CCU6_T12L Reset: 00H                                                 | Bit Field |            |              |                    | T12        | CVL          |            |              |            |

|                 | Timer T12 Counter Register Low                                       | Туре      |            |              |                    | rv         | vh           |            |              |            |

| FB <sub>H</sub> | CCU6_T12H Reset: 00H                                                 | Bit Field |            |              |                    | T12        | CVH          |            |              |            |

|                 | Timer T12 Counter Register High                                      | Туре      |            |              |                    | rv         | vh           |            |              |            |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub> Timer T13 Counter Register Low      | Bit Field |            |              |                    | T13        | CVL          |            |              |            |

|                 | Timer 113 Counter Register Low                                       | Туре      |            |              |                    | rv         | vh           |            |              |            |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub> Timer T13 Counter Register High     | Bit Field | ld T13CVH  |              |                    |            |              |            |              |            |

|                 | Timer 113 Counter Register High                                      | Туре      |            |              | rwh                |            |              |            |              |            |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub> Compare State Register Low      | Bit Field | 0          | CC63<br>ST   | CC<br>POS2         | CC<br>POS1 | CC<br>POS0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                      | Туре      | r          | rh           | rh                 | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High  | Bit Field | T13IM      | COUT<br>63PS | COUT<br>62PS       | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                      | Туре      | rwh        | rwh          | rwh                | rwh        | rwh          | rwh        | rwh          | rwh        |

# 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 15 UART1 Register Overview

| Addr            | Register Name                                                   | Bit       | 7   | 6        | 5   | 4   | 3    | 2          | 1    | 0    |

|-----------------|-----------------------------------------------------------------|-----------|-----|----------|-----|-----|------|------------|------|------|

| RMAP =          | = 1                                                             |           |     | JI.      | I.  | ı   | l.   | I.         |      | l .  |

| C8H             | SCON Reset: 00 <sub>H</sub>                                     | Bit Field | SM0 | SM1      | SM2 | REN | TB8  | RB8        | TI   | RI   |

|                 | Serial Channel Control Register                                 | Туре      | rw  | rw       | rw  | rw  | rw   | rwh        | rwh  | rwh  |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                                     | Bit Field |     |          |     | V   | AL   |            |      |      |

|                 | Serial Data Buffer Register                                     | Туре      |     |          |     | rv  | vh   |            |      |      |

| CA <sub>H</sub> | BCON Reset: 00 <sub>H</sub>                                     | Bit Field |     | (        | )   |     |      | BRPRE      |      | R    |

|                 | Baud Rate Control Register                                      | Туре      |     | r rw     |     |     |      |            |      | rw   |

| СВН             | BG Reset: 00 <sub>H</sub>                                       | Bit Field |     | BR_VALUE |     |     |      |            |      |      |

|                 | Baud Rate Timer/Reload Register                                 | Туре      |     |          |     | rv  | vh   |            |      |      |

| ССН             | FDCON Reset: 00 <sub>H</sub>                                    | Bit Field |     |          | 0   |     |      | NDOV       | FDM  | FDEN |

|                 | Fractional Divider Control Register                             | Туре      |     |          | r   |     |      | rwh        | rw   | rw   |

| CDH             | FDSTEP Reset: 00 <sub>H</sub>                                   | Bit Field |     |          |     | ST  | EP   |            |      |      |

|                 | Fractional Divider Reload Register                              | Туре      |     |          |     | r   | W    |            |      |      |

| CEH             | FDRES Reset: 00 <sub>H</sub>                                    | Bit Field |     |          |     | RES | SULT |            |      |      |

|                 | Fractional Divider Result Register                              | Туре      | rh  |          |     |     |      |            |      |      |

| CF <sub>H</sub> | SCON1 Reset: 07 <sub>H</sub><br>Serial Channel Control Register | Bit Field |     |          | 0   |     |      | NDOV<br>EN | TIEN | RIEN |

|                 | 1                                                               | Туре      |     |          | r   |     |      | rw         | rw   | rw   |

# 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

Table 16 SSC Register Overview

| Addr            | Register Name                            | Bit       | 7  | 6  | 5  | 4    | 3   | 2        | 1   | 0   |  |

|-----------------|------------------------------------------|-----------|----|----|----|------|-----|----------|-----|-----|--|

| RMAP =          | = 0                                      |           |    | •  |    |      |     |          |     |     |  |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00H                     | Bit Field |    |    | 0  |      |     | CIS      | SIS | MIS |  |

|                 | Port Input Select Register               | Туре      |    |    | r  |      |     | rw       | rw  | rw  |  |

| $AA_H$          | SSC_CONL Reset: 00H                      | Bit Field | LB | РО | PH | НВ   |     | BM<br>rw |     |     |  |

|                 | Control Register Low<br>Programming Mode | Туре      | rw | rw | rw | rw   |     |          |     |     |  |

| AA <sub>H</sub> | SSC_CONL Reset: 00H                      | Bit Field |    | (  | )  |      |     | В        | C   |     |  |

|                 | Control Register Low<br>Operating Mode   | Туре      |    |    | r  |      |     | rh       |     |     |  |

| AB <sub>H</sub> | SSC_CONH Reset: 00H                      | Bit Field | EN | MS | 0  | AREN | BEN | PEN      | REN | TEN |  |

|                 | Control Register High Programming Mode   | Туре      | rw | rw | r  | rw   | rw  | rw       | rw  | rw  |  |

Table 16

SSC Register Overview (cont'd)

| Addr                                    | Register Name                           | Bit       | 7           | 6        | 5 | 4    | 3    | 2   | 1   | 0   |

|-----------------------------------------|-----------------------------------------|-----------|-------------|----------|---|------|------|-----|-----|-----|

| AB <sub>H</sub>                         | SSC_CONH Reset: 00H                     | Bit Field | EN          | MS       | 0 | BSY  | BE   | PE  | RE  | TE  |

|                                         | Control Register High<br>Operating Mode | Туре      | rw          | rw       | r | rh   | rwh  | rwh | rwh | rwh |

| AC <sub>H</sub>                         | SSC_TBL Reset: 00H                      | Bit Field | TB_VALUE    |          |   |      |      |     |     |     |

|                                         | Transmitter Buffer Register Lov         | Туре      | rw          |          |   |      |      |     |     |     |

| $AD_H$                                  | SSC_RBL Reset: 00H                      | Bit Field |             | RB_VALUE |   |      |      |     |     |     |

|                                         | Receiver Buffer Register Low            | Туре      |             |          |   | rh   |      |     |     |     |

| AE <sub>H</sub>                         | SSC_BRL Reset: 00H                      | Bit Field |             |          |   | BR_V | ALUE |     |     |     |

|                                         | Baud Rate Timer Reload<br>Register Low  | Туре      | rw          |          |   |      |      |     |     |     |

| AF <sub>H</sub>                         | SSC_BRH Reset: 00H                      | Bit Field | ld BR_VALUE |          |   |      |      |     |     |     |

| Baud Rate Timer Reload<br>Register High |                                         | Туре      |             |          | • | r    | W    | •   |     | •   |

# 3.2.4.13 MultiCAN Registers

The MultiCAN SFRs can be accessed in the standard memory area (RMAP = 0).

Table 17 CAN Register Overview

| Addr            | Register Name                        | Bit       | 7            | 6   | 5   | 4   | 3    | 2    | 1    | 0    |

|-----------------|--------------------------------------|-----------|--------------|-----|-----|-----|------|------|------|------|

| RMAP =          | = 0                                  |           |              | •   | •   | •   |      |      |      |      |

| D8 <sub>H</sub> | ADCON Reset: 00 <sub>H</sub>         | Bit Field | V3           | V2  | V1  | V0  | AUAD |      | BSY  | RWEN |

|                 | CAN Address/Data Control<br>Register | Туре      | rw           | rw  | rw  | rw  | rw   |      | rh   | rw   |

| D9 <sub>H</sub> | ADL Reset: 00 <sub>H</sub>           | Bit Field | CA9          | CA8 | CA7 | CA6 | CA5  | CA4  | CA3  | CA2  |

|                 | CAN Address Register Low             | Туре      | rwh          | rwh | rwh | rwh | rwh  | rwh  | rwh  | rwh  |

| DA <sub>H</sub> | ADH Reset: 00 <sub>H</sub>           | Bit Field |              | (   | )   |     | CA13 | CA12 | CA11 | CA10 |

|                 | CAN Address Register High            | Туре      |              |     | r   |     | rwh  | rwh  | rwh  | rwh  |

| DBH             | DATA0 Reset: 00 <sub>H</sub>         | Bit Field |              |     |     | С   | D    |      |      |      |

|                 | CAN Data Register 0                  | Туре      |              |     |     | rv  | vh   |      |      |      |

| DCH             | DATA1 Reset: 00 <sub>H</sub>         | Bit Field |              |     |     | C   | D    |      |      |      |

|                 | CAN Data Register 1                  | Туре      |              |     |     | rv  | vh   |      |      |      |

| DDH             | DATA2 Reset: 00 <sub>H</sub>         | Bit Field |              |     |     | С   | D    |      |      |      |

|                 | CAN Data Register 2                  | Туре      | rwh          |     |     |     |      |      |      |      |

| DEH             | DATA3 Reset: 00 <sub>H</sub>         | Bit Field | Sit Field CD |     |     |     |      |      |      |      |

|                 | CAN Data Register 3                  | Туре      | rwh          |     |     |     |      |      |      |      |

# 3.2.4.14 OCDS Registers

The OCDS SFRs can be accessed in the mapped memory area (RMAP = 1).

# 3.2.4.15 Flash Registers

The Flash SFRs can be accessed in the mapped memory area (RMAP = 1).

Table 19 Flash Register Overview

| Addr                                                        | Register Name                                            | Bit       | 7        | 6         | 5    | 4 | 3          | 2           | 1         | 0         |

|-------------------------------------------------------------|----------------------------------------------------------|-----------|----------|-----------|------|---|------------|-------------|-----------|-----------|

| RMAP =                                                      | RMAP = 1                                                 |           |          |           |      |   |            |             |           |           |

| D1 <sub>H</sub>                                             | FCON Reset: 10 <sub>H</sub><br>P-Flash Control Register  | Bit Field | 0        | FBSY      | YE   | 1 | NVST<br>R  | MAS1        | ERAS<br>E | PROG      |

|                                                             |                                                          | Туре      | r        | rh        | rwh  | r | rw         | rw          | rw        | rw        |

| D2 <sub>H</sub>                                             | EECON Reset: 10 <sub>H</sub><br>D-Flash Control Register | Bit Field | 0        | EEBS<br>Y | YE   | 1 | NVST<br>R  | MAS1        | ERAS<br>E | PROG      |

|                                                             |                                                          | Туре      | r        | rh        | rwh  | r | rw         | rw          | rw        | rw        |

| D3 <sub>H</sub> FCS Re<br>Flash Control and Sta<br>Register | Flash Control and Status                                 | Bit Field | 1        | SBEIE     | FTEN | 0 | EEDE<br>RR | EESE<br>RR  | FDER<br>R | FSER<br>R |

|                                                             | Register                                                 | Туре      | r        | rw        | rwh  | r | rwh        | rwh         | rwh       | rwh       |

| D4 <sub>H</sub>                                             | FEAL Reset: 00 <sub>H</sub>                              | Bit Field | ECCEADDR |           |      |   |            |             |           |           |

|                                                             | Flash Error Address Register, Low Byte                   |           | rh       |           |      |   |            |             |           |           |

| D5 <sub>H</sub>                                             | FEAH Reset: 00 <sub>H</sub>                              | Bit Field | ECCEADDR |           |      |   |            |             |           |           |

|                                                             | Flash Error Address Register,<br>High Byte               | Туре      | rh       |           |      |   |            |             |           |           |

| D6 <sub>H</sub>                                             | FTVAL Reset: 78 <sub>H</sub>                             | Bit Field | MODE     | DE OFVAL  |      |   |            |             |           |           |

|                                                             | Flash Timer Value Register                               | Туре      | rw rw    |           |      |   |            |             |           |           |

| <sub>DD</sub> H                                             | FCS1 Reset: 00 <sub>H</sub> Flash Control and Status     | Bit Field | 0        |           |      |   |            | EEAB<br>ORT |           |           |

|                                                             | Register 1                                               | Туре      | r        |           |      |   |            |             | rwh       |           |

Table 20 and Table 21 shows the Flash data retention and endurance targets for Industrial profile and Automotive profile respectively.

Table 20 Flash Data Retention and Endurance for Industrial Profile (Operating Conditions apply)

| Retention     | Endurance <sup>1)2)</sup> | Size            | Remarks             |  |  |

|---------------|---------------------------|-----------------|---------------------|--|--|

| Program Flash | ·                         |                 |                     |  |  |

| 15 years      | 1000 cycles               | up to 60 Kbytes |                     |  |  |

| Data Flash    |                           | •               |                     |  |  |

| 15 years      | 1000 cycles               | 4 Kbytes        |                     |  |  |

| 10 years      | 10,000 cycles             | 4 Kbytes        |                     |  |  |

| 5 years       | 30,000 cycles             | 4 Kbytes        |                     |  |  |

| 1 year        | 100,000 cycles            | 4 Kbytes        | SAF and SAX variant |  |  |

|               | 80,000 cycles             |                 | SAK variant         |  |  |

<sup>1)</sup> In Program Flash, one cycle refers to the programming of all pages in the flash bank and a mass erase.

Table 21 Flash Data Retention and Endurance for Automotive Profile (Operating Conditions apply)

| Retention            | Endurance <sup>1)2)</sup> | Size            | Remarks |

|----------------------|---------------------------|-----------------|---------|

| Program Flash        |                           |                 |         |

| 15 years 1000 cycles |                           | up to 60 Kbytes |         |

| Data Flash           | ·                         | ·               | •       |

| 15 years             | 1000 cycles               | 4 Kbytes        |         |

| 5 years              | 10,000 cycles             | 1 Kbytes        |         |

| 2 years              | 15,000 cycles             | 512 Bytes       |         |

| 2 years              | 30,000 cycles             | 256 Bytes       |         |

| 1 year               | 100,000 cycles            | 128 Bytes       |         |

<sup>1)</sup> In Program Flash, one cycle refers to the programming of all pages in the flash bank and a mass erase.

Data Sheet 59 V1.5, 2011-03

<sup>2)</sup> In Data Flash, one cycle refers to the programming of all wordlines in a page and a page erase.

<sup>2)</sup> In Data Flash, one cycle refers to the programming of all wordlines in a page and a page erase.

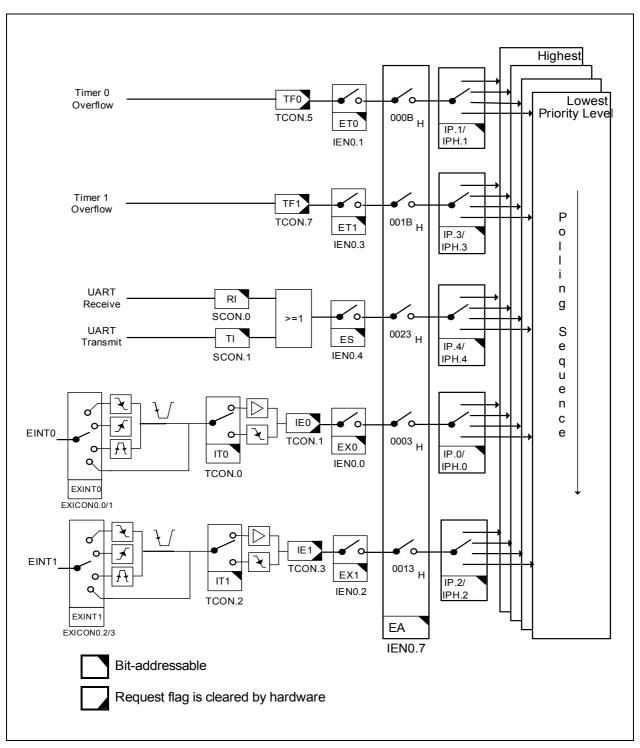

Figure 13 Interrupt Request Sources (Part 1)

### 3.4.2 Interrupt Source and Vector

Each interrupt event source has an associated interrupt vector address for the interrupt node it belongs to. This vector is accessed to service the corresponding interrupt node request. The interrupt service of each interrupt source can be individually enabled or disabled via an enable bit. The assignment of the XC87x interrupt sources to the interrupt vector address and the corresponding interrupt node enable bits are summarized in Table 22.

**Table 22** Interrupt Vector Addresses

| Interrupt<br>Source | Vector<br>Address | Assignment for XC87x                              | Enable Bit | SFR    |

|---------------------|-------------------|---------------------------------------------------|------------|--------|

| NMI                 | 0073 <sub>H</sub> | Watchdog Timer NMI                                | NMIWDT     | NMICON |

|                     |                   | PLL NMI                                           | NMIPLL     |        |

|                     |                   | Flash Timer NMI                                   | NMIFLASH   |        |

|                     |                   | V <sub>DDP</sub> Prewarning NMI                   | NMIVDDP    |        |

|                     |                   | Flash ECC NMI                                     | NMIECC     |        |

| XINTR0              | 0003 <sub>H</sub> | External Interrupt 0                              | EX0        | IEN0   |

| XINTR1              | 000B <sub>H</sub> | Timer 0                                           | ET0        |        |

| XINTR2              | 0013 <sub>H</sub> | External Interrupt 1                              | EX1        |        |

| XINTR3              | 001B <sub>H</sub> | Timer 1                                           | ET1        |        |

| XINTR4              | 0023 <sub>H</sub> | UART                                              | ES         |        |

| XINTR5              | 002B <sub>H</sub> | T2CCU                                             | ET2        |        |

|                     |                   | UART Fractional Divider (Normal Divider Overflow) |            |        |

|                     |                   | MultiCAN Node 0                                   |            |        |

|                     |                   | LIN                                               |            |        |

#### 3.8 Clock Generation Unit

The Clock Generation Unit (CGU) allows great flexibility in the clock generation for the XC87x. The power consumption is indirectly proportional to the frequency, whereas the performance of the microcontroller is directly proportional to the frequency. During user program execution, the frequency can be programmed for an optimal ratio between performance and power consumption. Therefore the power consumption can be adapted to the actual application state.

#### **Features**

- Phase-Locked Loop (PLL) for multiplying clock source by different factors

- PLL Base Mode

- Prescaler Mode

- PLL Mode

- Power-down mode support<sup>1)</sup>

The CGU consists of an oscillator circuit and a PLL. In the XC87x, the oscillator can be from either of these two sources: the on-chip oscillator (4 MHz) or the external oscillator (2 MHz to 20 MHz). The term "oscillator" is used to refer to both on-chip oscillator and external oscillator, unless otherwise stated. After the reset, the on-chip oscillator will be used by default. The external oscillator can be selected via software. In addition, the PLL provides a fail-safe logic to perform oscillator run and loss-of-lock detection. This allows emergency routines to be executed for system recovery or to perform system shut down.

Data Sheet 75 V1.5, 2011-03

<sup>1)</sup> SAK product variant does not support power-down mode.

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert FNMIWDT) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value (<WDTREL> \* 2<sup>8</sup>). The time period for an overflow of the WDT is programmable in two ways:

- The input frequency to the WDT can be selected to be either  $f_{\rm PCLK}/2$  or  $f_{\rm PCLK}/128$

- The reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{\rm WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} \, = \, \frac{2^{(1 \, + \, WDTIN \, \times \, 6)} \, \times \, (2^{16} - WDTREL \, \times \, 2^8)}{f_{PCLK}}$$

(3.3)

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{\rm WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 25**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB cannot be smaller than WDTREL.

Data Sheet 84 V1.5, 2011-03

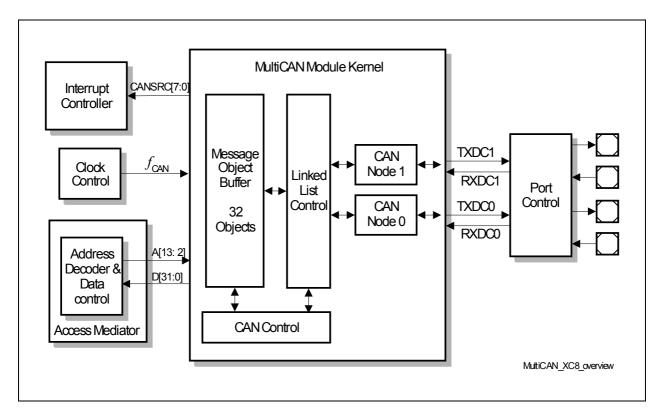

#### 3.21 Controller Area Network (MultiCAN)

The MultiCAN module contains two Full-CAN nodes operating independently or exchanging data and remote frames via a gateway function. Transmission and reception of CAN frames is handled in accordance to CAN specification V2.0 B active. Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

Both CAN nodes share a common set of message objects, where each message object may be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects may be combined to build gateways between the CAN nodes or to setup a FIFO buffer.

The message objects are organized in double chained lists, where each CAN node has it's own list of message objects. A CAN node stores frames only into message objects that are allocated to the list of the CAN node. It only transmits messages from objects of this list. A powerful, command driven list controller performs all list operations.

The bit timings for the CAN nodes are derived from the peripheral clock ( $f_{\text{CAN}}$ ) and are programmable up to a data rate of 1 MBaud. A pair of receive and transmit pins connects each CAN node to a bus transceiver.

Figure 30 Overview of the MultiCAN

#### **Features**

Compliant to ISO 11898.

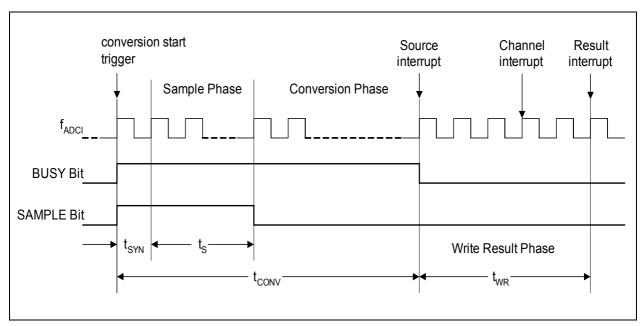

- Synchronization phase (t<sub>SYN</sub>)

- Sample phase  $(t_S)$

- Conversion phase

- Write result phase (t<sub>WR</sub>)

Figure 32 ADC Conversion Timing

#### **Electrical Parameters**

### 4 Electrical Parameters

**Chapter 4** provides the characteristics of the electrical parameters which are implementation-specific for the XC87x.

#### 4.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 4.2** and **Section 4.3**.

### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the XC87x and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

#### · cc

These parameters indicate Controller Characteristics, which are distinctive features of the XC87x and must be regarded for a system design.

#### SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the XC87x is designed in.

Data Sheet 108 V1.5, 2011-03

#### **Electrical Parameters**

#### 4.3.6 External Clock Drive XTAL1

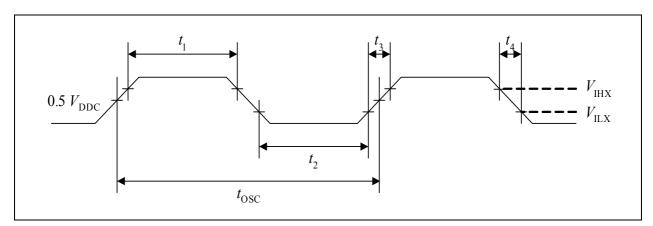

**Table 52** shows the parameters that define the external clock supply for XC87x. These timing parameters are based on the direct XTAL1 drive of clock input signals. They are not applicable if an external crystal or ceramic resonator is considered.

Table 52 External Clock Drive Characteristics (Operating Conditions apply)

| Parameter         | Symbo                 | Symbol |      | Limit Values |    | Test Conditions |  |

|-------------------|-----------------------|--------|------|--------------|----|-----------------|--|

|                   |                       |        | Min. | Max.         |    |                 |  |

| Oscillator period | $t_{\rm osc}$         | SR     | 50   | 500          | ns | 1)2)            |  |

| High time         | <i>t</i> <sub>1</sub> | SR     | 15   | -            | ns | 2)3)            |  |

| Low time          | $t_2$                 | SR     | 15   | -            | ns | 2)3)            |  |

| Rise time         | $t_3$                 | SR     | -    | 10           | ns | 2)3)            |  |

| Fall time         | $t_4$                 | SR     | -    | 10           | ns | 2)3)            |  |

- 1) The clock input signals with 45-55% duty cycle are used.

- 2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

- 3) The clock input signal must reach the defined levels  $V_{\rm ILX}$  and  $V_{\rm IHX}$ .

Figure 43 External Clock Drive XTAL1