Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Due durch Charture             |                                                                                |

|--------------------------------|--------------------------------------------------------------------------------|

| Product Status Ob              | bsolete                                                                        |

| Core Processor XC              | C800                                                                           |

| Core Size 8-I                  | Bit                                                                            |

| Speed 27                       | 7MHz                                                                           |

| Connectivity SP                | PI, SSI, UART/USART                                                            |

| Peripherals Bro                | rown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O 40               | 0                                                                              |

| Program Memory Size 64         | 4KB (64K x 8)                                                                  |

| Program Memory Type FL         | LASH                                                                           |

| EEPROM Size -                  |                                                                                |

| RAM Size 3.2                   | .25K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) 4.5 | 5V ~ 5.5V                                                                      |

| Data Converters A/I            | /D 8x10b                                                                       |

| Oscillator Type Int            | ternal                                                                         |

| Operating Temperature -40      | 10°C ~ 125°C (TA)                                                              |

| Mounting Type Su               | urface Mount                                                                   |

| Package / Case 64              | 4-LQFP                                                                         |

| Supplier Device Package PG     | G-LQFP-64-4                                                                    |

| Purchase URL htt               | ttps://www.e-xfl.com/product-detail/infineon-technologies/xc87816ffa5vackxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8-Bit

# XC87xCLM

8-Bit Single-Chip Microcontroller

Data Sheet V1.5 2011-03

# Microcontrollers

#### XC87x Data Sheet

#### Revision History: V1.5 2011-03

Previous Versions: V1.4

PageSubjects (major changes since last revision)Changes from V1.4 2010-08 to V1.5 2011-03Page 3A new variant, SAF-XC874CM-13FVA 5V, has been added in Table 2.

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

| $\sim$      |  |

|-------------|--|

| $\langle \$ |  |

|             |  |

#### **Summary of Features**

#### XC87x Variant Devices

The XC87x product family features devices with different configurations, program memory sizes, package options, power supply voltage, temperature and quality profiles (Automotive or Industrial), to offer cost-effective solutions for different application requirements.

The list of XC87x device configurations are summarized in **Table 1**. 2 types of packages are available :

- PG-LQFP-64, which is denoted by XC878 and;

- PG-VQFN-48, which is denoted by XC874

|             | •             |                    |               |

|-------------|---------------|--------------------|---------------|

| Device Name | CAN<br>Module | LIN BSL<br>Support | MDU<br>Module |

| XC87x       | No            | No                 | No            |

| XC87xM      | No            | No                 | Yes           |

| XC87xCM     | Yes           | No                 | Yes           |

| XC87xLM     | No            | Yes                | Yes           |

| XC87xCLM    | Yes           | Yes                | Yes           |

#### Table 1Device Configuration

From these 5 different combinations of configuration, each are further made available in many sales types, which are grouped according to device type, program memory sizes, power supply voltage, temperature and quality profiles (Automotive or Industrial), as shown in Table 2.

#### Table 2Device Profile

| Sales Type           | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|----------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAF-XC878-13FFI 5V   | Flash          | 52                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC878M-13FFI 5V  | Flash          | 52                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC878CM-13FFI 5V | Flash          | 52                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC878-16FFI 5V   | Flash          | 64                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC878M-16FFI 5V  | Flash          | 64                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC878CM-16FFI 5V | Flash          | 64                            | 5.0                    | -40 to 85                | Industrial         |

| SAF-XC878-13FFI 3V3  | Flash          | 52                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC878M-13FFI 3V3 | Flash          | 52                            | 3.3                    | -40 to 85                | Industrial         |

#### **General Device Information**

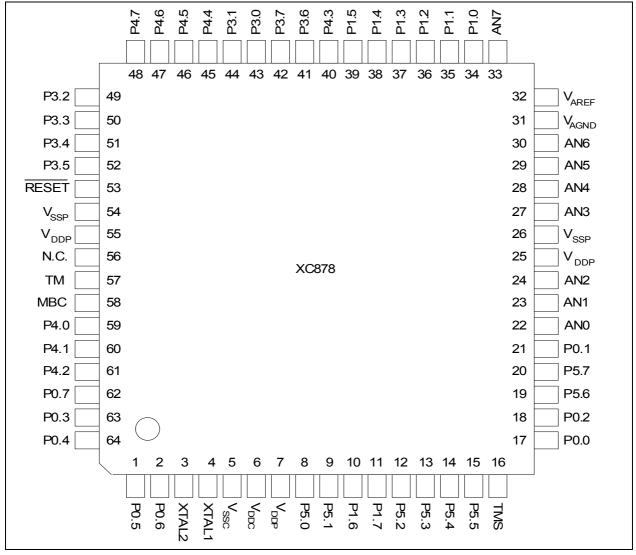

#### 2.3 Pin Configuration

The pin configuration of the XC878, which is based on the PG-LQFP-64, is shown in **Figure 4**, while that of the XC874, which is based on the PG-VQFN-48 package, is shown in **Figure 5**.

Figure 4 XC878 Pin Configuration, PG-LQFP-64 Package (top view)

# XC87xCLM

## **General Device Information**

# Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                  |                                                                                  |

|--------|--------------------------------------|------|----------------|---------------------------|----------------------------------------------------------------------------------|

| P0.3   | 63/1                                 |      | Hi-Z           | SCK_1<br>COUT63_1         | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3                 |

|        |                                      |      |                | RXDO1_0<br>A17            | UART1 Transmit Data Output<br>Address Line 17 Output                             |

| P0.4   | 64/2                                 |      | Hi-Z           | MTSR_1                    | SSC Master Transmit Output/<br>Slave Receive Input                               |

|        |                                      |      |                | CC62_1                    | Input/Output of<br>Capture/Compare channel 2                                     |

|        |                                      |      |                | TXD1_0                    | UART1 Transmit Data<br>Output/Clock Output                                       |

|        |                                      |      |                | A18                       | Address Line 18 Output                                                           |

| P0.5   | 1/3                                  |      | Hi-Z           | MRST_1                    | SSC Master Receive Input/Slave<br>Transmit Output                                |

|        |                                      |      |                | EXINT0_0                  | External Interrupt Input 0                                                       |

|        |                                      |      |                | T2EX1_1                   | Timer 21 External Trigger Input                                                  |

|        |                                      |      |                | RXD1_0                    | UART1 Receive Data Input                                                         |

|        |                                      |      |                | COUT62_1                  | Output of Capture/Compare<br>channel 2                                           |

|        |                                      |      |                | A19                       | Address Line 19 Output                                                           |

| P0.6   | 2/4                                  |      | PU             | T2CC4_1<br>WR             | Compare Output Channel 4<br>External Data Write Control<br>Output                |

| P0.7   | 62/48                                |      | PU             | CLKOUT_1<br>T2CC5_1<br>RD | Clock Output<br>Compare Output Channel 5<br>External Data Read Control<br>Output |

# 3.2.1 Memory Protection Strategy

The XC87x memory protection strategy includes:

- Basic protection: The user is able to block any external access via the boot option to any memory

- Read-out protection: The user is able to protect the contents in the Flash

- Flash program and erase protection

These protection strategies are enabled by programming a valid password (16-bit nonone value) via Bootstrap Loader (BSL) mode 6.

# 3.2.1.1 Flash Memory Protection

As long as a valid password is available, all external access to the device, including the Flash, will be blocked.

For additional security, the Flash hardware protection can be enabled to implement a second layer of read-out protection, as well as to enable program and erase protection.

Flash hardware protection is available only for Flash devices and comes in two modes:

- Mode 0: Only the P-Flash is protected; the D-Flash is unprotected

- Mode 1: Both the P-Flash and D-Flash are protected

The selection of each protection mode and the restrictions imposed are summarized in **Table 4**.

| Flash<br>Protection                                | Without hardware protection             | With hardware protection                      |                                               |  |  |  |  |  |

|----------------------------------------------------|-----------------------------------------|-----------------------------------------------|-----------------------------------------------|--|--|--|--|--|

| Hardware<br>Protection<br>Mode                     | -                                       | 0                                             | 1                                             |  |  |  |  |  |

| Activation Program a valid password via BSL mode 6 |                                         |                                               |                                               |  |  |  |  |  |

| Selection                                          | Bit 13 of password = 0                  | Bit 13 of password = 1<br>MSB of password = 0 | Bit 13 of password = 1<br>MSB of password = 1 |  |  |  |  |  |

| P-Flash<br>contents<br>can be read<br>by           | Read instructions in any program memory | Read instructions in the P-Flash              | Read instructions in the P-Flash or D-Flash   |  |  |  |  |  |

| External<br>access to P-<br>Flash                  | Not possible                            | Not possible                                  | Not possible                                  |  |  |  |  |  |

Table 4Flash Protection Modes

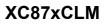

Address Extension by Mapping

# 3.2.4 XC87x Register Overview

The SFRs of the XC87x are organized into groups according to their functional units. The contents (bits) of the SFRs are summarized in **Chapter 3.2.4.1** to **Chapter 3.2.4.15**.

Note: The addresses of the bitaddressable SFRs appear in bold typeface.

# 3.2.4.1 CPU Registers

The CPU SFRs can be accessed in both the standard and mapped memory areas (RMAP = 0 or 1).

| Addr                                                                      | Register Name                                              | Bit           | 7             | 6    | 5    | 4         | 3    | 2      | 1    | 0    |  |

|---------------------------------------------------------------------------|------------------------------------------------------------|---------------|---------------|------|------|-----------|------|--------|------|------|--|

| RMAP =                                                                    | = 0 or 1                                                   | 1             |               |      |      |           |      |        |      |      |  |

| 81 <sub>H</sub>                                                           | SP Reset: 07 <sub>H</sub>                                  | Bit Field     |               |      |      | S         | P    |        |      |      |  |

|                                                                           | Stack Pointer Register                                     | Туре          |               |      |      | r         | W    |        |      |      |  |

| 82 <sub>H</sub>                                                           | DPL Reset: 00 <sub>H</sub>                                 | Bit Field     | DPL7          | DPL6 | DPL5 | DPL4      | DPL3 | DPL2   | DPL1 | DPL0 |  |

|                                                                           | Data Pointer Register Low                                  | Туре          | rw            | rw   | rw   | rw        | rw   | rw     | rw   | rw   |  |

| 83 <sub>H</sub>                                                           | DPH Reset: 00 <sub>H</sub>                                 | Bit Field     | DPH7          | DPH6 | DPH5 | DPH4      | DPH3 | DPH2   | DPH1 | DPH0 |  |

|                                                                           | Data Pointer Register High                                 | Туре          | rw            | rw   | rw   | rw        | rw   | rw     | rw   | rw   |  |

| 87 <sub>H</sub>                                                           | PCON Reset: 00 <sub>H</sub>                                | Bit Field     | SMOD          |      | 0    |           | GF1  | GF0    | 0    | IDLE |  |

|                                                                           | Power Control Register                                     | Туре          | rw            |      | r    |           | rw   | rw     | r    | rw   |  |

| <sup>88</sup> H                                                           | TCON Reset: 00 <sub>H</sub>                                | Bit Field     | TF1           | TR1  | TF0  | TR0       | IE1  | IT1    | IE0  | IT0  |  |

|                                                                           | Timer Control Register                                     | Туре          | rwh           | rw   | rwh  | rw        | rwh  | rw     | rwh  | rw   |  |

| 89 <sub>H</sub> <b>TMOD</b> Reset: 00 <sub>H</sub><br>Timer Mode Register | Bit Field                                                  | GATE<br>1     | T1S           | T1M  |      | GATE<br>0 | TOS  | OS TOM |      |      |  |

|                                                                           |                                                            | Туре          | Type rw rw rw |      |      | N         | rw   | rw     | r    | w    |  |

| 8A <sub>H</sub>                                                           | TL0 Reset: 00 <sub>H</sub>                                 | Bit Field VAL |               |      |      |           |      |        |      |      |  |

|                                                                           | Timer 0 Register Low                                       | Туре          |               |      |      | rv        | vh   |        |      |      |  |

| 8B <sub>H</sub>                                                           | TL1 Reset: 00 <sub>H</sub>                                 | Bit Field     | VAL           |      |      |           |      |        |      |      |  |

|                                                                           | Timer 1 Register Low                                       | Туре          |               |      |      | rv        | wh   |        |      |      |  |

| 8C <sub>H</sub>                                                           | TH0 Reset: 00 <sub>H</sub>                                 | Bit Field     |               |      |      | V         | AL   |        |      |      |  |

|                                                                           | Timer 0 Register High                                      | Туре          |               |      |      | rv        | vh   |        |      |      |  |

| 8D <sub>H</sub>                                                           | TH1 Reset: 00 <sub>H</sub>                                 | Bit Field     |               |      |      | V         | AL   |        |      |      |  |

|                                                                           | Timer 1 Register High                                      | Туре          |               |      |      | rv        | vh   |        |      |      |  |

| 94 <sub>H</sub>                                                           | MEX1 Reset: 00 <sub>H</sub>                                | Bit Field     |               | C    | В    |           |      | Ν      | IB   |      |  |

|                                                                           | Memory Extension Register 1                                | Туре          | pe r i        |      | r    | w         |      |        |      |      |  |

| 95 <sub>H</sub>                                                           | MEX2 Reset: 00 <sub>H</sub>                                | Bit Field     | MCM MCB IB    |      | В    |           |      |        |      |      |  |

|                                                                           | Memory Extension Register 2                                | Туре          | rw            |      | rw   |           |      | r      | w    |      |  |

| 96 <sub>H</sub>                                                           | MEX3 Reset: 00 <sub>H</sub><br>Memory Extension Register 3 | Bit Field     | MCB1<br>9     |      |      | IXM MXB   |      |        |      |      |  |

|                                                                           |                                                            | Туре          | rw            |      | r    | rw        | rw   |        | rw   |      |  |

#### Table 5 CPU Register Overview

| Table 6 | MDU Register Overview | (cont'd) |

|---------|-----------------------|----------|

|---------|-----------------------|----------|

| Addr            | Register Name                                                              | Bit       | 7      | 6                           | 5  | 4   | 3   | 2 | 1 | 0 |

|-----------------|----------------------------------------------------------------------------|-----------|--------|-----------------------------|----|-----|-----|---|---|---|

| B1 <sub>H</sub> | MDUCON Reset: 00 <sub>H</sub><br>MDU Control Register                      | Bit Field | IE     | IE IR RSEL STAR OPCODE<br>T |    |     |     |   |   | I |

|                 |                                                                            | Туре      | rw     | rw                          | rw | rwh |     | r | N |   |

| в2 <sub>Н</sub> | MD0 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Operand Register 0                                                     | Туре      |        |                             |    | r   | W   |   |   |   |

| B2 <sub>H</sub> | MR0 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Result Register 0                                                      | Туре      |        |                             |    | r   | h   |   |   |   |

| вз <sub>Н</sub> | MD1 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Operand Register 1                                                     | Туре      |        |                             |    | r   | w   |   |   |   |

| вз <sub>Н</sub> | MR1 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Result Register 1                                                      | Туре      |        |                             |    | r   | h   |   |   |   |

| B4 <sub>H</sub> | <sup>34</sup> H <b>MD2 Reset: 00<sub>H</sub></b><br>MDU Operand Register 2 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 |                                                                            | Туре      | rw     |                             |    |     |     |   |   |   |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Result Register 2                                                      | Туре      | rh     |                             |    |     |     |   |   |   |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Operand Register 3                                                     | Туре      |        |                             |    | r   | w   |   |   |   |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Result Register 3                                                      | Туре      |        |                             |    | r   | h   |   |   |   |

| в6 <sub>Н</sub> | MD4 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Operand Register 4                                                     | Туре      |        |                             |    | r   | W   |   |   |   |

| в6 <sub>Н</sub> | MR4 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Result Register 4                                                      | Туре      | ype rh |                             |    |     |     |   |   |   |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | ATA |   |   |   |

|                 | MDU Operand Register 5                                                     | Туре      |        |                             |    | r   | w   |   |   |   |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub>                                                 | Bit Field |        |                             |    | DA  | TA  |   |   |   |

|                 | MDU Result Register 5                                                      | Туре      |        |                             |    | r   | h   |   |   |   |

# 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 7 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|----------------------------------|-----------|-----------------|---|---|---|---|---|---|---|

| RMAP =          | : 1                              |           |                 |   |   |   |   |   |   |   |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field | Bit Field DATAL |   |   |   |   |   |   |   |

|                 | CORDIC X Data Low Byte           | Туре      |                 |   |   | r | W |   |   |   |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field | Bit Field DATAH |   |   |   |   |   |   |   |

|                 | CORDIC X Data High Byte          | Туре      |                 |   |   | r | W |   |   |   |

| Addr            | Register Name                                               | Bit       | 7    | 6    | 5          | 4    | 3    | 2    | 1      | 0    |  |

|-----------------|-------------------------------------------------------------|-----------|------|------|------------|------|------|------|--------|------|--|

| cc <sup>H</sup> | ADC_CRMR1 Reset: 00 <sub>H</sub><br>Conversion Request Mode | Bit Field | Rsv  | LDEV | CLRP<br>ND | SCAN | ENSI | ENTR | 0      | ENGT |  |

|                 | Register 1                                                  | Туре      | r    | w    | w          | rw   | rw   | rw   | r      | rw   |  |

| CD <sub>H</sub> | ADC_QMR0 Reset: 00 <sub>H</sub><br>Queue Mode Register 0    | Bit Field | CEV  | TREV | FLUS<br>H  | CLRV | 0    | ENTR | 0      | ENGT |  |

|                 |                                                             | Туре      | w    | w    | w          | w    | r    | rw   | r      | rw   |  |

| Ceh             | ADC_QSR0 Reset: 20 <sub>H</sub><br>Queue Status Register 0  | Bit Field | Rsv  | 0    | EMPT<br>Y  | EV   | (    | 0    |        | FILL |  |

|                 |                                                             | Туре      | r    | r    | rh         | rh   |      | r    | r      | h    |  |

| CF <sub>H</sub> | ADC_Q0R0 Reset: 00 <sub>H</sub>                             | Bit Field | EXTR | ENSI | RF         | V    | 0    | F    | REQCHN | २    |  |

|                 | Queue 0 Register 0                                          | Туре      | rh   | rh   | rh         | rh   | r    |      | rh     |      |  |

| D2 <sub>H</sub> | ADC_QBUR0 Reset: 00 <sub>H</sub>                            | Bit Field | EXTR | ENSI | RF         | V    | 0    | F    | REQCHN | २    |  |

|                 | Queue Backup Register 0                                     | Туре      | rh   | rh   | rh         | rh   | r    |      | rh     |      |  |

| D2 <sub>H</sub> | ADC_QINR0 Reset: 00 <sub>H</sub>                            | Bit Field | EXTR | ENSI | RF         | (    | )    | F    | REQCHN | ٦    |  |

|                 | Queue Input Register 0                                      | Туре      | w    | w    | w          |      | r    |      | w      |      |  |

# Table 11ADC Register Overview (cont'd)

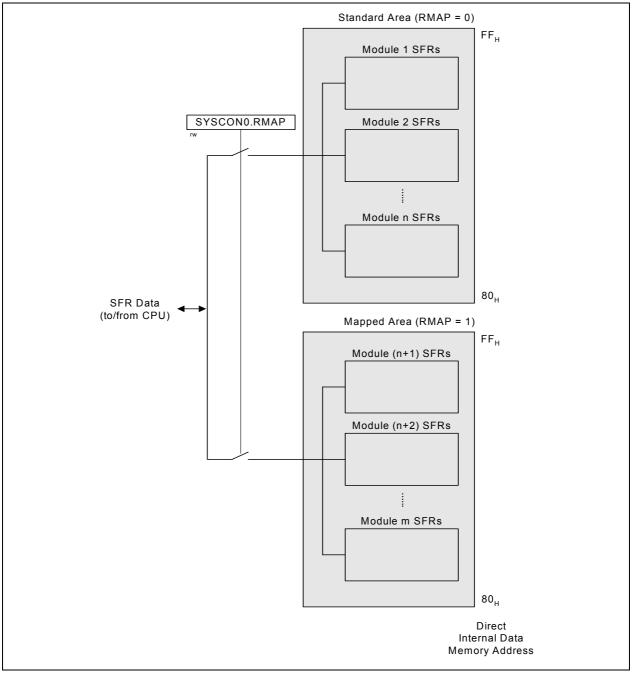

Figure 15 Interrupt Request Sources (Part 3)

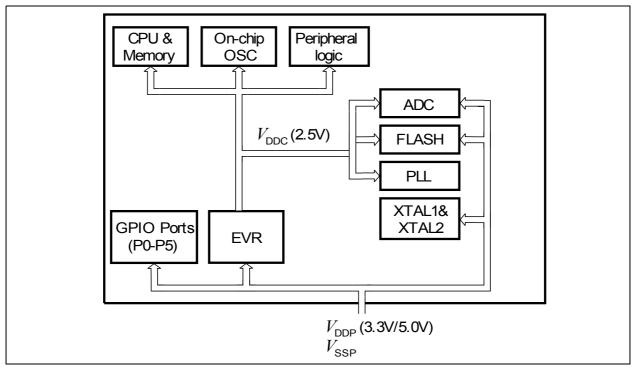

# 3.6 Power Supply System with Embedded Voltage Regulator

The XC87x microcontroller requires two different levels of power supply:

- 3.3 V or 5.0 V for the Embedded Voltage Regulator (EVR) and Ports

- 2.5 V for the core, memory, on-chip oscillator, and peripherals

**Figure 19** shows the XC87x power supply system. A power supply of 3.3 V or 5.0 V must be provided from the external power supply pin. The 2.5 V power supply for the logic is generated by the EVR. The EVR helps to reduce the power consumption of the whole chip and the complexity of the application board design.

The EVR consists of a main voltage regulator and a low power voltage regulator. In active mode, both voltage regulators are enabled. In power-down mode<sup>1)</sup>, the main voltage regulator is switched off, while the low power voltage regulator continues to function and provide power supply to the system with low power consumption.

72

Figure 19 XC87x Power Supply System

# **EVR Features**

- Input voltage ( $V_{\text{DDP}}$ ): 3.3 V/5.0 V

- Output voltage ( $V_{DDC}$ ): 2.5 V ± 7.5%

- Low power voltage regulator provided in power-down mode<sup>1)</sup>

- $V_{\text{DDP}}$  prewarning detection

- V<sub>DDC</sub> brownout detection

<sup>1)</sup> SAK product variant does not support power-down mode.

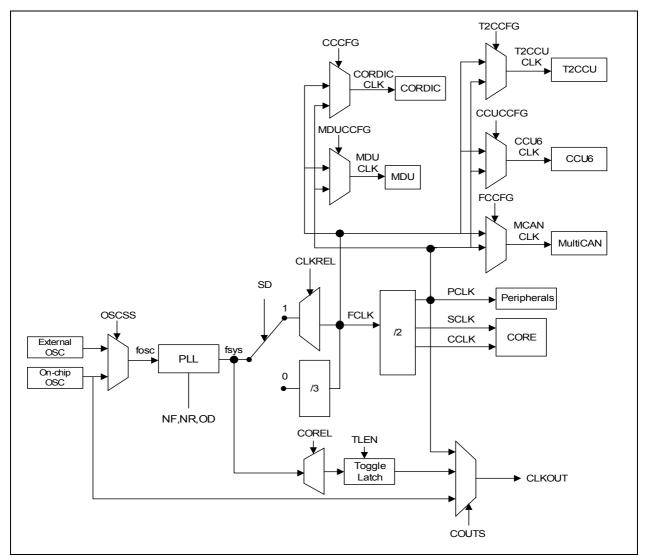

Figure 22 Clock Generation from  $f_{sys}$

For power saving purposes, the clocks may be disabled or slowed down according to **Table 27**.

# Table 27System frequency ( $f_{sys}$ = 144 MHz)

| Power Saving Mode        | Action                                                                                                                   |  |  |  |  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Idle                     | Clock to the CPU is disabled.                                                                                            |  |  |  |  |  |  |

| Slow-down                | Clocks to the CPU and all the peripherals are divided by a common programmable factor defined by bit field CMCON.CLKREL. |  |  |  |  |  |  |

| Power-down <sup>1)</sup> | Oscillator and PLL are switched off.                                                                                     |  |  |  |  |  |  |

1) SAK product variant does not support power-down mode.

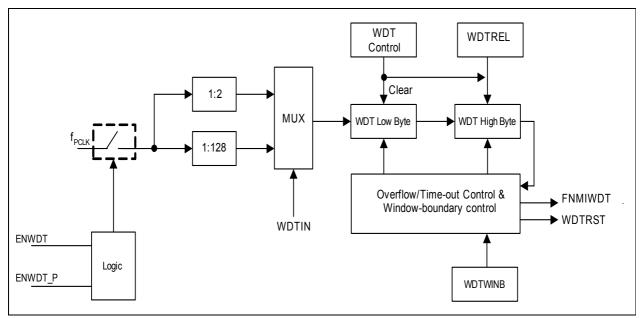

# 3.10 Watchdog Timer

The Watchdog Timer (WDT) provides a highly reliable and secure way to detect and recover from software or hardware failures. The WDT is reset at a regular interval that is predefined by the user. The CPU must service the WDT within this interval to prevent the WDT from causing an XC87x system reset. Hence, routine service of the WDT confirms that the system is functioning properly. This ensures that an accidental malfunction of the XC87x will be aborted in a user-specified time period.

In debug mode, the WDT is default suspended and stops counting. Therefore, there is no need to refresh the WDT during debugging.

#### Features

- 16-bit Watchdog Timer

- Programmable reload value for upper 8 bits of timer

- Programmable window boundary

- Selectable input frequency of  $f_{PCLK}/2$  or  $f_{PCLK}/128$

- Time-out detection with NMI generation and reset prewarning activation (after which a system reset will be performed)

The WDT is a 16-bit timer incremented by a count rate of  $f_{PCLK}/2$  or  $f_{PCLK}/128$ . This 16-bit timer is realized as two concatenated 8-bit timers. The upper 8 bits of the WDT can be preset to a user-programmable value via a watchdog service access in order to modify the watchdog expire time period. The lower 8 bits are reset on each service access. **Figure 24** shows the block diagram of the WDT unit.

Figure 24 WDT Block Diagram

| Table 32 Deviation Error for UART with Fractional Divider enabled |                               |                                |                        |                    |  |

|-------------------------------------------------------------------|-------------------------------|--------------------------------|------------------------|--------------------|--|

| f <sub>pclk</sub>                                                 | Prescaling Factor<br>(2BRPRE) | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |  |

| 24 MHz                                                            | 1                             | 6 (6 <sub>H</sub> )            | 59 (3B <sub>H</sub> )  | +0.03 %            |  |

| 12 MHz                                                            | 1                             | 3 (3 <sub>H</sub> )            | 59 (3B <sub>H</sub> )  | +0.03 %            |  |

| 8 MHz                                                             | 1                             | 2 (2 <sub>H</sub> )            | 59 (3B <sub>H</sub> )  | +0.03 %            |  |

| 6 MHz                                                             | 1                             | 6 (6 <sub>H</sub> )            | 236 (EC <sub>H</sub> ) | +0.03 %            |  |

# Table 32 Deviation Error for UART with Fractional Divider enabled

#### 3.13.2 Baud Rate Generation using Timer 1

In UART modes 1 and 3 of UART module, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

Mode 1, 3 baud rate=

$$\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$$

(3.6)

# 3.14 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see **Figure 26**). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock  $f_{MOD}$  that is 1/n of the input clock  $f_{DIV}$ , where n is defined by 256 - STEP. The output frequency in normal divider mode is derived as follows:

$$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$$

(3.7)

needed for the handshaking between the master and slave tasks is provided by the master task through the header portion of the frame.

The header consists of a break and synch pattern followed by an identifier. Among these three fields, only the break pattern cannot be transmitted as a normal 8-bit UART data. The break must contain a dominant value of 13 bits or more to ensure proper synchronization of slave nodes.

In the LIN communication, a slave task is required to be synchronized at the beginning of the protected identifier field of frame. For this purpose, every frame starts with a sequence consisting of a break field followed by a synch byte field. This sequence is unique and provides enough information for any slave task to detect the beginning of a new frame and be synchronized at the start of the identifier field.

Upon entering LIN communication, a connection is established and the transfer speed (baud rate) of the serial communication partner (host) is automatically synchronized in the following steps:

STEP 1: Initialize interface for reception and timer for baud rate measurement

- STEP 2: Wait for an incoming LIN frame from host

- STEP 3: Synchronize the baud rate to the host

- STEP 4: Enter for Master Request Frame or for Slave Response Frame

- Note: Re-synchronization and setup of baud rate are always done for **every** Master Request Header or Slave Response Header LIN frame.

#### **Electrical Parameters**

# 4.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the XC87x can be subjected to without permanent damage.

| Parameter                                                    | Symbol            | Limit Values |                                        | Unit | Notes                |

|--------------------------------------------------------------|-------------------|--------------|----------------------------------------|------|----------------------|

|                                                              |                   | min.         | max.                                   |      |                      |

| Ambient temperature                                          | T <sub>A</sub>    | -40          | 125                                    | °C   | under bias           |

| Storage temperature                                          | T <sub>ST</sub>   | -65          | 150                                    | °C   |                      |

| Junction temperature                                         | TJ                | -40          | 140                                    | °C   | under bias           |

| Voltage on power supply pin with respect to $V_{SS}$         | V <sub>DDP</sub>  | -0.5         | 6                                      | V    |                      |

| Voltage on any pin with respect to $V_{SS}$                  | V <sub>IN</sub>   | -0.5         | V <sub>DDP</sub> +<br>0.5 or<br>max. 6 | V    | Whatever is<br>lower |

| Input current on any pin during overload condition           | I <sub>IN</sub>   | -10          | 10                                     | mA   |                      |

| Absolute sum of all input currents during overload condition | $\Sigma  I_{IN} $ | -            | 50                                     | mA   |                      |

| Table 38 | Absolute Maximum Rating Parameters |

|----------|------------------------------------|

|----------|------------------------------------|

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pin with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### **Electrical Parameters**

# 4.2 DC Parameters

The electrical characteristics of the DC Parameters are detailed in this section.

#### 4.2.1 Input/Output Characteristics

Table 40 provides the characteristics of the input/output pins of the XC87x.

| Table 40Input/Output Characteristics (Operating Conditions apply) | Table 40 | Input/Output C | Characteristics | (Operating | Conditions apply) |

|-------------------------------------------------------------------|----------|----------------|-----------------|------------|-------------------|

|-------------------------------------------------------------------|----------|----------------|-----------------|------------|-------------------|

| Parameter                                            | Symbol            |    | Limit Values |                  | Unit | Test Conditions                                                                              |  |

|------------------------------------------------------|-------------------|----|--------------|------------------|------|----------------------------------------------------------------------------------------------|--|

|                                                      |                   |    | min.         | max.             |      |                                                                                              |  |

| V <sub>DDP</sub> = 5 V Range                         |                   |    |              |                  |      |                                                                                              |  |

| Output low voltage                                   | V <sub>OL</sub>   | CC | _            | 0.6              | V    | $I_{OL} = 9 \text{ mA} (DS = 0)^{1}$<br>$I_{OL} = 12 \text{ mA} (DS = 1)^{2}$                |  |

| Output high voltage                                  | V <sub>OH</sub>   | CC | 2.4          | -                | V    | $I_{\rm OH}$ = -20 mA (DS = 0) <sup>1)</sup><br>$I_{\rm OH}$ = -25 mA (DS = 1) <sup>2)</sup> |  |

| Input low voltage                                    | $V_{\rm IL}$      | SR | -0.3         | 0.8              | V    | CMOS Mode                                                                                    |  |

| Input high voltage                                   | $V_{\rm IH}$      | SR | 2.2          | $V_{DDP}$        | V    | CMOS Mode                                                                                    |  |

| Input Hysteresis                                     | HYS               | CC | 0.35         | -                | V    | CMOS Mode <sup>3)7)</sup>                                                                    |  |

| Input low voltage at XTAL1                           | V <sub>ILX</sub>  | SR | -0.3         | 0.8              | V    |                                                                                              |  |

| Input high voltage at XTAL1                          | V <sub>IHX</sub>  | SR | 3.4          | V <sub>DDP</sub> | V    |                                                                                              |  |

| Pull-up current                                      | $I_{\rm PU}$      | SR | -            | -20              | μA   | V <sub>IH,min</sub>                                                                          |  |

|                                                      |                   |    | -88          | _                | μA   | V <sub>IL,max</sub>                                                                          |  |

| Pull-down current                                    | $I_{PD}$          | SR | _            | 10               | μA   | V <sub>IL,max</sub>                                                                          |  |

|                                                      |                   |    | 66           | -                | μA   | V <sub>IH,min</sub>                                                                          |  |

| Input leakage current                                | I <sub>OZ1</sub>  | CC | -1           | 1                | μA   | $0 < V_{IN} < V_{DDP},$<br>$T_A \le 105^{\circ}C^{4)}$                                       |  |

| Overload current on any pin                          | I <sub>OV</sub>   | SR | -5           | 5                | mA   |                                                                                              |  |

| Absolute sum of overload currents                    | $\Sigma  I_{OV} $ | SR | -            | 25               | mA   | 5)                                                                                           |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off | V <sub>PO</sub>   | SR | -            | 0.3              | V    | 6)                                                                                           |  |

# Package and Quality Declaration

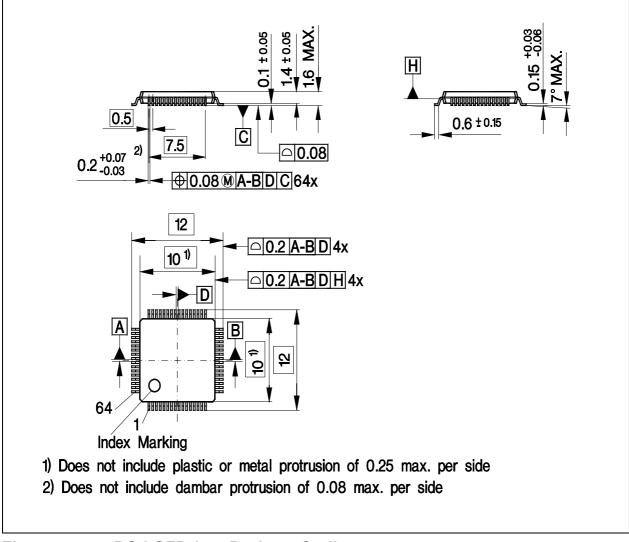

# 5.2 Package Outline

Figure 47 shows the package outlines of the XC878.

Figure 47 PG-LQFP-64-4 Package Outline