Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 27MHz                                                                           |

| Connectivity               | SPI, SSI, UART/USART                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 40                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | <u> </u>                                                                        |

| RAM Size                   | 3.25K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                       |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | PG-LQFP-64-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc87816ffi5vacfxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

## **Table of Contents**

| 1                                    | Summary of Features                                                                                                                   | 1           |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|

| <b>2</b><br>2.1<br>2.2<br>2.3<br>2.4 | General Device Information         Block Diagram         Logic Symbol         Pin Configuration         Pin Definitions and Functions | 6<br>7<br>8 |

| 3                                    | Functional Description                                                                                                                | 21          |

| 3.1                                  | Processor Architecture                                                                                                                | 21          |

| 3.2                                  | Memory Organization                                                                                                                   | 22          |

| 3.2.1                                | Memory Protection Strategy 2                                                                                                          |             |

| 3.2.1.1                              | Flash Memory Protection                                                                                                               |             |

| 3.2.2                                | Special Function Register                                                                                                             |             |

| 3.2.2.1                              | Address Extension by Mapping 2                                                                                                        |             |

| 3.2.2.2                              | Address Extension by Paging 2                                                                                                         |             |

| 3.2.3                                | Bit Protection Scheme                                                                                                                 |             |

| 3.2.3.1                              | Password Register                                                                                                                     | 33          |

| 3.2.4                                | XC87x Register Overview                                                                                                               |             |

| 3.2.4.1                              | CPU Registers                                                                                                                         | 34          |

| 3.2.4.2                              | MDU Registers                                                                                                                         | 35          |

| 3.2.4.3                              | CORDIC Registers                                                                                                                      | 36          |

| 3.2.4.4                              | System Control Registers 3                                                                                                            | 37          |

| 3.2.4.5                              | WDT Registers                                                                                                                         | 10          |

| 3.2.4.6                              | Port Registers 4                                                                                                                      | 10          |

| 3.2.4.7                              | ADC Registers 4                                                                                                                       | 13          |

| 3.2.4.8                              | Timer 2 Compare/Capture Unit Registers 4                                                                                              | 17          |

| 3.2.4.9                              | Timer 21 Registers 4                                                                                                                  | 19          |

| 3.2.4.10                             | CCU6 Registers 5                                                                                                                      | 50          |

| 3.2.4.11                             | UART1 Registers                                                                                                                       | 54          |

| 3.2.4.12                             | SSC Registers 5                                                                                                                       | 54          |

| 3.2.4.13                             | MultiCAN Registers 5                                                                                                                  | 55          |

| 3.2.4.14                             | OCDS Registers 5                                                                                                                      | 55          |

| 3.2.4.15                             | Flash Registers 5                                                                                                                     | 57          |

| 3.3                                  | Flash Memory                                                                                                                          | 58          |

| 3.3.1                                | 0                                                                                                                                     | 60          |

| 3.4                                  |                                                                                                                                       | 51          |

| 3.4.1                                |                                                                                                                                       | 51          |

| 3.4.2                                |                                                                                                                                       | 67          |

| 3.4.3                                |                                                                                                                                       | <u>5</u> 9  |

| 3.5                                  |                                                                                                                                       | 70          |

| 3.6                                  | Power Supply System with Embedded Voltage Regulator                                                                                   | '2          |

#### **Summary of Features**

## Table 2Device Profile (cont'd)

| Sales Type            | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|-----------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAF-XC878CM-13FFI 3V3 | Flash          | 52                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC878-16FFI 3V3   | Flash          | 64                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC878M-16FFI 3V3  | Flash          | 64                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC878CM-16FFI 3V3 | Flash          | 64                            | 3.3                    | -40 to 85                | Industrial         |

| SAF-XC878-13FFA 5V    | Flash          | 52                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC878CM-13FFA 5V  | Flash          | 52                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC878LM-13FFA 5V  | Flash          | 52                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC878CLM-13FFA 5V | Flash          | 52                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC878-16FFA 5V    | Flash          | 64                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC878CM-16FFA 5V  | Flash          | 64                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC878LM-16FFA 5V  | Flash          | 64                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC878CLM-16FFA 5V | Flash          | 64                            | 5.0                    | -40 to 85                | Automotive         |

| SAX-XC878-13FFA 5V    | Flash          | 52                            | 5.0                    | -40 to 105               | Automotive         |

| SAX-XC878CM-13FFA 5V  | Flash          | 52                            | 5.0                    | -40 to 105               | Automotive         |

| SAX-XC878LM-13FFA 5V  | Flash          | 52                            | 5.0                    | -40 to 105               | Automotive         |

| SAX-XC878CLM-13FFA 5V | Flash          | 52                            | 5.0                    | -40 to 105               | Automotive         |

| SAX-XC878-16FFA 5V    | Flash          | 64                            | 5.0                    | -40 to 105               | Automotive         |

| SAX-XC878CM-16FFA 5V  | Flash          | 64                            | 5.0                    | -40 to 105               | Automotive         |

| SAX-XC878LM-16FFA 5V  | Flash          | 64                            | 5.0                    | -40 to 105               | Automotive         |

| SAX-XC878CLM-16FFA 5V | Flash          | 64                            | 5.0                    | -40 to 105               | Automotive         |

| SAK-XC878-13FFA 5V    | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC878CM-13FFA 5V  | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC878LM-13FFA 5V  | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC878CLM-13FFA 5V | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC878-16FFA 5V    | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC878CM-16FFA 5V  | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC878LM-16FFA 5V  | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC878CLM-16FFA 5V | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAF-XC874LM-16FVA 5V  | Flash          | 64                            | 5.0                    | -40 to 85                | Automotive         |

#### **Summary of Features**

| Sales Type           | Device<br>Type | Program<br>Memory<br>(Kbytes) | Power<br>Supply<br>(V) | Temp-<br>erature<br>(°C) | Quality<br>Profile |

|----------------------|----------------|-------------------------------|------------------------|--------------------------|--------------------|

| SAF-XC874CM-16FVA 5V | Flash          | 64                            | 5.0                    | -40 to 85                | Automotive         |

| SAF-XC874CM-13FVA 5V | Flash          | 52                            | 5.0                    | -40 to 85                | Automotive         |

| SAK-XC874LM-16FVA 5V | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874CM-16FVA 5V | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874-16FVA 5V   | Flash          | 64                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874LM-13FVA 5V | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874CM-13FVA 5V | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

| SAK-XC874-13FVA 5V   | Flash          | 52                            | 5.0                    | -40 to 125               | Automotive         |

As this document refers to all the derivatives, some description may not apply to a specific product. For simplicity, all versions are referred to by the term XC87x throughout this document.

#### **Ordering Information**

The ordering code for Infineon Technologies microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- The package and the type of delivery

For the available ordering codes for the XC87x, please refer to your responsible sales representative or your local distributor.

#### **General Device Information**

## 2.4 Pin Definitions and Functions

The functions and default states of the XC87x external pins are provided in Table 3.

| Table S |                                      |      |                |                                                               |                                                                                                                                                                                                      |

|---------|--------------------------------------|------|----------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                                                      |                                                                                                                                                                                                      |

| P0      |                                      | I/O  |                | I/O port. It ca<br>for the JTAG<br>Timer 21, Mu<br>Interface. | B-bit bidirectional general purpose<br>an be used as alternate functions<br>6, CCU6, UART, UART1, T2CCU,<br>ultiCAN, SSC and External Bus<br>al Bus Interface is not available in<br>4.              |

| P0.0    | 17/12                                |      | Hi-Z           | TCK_0<br>T12HR_1<br>CC61_1<br>CLKOUT_0<br>RXDO_1              | •                                                                                                                                                                                                    |

| P0.1    | 21/14                                |      | Hi-Z           | TDI_0<br>T13HR_1<br>RXD_1<br>RXDC1_0<br>COUT61_1<br>EXF2_1    | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input<br>UART Receive Data Input<br>MultiCAN Node 1 Receiver Input<br>Output of Capture/Compare<br>channel 1<br>Timer 2 External Flag Output |

| P0.2    | 18/13                                |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1<br>TXDC1_0                          | CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Data<br>Output/Clock Output<br>MultiCAN Node 1 Transmitter<br>Output                                                                     |

#### Table 3Pin Definitions and Functions

## 3.2.3.1 Password Register

# PASSWD

| Password | Register |      |   |   |               | Reset | Value: 07 <sub>H</sub> |

|----------|----------|------|---|---|---------------|-------|------------------------|

| 7        | 6        | 5    | 4 | 3 | 2             | 1     | 0                      |

|          | 1        | PASS |   | 1 | PROTECT<br>_S | МС    | DDE                    |

| L        |          | W    | I | I | rh            | r     | W                      |

| Field     | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE      | [1:0] | rw   | <ul> <li>Bit Protection Scheme Control Bits</li> <li>00 Scheme disabled - direct access to the protected bits is allowed.</li> <li>11 Scheme enabled - the bit field PASS has to be written with the passwords to open and close the access to protected bits. (default)</li> <li>Others:Scheme Enabled.</li> <li>These two bits cannot be written directly. To change the value between 11<sub>B</sub> and 00<sub>B</sub>, the bit field PASS must be written with 11000<sub>B</sub>; only then, will the MODE[1:0] be registered.</li> </ul> |

| PROTECT_S | 2     | rh   | <ul> <li>Bit Protection Signal Status Bit</li> <li>This bit shows the status of the protection.</li> <li>0 Software is able to write to all protected bits.</li> <li>1 Software is unable to write to any protected bits.</li> </ul>                                                                                                                                                                                                                                                                                                           |

| PASS      | [7:3] | w    | Password BitsThe Bit Protection Scheme only recognizes threepatterns. $11000_B$ Enables writing of the bit field MODE. $10011_B$ Opens access to writing of all protected bits. $10101_B$ Closes access to writing of all protected bits                                                                                                                                                                                                                                                                                                       |

### Table 12T2CCU Register Overview (cont'd)

| Addr            | Register Name                                                                        | Bit       | 7          | 6    | 5          | 4          | 3          | 2           | 1          | 0          |

|-----------------|--------------------------------------------------------------------------------------|-----------|------------|------|------------|------------|------------|-------------|------------|------------|

| C5 <sub>H</sub> | T2CCU_CCTH Reset: 00 <sub>H</sub>                                                    | Bit Field |            | Ι    | Ι          | C          | СТ         |             |            | 1          |

|                 | T2CCU Capture/Compare<br>Timer Register High                                         | Туре      |            |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CCTCON Reset: 00 <sub>H</sub><br>T2CCU CaptureCcompare                         | Bit Field |            | ССТ  | PRE        |            | CCTO<br>VF | CCTO<br>VEN | TIMSY<br>N | CCTS<br>T  |

|                 | Timer Control Register                                                               | Туре      |            | r    | W          |            | rwh        | rw          | rw         | rw         |

| RMAP =          | 0, PAGE 2                                                                            |           |            |      |            |            |            |             |            |            |

| C0 <sub>H</sub> | <b>T2CCU_COSHDWReset: 00<sub>H</sub></b><br>T2CCU Capture/compare<br>Enable Register | Bit Field | ENSH<br>DW | TXOV | COOU<br>T5 | COOU<br>T4 | COOU<br>T3 | COOU<br>T2  | COOU<br>T1 | COOU<br>T0 |

|                 |                                                                                      | Туре      | rwh        | rwh  | rwh        | rwh        | rwh        | rwh         | rwh        | rwh        |

| C1 <sub>H</sub> | T2CCU_CC0L Reset: 00 <sub>H</sub><br>T2CCU Capture/Compare                           | Bit Field |            |      |            | CC/        | /ALL       |             |            |            |

|                 | Register 0 Low                                                                       | Туре      |            |      |            | rv         | vh         |             |            |            |

| C2 <sub>H</sub> | T2CCU_CC0H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 0 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

| C3 <sub>H</sub> | T2CCU_CC1L Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 1 Low                                              | Туре      |            |      |            | rv         | vh         |             |            |            |

| C4 <sub>H</sub> | T2CCU_CC1H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 1 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

| C5 <sub>H</sub> | T2CCU_CC2L Reset: 00 <sub>H</sub>                                                    | Bit Field | CCVALL     |      |            |            |            |             |            |            |

|                 | T2CCU Capture/compare<br>Register 2 Low                                              | Туре      | rwh        |      |            |            |            |             |            |            |

| C6 <sub>H</sub> | T2CCU_CC2H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 2 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

| RMAP =          | 0, PAGE 3                                                                            |           |            |      |            |            |            |             |            |            |

| C0 <sub>H</sub> | T2CCU_COCON Reset: 00 <sub>H</sub><br>T2CCU Compare Control                          | Bit Field | CCM5       | CCM4 | CM5F       | CM4F       | POLB       | POLA        | CON        | NOD        |

|                 | Register                                                                             | Туре      | rw         | rw   | rwh        | rwh        | rw         | rw          | r          | W          |

| C1 <sub>H</sub> | T2CCU_CC3L Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 3 Low                                              | Туре      |            |      |            | rv         | vh         |             |            |            |

| C2 <sub>H</sub> | T2CCU_CC3H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 3 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

| C3 <sub>H</sub> | T2CCU_CC4L Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 4 Low                                              | Туре      |            |      |            | rv         | vh         |             |            |            |

| C4 <sub>H</sub> | T2CCU_CC4H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 4 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

| C5 <sub>H</sub> | T2CCU_CC5L Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 5 Low                                              | Туре      |            |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CC5H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 5 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

## 3.2.4.10 CCU6 Registers

The CCU6 SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 14 CCU6 Register Overview

| Addr            | Register Name                                                                | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |  |

|-----------------|------------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|--|--|

| RMAP =          | = 0                                                                          |           | 1          |            | 1          | 1          |            |            |            |            |  |  |

| A3 <sub>H</sub> | CCU6_PAGE Reset: 00 <sub>H</sub>                                             | Bit Field | C          | P          | ST         | NR         | 0          |            | PAGE       |            |  |  |

|                 | Page Register                                                                | Туре      | \<br>\     | w w r rwh  |            |            |            |            |            |            |  |  |

| RMAP =          | = 0, PAGE 0                                                                  |           |            |            |            |            |            |            |            |            |  |  |

| 9A <sub>H</sub> | CCU6_CC63SRL Reset: 00 <sub>H</sub>                                          | Bit Field |            |            |            | CC6        | 3SL        |            |            |            |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC63 Low                      | Туре      | rw         |            |            |            |            |            |            |            |  |  |

| 9B <sub>H</sub> | CCU6_CC63SRH Reset: 00 <sub>H</sub>                                          | Bit Field |            |            |            | CC6        | 3SH        |            |            |            |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC63 High                     | Туре      |            |            |            | r          | w          |            |            |            |  |  |

| 9CH             | CCU6_TCTR4L Reset: 00 <sub>H</sub><br>Timer Control Register 4 Low           | Bit Field | T12<br>STD | T12<br>STR |            | 0          | DT<br>RES  | T12<br>RES | T12R<br>S  | T12R<br>R  |  |  |

|                 |                                                                              | Туре      | w          | w          |            | r          | w          | w          | w          | w          |  |  |

| 9D <sub>H</sub> | CCU6_TCTR4H Reset: 00 <sub>H</sub><br>Timer Control Register 4 High          | Bit Field | T13<br>STD | T13<br>STR |            | 0          |            | T13<br>RES | T13R<br>S  | T13R<br>R  |  |  |

|                 |                                                                              | Туре      | w          | w          |            | r          |            | w          | w          | w          |  |  |

| 9E <sub>H</sub> | CCU6_MCMOUTSL Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRM<br>CM | 0          | MCMPS      |            |            |            |            |            |  |  |

|                 | Register Low                                                                 | Туре      | w          | r          | rw         |            |            |            |            |            |  |  |

| 9F <sub>H</sub> | CCU6_MCMOUTSH Reset: 00 <sub>H</sub><br>Multi-Channel Mode Output Shadow     | Bit Field | STRH<br>P  | 0          |            | CURHS      |            | EXPHS      |            |            |  |  |

|                 | Register High                                                                | Туре      | w          | r          | rw         |            | rw         |            |            |            |  |  |

| A4 <sub>H</sub> | CCU6_ISRL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RT12<br>PM | RT12<br>OM | RCC6<br>2F | RCC6<br>2R | RCC6<br>1F | RCC6<br>1R | RCC6<br>0F | RCC6<br>0R |  |  |

|                 | Reset Register Low                                                           | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |  |  |

| A5 <sub>H</sub> | CCU6_ISRH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status         | Bit Field | RSTR       | RIDLE      | RWH<br>E   | RCHE       | 0          | RTRP<br>F  | RT13<br>PM | RT13<br>CM |  |  |

|                 | Reset Register High                                                          | Туре      | w          | w          | w          | w          | r          | w          | w          | w          |  |  |

| A6 <sub>H</sub> | CCU6_CMPMODIFL Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC6<br>3S |            | 0          |            | MCC6<br>2S | MCC6<br>1S | MCC6<br>0S |  |  |

|                 | Low                                                                          | Туре      | r          | w          |            | r          |            | w          | w          | w          |  |  |

| а7 <sub>Н</sub> | CCU6_CMPMODIFH Reset: 00 <sub>H</sub><br>Compare State Modification Register | Bit Field | 0          | MCC6<br>3R |            | 0          |            | MCC6<br>2R | MCC6<br>1R | MCC6<br>0R |  |  |

|                 | High                                                                         | Туре      | r          | w          |            | r          |            | w          | w          | w          |  |  |

| FA <sub>H</sub> | CCU6_CC60SRL Reset: 00 <sub>H</sub>                                          | Bit Field |            |            |            | CC6        | 60SL       |            |            |            |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 Low                      | Туре      |            |            |            | rv         | vh         |            |            |            |  |  |

| FB <sub>H</sub> | CCU6_CC60SRH Reset: 00 <sub>H</sub>                                          | Bit Field |            |            |            | CC6        | 0SH        |            |            |            |  |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC60 High                     | Туре      |            |            |            | rv         | vh         |            |            |            |  |  |

## 3.2.4.11 UART1 Registers

The UART1 SFRs can be accessed in the mapped memory area (RMAP = 1).

| Addr            | Register Name                                                   | Bit       | 7    | 6   | 5   | 4        | 3    | 2          | 1    | 0    |

|-----------------|-----------------------------------------------------------------|-----------|------|-----|-----|----------|------|------------|------|------|

| RMAP =          | = 1                                                             |           |      |     |     |          |      |            |      |      |

| C8 <sub>H</sub> | SCON Reset: 00 <sub>H</sub>                                     | Bit Field | SM0  | SM1 | SM2 | REN      | TB8  | RB8        | TI   | RI   |

|                 | Serial Channel Control Register                                 | Туре      | rw   | rw  | rw  | rw       | rw   | rwh        | rwh  | rwh  |

| C9 <sub>H</sub> | SBUF Reset: 00 <sub>H</sub>                                     | Bit Field |      |     |     | V        | AL   | •          |      | •    |

|                 | Serial Data Buffer Register                                     | Туре      |      |     |     | rv       | vh   |            |      |      |

| CA <sub>H</sub> | BCON Reset: 00 <sub>H</sub>                                     | Bit Field |      | (   | C   |          |      | BRPRE      | R    |      |

|                 | Baud Rate Control Register                                      | Туре      |      |     | r   |          |      | rw         |      | rw   |

| св <sub>Н</sub> | BG Reset: 00 <sub>H</sub>                                       | Bit Field |      |     |     | BR_VALUE |      |            |      |      |

|                 | Baud Rate Timer/Reload<br>Register                              | Туре      | rwh  |     |     |          |      |            |      |      |

| сс <sub>Н</sub> | Register<br>FDCON Reset: 00 <sub>H</sub>                        | Bit Field |      |     | 0   |          |      | NDOV       | FDM  | FDEN |

|                 | Fractional Divider Control<br>Register                          | Туре      |      |     | r   |          |      | rwh        | rwh  | rw   |

| CD <sub>H</sub> | FDSTEP Reset: 00 <sub>H</sub>                                   | Bit Field |      |     |     | ST       | ΈP   |            |      |      |

|                 | Fractional Divider Reload<br>Register                           | Туре      |      |     |     | r        | w    |            |      |      |

| CeH             | FDRES Reset: 00 <sub>H</sub>                                    | Bit Field |      |     |     | RES      | SULT |            |      |      |

|                 | Fractional Divider Result<br>Register                           | Туре      |      |     |     | r        | h    |            |      |      |

| CF <sub>H</sub> | SCON1 Reset: 07 <sub>H</sub><br>Serial Channel Control Register | Bit Field |      |     | 0   |          |      | NDOV<br>EN | TIEN | RIEN |

|                 | 1                                                               | Туре      | r rw |     |     |          |      | rw         | rw   |      |

#### Table 15 UART1 Register Overview

#### 3.2.4.12 SSC Registers

The SSC SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 16SSC Register Overview

|                 | _                                              |           |    |    |    |      |     |     |     |     |

|-----------------|------------------------------------------------|-----------|----|----|----|------|-----|-----|-----|-----|

| Addr            | Register Name                                  | Bit       | 7  | 6  | 5  | 4    | 3   | 2   | 1   | 0   |

| RMAP =          | 0                                              |           |    |    |    |      |     |     |     |     |

| A9 <sub>H</sub> | SSC_PISEL Reset: 00 <sub>H</sub>               | Bit Field |    | 0  |    |      |     |     | SIS | MIS |

|                 | Port Input Select Register                     | Туре      |    |    | r  |      |     | rw  | rw  | rw  |

| AA <sub>H</sub> | A <sub>H</sub> SSC_CONL Reset: 00 <sub>H</sub> | Bit Field | LB | PO | PH | HB   |     | В   | M   |     |

|                 | Control Register Low<br>Programming Mode       | Туре      | rw | rw | rw | rw   |     | r   | w   |     |

| AA <sub>H</sub> | SSC_CONL Reset: 00 <sub>H</sub>                | Bit Field |    | (  | )  |      |     | В   | С   |     |

|                 | Control Register Low<br>Operating Mode         | Туре      |    |    | r  |      | r   | h   |     |     |

| ab <sub>h</sub> | SSC_CONH Reset: 00 <sub>H</sub>                | Bit Field | EN | MS | 0  | AREN | BEN | PEN | REN | TEN |

|                 | Control Register High<br>Programming Mode      | Туре      | rw | rw | r  | rw   | rw  | rw  | rw  | rw  |

**Table 20** and **Table 21** shows the Flash data retention and endurance targets for Industrial profile and Automotive profile respectively.

# Table 20Flash Data Retention and Endurance for Industrial Profile<br/>(Operating Conditions apply)

| Retention Endurance <sup>1)2)</sup> |                | Size            | Remarks             |  |  |

|-------------------------------------|----------------|-----------------|---------------------|--|--|

| Program Flash                       |                |                 |                     |  |  |

| 15 years                            | 1000 cycles    | up to 60 Kbytes |                     |  |  |

| Data Flash                          | <b>I</b>       |                 |                     |  |  |

| 15 years                            | 1000 cycles    | 4 Kbytes        |                     |  |  |

| 10 years                            | 10,000 cycles  | 4 Kbytes        |                     |  |  |

| 5 years                             | 30,000 cycles  | 4 Kbytes        |                     |  |  |

| 1 year                              | 100,000 cycles | 4 Kbytes        | SAF and SAX variant |  |  |

|                                     | 80,000 cycles  |                 | SAK variant         |  |  |

1) In Program Flash, one cycle refers to the programming of all pages in the flash bank and a mass erase.

2) In Data Flash, one cycle refers to the programming of all wordlines in a page and a page erase.

# Table 21Flash Data Retention and Endurance for Automotive Profile<br/>(Operating Conditions apply)

| Retention     | Endurance <sup>1)2)</sup> | Size            | Remarks |

|---------------|---------------------------|-----------------|---------|

| Program Flash | <b>-</b>                  |                 |         |

| 15 years      | 1000 cycles               | up to 60 Kbytes |         |

| Data Flash    |                           |                 |         |

| 15 years      | 1000 cycles               | 4 Kbytes        |         |

| 5 years       | 10,000 cycles             | 1 Kbytes        |         |

| 2 years       | 15,000 cycles             | 512 Bytes       |         |

| 2 years       | 30,000 cycles             | 256 Bytes       |         |

| 1 year        | 100,000 cycles            | 128 Bytes       |         |

1) In Program Flash, one cycle refers to the programming of all pages in the flash bank and a mass erase.

2) In Data Flash, one cycle refers to the programming of all wordlines in a page and a page erase.

#### 3.12 CORDIC Coprocessor

The CORDIC Coprocessor provides CPU with hardware support for the solving of circular (trigonometric), linear (multiply-add, divide-add) and hyperbolic functions.

#### Features

- Modes of operation

- Supports all CORDIC operating modes for solving circular (trigonometric), linear (multiply-add, divide-add) and hyperbolic functions

- Integrated look-up tables (LUTs) for all operating modes

- Circular vectoring mode: Extended support for values of initial X and Y data up to full range of [-2<sup>15</sup>,(2<sup>15</sup>-1)] for solving angle and magnitude

- Circular rotation mode: Extended support for values of initial Z data up to full range of  $[-2^{15},(2^{15}-1)]$ , representing angles in the range  $[-\pi,((2^{15}-1)/2^{15})\pi]$  for solving trigonometry

- Implementation-dependent operational frequency of up to 80 MHz

- Gated clock input to support disabling of module

- 16-bit accessible data width

- 24-bit kernel data width plus 2 overflow bits for X and Y each

- 20-bit kernel data width plus 1 overflow bit for Z

- With KEEP bit to retain the last value in the kernel register for a new calculation

- 16 iterations per calculation: Approximately 41 clock-cycles or less, from set of start (ST) bit to set of end-of-calculation flag, excluding time taken for write and read access of data bytes.

- Twos complement data processing

- Only exception: X result data with user selectable option for unsigned result

- X and Y data generally accepted as integer or rational number; X and Y must be of the same data form

- Entries of LUTs are 20-bit signed integers

- Entries of atan and atanh LUTs are integer representations (S19) of angles with the scaling such that  $[-2^{15},(2^{15}-1)]$  represents the range  $[-\pi,((2^{15}-1)/2^{15})\pi]$

- Accessible Z result data for circular and hyperbolic functions is integer in data form of S15

- Emulated LUT for linear function

- Data form is 1 integer bit and 15-bit fractional part (1.15)

- Accessible Z result data for linear function is rational number with fixed data form of S4.11 (signed 4Q16)

- Truncation Error

- The result of a CORDIC calculation may return an approximation due to truncation of LSBs

- Good accuracy of the CORDIC calculated result data, especially in circular mode

- Interrupt

- On completion of a calculation

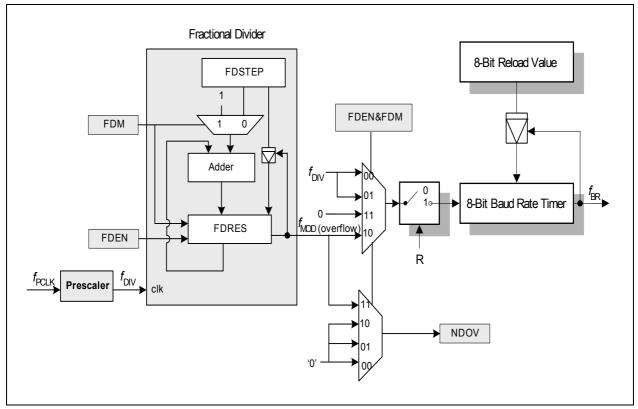

fractional divider) for generating a wide range of baud rates based on its input clock  $f_{\text{PCLK}}$ , see **Figure 26**.

#### Figure 26Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.14**.

The baud rate ( $f_{BR}$ ) value is dependent on the following parameters:

- Input clock  $f_{PCLK}$

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

- 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

| Table 32 Deviation Error for UART with Fractional Divider enabled |                               |                                |                        |                    |  |  |  |  |

|-------------------------------------------------------------------|-------------------------------|--------------------------------|------------------------|--------------------|--|--|--|--|

| f <sub>pclk</sub>                                                 | Prescaling Factor<br>(2BRPRE) | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |  |  |  |  |

| 24 MHz                                                            | 1                             | 6 (6 <sub>H</sub> )            | 59 (3B <sub>H</sub> )  | +0.03 %            |  |  |  |  |

| 12 MHz                                                            | 1                             | 3 (3 <sub>H</sub> )            | 59 (3B <sub>H</sub> )  | +0.03 %            |  |  |  |  |

| 8 MHz                                                             | 1                             | 2 (2 <sub>H</sub> )            | 59 (3B <sub>H</sub> )  | +0.03 %            |  |  |  |  |

| 6 MHz                                                             | 1                             | 6 (6 <sub>H</sub> )            | 236 (EC <sub>H</sub> ) | +0.03 %            |  |  |  |  |

#### Table 32 Deviation Error for UART with Fractional Divider enabled

#### 3.13.2 Baud Rate Generation using Timer 1

In UART modes 1 and 3 of UART module, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

Mode 1, 3 baud rate=

$$\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$$

(3.6)

#### 3.14 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see **Figure 26**). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock  $f_{MOD}$  that is 1/n of the input clock  $f_{DIV}$ , where n is defined by 256 - STEP. The output frequency in normal divider mode is derived as follows:

$$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$$

(3.7)

## XC87xCLM

**Functional Description**

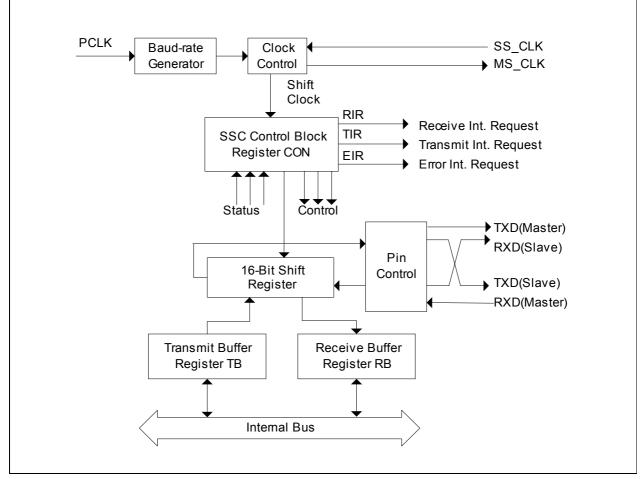

Figure 28 SSC Block Diagram

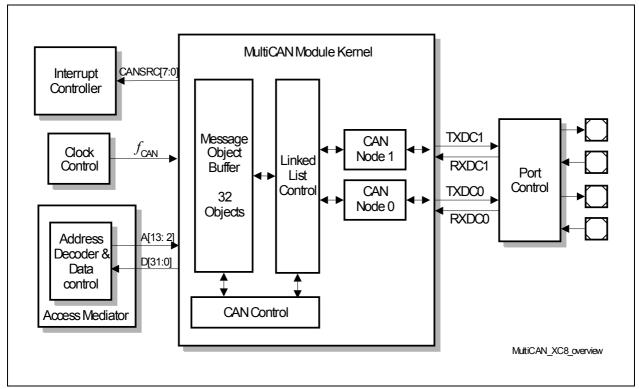

## 3.21 Controller Area Network (MultiCAN)

The MultiCAN module contains two Full-CAN nodes operating independently or exchanging data and remote frames via a gateway function. Transmission and reception of CAN frames is handled in accordance to CAN specification V2.0 B active. Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

Both CAN nodes share a common set of message objects, where each message object may be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects may be combined to build gateways between the CAN nodes or to setup a FIFO buffer.

The message objects are organized in double chained lists, where each CAN node has it's own list of message objects. A CAN node stores frames only into message objects that are allocated to the list of the CAN node. It only transmits messages from objects of this list. A powerful, command driven list controller performs all list operations.

The bit timings for the CAN nodes are derived from the peripheral clock ( $f_{CAN}$ ) and are programmable up to a data rate of 1 MBaud. A pair of receive and transmit pins connects each CAN node to a bus transceiver.

Figure 30 Overview of the MultiCAN

#### Features

Compliant to ISO 11898.

- CAN functionality according to CAN specification V2.0 B active.

- Dedicated control registers are provided for each CAN node.

- A data transfer rate up to 1 MBaud is supported.

- Flexible and powerful message transfer control and error handling capabilities are implemented.

- Advanced CAN bus bit timing analysis and baud rate detection can be performed for each CAN node via the frame counter.

- Full-CAN functionality: A set of 32 message objects can be individually

- allocated (assigned) to any CAN node

- configured as transmit or receive object

- setup to handle frames with 11-bit or 29-bit identifier

- counted or assigned a timestamp via a frame counter

- configured to remote monitoring mode

- Advanced Acceptance Filtering:

- Each message object provides an individual acceptance mask to filter incoming frames.

- A message object can be configured to accept only standard or only extended frames or to accept both standard and extended frames.

- Message objects can be grouped into 4 priority classes.

- The selection of the message to be transmitted first can be performed on the basis of frame identifier, IDE bit and RTR bit according to CAN arbitration rules.

- Advanced Message Object Functionality:

- Message Objects can be combined to build FIFO message buffers of arbitrary size, which is only limited by the total number of message objects.

- Message objects can be linked to form a gateway to automatically transfer frames between 2 different CAN buses. A single gateway can link any two CAN nodes. An arbitrary number of gateways may be defined.

- Advanced Data Management:

- The Message objects are organized in double chained lists.

- List reorganizations may be performed any time, even during full operation of the CAN nodes.

- A powerful, command driven list controller manages the organization of the list structure and ensures consistency of the list.

- Message FIFOs are based on the list structure and can easily be scaled in size during CAN operation.

- Static Allocation Commands offer compatibility with TwinCAN applications, which are not list based.

- Advanced Interrupt Handling:

- Up to 8 interrupt output lines are available. Most interrupt requests can be individually routed to one of the 8 interrupt output lines.

- Message postprocessing notifications can be flexibly aggregated into a dedicated register field of 64 notification bits.

#### Table 40 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                            | Symbol             |    | Limit Values |      | Unit | Test Conditions |  |

|--------------------------------------------------------------------------------------|--------------------|----|--------------|------|------|-----------------|--|

|                                                                                      |                    |    | min.         | max. |      |                 |  |

| Voltage on any pin during $V_{\text{DDP}}$ power off                                 | V <sub>PO</sub>    | SR | -            | 0.3  | V    | 6)              |  |

| Maximum current per pin (excluding $V_{\text{DDP}}$ and $V_{\text{SS}}$ )            | $I_{\rm M}{ m SR}$ | SR | _            | 8    | mA   |                 |  |

| Maximum current for<br>all pins (excluding<br>$V_{\text{DDP}}$ and $V_{\text{SS}}$ ) | $\Sigma  I_{M} $   | SR | _            | 150  | mA   |                 |  |

| Maximum current into $V_{\text{DDP}}$                                                | I <sub>mvddp</sub> | SR | -            | 200  | mA   | 5)              |  |

| Maximum current out of $V_{SS}$                                                      | I <sub>MVSS</sub>  | SR | -            | 200  | mA   | 5)              |  |

1) DS = 0 refers to the pin having a weak drive strength which is programmable via Px\_DS register.

2) DS = 1 refers to the pin having a strong drive strength which is programmable via Px\_DS register.

3) Not subjected to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

4) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. TMS pin and RESET pin have internal pull devices and are not included in the input leakage current characteristic.

5) Not subjected to production test, verified by design/characterization.

6) Not subjected to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any GPIO pin when  $V_{\text{DDP}}$  is powered off.

7) P0.1 has a minimum input hysteresis of 0.25V.

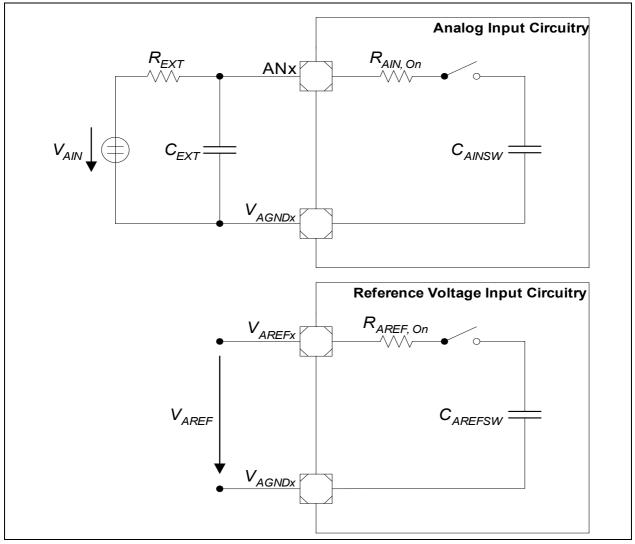

#### Table 42ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

| Parameter                                             | Symbol            |    | Limit Values |      |      | Unit | Test Conditions/ |

|-------------------------------------------------------|-------------------|----|--------------|------|------|------|------------------|

|                                                       |                   |    | min.         | typ. | max. |      | Remarks          |

| Input resistance of the reference input               | R <sub>AREF</sub> | CC | -            | 1    | 2    | kΩ   | 1)               |

| Input resistance of<br>the selected analog<br>channel | R <sub>AIN</sub>  | CC | _            | 1    | 3    | kΩ   | 1)               |

1) Not subjected to production test, verified by design/characterization.

2) This value includes the maximum oscillator deviation.

3) This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

4) The sampling capacity of the conversion C-Network is pre-charged to  $V_{AREF}/2$  before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than  $V_{AREF}/2$ .

Figure 35 ADC Input Circuits

## 4.2.3.1 ADC Conversion Timing

Conversion time,  $t_{\rm C} = t_{\rm ADC} \times (1 + r \times (3 + n + STC))$ , where r = CTC + 2 for CTC =  $00_{\rm B}$ ,  $01_{\rm B}$  or  $10_{\rm B}$ , r = 32 for CTC =  $11_{\rm B}$ , CTC = Conversion Time Control (GLOBCTR.CTC), STC = Sample Time Control (INPCR0.STC), n = 8 or 10 (for 8-bit and 10-bit conversion respectively),  $t_{\rm ADC} = 1 / f_{\rm ADC}$

#### **Electrical Parameters**

| Table 44             | Power Down Current <sup>1)</sup> (Operating Conditions apply; $V_{DDP}$ = 5V range) |                  |                    |                    |                        |                                       |  |

|----------------------|-------------------------------------------------------------------------------------|------------------|--------------------|--------------------|------------------------|---------------------------------------|--|

| Parameter            | ter Symbol Limit Values                                                             |                  | Values             | Unit               | <b>Test Conditions</b> |                                       |  |

|                      |                                                                                     |                  | typ. <sup>2)</sup> | max. <sup>3)</sup> | 1                      |                                       |  |

| $V_{\rm DDP}$ = 5V F | Range                                                                               |                  |                    |                    |                        | ·                                     |  |

| Power-Dowr           | n Mode                                                                              | I <sub>PDP</sub> | 20                 | 80                 | μA                     | $T_{\rm A}$ = + 25 °C <sup>4)5)</sup> |  |

|                      |                                                                                     |                  | -                  | 250                | μA                     | $T_{\rm A}$ = + 85 °C <sup>5)6)</sup> |  |

1) The table is only applicable to SAF and SAX variants. SAK variant does not support power-down mode

2) The typical  $I_{PDP}$  values are based on preliminary measurements and are to be used as reference only. These values are measured at  $V_{\text{DDP}}$  = 5.0 V.

3) The maximum  $I_{PDP}$  values are measured at  $V_{DDP}$  = 5.5 V.

4)  $I_{PDP}$  has a maximum value of 450  $\mu$ A at T<sub>A</sub> = + 105 °C.

5)  $I_{PDP}$  is measured with: RESET =  $V_{DDP}$ ,  $V_{AGND}$ =  $V_{SS}$ , RXD/INT0 =  $V_{DDP}$ ; rest of the ports are programmed to be input with either internal pull devices enabled or driven externally to ensure no floating inputs.

6) Not subjected to production test, verified by design/characterization.

#### 4.3 AC Parameters

The electrical characteristics of the AC Parameters are detailed in this section.

#### 4.3.1 Testing Waveforms

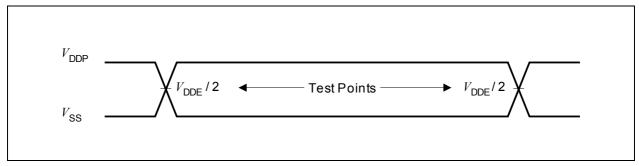

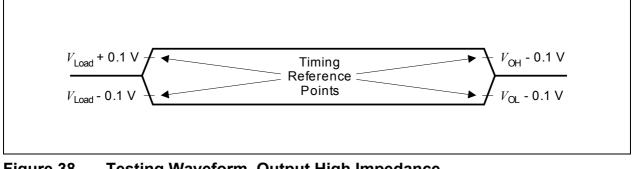

The testing waveforms for rise/fall time, output delay and output high impedance are shown in **Figure 36**, **Figure 37** and **Figure 38**.

Figure 36 Rise/Fall Time Parameters

Figure 37 Testing Waveform, Output Delay

Figure 38 Testing Waveform, Output High Impedance