Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                           |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                              |

| Core Size                  | 8-Bit                                                                              |

| Speed                      | 27MHz                                                                              |

| Connectivity               | CANbus, LINbus, SSI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                              |

| Number of I/O              | 40                                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 3.25K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                        |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-LQFP                                                                            |

| Supplier Device Package    | PG-LQFP-64-4                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc878clm16ffa5vacxxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 8-Bit Single-Chip Microcontroller

#### XC87xCLM

## **1** Summary of Features

The XC87x has the following features:

- High-performance XC800 Core

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- · On-chip memory

- 8 Kbytes of Boot ROM

- 256 bytes of RAM

- 3 Kbytes of XRAM

- 64/52 Kbytes of Flash;

- (includes memory protection strategy)

- I/O port supply at 3.3 V or 5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

(more features on next page)

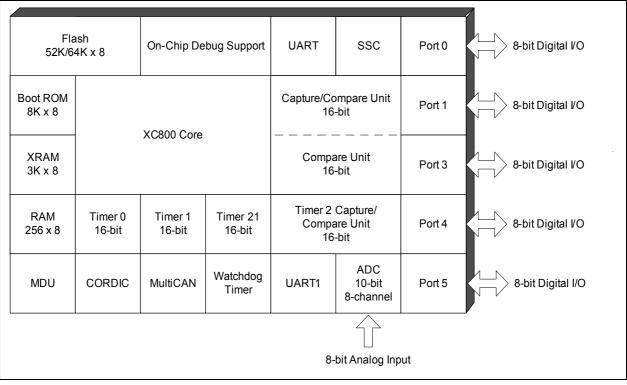

#### Figure 1 XC87x Functional Units

## XC87xCLM

#### **General Device Information**

#### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                                                   |                                                                                               |

|--------|--------------------------------------|------|----------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| P1.5   | 39/30                                |      | PU             | CCPOS0_1<br>EXINT5_0<br>T1_1<br>MRST_2<br>EXF2_0<br>RXDO_0 | •                                                                                             |

| P1.6   | 10/9                                 |      | PU             | CCPOS1_1<br>T12HR_0<br>EXINT6_0<br>RXDC0_2<br>T21_1        | CCU6 Timer 12 Hardware Run<br>Input                                                           |

| P1.7   | 11/10                                |      | PU             | CCPOS2_1<br>T13HR_0<br>T2_1<br>TXDC0_2                     | CCU6 Timer 13 Hardware Run<br>Input<br>Timer 2 Input<br>MultiCAN Node 0 Transmitter<br>Output |

|        |                                      |      |                |                                                            | .6 can be used as a software chip<br>t for the SSC.                                           |

## XC87xCLM

#### **General Device Information**

#### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                                                    |                                                                                                                                                                                                              |

|--------|--------------------------------------|------|----------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.4   | 51/37                                |      | Hi-Z           | CC62_0<br>RXDC0_1<br>T2EX1_0<br>T2CC3_1/<br>EXINT6_3<br>A14 | Input/Output of<br>Capture/Compare channel 2<br>MultiCAN Node 0 Receiver Input<br>Timer 21 External Trigger Input<br>External Interrupt Input 6/T2CCU<br>Capture/Compare Channel 3<br>Address Line 14 Output |

| P3.5   | 52/38                                |      | Hi-Z           | COUT62_0<br>EXF21_0<br>TXDC0_1<br>A15                       | Output of Capture/Compare<br>channel 2<br>Timer 21 External Flag Output<br>MultiCAN Node 0 Transmitter<br>Output<br>Address Line 15 Output                                                                   |

| P3.6   | 41/32                                |      | PU             | CTRAP_0                                                     | CCU6 Trap Input                                                                                                                                                                                              |

| P3.7   | 42/-                                 |      | Hi-Z           | EXINT4_0<br>COUT63_0<br>A16                                 | External Interrupt Input 4<br>Output of Capture/Compare<br>channel 3<br>Address Line 16 Output                                                                                                               |

## XC87xCLM

#### **General Device Information**

#### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                                       |                                                                                                                                              |

|--------|--------------------------------------|------|----------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| P5.5   | 15/-                                 |      | PU             | CCPOS2_0<br>CTRAP_1<br>CC60_3                  | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Input of Capture/Compare<br>channel 0                                                                |

|        |                                      |      |                | TDO_1<br>TXD1_2                                | JTAG Serial Data Output<br>UART1 Transmit Data Output/<br>Clock Output                                                                       |

|        |                                      |      |                | T2CC0_2/<br>EXINT3_3<br>A5                     | External Interrupt Input 3/T2CCU<br>Capture/Compare Channel 0<br>Address Line 5 Output                                                       |

| P5.6   | 19/-                                 |      | PU             | TCK_1<br>RXDO1_2<br>T2CC1_2/<br>EXINT4_3<br>A6 |                                                                                                                                              |

| P5.7   | 20/-                                 |      | PU             | TDI_1<br>RXD1_2<br>T2CC3_2/<br>EXINT6_4<br>A7  | JTAG Serial Data Input<br>UART1 Receive Data Input<br>External Interrupt Input 6/T2CCU<br>Capture/Compare Channel 3<br>Address Line 7 Output |

The page register has the following definition:

#### MOD\_PAGE Page Register for module MOD

Reset Value: 00<sub>H</sub>

| 7 | 6 | 5  | 4  | 3 | 2 | 1    | 0 |

|---|---|----|----|---|---|------|---|

| 0 | Ρ | ST | NR | 0 |   | PAGE |   |

| v | V | V  | V  | r |   | rw   | I |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAGE  | [2:0] | rw   | <b>Page Bits</b><br>When written, the value indicates the new page.<br>When read, the value indicates the currently active<br>page.                                                                                                                                                                                                                                                                                                                                        |

| STNR  | [5:4] | W    | Storage NumberThis number indicates which storage bit field is the<br>target of the operation defined by bit field OP.If $OP = 10_B$ ,<br>the contents of PAGE are saved in STx before being<br>overwritten with the new value.If $OP = 11_B$ ,<br>the contents of PAGE are overwritten by the<br>contents of STx. The value written to the bit positions<br>of PAGE is ignored.00ST0 is selected.<br>0101ST1 is selected.<br>1010ST2 is selected.<br>1111ST3 is selected. |

#### Table 12T2CCU Register Overview (cont'd)

| Addr            | Register Name                                                                        | Bit       | 7           | 6    | 5          | 4          | 3          | 2           | 1          | 0          |

|-----------------|--------------------------------------------------------------------------------------|-----------|-------------|------|------------|------------|------------|-------------|------------|------------|

| C5 <sub>H</sub> | T2CCU_CCTH Reset: 00 <sub>H</sub>                                                    | Bit Field |             | Ι    | Ι          | C          | СТ         |             |            | Ι          |

|                 | T2CCU Capture/Compare<br>Timer Register High                                         | Туре      |             |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CCTCON Reset: 00 <sub>H</sub><br>T2CCU CaptureCcompare                         | Bit Field |             | ССТ  | PRE        |            | CCTO<br>VF | CCTO<br>VEN | TIMSY<br>N | CCTS<br>T  |

|                 | Timer Control Register                                                               | Туре      |             | r    | W          |            | rwh        | rw          | rw         | rw         |

| RMAP =          | 0, PAGE 2                                                                            |           |             |      |            |            |            |             |            |            |

| C0 <sub>H</sub> | <b>T2CCU_COSHDWReset: 00<sub>H</sub></b><br>T2CCU Capture/compare<br>Enable Register | Bit Field | ENSH<br>DW  | TXOV | COOU<br>T5 | COOU<br>T4 | COOU<br>T3 | COOU<br>T2  | COOU<br>T1 | COOU<br>T0 |

|                 |                                                                                      | Туре      | rwh         | rwh  | rwh        | rwh        | rwh        | rwh         | rwh        | rwh        |

| C1 <sub>H</sub> | T2CCU_CC0L Reset: 00 <sub>H</sub><br>T2CCU Capture/Compare                           | Bit Field |             |      |            | CC/        | /ALL       |             |            |            |

|                 | Register 0 Low                                                                       | Туре      |             |      |            | rv         | vh         |             |            |            |

| C2 <sub>H</sub> | T2CCU_CC0H Reset: 00 <sub>H</sub>                                                    | Bit Field |             |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 0 High                                             | Туре      |             |      |            | rv         | vh         |             |            |            |

| C3 <sub>H</sub> | T2CCU_CC1L Reset: 00 <sub>H</sub>                                                    | Bit Field |             |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 1 Low                                              | Туре      |             |      |            | rv         | vh         |             |            |            |

| C4 <sub>H</sub> | T2CCU_CC1H Reset: 00 <sub>H</sub>                                                    | Bit Field |             |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 1 High                                             | Туре      |             |      |            | rv         | vh         |             |            |            |

| C5 <sub>H</sub> | T2CCU_CC2L Reset: 00 <sub>H</sub>                                                    | Bit Field | ield CCVALL |      |            |            |            |             |            |            |

|                 | T2CCU Capture/compare<br>Register 2 Low                                              | Туре      |             |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CC2H Reset: 00 <sub>H</sub>                                                    | Bit Field |             |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 2 High                                             | Туре      |             |      |            | rv         | vh         |             |            |            |

| RMAP =          | 0, PAGE 3                                                                            |           |             |      |            |            |            |             |            |            |

| C0 <sub>H</sub> | T2CCU_COCON Reset: 00 <sub>H</sub><br>T2CCU Compare Control                          | Bit Field | CCM5        | CCM4 | CM5F       | CM4F       | POLB       | POLA        | CON        | NOD        |

|                 | Register                                                                             | Туре      | rw          | rw   | rwh        | rwh        | rw         | rw          | r          | W          |

| C1 <sub>H</sub> | T2CCU_CC3L Reset: 00 <sub>H</sub>                                                    | Bit Field |             |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 3 Low                                              | Туре      |             |      |            | rv         | vh         |             |            |            |

| C2 <sub>H</sub> | T2CCU_CC3H Reset: 00 <sub>H</sub>                                                    | Bit Field |             |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 3 High                                             | Туре      |             |      |            | rv         | vh         |             |            |            |

| C3 <sub>H</sub> | T2CCU_CC4L Reset: 00 <sub>H</sub>                                                    | Bit Field |             |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 4 Low                                              | Туре      |             |      |            | rv         | vh         |             |            |            |

| C4 <sub>H</sub> | T2CCU_CC4H Reset: 00 <sub>H</sub>                                                    | Bit Field | eld CCVALH  |      |            |            |            |             |            |            |

|                 | T2CCU Capture/compare<br>Register 4 High                                             | Туре      | rwh         |      |            |            |            |             |            |            |

| C5 <sub>H</sub> | T2CCU_CC5L Reset: 00 <sub>H</sub>                                                    | Bit Field |             |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 5 Low                                              | Туре      |             |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CC5H Reset: 00 <sub>H</sub>                                                    | Bit Field |             |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 5 High                                             | Туре      |             |      |            | rv         | vh         |             |            |            |

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                         | Bit       | 7      | 6    | 5         | 4    | 3          | 2        | 1        | 0    |  |

|-----------------|-----------------------------------------------------------------------|-----------|--------|------|-----------|------|------------|----------|----------|------|--|

| FC <sub>H</sub> | CCU6_CC61SRL Reset: 00 <sub>H</sub>                                   | Bit Field |        |      |           | CC6  | S1SL       | <u> </u> | <u> </u> |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 Low               | Туре      |        |      |           | rv   | vh         |          |          |      |  |

| FD <sub>H</sub> | CCU6_CC61SRH Reset: 00 <sub>H</sub>                                   | Bit Field |        |      |           | CC6  | 1SH        |          |          |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC61 High              | Туре      | rwh    |      |           |      |            |          |          |      |  |

| FE <sub>H</sub> | CCU6_CC62SRL Reset: 00 <sub>H</sub>                                   | Bit Field | CC62SL |      |           |      |            |          |          |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 Low               | Туре      | rwh    |      |           |      |            |          |          |      |  |

| FF <sub>H</sub> | CCU6_CC62SRH Reset: 00 <sub>H</sub>                                   | Bit Field |        |      |           | CC6  | 2SH        |          |          |      |  |

|                 | Capture/Compare Shadow Register<br>for Channel CC62 High              | Туре      |        |      |           | rv   | vh         |          |          |      |  |

| RMAP =          | = 0, PAGE 1                                                           |           |        |      |           |      |            |          |          |      |  |

| 9A <sub>H</sub> | CCU6_CC63RL Reset: 00 <sub>H</sub>                                    | Bit Field |        |      |           | CC6  | 3VL        |          |          |      |  |

|                 | Capture/Compare Register for<br>Channel CC63 Low                      | Туре      |        |      |           | r    | h          |          |          |      |  |

| 9в <sub>Н</sub> | CCU6_CC63RH Reset: 00 <sub>H</sub>                                    | Bit Field |        |      |           | CC6  | 3VH        |          |          |      |  |

|                 | Capture/Compare Register for<br>Channel CC63 High                     | Туре      |        |      |           | r    | h          |          |          |      |  |

| 9CH             | CCU6_T12PRL Reset: 00 <sub>H</sub>                                    | Bit Field |        |      |           | T12  | PVL        |          |          |      |  |

|                 | Timer T12 Period Register Low                                         | Туре      | rwh    |      |           |      |            |          |          |      |  |

| 9D <sub>H</sub> | CCU6_T12PRH Reset: 00 <sub>H</sub>                                    | Bit Field |        |      |           | T12  | PVH        |          |          |      |  |

|                 | Timer T12 Period Register High                                        | Туре      | rwh    |      |           |      |            |          |          |      |  |

| 9E <sub>H</sub> | CCU6_T13PRL Reset: 00 <sub>H</sub><br>Timer T13 Period Register Low   | Bit Field |        |      |           | T13  | PVL        |          |          |      |  |

|                 |                                                                       | Туре      | rwh    |      |           |      |            |          |          |      |  |

| 9F <sub>H</sub> | CCU6_T13PRH Reset: 00 <sub>H</sub><br>Timer T13 Period Register High  | Bit Field |        |      |           | T13  | PVH        |          |          |      |  |

|                 |                                                                       | Туре      |        |      |           | rv   | vh         |          |          |      |  |

| A4 <sub>H</sub> | CCU6_T12DTCL Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field |        |      |           | D    | ΓM         |          |          |      |  |

|                 | Timer T12 Low                                                         | Туре      |        |      |           | r    | N          | 1        | 1        |      |  |

| A5 <sub>H</sub> | CCU6_T12DTCH Reset: 00 <sub>H</sub><br>Dead-Time Control Register for | Bit Field | 0      | DTR2 | DTR1      | DTR0 | 0          | DTE2     | DTE1     | DTE0 |  |

|                 | Timer T12 High                                                        | Туре      | r      | rh   | rh        | rh   | r          | rw       | rw       | rw   |  |

| A6 <sub>H</sub> | CCU6_TCTR0L Reset: 00 <sub>H</sub><br>Timer Control Register 0 Low    | Bit Field | СТМ    | CDIR | STE1<br>2 | T12R | T12<br>PRE |          | T12CLK   |      |  |

|                 |                                                                       | Туре      | rw     | rh   | rh        | rh   | rw         |          | rw       |      |  |

| а7 <sub>Н</sub> | CCU6_TCTR0H Reset: 00 <sub>H</sub><br>Timer Control Register 0 High   | Bit Field |        | 0    | STE1<br>3 | T13R | T13<br>PRE |          | T13CLK   |      |  |

|                 |                                                                       | Туре      |        | r    | rh        | rh   | rw         |          | rw       |      |  |

| FA <sub>H</sub> | CCU6_CC60RL Reset: 00 <sub>H</sub>                                    | Bit Field |        |      |           | CC6  | 60VL       |          |          |      |  |

|                 | Capture/Compare Register for<br>Channel CC60 Low                      | Туре      |        |      |           | r    | h          |          |          |      |  |

| FB <sub>H</sub> | CCU6_CC60RH Reset: 00 <sub>H</sub>                                    | Bit Field |        |      |           | CC6  | 60VH       |          |          |      |  |

|                 | Capture/Compare Register for<br>Channel CC60 High                     | Туре      |        |      |           | r    | h          |          |          |      |  |

| FC <sub>H</sub> | CCU6_CC61RL Reset: 00 <sub>H</sub>                                    | Bit Field |        |      |           | CC6  | 51VL       |          |          |      |  |

|                 | Capture/Compare Register for<br>Channel CC61 Low                      | Туре      |        |      |           | r    | h          |          |          |      |  |

## 3.2.4.15 Flash Registers

The Flash SFRs can be accessed in the mapped memory area (RMAP = 1).

| Addr            | Register Name                                                           | Bit       | 7        | 6         | 5    | 4    | 3          | 2          | 1         | 0           |

|-----------------|-------------------------------------------------------------------------|-----------|----------|-----------|------|------|------------|------------|-----------|-------------|

| RMAP =          | = 1                                                                     |           |          |           |      |      |            |            |           |             |

| D1 <sub>H</sub> | FCON Reset: 10 <sub>H</sub><br>P-Flash Control Register                 | Bit Field | 0        | FBSY      | YE   | 1    | NVST<br>R  | MAS1       | ERAS<br>E | PROG        |

|                 |                                                                         | Туре      | r        | rh        | rwh  | r    | rw         | rw         | rw        | rw          |

| D2 <sub>H</sub> | EECON Reset: 10 <sub>H</sub><br>D-Flash Control Register                | Bit Field | 0        | EEBS<br>Y | YE   | 1    | NVST<br>R  | MAS1       | ERAS<br>E | PROG        |

|                 |                                                                         | Туре      | r        | rh        | rwh  | r    | rw         | rw         | rw        | rw          |

| D3 <sub>H</sub> | FCS Reset: 80 <sub>H</sub><br>Flash Control and Status                  | Bit Field | 1        | SBEIE     | FTEN | 0    | EEDE<br>RR | EESE<br>RR | FDER<br>R | FSER<br>R   |

|                 | Register                                                                | Туре      | r        | rw        | rwh  | r    | rwh        | rwh        | rwh       | rwh         |

| D4 <sub>H</sub> | FEAL Reset: 00 <sub>H</sub>                                             | Bit Field | ECCEADDR |           |      |      |            |            |           |             |

|                 | Flash Error Address Register,<br>Low Byte                               | Туре      | rh       |           |      |      |            |            |           |             |

| D5 <sub>H</sub> | FEAH Reset: 00 <sub>H</sub>                                             | Bit Field |          |           |      | ECCE | ADDR       |            |           |             |

|                 | Flash Error Address Register,<br>High Byte                              | Туре      |          |           |      | r    | h          |            |           |             |

| D6 <sub>H</sub> | FTVAL Reset: 78 <sub>H</sub>                                            | Bit Field | MODE     |           |      |      | OFVAL      |            |           |             |

|                 | Flash Timer Value Register                                              | Туре      | rw rw    |           |      |      |            |            |           |             |

| dd <sub>H</sub> | DD <sub>H</sub> FCS1 Reset: 00 <sub>H</sub><br>Flash Control and Status |           |          |           |      | 0    |            |            |           | EEAB<br>ORT |

|                 | Register 1                                                              | Туре      |          |           |      | r    |            |            |           | rwh         |

#### Table 19Flash Register Overview

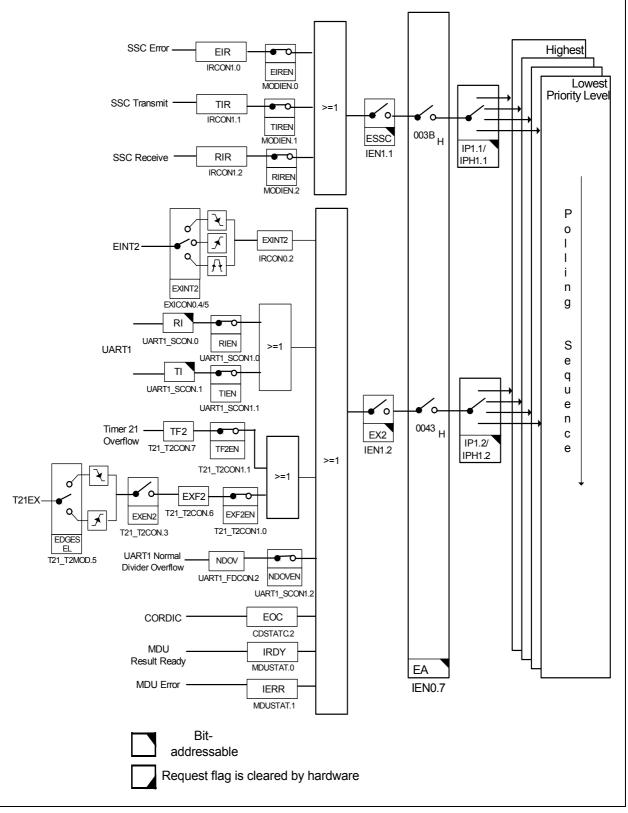

Figure 15 Interrupt Request Sources (Part 3)

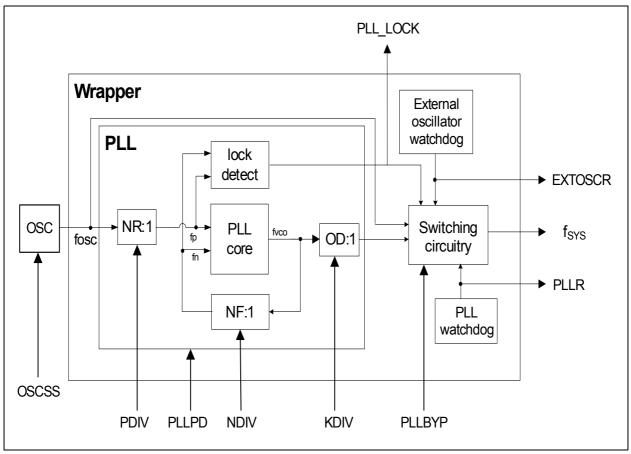

Figure 20 CGU Block Diagram

#### **Direct Drive (PLL Bypass Operation)**

During PLL bypass operation, the system clock has the same frequency as the external clock source.

(3.1)

$$f_{SYS} = f_{OSC}$$

#### PLL Mode

The CPU clock is derived from the oscillator clock, divided by the NR factor (PDIV), multiplied by the NF factor (NDIV), and divided by the OD factor (KDIV). PLL output must

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert FNMIWDT) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value ( $\langle WDTREL \rangle * 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- The input frequency to the WDT can be selected to be either  $f_{\rm PCLK}/2$  or  $f_{\rm PCLK}/128$

- The reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{\rm WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1 + WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

(3.3)

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{\rm WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 25**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB cannot be smaller than WDTREL.

#### 3.12 CORDIC Coprocessor

The CORDIC Coprocessor provides CPU with hardware support for the solving of circular (trigonometric), linear (multiply-add, divide-add) and hyperbolic functions.

#### Features

- Modes of operation

- Supports all CORDIC operating modes for solving circular (trigonometric), linear (multiply-add, divide-add) and hyperbolic functions

- Integrated look-up tables (LUTs) for all operating modes

- Circular vectoring mode: Extended support for values of initial X and Y data up to full range of [-2<sup>15</sup>,(2<sup>15</sup>-1)] for solving angle and magnitude

- Circular rotation mode: Extended support for values of initial Z data up to full range of  $[-2^{15},(2^{15}-1)]$ , representing angles in the range  $[-\pi,((2^{15}-1)/2^{15})\pi]$  for solving trigonometry

- Implementation-dependent operational frequency of up to 80 MHz

- Gated clock input to support disabling of module

- 16-bit accessible data width

- 24-bit kernel data width plus 2 overflow bits for X and Y each

- 20-bit kernel data width plus 1 overflow bit for Z

- With KEEP bit to retain the last value in the kernel register for a new calculation

- 16 iterations per calculation: Approximately 41 clock-cycles or less, from set of start (ST) bit to set of end-of-calculation flag, excluding time taken for write and read access of data bytes.

- Twos complement data processing

- Only exception: X result data with user selectable option for unsigned result

- X and Y data generally accepted as integer or rational number; X and Y must be of the same data form

- Entries of LUTs are 20-bit signed integers

- Entries of atan and atanh LUTs are integer representations (S19) of angles with the scaling such that  $[-2^{15},(2^{15}-1)]$  represents the range  $[-\pi,((2^{15}-1)/2^{15})\pi]$

- Accessible Z result data for circular and hyperbolic functions is integer in data form of S15

- Emulated LUT for linear function

- Data form is 1 integer bit and 15-bit fractional part (1.15)

- Accessible Z result data for linear function is rational number with fixed data form of S4.11 (signed 4Q16)

- Truncation Error

- The result of a CORDIC calculation may return an approximation due to truncation of LSBs

- Good accuracy of the CORDIC calculated result data, especially in circular mode

- Interrupt

- On completion of a calculation

- CAN functionality according to CAN specification V2.0 B active.

- Dedicated control registers are provided for each CAN node.

- A data transfer rate up to 1 MBaud is supported.

- Flexible and powerful message transfer control and error handling capabilities are implemented.

- Advanced CAN bus bit timing analysis and baud rate detection can be performed for each CAN node via the frame counter.

- Full-CAN functionality: A set of 32 message objects can be individually

- allocated (assigned) to any CAN node

- configured as transmit or receive object

- setup to handle frames with 11-bit or 29-bit identifier

- counted or assigned a timestamp via a frame counter

- configured to remote monitoring mode

- Advanced Acceptance Filtering:

- Each message object provides an individual acceptance mask to filter incoming frames.

- A message object can be configured to accept only standard or only extended frames or to accept both standard and extended frames.

- Message objects can be grouped into 4 priority classes.

- The selection of the message to be transmitted first can be performed on the basis of frame identifier, IDE bit and RTR bit according to CAN arbitration rules.

- Advanced Message Object Functionality:

- Message Objects can be combined to build FIFO message buffers of arbitrary size, which is only limited by the total number of message objects.

- Message objects can be linked to form a gateway to automatically transfer frames between 2 different CAN buses. A single gateway can link any two CAN nodes. An arbitrary number of gateways may be defined.

- Advanced Data Management:

- The Message objects are organized in double chained lists.

- List reorganizations may be performed any time, even during full operation of the CAN nodes.

- A powerful, command driven list controller manages the organization of the list structure and ensures consistency of the list.

- Message FIFOs are based on the list structure and can easily be scaled in size during CAN operation.

- Static Allocation Commands offer compatibility with TwinCAN applications, which are not list based.

- Advanced Interrupt Handling:

- Up to 8 interrupt output lines are available. Most interrupt requests can be individually routed to one of the 8 interrupt output lines.

- Message postprocessing notifications can be flexibly aggregated into a dedicated register field of 64 notification bits.

#### 3.24 Chip Identification Number

The XC87x identity (ID) register is located at Page 1 of address  $B3_{H}$ . The value of ID register is  $49_{H}$ . However, for easy identification of product variants, the Chip Identification Number, which is an unique number assigned to each product variant, is available. The differentiation is based on the product, variant type and device step information.

Two methods are provided to read a device's chip identification number:

- In-application subroutine, GET\_CHIP\_INFO

- Bootstrap loader (BSL) mode A

Table 37 lists the chip identification numbers of available XC87x Flash device variants.

| Product Variant  | Chip Identification Number |

|------------------|----------------------------|

|                  | AC-step                    |

| Flash Devices    |                            |

| XC878-16FF 5V    | 4B580063 <sub>H</sub>      |

| XC878M-16FF 5V   | 4B580023 <sub>H</sub>      |

| XC878CM-16FF 5V  | 4B580003 <sub>H</sub>      |

| XC878LM-16FF 5V  | 4B500023 <sub>H</sub>      |

| XC878CLM-16FF 5V | 4B500003 <sub>H</sub>      |

| XC878-13FF 5V    | 4B590463 <sub>H</sub>      |

| XC878M-13FF 5V   | 4B590423 <sub>H</sub>      |

| XC878CM-13FF 5V  | 4B590403 <sub>H</sub>      |

| XC878LM-13FF 5V  | 4B510423 <sub>H</sub>      |

| XC878CLM-13FF 5V | 4B510403 <sub>H</sub>      |

| XC878-16FF 3V3   | 4B180063 <sub>H</sub>      |

| XC878M-16FF 3V3  | 4B180023 <sub>H</sub>      |

| XC878CM-16FF 3V3 | 4B180003 <sub>H</sub>      |

| XC878-13FF 3V3   | 4B190463 <sub>H</sub>      |

| XC878M-13FF 3V3  | 4B190423 <sub>H</sub>      |

| XC878CM-13FF 3V3 | 4B190403 <sub>H</sub>      |

| XC874CM-16FV 5V  | 4B580002 <sub>H</sub>      |

| XC874LM-16FV 5V  | 4B500022 <sub>H</sub>      |

| XC874-16FV 5V    | 4B580062 <sub>H</sub>      |

Table 37

Chip Identification Number

#### **Electrical Parameters**

#### 4.2.3 ADC Characteristics

The values in the table below are given for an analog power supply between 4.5 V to 5.5 V. The ADC can be used with an analog power supply down to 3 V. But in this case, the analog parameters may show a reduced performance. All ground pins ( $V_{\rm SS}$ ) must be externally connected to one single star point in the system. The voltage difference between the ground pins must not exceed 200mV.

| Parameter                                                    | Symbol              |    | Lir                                 | nit Val          | ues                        | Unit | Test Conditions/                                            |  |

|--------------------------------------------------------------|---------------------|----|-------------------------------------|------------------|----------------------------|------|-------------------------------------------------------------|--|

|                                                              |                     |    | min.                                | typ.             | max.                       |      | Remarks                                                     |  |

| Analog reference voltage                                     | V <sub>AREF</sub>   | SR | V <sub>AGND</sub><br>+ 1            | V <sub>DDP</sub> | V <sub>DDP</sub><br>+ 0.05 | V    | 1)                                                          |  |

| Analog reference ground                                      | V <sub>AGND</sub>   | SR | V <sub>SS</sub> -<br>0.05           | V <sub>SS</sub>  | V <sub>AREF</sub><br>- 1   | V    | 1)                                                          |  |

| Analog input<br>voltage range                                | $V_{AIN}$           | SR | $V_{AGND}$                          | -                | V <sub>AREF</sub>          | V    |                                                             |  |

| ADC clocks                                                   | $f_{\rm ADC}$       |    | -                                   | 24               | -                          | MHz  | module clock <sup>1)</sup>                                  |  |

|                                                              | f <sub>adci</sub>   |    | _                                   | -                | 14 <sup>2)</sup>           | MHz  | internal analog clock <sup>1)</sup><br>See <b>Figure 31</b> |  |

| Sample time                                                  | t <sub>S</sub>      | CC | (2 + IN<br><i>t</i> <sub>ADCI</sub> | PCR0.            | STC) ×                     | μS   | 1)                                                          |  |

| Conversion time                                              | t <sub>C</sub>      | CC | See S                               | ection           | 4.2.3.1                    | μs   | 1)                                                          |  |

| Differential<br>Nonlinearity                                 | EA <sub>DNL</sub>   | CC | -                                   | -                | 1.5                        | LSB  | 10-bit conversion                                           |  |

| Integral<br>Nonlinearity                                     | EA <sub>INL</sub>   | CC | -                                   | -                | 2                          | LSB  | 10-bit conversion                                           |  |

| Offset                                                       | $ EA_{OFF} $        | CC | -                                   | _                | 3                          | LSB  | 10-bit conversion                                           |  |

| Gain                                                         | $ EA_{GAIN} $       | CC | -                                   | -                | 2.5                        | LSB  | 10-bit conversion                                           |  |

| Switched<br>capacitance at the<br>reference voltage<br>input | C <sub>AREFSW</sub> | CC | _                                   | 10               | 14                         | pF   | 1)3)                                                        |  |

| Switched<br>capacitance at the<br>analog voltage<br>inputs   | C <sub>AINSW</sub>  | CC | _                                   | 4                | 5                          | pF   | 1)4)                                                        |  |

#### Table 42ADC Characteristics (Operating Conditions apply; $V_{DDP}$ = 5V Range)

#### **Electrical Parameters**

# Table 45Power Supply Current Parameters<sup>1)</sup> (Operating Conditions apply; $V_{\text{DDP}} = 3.3V$ range)

| Parameter                          | Symbol           | Limit              | Values                              | Unit | Test       |  |

|------------------------------------|------------------|--------------------|-------------------------------------|------|------------|--|

|                                    |                  | typ. <sup>2)</sup> | p. <sup>2)</sup> max. <sup>3)</sup> |      | Conditions |  |

| $V_{\text{DDP}}$ = 3.3V Range      |                  |                    |                                     |      |            |  |

| Active Mode                        | I <sub>DDP</sub> | 35.4               | 43                                  | mA   | 4)         |  |

| Idle Mode                          | I <sub>DDP</sub> | 27.6               | 33                                  | mA   | 5)         |  |

| Active Mode with slow-down enabled | I <sub>DDP</sub> | 8.6                | 13                                  | mA   | 6)         |  |

| Idle Mode with slow-down enabled   | I <sub>DDP</sub> | 8                  | 12                                  | mA   | 7)         |  |

1) The table is only applicable to SAF and SAX variants.

2) The typical  $I_{\text{DDP}}$  values are based on preliminary measurements and are to be used as reference only. These values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 3.3 V.

3) The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 105 °C and  $V_{\text{DDP}}$  = 3.6 V).

4)  $I_{\text{DDP}}$  (active mode) is measured with: CPU clock and input clock to all peripherals running at 24 MHz with onchip oscillator of 4 MHz, RESET =  $V_{\text{DDP}}$ ; all other pins are disconnected, no load on ports.

5)  $I_{\text{DDP}}$  (idle mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 24 MHz, RESET =  $V_{\text{DDP}}$ ; all other pins are disconnected, no load on ports.

- 6)  $I_{\text{DDP}}$  (active mode with slow-down mode) is measured with: CPU clock and input clock to all peripherals running at 1 MHz by setting CLKREL in CMCON to  $1000_{\text{B}}$ ,  $\overline{\text{RESET}} = V_{\text{DDP}}$ ; all other pins are disconnected, no load on ports.

- 7)  $I_{\text{DDP}}$  (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 1 MHz by setting CLKREL in CMCON to  $1000_{\text{B}}$ , RESET =  $V_{\text{DDP}}$ ; all other pins are disconnected, no load on ports.

#### **Electrical Parameters**

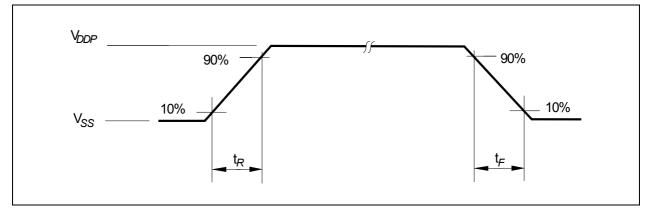

#### 4.3.2 Output Rise/Fall Times

Table 47 provides the characteristics of the output rise/fall times in the XC87x.

#### Table 47 Output Rise/Fall Times Parameters (Operating Conditions apply)

| -                             |                                 |                 |        | • •  |                           |

|-------------------------------|---------------------------------|-----------------|--------|------|---------------------------|

| Parameter                     | Symbol                          | Limit<br>Values |        | Unit | Test Conditions           |

|                               |                                 | min.            | max.   |      |                           |

| $V_{\rm DDP}$ = 5V Range      |                                 |                 |        | •    |                           |

| Rise/fall times               | t <sub>R</sub> , t <sub>F</sub> | -               | 10     | ns   | 20 pF. <sup>1) 2)3)</sup> |

| $V_{\text{DDP}}$ = 3.3V Range |                                 |                 |        |      | ·                         |

| Rise/fall times               | t <sub>R</sub> , t <sub>F</sub> | -               | 10     | ns   | 20 pF. <sup>1) 2)4)</sup> |

|                               |                                 | 1 400/          | 000/ 5 |      |                           |

1) Rise/Fall time measurements are taken with 10% - 90% of pad supply.

2) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

3) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF - 100pF @ 0.125 ns/pF.

4) Additional rise/fall time valid for  $C_{\rm L}$  = 20pF - 100pF @ 0.225 ns/pF.

Figure 39 Rise/Fall Times Parameters

#### Package and Quality Declaration

# 5 Package and Quality Declaration

Chapter 5 provides the information of the XC87x package and reliability section.

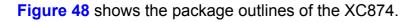

#### 5.1 Package Parameters

Table 56 provides the thermal characteristics of the package used in XC878 and XC874.

| Parameter                                      | Symbol             |      | Lim       | nit Values | Unit | Notes |

|------------------------------------------------|--------------------|------|-----------|------------|------|-------|

|                                                |                    |      | Min. Max. |            |      |       |

| PG-LQFP-64-4 (XC878)                           | 1                  |      |           |            |      |       |

| Thermal resistance junction case <sup>1)</sup> | R <sub>TJC</sub> C | CC - |           | 13.8       | K/W  | -     |

| Thermal resistance junction lead <sup>1)</sup> | $R_{\rm TJL}$ C    | CC - |           | 34.6       | K/W  | -     |

| PG-VQFN-48-22 (XC874)                          |                    | ľ    |           |            |      |       |

| Thermal resistance junction case <sup>1)</sup> | R <sub>TJC</sub> C | CC - |           | 16.6       | K/W  | -     |

| Thermal resistance junction lead <sup>1)</sup> | R <sub>TJL</sub> C | CC - |           | 30.7       | K/W  | -     |

#### Table 56 Thermal Characteristics of the Packages

1) The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  are to be combined with the thermal resistances between the junction and the case  $(R_{TJC})$ , the junction and the lead  $(R_{TJL})$  given above, in order to calculate the total thermal resistance between the junction and the ambient  $(R_{TJA})$ . The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$ . The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  depend on the external system (PCB, case) characteristics, and are under user responsibility.

The junction temperature can be calculated using the following equation:  $T_J = T_A + R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient. This total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by

a) simply adding only the two thermal resistances (junction lead and lead ambient), or

b) by taking all four resistances into account, depending on the precision needed.

#### Package and Quality Declaration

Figure 48 PG-VQFN-48-22 Package Outline

www.infineon.com

Published by Infineon Technologies AG