Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product StatusObsoleteCore ProcessorXC800Core Size8-BitSpeed27MHzConnectivityLINbus, SPI, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O40Program Memory Size52KB (52K x 8)Program Memory TypeFLASHEEPROM Size- |                           |                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------|

| Core Size8-BitSpeed27MHzConnectivityLINbus, SPI, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O40Program Memory Size52KB (52K x 8)Program Memory TypeFLASH                                                      | oduct Status              | Obsolete                                                                          |

| Speed27MHzConnectivityLINbus, SPI, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O40Program Memory Size52KB (52K x 8)Program Memory TypeFLASH                                                                    | ore Processor             | XC800                                                                             |

| ConnectivityLINbus, SPI, SSI, UART/USARTPeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O40Program Memory Size52KB (52K x 8)Program Memory TypeFLASH                                                                              | ore Size                  | 8-Bit                                                                             |

| PeripheralsBrown-out Detect/Reset, POR, PWM, WDTNumber of I/O40Program Memory Size52KB (52K x 8)Program Memory TypeFLASH                                                                                                                      | beed                      | 27MHz                                                                             |

| Number of I/O40Program Memory Size52KB (52K x 8)Program Memory TypeFLASH                                                                                                                                                                      | onnectivity               | LINbus, SPI, SSI, UART/USART                                                      |

| Program Memory Size     52KB (52K x 8)       Program Memory Type     FLASH                                                                                                                                                                    | eripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Program Memory Type FLASH                                                                                                                                                                                                                     | umber of I/O              | 40                                                                                |

|                                                                                                                                                                                                                                               | ogram Memory Size         | 52KB (52K x 8)                                                                    |

| EEPROM Size -                                                                                                                                                                                                                                 | ogram Memory Type         | FLASH                                                                             |

|                                                                                                                                                                                                                                               | EPROM Size                | -                                                                                 |

| RAM Size         3.25K x 8                                                                                                                                                                                                                    | AM Size                   | 3.25K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5V                                                                                                                                                                                                         | oltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters     A/D 8x10b                                                                                                                                                                                                                 | ata Converters            | A/D 8x10b                                                                         |

| Oscillator Type Internal                                                                                                                                                                                                                      | scillator Type            | Internal                                                                          |

| Operating Temperature -40°C ~ 105°C (TA)                                                                                                                                                                                                      | perating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type Surface Mount                                                                                                                                                                                                                   | ounting Type              | Surface Mount                                                                     |

| Package / Case 64-LQFP                                                                                                                                                                                                                        | ackage / Case             | 64-LQFP                                                                           |

| Supplier Device Package PG-LQFP-64-4                                                                                                                                                                                                          | upplier Device Package    | PG-LQFP-64-4                                                                      |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/xc878lm13ffa5vacxxuma1                                                                                                                                                | urchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc878lm13ffa5vacxxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 8-Bit

# XC87xCLM

8-Bit Single-Chip Microcontroller

Data Sheet V1.5 2011-03

# Microcontrollers

#### **General Device Information**

#### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                                                        |                                                                                                                                                                                                  |

|--------|--------------------------------------|------|----------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3     |                                      | I/O  |                | I/O port. It ca<br>for CCU6, U/<br>MultiCAN an                  | B-bit bidirectional general purpose<br>an be used as alternate functions<br>ART1, T2CCU, Timer 21,<br>d External Bus Interface.<br>al Bus Interface is not available in<br>4.                    |

| P3.0   | 43/33                                |      | Hi-Z           | CCPOS1_2<br>CC60_0<br>RXDO1_1<br>T2CC0_1/<br>EXINT3_2           | Input/Output of<br>Capture/Compare channel 0<br>UART1 Transmit Data Output                                                                                                                       |

| P3.1   | 44/34                                |      | Hi-Z           | CCPOS0_2<br>CC61_2<br>COUT60_0<br>TXD1_1                        | CCU6 Hall Input 0<br>Input/Output of<br>Capture/Compare channel 1<br>Output of Capture/Compare<br>channel 0<br>UART1 Transmit Data<br>Output/Clock Output                                        |

| P3.2   | 49/35                                |      | Hi-Z           | CCPOS2_2<br>RXDC1_1<br>RXD1_1<br>CC61_0<br>T2CC1_1/<br>EXINT4_2 | CCU6 Hall Input 2<br>MultiCAN Node 1 Receiver Input<br>UART1 Receive Data Input<br>Input/Output of<br>Capture/Compare channel 1<br>External Interrupt Input 4/T2CCU<br>Capture/Compare Channel 1 |

| P3.3   | 50/36                                |      | Hi-Z           | COUT61_0<br>TXDC1_1<br>T2CC2_1/<br>EXINT5_2<br>A13              | Output of Capture/Compare<br>channel 1<br>MultiCAN Node 1 Transmitter<br>Output<br>External Interrupt Input 5/T2CCU<br>Capture/Compare Channel 2<br>Address Line 13 Output                       |

### XC87xCLM

#### **General Device Information**

#### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                                    |                                                                                                                                      |

|--------|--------------------------------------|------|----------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| P4.5   | 46/-                                 |      | Hi-Z           | CCPOS1_3<br>T1_0<br>COUT61_2                | CCU6 Hall Input 1<br>Timer 1 Input<br>Output of Capture/Compare<br>channel 1                                                         |

|        |                                      |      |                | T2CC3_0/<br>EXINT6_2<br>D5                  | External Interrupt Input 6/T2CCU<br>Capture/Compare Channel 3<br>Data Line 5 Input/Output                                            |

| P4.6   | 47/-                                 |      | Hi-Z           | CCPOS2_3<br>T2_0<br>CC62_2<br>T2CC4_0<br>D6 | CCU6 Hall Input 2<br>Timer 2 Input<br>Output of Capture/Compare<br>channel 2<br>Compare Output Channel 4<br>Data Line 6 Input/Output |

| P4.7   | 48/-                                 |      | Hi-Z           | CTRAP_3<br>COUT62_2<br>T2CC5_0<br>D7        |                                                                                                                                      |

## 3 Functional Description

**Chapter 3** provides an overview of the XC87x functional description.

#### 3.1 **Processor Architecture**

The XC87x is based on a high-performance 8-bit Central Processing Unit (CPU) that is compatible with the standard 8051 processor. While the standard 8051 processor is designed around a 12-clock machine cycle, the XC87x CPU uses a 2-clock machine cycle. This allows fast access to ROM or RAM memories without wait state. The instruction set consists of 45% one-byte, 41% two-byte and 14% three-byte instructions.

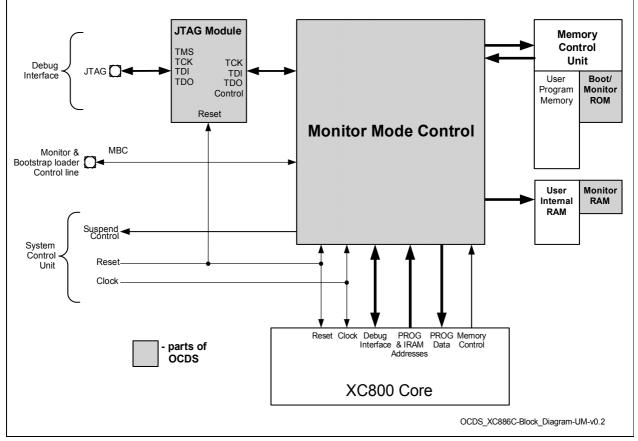

The XC87x CPU provides a range of debugging features, including basic stop/start, single-step execution, breakpoint support and read/write access to the data memory, program memory and Special Function Registers (SFRs).

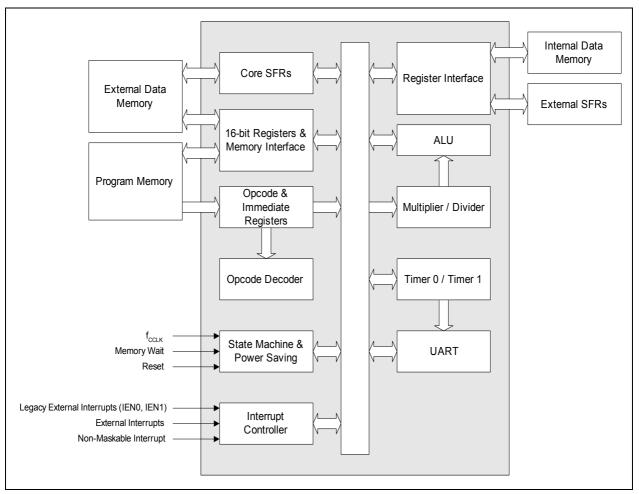

Figure 6 shows the CPU functional blocks.

Figure 6 CPU Block Diagram

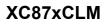

Figure 10 Address Extension by Paging

In order to access a register located in a page different from the actual one, the current page must be exited. This is done by reprogramming the bit field PAGE in the page register. Only then can the desired access be performed.

If an interrupt routine is initiated between the page register access and the module register access, and the interrupt needs to access a register located in another page, the current page setting can be saved, the new one programmed and the old page setting restored. This is possible with the storage fields STx (x = 0 - 3) for the save and restore action of the current page setting. By indicating which storage bit field should be used in parallel with the new page value, a single write operation can:

• Save the contents of PAGE in STx before overwriting with the new value (this is done in the beginning of the interrupt routine to save the current page setting and program the new page number); or

| Table 6 | MDU Register Overview | (cont'd) |

|---------|-----------------------|----------|

|---------|-----------------------|----------|

| Addr            | Register Name                                         | Bit       | 7  | 6  | 5    | 4         | 3   | 2   | 1   | 0 |

|-----------------|-------------------------------------------------------|-----------|----|----|------|-----------|-----|-----|-----|---|

| B1 <sub>H</sub> | MDUCON Reset: 00 <sub>H</sub><br>MDU Control Register | Bit Field | IE | IR | RSEL | STAR<br>T |     | OPC | ODE | I |

|                 |                                                       | Туре      | rw | rw | rw   | rwh       |     | r   | N   |   |

| в2 <sub>Н</sub> | MD0 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Operand Register 0                                | Туре      |    |    |      | r         | W   |     |     |   |

| B2 <sub>H</sub> | MR0 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Result Register 0                                 | Туре      |    |    |      | r         | h   |     |     |   |

| вз <sub>Н</sub> | MD1 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Operand Register 1                                | Туре      |    |    |      | r         | w   |     |     |   |

| вз <sub>Н</sub> | MR1 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Result Register 1                                 | Туре      |    |    |      | r         | h   |     |     |   |

| B4 <sub>H</sub> | MD2 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Operand Register 2                                | Туре      |    |    |      | r         | w   |     |     |   |

| B4 <sub>H</sub> | MR2 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Result Register 2                                 | Туре      |    |    |      | r         | h   |     |     |   |

| в5 <sub>Н</sub> | MD3 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Operand Register 3                                | Туре      |    |    |      | r         | w   |     |     |   |

| в5 <sub>Н</sub> | MR3 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Result Register 3                                 | Туре      |    |    |      | r         | h   |     |     |   |

| в6 <sub>Н</sub> | MD4 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Operand Register 4                                | Туре      |    |    |      | r         | W   |     |     |   |

| в6 <sub>Н</sub> | MR4 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Result Register 4                                 | Туре      |    |    |      | r         | h   |     |     |   |

| в7 <sub>Н</sub> | MD5 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | ATA |     |     |   |

|                 | MDU Operand Register 5                                | Туре      |    |    |      | r         | w   |     |     |   |

| в7 <sub>Н</sub> | MR5 Reset: 00 <sub>H</sub>                            | Bit Field |    |    |      | DA        | TA  |     |     |   |

|                 | MDU Result Register 5                                 | Туре      |    |    |      | r         | h   |     |     |   |

### 3.2.4.3 CORDIC Registers

The CORDIC SFRs can be accessed in the mapped memory area (RMAP = 1).

#### Table 7 CORDIC Register Overview

| Addr            | Register Name                    | Bit       | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 |

|-----------------|----------------------------------|-----------|---|---|---|----|-----|---|---|---|

| RMAP =          | : 1                              |           |   |   |   |    |     |   |   |   |

| 9A <sub>H</sub> | CD_CORDXL Reset: 00 <sub>H</sub> | Bit Field |   |   |   | DA | TAL |   |   |   |

|                 | CORDIC X Data Low Byte           | Туре      |   |   |   | r  | W   |   |   |   |

| 9B <sub>H</sub> | CD_CORDXH Reset: 00 <sub>H</sub> | Bit Field |   |   |   | DA | ТАН |   |   |   |

|                 | CORDIC X Data High Byte          | Туре      |   |   |   | r  | W   |   |   |   |

#### Table 8SCU Register Overview (cont'd)

| Addr            | Register Name                                                              | Bit       | 7                   | 6                   | 5           | 4               | 3          | 2             | 1             | 0            |

|-----------------|----------------------------------------------------------------------------|-----------|---------------------|---------------------|-------------|-----------------|------------|---------------|---------------|--------------|

| вв <sub>Н</sub> | PASSWD Reset: 07 <sub>H</sub><br>Password Register                         | Bit Field |                     |                     | PASS        |                 |            | PROT<br>ECT_S | МС            | DE           |

|                 |                                                                            | Туре      |                     |                     | W           |                 |            | rh            | r             | w            |

| BE <sub>H</sub> | COCON Reset: 00 <sub>H</sub>                                               | Bit Field | CO                  | UTS                 | TLEN        | 0               |            | CO            | REL           |              |

|                 | Clock Output Control Register                                              | Туре      | r                   | W                   | rw          | r               |            | r             | W             |              |

| E9 <sub>H</sub> | MISC_CON Reset: 00 <sub>H</sub><br>Miscellaneous Control Register          | Bit Field | ADCE<br>TR0_<br>MUX | ADCE<br>TR1_<br>MUX |             |                 | 0          |               |               | DFLAS<br>HEN |

|                 |                                                                            | Туре      | rw                  | rw                  |             |                 | r          |               |               | rwh          |

| EA <sub>H</sub> | PLL_CON1 Reset: 20 <sub>H</sub>                                            | Bit Field |                     | NDIV                |             |                 |            | PDIV          |               |              |

|                 | PLL Control Register 1                                                     | Туре      |                     | rw                  |             |                 |            | rw            |               |              |

| EB <sub>H</sub> | CR_MISC Reset: 00 <sub>H</sub> or 01 <sub>H</sub><br>Reset Status Register | Bit Field | CCCF<br>G           | MDUC<br>CFG         | CCUC<br>CFG | T2CCF<br>G      |            | 0             |               | HDRS<br>T    |

|                 |                                                                            | Туре      | rw                  | rw                  | rw          | rw              |            | r             |               | rwh          |

| RMAP =          | = 0, PAGE 3                                                                |           |                     |                     |             |                 |            |               |               |              |

| вз <sub>Н</sub> | XADDRH Reset: F0 <sub>H</sub>                                              | Bit Field |                     |                     |             | ADI             | ORH        |               |               |              |

|                 | On-chip XRAM Address Higher<br>Order                                       | Туре      |                     |                     |             | r               | W          |               |               |              |

| B4 <sub>H</sub> | IRCON3 Reset: 00 <sub>H</sub><br>Interrupt Request Register 3              | Bit Field | (                   | 0                   | CANS<br>RC5 | CCU6<br>SR1     | (          | )             | CANS<br>RC4   | CCU6<br>SR0  |

|                 |                                                                            | Туре      |                     | r                   | rwh         | rwh             |            | r             | rwh           | rwh          |

| в5 <sub>Н</sub> | IRCON4 Reset: 00 <sub>H</sub><br>Interrupt Request Register 4              | Bit Field | (                   | 0                   | CANS<br>RC7 | CCU6<br>SR3     | 0          |               | CANS<br>RC6   | CCU6<br>SR2  |

|                 |                                                                            | Туре      |                     | r                   | rwh         | rwh             |            | r             | rwh           | rwh          |

| в6 <sub>Н</sub> | MODIEN Reset: 07 <sub>H</sub><br>Peripheral Interrupt Enable<br>Register   | Bit Field |                     | 0                   |             | CM5E<br>N       | CM4E<br>N  | RIREN         | TIREN         | EIREN        |

|                 | Register                                                                   | Туре      |                     | r                   |             | rw              | rw         | rw            | rw            | rw           |

| в7 <sub>Н</sub> | MODPISEL1 Reset: 00 <sub>H</sub><br>Peripheral Input Select Register       | Bit Field |                     | EXINT6IS            | 3           | UR <sup>2</sup> | IRIS       | T21EX<br>IS   | (             | 0            |

|                 | 1                                                                          | Туре      |                     | rw                  |             | r               | w          | rw            |               | r            |

| ва <sub>Н</sub> | MODPISEL2 Reset: 00 <sub>H</sub><br>Peripheral Input Select Register       | Bit Field |                     | 0                   |             | T2EXI<br>S      | T21IS      | T2IS          | T1IS          | TOIS         |

|                 | 2                                                                          | Туре      |                     | r                   |             | rw              | rw         | rw            | rw            | rw           |

| вв <sub>Н</sub> | PMCON2 Reset: 00 <sub>H</sub><br>Power Mode Control Register 2             | Bit Field |                     |                     |             | 0               |            |               | UART<br>1_DIS | T21_D<br>IS  |

|                 |                                                                            | Туре      |                     |                     |             | r               |            |               | rw            | rw           |

| вd <sub>Н</sub> | MODSUSP Reset: 01 <sub>H</sub><br>Module Suspend Control<br>Register       | Bit Field | (                   | 0                   | CCTS<br>USP | T21SU<br>SP     | T2SUS<br>P | T13SU<br>SP   | T12SU<br>SP   | WDTS<br>USP  |

|                 | Register                                                                   | Туре      |                     | r                   | rw          | rw              | rw         | rw            | rw            | rw           |

| ве <sub>Н</sub> | MODPISEL3 Reset: 00 <sub>H</sub><br>Peripheral Input Select Register       | Bit Field | 0                   |                     | С           | IS              | S          | IS            | М             | IS           |

|                 | 3                                                                          | Туре      |                     | r                   | r           | w               | / rw       |               | rw            |              |

| EA <sub>H</sub> | MODPISEL4 Reset: 00 <sub>H</sub>                                           | Bit Field | (                   | 0                   | EXIN        | NT5IS           | EXINT4IS   |               | EXINT3IS      |              |

|                 | Peripheral Input Select Register 4                                         | Туре      |                     | r                   | r           | w               | r          | w             | r             | w            |

#### 3.2.4.5 WDT Registers

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

| Addr            | Register Name                                           | Bit       | 7 | 6 | 5          | 4         | 3    | 2         | 1         | 0         |

|-----------------|---------------------------------------------------------|-----------|---|---|------------|-----------|------|-----------|-----------|-----------|

| RMAP =          | = 1                                                     |           |   |   |            | •         |      |           |           |           |

| вв <sub>Н</sub> | WDTCON Reset: 00 <sub>H</sub><br>Watchdog Timer Control | Bit Field |   | 0 | WINB<br>EN | WDTP<br>R | 0    | WDTE<br>N | WDTR<br>S | WDTI<br>N |

|                 | Register                                                | Туре      |   | r | rw         | rh        | r    | rw        | rwh       | rw        |

| вс <sub>Н</sub> | WDTREL Reset: 00 <sub>H</sub>                           | Bit Field |   |   |            | WD1       | REL  |           |           |           |

|                 | Watchdog Timer Reload<br>Register                       | Туре      |   |   |            | r         | w    |           |           |           |

| вd <sub>Н</sub> | WDTWINB Reset: 00 <sub>H</sub>                          | Bit Field |   |   |            | WDT       | WINB |           |           |           |

|                 | Watchdog Window-Boundary<br>Count Register              | Туре      |   |   |            | r         | w    |           |           |           |

| BE <sub>H</sub> | WDTL Reset: 00 <sub>H</sub>                             | Bit Field |   |   |            | W         | DT   |           |           |           |

|                 | Watchdog Timer Register Low                             | Туре      |   |   |            | r         | h    |           |           |           |

| bf <sub>h</sub> | WDTH Reset: 00 <sub>H</sub>                             | Bit Field |   |   |            | W         | DT   |           |           |           |

|                 | Watchdog Timer Register High                            | Туре      |   |   |            | r         | h    |           |           |           |

#### Table 9WDT Register Overview

#### 3.2.4.6 Port Registers

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 10Port Register Overview

| Addr            | Register Name                    | Bit       | 7   | 6   | 5   | 4   | 3   | 2   | 1    | 0   |

|-----------------|----------------------------------|-----------|-----|-----|-----|-----|-----|-----|------|-----|

| RMAP =          | = 0                              |           |     |     |     |     |     |     |      |     |

| B2 <sub>H</sub> | PORT_PAGE Reset: 00 <sub>H</sub> | Bit Field | C   | )P  | ST  | NR  | 0   |     | PAGE |     |

|                 | Page Register                    | Туре      | Ņ   | N   | ١   | N   | r   |     | rwh  |     |

| RMAP =          | = 0, PAGE 0                      | -         |     |     |     |     |     |     |      |     |

| 80 <sub>H</sub> | P0_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P0 Data Register                 | Туре      | rwh  | rwh |

| 86 <sub>H</sub> | P0_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P0 Direction Register            | Туре      | rw   | rw  |

| 90 <sub>H</sub> | P1_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P1 Data Register                 | Туре      | rwh  | rwh |

| 91 <sub>H</sub> | P1_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P1 Direction Register            | Туре      | rw   | rw  |

| 92 <sub>H</sub> | P5_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P5 Data Register                 | Туре      | rwh  | rwh |

| 93 <sub>H</sub> | P5_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                 | P5 Direction Register            | Туре      | rw   | rw  |

#### Table 12T2CCU Register Overview (cont'd)

| Addr            | Register Name                                                                        | Bit       | 7          | 6    | 5          | 4          | 3          | 2           | 1          | 0          |

|-----------------|--------------------------------------------------------------------------------------|-----------|------------|------|------------|------------|------------|-------------|------------|------------|

| C5 <sub>H</sub> | T2CCU_CCTH Reset: 00 <sub>H</sub>                                                    | Bit Field |            | Ι    | Ι          | C          | СТ         |             |            | 1          |

|                 | T2CCU Capture/Compare<br>Timer Register High                                         | Туре      |            |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CCTCON Reset: 00 <sub>H</sub><br>T2CCU CaptureCcompare                         | Bit Field |            | ССТ  | PRE        |            | CCTO<br>VF | CCTO<br>VEN | TIMSY<br>N | CCTS<br>T  |

|                 | Timer Control Register                                                               | Туре      |            | r    | W          |            | rwh        | rw          | rw         | rw         |

| RMAP =          | 0, PAGE 2                                                                            |           |            |      |            |            |            |             |            |            |

| C0 <sub>H</sub> | <b>T2CCU_COSHDWReset: 00<sub>H</sub></b><br>T2CCU Capture/compare<br>Enable Register | Bit Field | ENSH<br>DW | TXOV | COOU<br>T5 | COOU<br>T4 | COOU<br>T3 | COOU<br>T2  | COOU<br>T1 | COOU<br>T0 |

|                 |                                                                                      | Туре      | rwh        | rwh  | rwh        | rwh        | rwh        | rwh         | rwh        | rwh        |

| C1 <sub>H</sub> | T2CCU_CC0L Reset: 00 <sub>H</sub><br>T2CCU Capture/Compare                           | Bit Field |            |      |            | CC/        | /ALL       |             |            |            |

|                 | Register 0 Low                                                                       | Туре      |            |      |            | rv         | vh         |             |            |            |

| C2 <sub>H</sub> | T2CCU_CC0H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 0 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

| C3 <sub>H</sub> | T2CCU_CC1L Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 1 Low                                              | Туре      |            |      |            | rv         | vh         |             |            |            |

| C4 <sub>H</sub> | T2CCU_CC1H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 1 High                                             | Туре      | rwh        |      |            |            |            |             |            |            |

| C5 <sub>H</sub> | T2CCU_CC2L Reset: 00 <sub>H</sub>                                                    | Bit Field | d CCVALL   |      |            |            |            |             |            |            |

|                 | T2CCU Capture/compare<br>Register 2 Low                                              | Туре      |            |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CC2H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 2 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

| RMAP =          | 0, PAGE 3                                                                            |           |            |      |            |            |            |             |            |            |

| C0 <sub>H</sub> | T2CCU_COCON Reset: 00 <sub>H</sub><br>T2CCU Compare Control                          | Bit Field | CCM5       | CCM4 | CM5F       | CM4F       | POLB       | POLA        | CON        | NOD        |

|                 | Register                                                                             | Туре      | rw         | rw   | rwh        | rwh        | rw         | rw          | r          | W          |

| C1 <sub>H</sub> | T2CCU_CC3L Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 3 Low                                              | Туре      |            |      |            | rv         | vh         |             |            |            |

| C2 <sub>H</sub> | T2CCU_CC3H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 3 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

| C3 <sub>H</sub> | T2CCU_CC4L Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CC/        | /ALL       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 4 Low                                              | Туре      |            |      |            | rv         | vh         |             |            |            |

| C4 <sub>H</sub> | T2CCU_CC4H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 4 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

| C5 <sub>H</sub> | T2CCU_CC5L Reset: 00 <sub>H</sub>                                                    | Bit Field | CCVALL     |      |            |            |            |             |            |            |

|                 | T2CCU Capture/compare<br>Register 5 Low                                              | Туре      |            |      |            | rv         | vh         |             |            |            |

| C6 <sub>H</sub> | T2CCU_CC5H Reset: 00 <sub>H</sub>                                                    | Bit Field |            |      |            | CCV        | /ALH       |             |            |            |

|                 | T2CCU Capture/compare<br>Register 5 High                                             | Туре      |            |      |            | rv         | vh         |             |            |            |

#### Table 14CCU6 Register Overview (cont'd)

| Addr            | Register Name                                                            | Bit       | 7          | 6            | 5            | 4          | 3            | 2          | 1            | 0          |

|-----------------|--------------------------------------------------------------------------|-----------|------------|--------------|--------------|------------|--------------|------------|--------------|------------|

| FD <sub>H</sub> | CCU6_MODCTRH Reset: 00 <sub>H</sub><br>Modulation Control Register High  | Bit Field | ECT1<br>3O | 0            |              | L          | T13M         | ODEN       | •            |            |

|                 |                                                                          | Туре      | rw         | r            |              |            | r            | w          |              |            |

| FE <sub>H</sub> | CCU6_TRPCTRL Reset: 00 <sub>H</sub><br>Trap Control Register Low         | Bit Field |            |              | 0            |            |              | TRPM<br>2  | TRPM<br>1    | TRPM<br>0  |

|                 |                                                                          | Туре      |            |              | r            |            |              | rw         | rw           | rw         |

| FF <sub>H</sub> | CCU6_TRPCTRH Reset: 00 <sub>H</sub><br>Trap Control Register High        | Bit Field | TRPP<br>EN | TRPE<br>N13  |              |            | TRI          | PEN        |              |            |

|                 |                                                                          | Туре      | rw         | rw           |              |            | r            | w          |              |            |

| RMAP =          | 0, PAGE 3                                                                | 1         |            |              | 1            |            |              |            |              |            |

| 9A <sub>H</sub> | CCU6_MCMOUTL Reset: 00 <sub>H</sub>                                      | Bit Field | 0          | R            |              |            | MC           | MP         |              |            |

|                 | Multi-Channel Mode Output Register<br>Low                                | Туре      | r          | rh           |              |            | r            | h          |              |            |

| 9B <sub>H</sub> | CCU6_MCMOUTH Reset: 00 <sub>H</sub>                                      | Bit Field | (          | )            |              | CURH       |              |            | EXPH         |            |

|                 | Multi-Channel Mode Output Register<br>High                               | Туре      |            | r            |              | rh         |              |            | rh           |            |

| 9CH             | CCU6_ISL Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status      | Bit Field | T12<br>PM  | T12<br>OM    | ICC62<br>F   | ICC62<br>R | ICC61<br>F   | ICC61<br>R | ICC60<br>F   | ICC60<br>R |

|                 | Register Low                                                             | Туре      | rh         | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| 9D <sub>H</sub> | CCU6_ISH Reset: 00 <sub>H</sub><br>Capture/Compare Interrupt Status      | Bit Field | STR        | IDLE         | WHE          | CHE        | TRPS         | TRPF       | T13<br>PM    | T13<br>CM  |

|                 | Register High                                                            | Туре      | rh         | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| 9E <sub>H</sub> | CCU6_PISEL0L Reset: 00 <sub>H</sub>                                      | Bit Field | IST        | RP           | ISC          | C62        | ISC          | C61        | ISC          | C60        |

|                 | Port Input Select Register 0 Low                                         | Туре      | r          | w            | r            | w          | r            | w          | r            | N          |

| 9F <sub>H</sub> | CCU6_PISEL0H Reset: 00 <sub>H</sub><br>Port Input Select Register 0 High | Bit Field | IST1       | 2HR          | ISP          | OS2        | ISP          | OS1        | ISP          | OS0        |

|                 |                                                                          | Туре      | r          | W            | r            | W          | r            | W          | r            | N          |

| A4 <sub>H</sub> | CCU6_PISEL2 Reset: 00 <sub>H</sub><br>Port Input Select Register 2       | Bit Field |            |              |              | 0          |              |            | IST1         | 3HR        |

|                 |                                                                          | Туре      |            |              |              | r          |              |            | r            | N          |

| FA <sub>H</sub> | CCU6_T12LReset: 00 <sub>H</sub> Timer T12 Counter Register Low           | Bit Field |            |              |              | T12        | CVL          |            |              |            |

|                 | _                                                                        | Туре      |            |              |              | rv         | vh           |            |              |            |

| FB <sub>H</sub> | CCU6_T12H Reset: 00 <sub>H</sub><br>Timer T12 Counter Register High      | Bit Field |            |              |              | T12        | CVH          |            |              |            |

|                 |                                                                          | Туре      |            |              |              | rv         | vh           |            |              |            |

| FC <sub>H</sub> | CCU6_T13L Reset: 00 <sub>H</sub><br>Timer T13 Counter Register Low       | Bit Field |            |              |              | T13        | CVL          |            |              |            |

|                 |                                                                          | Туре      |            |              |              | rv         | vh           |            |              |            |

| FD <sub>H</sub> | CCU6_T13H Reset: 00 <sub>H</sub><br>Timer T13 Counter Register High      | Bit Field |            |              |              | T13        | CVH          |            |              |            |

|                 |                                                                          | Туре      |            |              |              |            | vh           |            |              |            |

| FE <sub>H</sub> | CCU6_CMPSTATL Reset: 00 <sub>H</sub><br>Compare State Register Low       | Bit Field | 0          | CC63<br>ST   | CC<br>POS2   | CC<br>POS1 | CC<br>POS0   | CC62<br>ST | CC61<br>ST   | CC60<br>ST |

|                 |                                                                          | Туре      | r          | rh           | rh           | rh         | rh           | rh         | rh           | rh         |

| FF <sub>H</sub> | CCU6_CMPSTATH Reset: 00 <sub>H</sub><br>Compare State Register High      | Bit Field | T13IM      | COUT<br>63PS | COUT<br>62PS | CC62<br>PS | COUT<br>61PS | CC61<br>PS | COUT<br>60PS | CC60<br>PS |

|                 |                                                                          | Туре      | rwh        | rwh          | rwh          | rwh        | rwh          | rwh        | rwh          | rwh        |

#### XC87xCLM

#### **Functional Description**

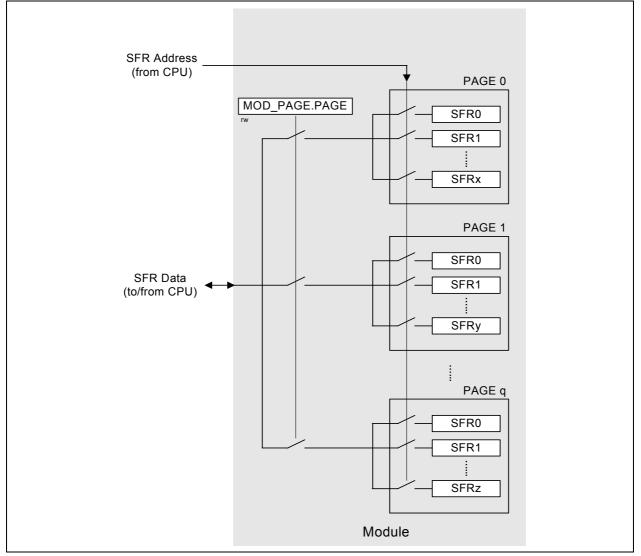

Figure 14 Interrupt Request Sources (Part 2)

#### 3.11 Multiplication/Division Unit

The Multiplication/Division Unit (MDU) provides fast 16-bit multiplication, 16-bit and 32-bit division as well as shift and normalize features. It has been integrated to support the XC87x Core in real-time control applications, which require fast mathematical computations.

#### Features

- Fast signed/unsigned 16-bit multiplication

- Fast signed/unsigned 32-bit divide by 16-bit and 16-bit divide by 16-bit operations

- 32-bit unsigned normalize operation

- 32-bit arithmetic/logical shift operations

Table 29 specifies the number of clock cycles used for calculation in various operations.

| Operation                | Result | Remainder | No. of Clock Cycles<br>used for calculation |

|--------------------------|--------|-----------|---------------------------------------------|

| Signed 32-bit/16-bit     | 32-bit | 16-bit    | 33                                          |

| Signed 16-bit/16bit      | 16-bit | 16-bit    | 17                                          |

| Signed 16-bit x 16-bit   | 32-bit | -         | 16                                          |

| Unsigned 32-bit/16-bit   | 32-bit | 16-bit    | 32                                          |

| Unsigned 16-bit/16-bit   | 16-bit | 16-bit    | 16                                          |

| Unsigned 16-bit x 16-bit | 32-bit | -         | 16                                          |

| 32-bit normalize         | -      | -         | No. of shifts + 1 (Max. 32)                 |

| 32-bit shift L/R         | -      | -         | No. of shifts + 1 (Max. 32)                 |

Table 29

MDU Operation Characteristics

- Interrupt enabling and corresponding flag

#### 3.13 UART and UART1

The XC87x provides two Universal Asynchronous Receiver/Transmitter (UART and UART1) modules for full-duplex asynchronous reception/transmission. Both are also receive-buffered, i.e., they can commence reception of a second byte before a previously received byte has been read from the receive register. However, if the first byte still has not been read by the time reception of the second byte is complete, one of the bytes will be lost.

#### Features

- Full-duplex asynchronous modes

- 8-bit or 9-bit data frames, LSB first

- Fixed or variable baud rate

- Receive buffered

- Multiprocessor communication

- Interrupt generation on the completion of a data transmission or reception

The UART modules can operate in the four modes shown in **Table 30**.

| f <sub>PCLK</sub> /2                               |

|----------------------------------------------------|

| Variable                                           |

| $f_{\rm PCLK}/32 \text{ or } f_{\rm PCLK}/64^{1)}$ |

| Variable                                           |

|                                                    |

#### Table 30UART Modes

1) For UART1 module, the baud rate is fixed at  $f_{PCLK}/64$ .

There are several ways to generate the baud rate clock for the serial port, depending on the mode in which it is operating. In mode 0, the baud rate for the transfer is fixed at  $f_{\rm PCLK}/2$ . In mode 2, the baud rate is generated internally based on the UART input clock and can be configured to either  $f_{\rm PCLK}/32$  or  $f_{\rm PCLK}/64$ . For UART1 module, only  $f_{\rm PCLK}/64$  is available. The variable baud rate is set by the underflow rate on the dedicated baud-rate generator. For UART module, the variable baud rate alternatively can be set by the overflow rate on Timer 1.

#### 3.13.1 Baud-Rate Generator

Both UART modules have their own dedicated baud-rate generator, which is based on a programmable 8-bit reload value, and includes divider stages (i.e., prescaler and

| Table 32 Deviation Error for UART with Fractional Divider enabled |                               |                                |                        |                    |  |  |  |  |  |

|-------------------------------------------------------------------|-------------------------------|--------------------------------|------------------------|--------------------|--|--|--|--|--|

| f <sub>pclk</sub>                                                 | Prescaling Factor<br>(2BRPRE) | Reload Value<br>(BR_VALUE + 1) | STEP                   | Deviation<br>Error |  |  |  |  |  |

| 24 MHz                                                            | 1                             | 6 (6 <sub>H</sub> )            | 59 (3B <sub>H</sub> )  | +0.03 %            |  |  |  |  |  |

| 12 MHz                                                            | 1                             | 3 (3 <sub>H</sub> )            | 59 (3B <sub>H</sub> )  | +0.03 %            |  |  |  |  |  |

| 8 MHz                                                             | 1                             | 2 (2 <sub>H</sub> )            | 59 (3B <sub>H</sub> )  | +0.03 %            |  |  |  |  |  |

| 6 MHz                                                             | 1                             | 6 (6 <sub>H</sub> )            | 236 (EC <sub>H</sub> ) | +0.03 %            |  |  |  |  |  |

#### Table 32 Deviation Error for UART with Fractional Divider enabled

#### 3.13.2 Baud Rate Generation using Timer 1

In UART modes 1 and 3 of UART module, Timer 1 can be used for generating the variable baud rates. In theory, this timer could be used in any of its modes. But in practice, it should be set into auto-reload mode (Timer 1 mode 2), with its high byte set to the appropriate value for the required baud rate. The baud rate is determined by the Timer 1 overflow rate and the value of SMOD as follows:

Mode 1, 3 baud rate=

$$\frac{2^{\text{SMOD}} \times f_{\text{PCLK}}}{32 \times 2 \times (256 - \text{TH1})}$$

(3.6)

#### 3.14 Normal Divider Mode (8-bit Auto-reload Timer)

Setting bit FDM in register FDCON to 1 configures the fractional divider to normal divider mode, while at the same time disables baud rate generation (see **Figure 26**). Once the fractional divider is enabled (FDEN = 1), it functions as an 8-bit auto-reload timer (with no relation to baud rate generation) and counts up from the reload value with each input clock pulse. Bit field RESULT in register FDRES represents the timer value, while bit field STEP in register FDSTEP defines the reload value. At each timer overflow, an overflow flag (FDCON.NDOV) will be set and an interrupt request generated. This gives an output clock  $f_{MOD}$  that is 1/n of the input clock  $f_{DIV}$ , where n is defined by 256 - STEP. The output frequency in normal divider mode is derived as follows:

$$f_{MOD} = f_{DIV} \times \frac{1}{256 - STEP}$$

(3.7)

#### 3.23.1 JTAG ID Register

This is a read-only register located inside the JTAG module, and is used to recognize the device(s) connected to the JTAG interface. Its content is shifted out when INSTRUCTION register contains the IDCODE command (opcode  $04_H$ ), and the same is also true immediately after reset.

The JTAG ID register contents for the XC87x Flash devices are given in Table 36.

| Device Type | Device Name | JTAG ID                |  |

|-------------|-------------|------------------------|--|

| Flash       | XC87x*-16FF | 1018 2083 <sub>H</sub> |  |

|             | XC87x*-13FF | 1018 3083 <sub>H</sub> |  |

Note: The asterisk (\*) above denotes all possible device configurations.

#### 3.24 Chip Identification Number

The XC87x identity (ID) register is located at Page 1 of address  $B3_{H}$ . The value of ID register is  $49_{H}$ . However, for easy identification of product variants, the Chip Identification Number, which is an unique number assigned to each product variant, is available. The differentiation is based on the product, variant type and device step information.

Two methods are provided to read a device's chip identification number:

- In-application subroutine, GET\_CHIP\_INFO

- Bootstrap loader (BSL) mode A

Table 37 lists the chip identification numbers of available XC87x Flash device variants.

| Product Variant  | Chip Identification Number<br>AC-step |  |  |  |  |  |

|------------------|---------------------------------------|--|--|--|--|--|

|                  |                                       |  |  |  |  |  |

| Flash Devices    |                                       |  |  |  |  |  |

| XC878-16FF 5V    | 4B580063 <sub>H</sub>                 |  |  |  |  |  |

| XC878M-16FF 5V   | 4B580023 <sub>H</sub>                 |  |  |  |  |  |

| XC878CM-16FF 5V  | 4B580003 <sub>H</sub>                 |  |  |  |  |  |

| XC878LM-16FF 5V  | 4B500023 <sub>H</sub>                 |  |  |  |  |  |

| XC878CLM-16FF 5V | 4B500003 <sub>H</sub>                 |  |  |  |  |  |

| XC878-13FF 5V    | 4B590463 <sub>H</sub>                 |  |  |  |  |  |

| XC878M-13FF 5V   | 4B590423 <sub>H</sub>                 |  |  |  |  |  |

| XC878CM-13FF 5V  | 4B590403 <sub>H</sub>                 |  |  |  |  |  |

| XC878LM-13FF 5V  | 4B510423 <sub>H</sub>                 |  |  |  |  |  |

| XC878CLM-13FF 5V | 4B510403 <sub>H</sub>                 |  |  |  |  |  |

| XC878-16FF 3V3   | 4B180063 <sub>H</sub>                 |  |  |  |  |  |

| XC878M-16FF 3V3  | 4B180023 <sub>H</sub>                 |  |  |  |  |  |

| XC878CM-16FF 3V3 | 4B180003 <sub>H</sub>                 |  |  |  |  |  |

| XC878-13FF 3V3   | 4B190463 <sub>H</sub>                 |  |  |  |  |  |

| XC878M-13FF 3V3  | 4B190423 <sub>H</sub>                 |  |  |  |  |  |

| XC878CM-13FF 3V3 | 4B190403 <sub>H</sub>                 |  |  |  |  |  |

| XC874CM-16FV 5V  | 4B580002 <sub>H</sub>                 |  |  |  |  |  |

| XC874LM-16FV 5V  | 4B500022 <sub>H</sub>                 |  |  |  |  |  |

| XC874-16FV 5V    | 4B580062 <sub>H</sub>                 |  |  |  |  |  |

Table 37

Chip Identification Number

#### **Electrical Parameters**

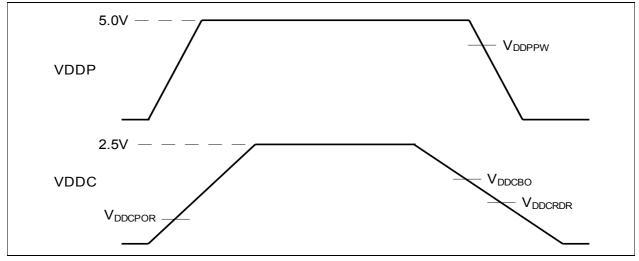

#### 4.2.2 Supply Threshold Characteristics

Table 41 provides the characteristics of the supply threshold in the XC87x.

#### Table 41 Supply Threshold Parameters (Operating Conditions apply)

| Parameters                                     | Symbol              |    | Unit |      |      |   |

|------------------------------------------------|---------------------|----|------|------|------|---|

|                                                |                     |    | min. | typ. | max. |   |

| $V_{\rm DDC}$ brownout voltage <sup>1)</sup>   | V <sub>DDCBO</sub>  | CC | 1.7  | 1.9  | 2.2  | V |

| RAM data retention voltage                     | V <sub>DDCRDR</sub> | CC | 1.2  | -    | -    | V |

| $V_{\rm DDP}$ prewarning voltage <sup>2)</sup> | V <sub>DDPPW</sub>  | CC | 3.8  | 4.2  | 4.5  | V |

| Power-on reset voltage <sup>1)3)</sup>         | VDDCPOR             | CC | 1.7  | 1.9  | 2.2  | V |

1) Detection is enabled in both active and power-down mode.

2) Detection is enabled for 5.0V power supply variant. Detection is disabled for 3.3V power supply variant.

3) The reset of EVR is extended by 300  $\mu$ s typically after the VDDC reaches the power-on reset voltage.

#### **Electrical Parameters**

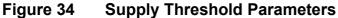

#### 4.3.3 Power-on Reset and PLL Timing

Table 48 provides the characteristics of the power-on reset and PLL timing in the XC87x.

#### Table 48 Power-On Reset and PLL Timing (Operating Conditions apply)

| Parameter                           | Symbol             |    | Limit Values |      |      | Unit | Test Conditions |  |

|-------------------------------------|--------------------|----|--------------|------|------|------|-----------------|--|

|                                     |                    |    | min.         | typ. | max. | -    |                 |  |

| On-Chip Oscillator<br>start-up time | t <sub>OSCST</sub> | CC | -            | -    | 500  | ns   | 1)              |  |

| PLL lock-in in time                 | t <sub>LOCK</sub>  | CC | -            | _    | 200  | μS   | 1)              |  |

| PLL accumulated jitter              | D <sub>P</sub>     |    | _            | _    | 1.8  | ns   | 1)2)            |  |

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

2) PLL lock at 144 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 72 and P = 1.

Figure 40 Power-on Reset Timing

#### **Electrical Parameters**

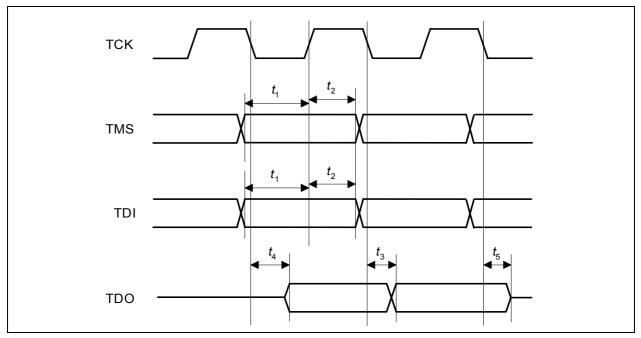

| Table 54 JTAG Timing (Operating Conditions apply; CL = 50 pr) (cont d) |                   |        |     |        |                           |      |                        |

|------------------------------------------------------------------------|-------------------|--------|-----|--------|---------------------------|------|------------------------|

| Parameter                                                              | Symbol            | Limits |     | Limits |                           | Unit | <b>Test Conditions</b> |

|                                                                        |                   | min    | max |        |                           |      |                        |

| TDO high impedance to valid                                            | $t_4$ CC          | -      | 18  | ns     | 5V Device <sup>1)</sup>   |      |                        |

| output from TCK                                                        |                   | -      | 21  | ns     | 3.3V Device <sup>1)</sup> |      |                        |

| TDO valid output to high                                               | t <sub>5</sub> CC | -      | 21  | ns     | 5V Device <sup>1)</sup>   |      |                        |

| impedance from TCK                                                     |                   | -      | 20  | ns     | 3.3V Device <sup>1)</sup> |      |                        |

Table 54JTAG Timing (Operating Conditions apply; CL = 50 pF) (cont'd)

1) Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

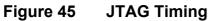

#### Package and Quality Declaration

#### 5.2 Package Outline

Figure 47 shows the package outlines of the XC878.

Figure 47 PG-LQFP-64-4 Package Outline