Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | XC800                                                                             |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 27MHz                                                                             |

| Connectivity               | LINbus, SSI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                             |

| Number of I/O              | 40                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 3.25K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | A/D 8x10b                                                                         |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP                                                                           |

| Supplier Device Package    | PG-LQFP-64-4                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc878lm16ffa5vackxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **General Device Information**

#### 2.2 Logic Symbol

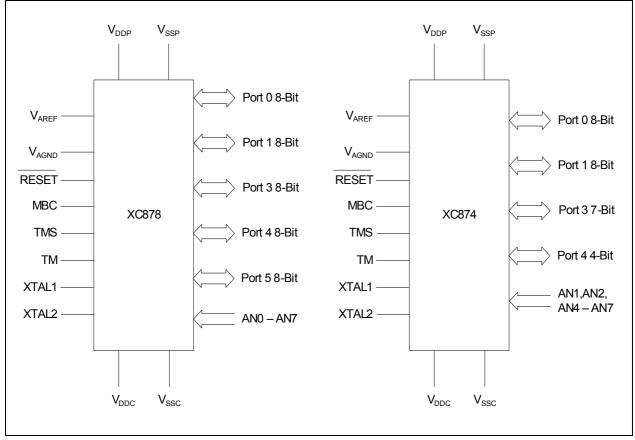

The logic symbols of the XC878 and XC874 are shown in Figure 3.

Figure 3 XC878 and XC874 Logic Symbol

# XC87xCLM

#### **General Device Information**

#### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                  |                                                                                  |

|--------|--------------------------------------|------|----------------|---------------------------|----------------------------------------------------------------------------------|

| P0.3   | 63/1                                 |      | Hi-Z           | SCK_1<br>COUT63_1         | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3                 |

|        |                                      |      |                | RXDO1_0<br>A17            | UART1 Transmit Data Output<br>Address Line 17 Output                             |

| P0.4   | 64/2                                 |      | Hi-Z           | MTSR_1                    | SSC Master Transmit Output/<br>Slave Receive Input                               |

|        |                                      |      |                | CC62_1                    | Input/Output of<br>Capture/Compare channel 2                                     |

|        |                                      |      |                | TXD1_0                    | UART1 Transmit Data<br>Output/Clock Output                                       |

|        |                                      |      |                | A18                       | Address Line 18 Output                                                           |

| P0.5   | 1/3                                  |      | Hi-Z           | MRST_1                    | SSC Master Receive Input/Slave<br>Transmit Output                                |

|        |                                      |      |                | EXINT0_0                  | External Interrupt Input 0                                                       |

|        |                                      |      |                | T2EX1_1                   | Timer 21 External Trigger Input                                                  |

|        |                                      |      |                | RXD1_0                    | UART1 Receive Data Input                                                         |

|        |                                      |      |                | COUT62_1                  | Output of Capture/Compare<br>channel 2                                           |

|        |                                      |      |                | A19                       | Address Line 19 Output                                                           |

| P0.6   | 2/4                                  |      | PU             | <u>T2CC4_</u> 1<br>WR     | Compare Output Channel 4<br>External Data Write Control<br>Output                |

| P0.7   | 62/48                                |      | PU             | CLKOUT_1<br>T2CC5_1<br>RD | Clock Output<br>Compare Output Channel 5<br>External Data Read Control<br>Output |

# XC87xCLM

#### **General Device Information**

#### Table 3Pin Definitions and Functions (cont'd)

| Symbol | Pin Number<br>(LQFP-64 /<br>VQFN-48) | Туре | Reset<br>State | Function                                    |                                                                                                                                      |

|--------|--------------------------------------|------|----------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| P4.5   | 46/-                                 |      | Hi-Z           | CCPOS1_3<br>T1_0<br>COUT61_2                | CCU6 Hall Input 1<br>Timer 1 Input<br>Output of Capture/Compare<br>channel 1                                                         |

|        |                                      |      |                | T2CC3_0/<br>EXINT6_2<br>D5                  | External Interrupt Input 6/T2CCU<br>Capture/Compare Channel 3<br>Data Line 5 Input/Output                                            |

| P4.6   | 47/-                                 |      | Hi-Z           | CCPOS2_3<br>T2_0<br>CC62_2<br>T2CC4_0<br>D6 | CCU6 Hall Input 2<br>Timer 2 Input<br>Output of Capture/Compare<br>channel 2<br>Compare Output Channel 4<br>Data Line 6 Input/Output |

| P4.7   | 48/-                                 |      | Hi-Z           | CTRAP_3<br>COUT62_2<br>T2CC5_0<br>D7        |                                                                                                                                      |

| Flash<br>Protection                      | Without hardware protection             | With hardware protect                                                                                                                                                         | tion                                                                  |

|------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| P-Flash<br>program<br>and erase          | Possible                                | Possible only on the condition that MSB - 1 of password is set to 1                                                                                                           | Possible only on the condition that MSB - 1 of password is set to 1   |

| D-Flash<br>contents<br>can be read<br>by | Read instructions in any program memory | Read instructions in any program memory                                                                                                                                       | Read instructions in<br>the P-Flash or D-<br>Flash                    |

| External<br>access to D-<br>Flash        | Not possible                            | Not possible                                                                                                                                                                  | Not possible                                                          |

| D-Flash<br>program                       | Possible                                | Possible                                                                                                                                                                      | Possible, on the condition that MSB - 1 of password is set to 1       |

| D-Flash<br>erase                         | Possible                                | <ul> <li>Possible, on these conditions:</li> <li>MISC_CON.DFLASH EN bit is set to 1 prior to each erase operation; or</li> <li>the MSB - 1 of password is set to 1</li> </ul> | Possible, on the<br>condition that MSB - 1<br>of password is set to 1 |

#### Table 4Flash Protection Modes (cont'd)

BSL mode 6, which is used for enabling Flash protection, can also be used for disabling Flash protection. Here, the programmed password must be provided by the user. To disable the flash protection, a password match is required. A password match triggers an automatic erase of the protected P-Flash and D-Flash contents, including the programmed password. With a valid password, the Flash hardware protection is then enabled or disabled upon next reset. For the other protection strategies, no reset is necessary.

Although no protection scheme can be considered infallible, the XC87x memory protection strategy provides a very high level of protection for a general purpose microcontroller.

Note: If ROM read-out protection is enabled, only read instructions in the ROM memory can target the ROM contents.

SYSCON0

#### **Functional Description**

#### System Control Register 0 Reset Value: 04 7 5 4 3 2 1 0 6 IMODE 1 RMAP 0 0 0 r r r r rw rw

| Field | Bits          | Туре | Description                                                                                                                                                            |  |  |  |  |  |

|-------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RMAP  | 0             | rw   | <ul> <li>Interrupt Node XINTR0 Enable</li> <li>The access to the standard SFR area is<br/>enabled</li> <li>The access to the mapped SFR area is<br/>enabled</li> </ul> |  |  |  |  |  |

| 1     | 2             | r    | Reserved<br>Returns 1 if read; should be written with 1.                                                                                                               |  |  |  |  |  |

| 0     | [7:5],<br>3,1 | r    | <b>Reserved</b><br>Returns 0 if read; should be written with 0.                                                                                                        |  |  |  |  |  |

Note: The RMAP bit should be cleared/set by ANL or ORL instructions. The rest bits of SYSCON0 should not be modified.

#### 3.2.2.2 Address Extension by Paging

Address extension is further performed at the module level by paging. With the address extension by mapping, the XC87x has a 256-SFR address range. However, this is still less than the total number of SFRs needed by the on-chip peripherals. To meet this requirement, some peripherals have a built-in local address extension mechanism for increasing the number of addressable SFRs. The extended address range is not directly controlled by the CPU instruction itself, but is derived from bit field PAGE in the module page register MOD\_PAGE. Hence, the bit field PAGE must be programmed before accessing the SFR of the target module. Each module may contain a different number of pages and a different number of SFRs per page, depending on the specific requirement. Besides setting the correct RMAP bit value to select the SFR area, the user must also ensure that a valid PAGE is selected to target the desired SFR. A page inside the extended address range can be selected as shown in **Figure 10**.

| Addr            | Register Name                                             | Bit       | 7         | 6         | 5           | 4           | 3          | 2   | 1         | 0   |

|-----------------|-----------------------------------------------------------|-----------|-----------|-----------|-------------|-------------|------------|-----|-----------|-----|

| 9CH             | CD_CORDYL Reset: 00 <sub>H</sub>                          | Bit Field |           | DATAL     |             |             |            |     |           |     |

|                 | CORDIC Y Data Low Byte                                    | Туре      |           | rw        |             |             |            |     |           |     |

| 9D <sub>H</sub> | CD_CORDYH Reset: 00 <sub>H</sub>                          | Bit Field | DATAH     |           |             |             |            |     |           |     |

|                 | CORDIC Y Data High Byte                                   | Туре      |           | rw        |             |             |            |     |           |     |

| 9E <sub>H</sub> | CD_CORDZL Reset: 00 <sub>H</sub>                          | Bit Field |           |           |             | DA          | TAL        |     |           |     |

|                 | CORDIC Z Data Low Byte                                    | Туре      | rw        |           |             |             |            |     |           |     |

| 9F <sub>H</sub> | CD_CORDZH Reset: 00 <sub>H</sub>                          | Bit Field | DATAH     |           |             |             |            |     |           |     |

|                 | CORDIC Z Data High Byte                                   | Туре      | rw        |           |             |             |            |     |           |     |

| ^0 <sub>H</sub> | CD_STATC Reset: 00 <sub>H</sub><br>CORDIC Status and Data | Bit Field | KEEP<br>Z | KEEP<br>Y | KEEP<br>X   | DMAP        | INT_E<br>N | EOC | ERRO<br>R | BSY |

|                 | Control Register                                          | Туре      | rw        | rw        | rw          | rw          | rw         | rwh | rh        | rh  |

| А1 <sub>Н</sub> | CD_CON Reset: 00 <sub>H</sub><br>CORDIC Control Register  | Bit Field | MPS       |           | X_USI<br>GN | ST_M<br>ODE | ROTV<br>EC | MC  | DE        | ST  |

|                 |                                                           | Туре      | n         | N         | rw          | rw          | rw         | r   | W         | rwh |

#### Table 7CORDIC Register Overview (cont'd)

#### 3.2.4.4 System Control Registers

The system control SFRs can be accessed in the mapped memory area (RMAP = 0).

#### Table 8 SCU Register Overview

| Addr            | Register Name                                                              | Bit       | 7 | 6           | 5            | 4            | 3            | 2            | 1            | 0           |

|-----------------|----------------------------------------------------------------------------|-----------|---|-------------|--------------|--------------|--------------|--------------|--------------|-------------|

| RMAP =          | = 0 or 1                                                                   |           |   |             |              |              |              |              |              |             |

| 8F <sub>H</sub> | F <sub>H</sub> SYSCON0 Reset: 04 <sub>H</sub><br>System Control Register 0 |           |   | 0           |              | IMOD<br>E    | 0            | 1            | 0            | RMAP        |

|                 |                                                                            | Туре      |   | r           |              | rw           | r            | r            | r            | rw          |

| RMAP =          | = 0                                                                        |           |   |             |              |              |              |              |              |             |

| bf <sub>H</sub> | SCU_PAGE Reset: 00 <sub>H</sub>                                            | Bit Field | ( | OP          | ST           | NR           | 0            |              | PAGE         |             |

|                 | Page Register                                                              | Туре      | w |             | ١            | N            | r            |              | rwh          |             |

| RMAP =          | = 0, PAGE 0                                                                |           |   |             | •            |              |              |              |              |             |

|                 | MODPISEL Reset: 00 <sub>H</sub><br>Peripheral Input Select Register        | Bit Field | 0 | URRIS<br>H  | JTAGT<br>DIS | JTAGT<br>CKS | EXINT<br>2IS | EXINT<br>1IS | EXINT<br>0IS | URRIS       |

|                 |                                                                            | Туре      | r | rw          | rw           | rw           | rw           | rw           | rw           | rw          |

| B4 <sub>H</sub> | IRCON0 Reset: 00 <sub>H</sub><br>Interrupt Request Register 0              | Bit Field | 0 | EXINT<br>6  | EXINT<br>5   | EXINT<br>4   | EXINT<br>3   | EXINT<br>2   | EXINT<br>1   | EXINT<br>0  |

|                 |                                                                            | Туре      | r | rwh         | rwh          | rwh          | rwh          | rwh          | rwh          | rwh         |

| B5 <sub>H</sub> | IRCON1 Reset: 00 <sub>H</sub><br>Interrupt Request Register 1              | Bit Field | 0 | CANS<br>RC2 | CANS<br>RC1  | ADCS<br>R1   | ADCS<br>R0   | RIR          | TIR          | EIR         |

|                 |                                                                            | Туре      | r | rwh         | rwh          | rwh          | rwh          | rwh          | rwh          | rwh         |

| B6 <sub>H</sub> | IRCON2 Reset: 00 <sub>H</sub><br>Interrupt Request Register 2              | Bit Field | 0 |             |              | CANS<br>RC3  |              | 0            |              | CANS<br>RC0 |

|                 |                                                                            | Туре      |   | r           |              | rwh          |              | r            |              | rwh         |

#### 3.2.4.5 WDT Registers

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

| Addr            | Register Name                                                                      | Bit       | 7       | 6 | 5          | 4         | 3 | 2         | 1         | 0         |

|-----------------|------------------------------------------------------------------------------------|-----------|---------|---|------------|-----------|---|-----------|-----------|-----------|

| RMAP =          | = 1                                                                                |           |         |   |            | •         |   |           |           |           |

| вв <sub>Н</sub> | B <sub>H</sub> WDTCON Reset: 00 <sub>H</sub><br>Watchdog Timer Control<br>Register | Bit Field |         | 0 | WINB<br>EN | WDTP<br>R | 0 | WDTE<br>N | WDTR<br>S | WDTI<br>N |

| Register        | Register                                                                           | Туре      |         | r | rw         | rh        | r | rw        | rwh       | rw        |

| вс <sub>Н</sub> | WDTREL Reset: 00 <sub>H</sub>                                                      | Bit Field | WDTREL  |   |            |           |   |           |           |           |

|                 | Watchdog Timer Reload<br>Register                                                  | Туре      | rw      |   |            |           |   |           |           |           |

| вd <sub>Н</sub> | WDTWINB Reset: 00 <sub>H</sub>                                                     | Bit Field | WDTWINB |   |            |           |   |           |           |           |

|                 | Watchdog Window-Boundary<br>Count Register                                         | Туре      | rw      |   |            |           |   |           |           |           |

| BE <sub>H</sub> | WDTL Reset: 00 <sub>H</sub>                                                        | Bit Field | WDT     |   |            |           |   |           |           |           |

|                 | Watchdog Timer Register Low                                                        | Туре      | rh      |   |            |           |   |           |           |           |

| bf <sub>h</sub> | WDTH Reset: 00 <sub>H</sub>                                                        | Bit Field | WDT     |   |            |           |   |           |           |           |

|                 | Watchdog Timer Register High                                                       |           | rh      |   |            |           |   |           |           |           |

#### Table 9WDT Register Overview

#### 3.2.4.6 Port Registers

The Port SFRs can be accessed in the standard memory area (RMAP = 0).

#### Table 10Port Register Overview

| Addr             | Register Name                    | Bit       | 7   | 6   | 5   | 4   | 3   | 2   | 1    | 0   |

|------------------|----------------------------------|-----------|-----|-----|-----|-----|-----|-----|------|-----|

| RMAP =           | = 0                              |           |     |     |     |     |     |     |      |     |

| B2 <sub>H</sub>  | PORT_PAGE Reset: 00 <sub>H</sub> | Bit Field | C   | )P  | ST  | NR  | 0   |     | PAGE |     |

|                  | Page Register                    | Туре      | Ņ   | N   | ١   | N   | r   |     | rwh  |     |

| RMAP =           | = 0, PAGE 0                      | -         |     |     |     |     |     |     |      |     |

| 80 <sub>H</sub>  | P0_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

| P0               | P0 Data Register                 | Туре      | rwh  | rwh |

| 86 <sub>H</sub>  | P0_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                  | P0 Direction Register            | Туре      | rw   | rw  |

| 90 <sub>H</sub>  | P1_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                  | P1 Data Register                 | Туре      | rwh  | rwh |

| 91 <sub>H</sub>  | P1_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                  | P1 Direction Register            | Туре      | rw   | rw  |

| 92 <sub>H</sub>  | P5_DATA Reset: 00 <sub>H</sub>   | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

|                  | P5 Data Register                 | Туре      | rwh  | rwh |

| 93 <sub>H</sub>  | P5_DIR Reset: 00 <sub>H</sub>    | Bit Field | P7  | P6  | P5  | P4  | P3  | P2  | P1   | P0  |

| P5 Direction Reg | P5 Direction Register            | Туре      | rw   | rw  |

#### Table 11ADC Register Overview (cont'd)

| Addr            | Register Name                                                          | Bit       | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|-----------------|------------------------------------------------------------------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|

| св <sub>Н</sub> | ADC_RCR1 Reset: 00 <sub>H</sub><br>Result Control Register 1           | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                        | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| сс <sup>н</sup> | ADC_RCR2 Reset: 00 <sub>H</sub><br>Result Control Register 2           | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                        | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| CD <sub>H</sub> | ADC_RCR3 Reset: 00 <sub>H</sub><br>Result Control Register 3           | Bit Field | VFCT<br>R  | WFR        | 0          | IEN        |            | 0          |            | DRCT<br>R  |

|                 |                                                                        | Туре      | rw         | rw         | r          | rw         |            | r          |            | rw         |

| CEH             | ADC_VFCR Reset: 00 <sub>H</sub>                                        | Bit Field |            | (          | )          |            | VFC3       | VFC2       | VFC1       | VFC0       |

|                 | Valid Flag Clear Register                                              | Туре      |            | l          | r          |            | w          | w          | w          | w          |

| RMAP =          | 0, PAGE 5                                                              |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_CHINFR Reset: 00 <sub>H</sub><br>Channel Interrupt Flag Register   | Bit Field | CHINF<br>7 | CHINF<br>6 | CHINF<br>5 | CHINF<br>4 | CHINF<br>3 | CHINF<br>2 | CHINF<br>1 | CHINF<br>0 |

|                 |                                                                        | Туре      | rh         |

| св <sub>Н</sub> | ADC_CHINCR Reset: 00 <sub>H</sub><br>Channel Interrupt Clear Register  | Bit Field | CHINC<br>7 | CHINC<br>6 | CHINC<br>5 | CHINC<br>4 | CHINC<br>3 | CHINC<br>2 | CHINC<br>1 | CHINC<br>0 |

|                 |                                                                        | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |

| сс <sub>Н</sub> | ADC_CHINSR Reset: 00 <sub>H</sub><br>Channel Interrupt Set Register    | Bit Field | CHINS<br>7 | CHINS<br>6 | CHINS<br>5 | CHINS<br>4 | CHINS<br>3 | CHINS<br>2 | CHINS<br>1 | CHINS<br>0 |

|                 |                                                                        | Туре      | w          | w          | w          | w          | w          | w          | w          | w          |

| CD <sub>H</sub> | ADC_CHINPR Reset: 00 <sub>H</sub><br>Channel Interrupt Node Pointer    | Bit Field | CHINP<br>7 | CHINP<br>6 | CHINP<br>5 | CHINP<br>4 | CHINP<br>3 | CHINP<br>2 | CHINP<br>1 | CHINP<br>0 |

|                 | Register                                                               | Туре      | rw         |

| Ceh             | ADC_EVINFR Reset: 00 <sub>H</sub><br>Event Interrupt Flag Register     | Bit Field | EVINF<br>7 | EVINF<br>6 | EVINF<br>5 | EVINF<br>4 | (          | 0          | EVINF<br>1 | EVINF<br>0 |

|                 |                                                                        | Туре      | rh         | rh         | rh         | rh         |            | r          | rh         | rh         |

| CF <sub>H</sub> | ADC_EVINCR Reset: 00 <sub>H</sub><br>Event Interrupt Clear Flag        | Bit Field | EVINC<br>7 | EVINC<br>6 | EVINC<br>5 | EVINC<br>4 | (          | 0          | EVINC<br>1 | EVINC<br>0 |

|                 | Register                                                               | Туре      | W          | w          | w          | w          |            | r          | w          | w          |

| D2 <sub>H</sub> | ADC_EVINSR Reset: 00 <sub>H</sub><br>Event Interrupt Set Flag Register | Bit Field | EVINS<br>7 | EVINS<br>6 | EVINS<br>5 | EVINS<br>4 | (          | 0          | EVINS<br>1 | EVINS<br>0 |

|                 |                                                                        | Туре      | w          | w          | w          | w          |            | r          | w          | w          |

| D3 <sub>H</sub> | ADC_EVINPR Reset: 00 <sub>H</sub><br>Event Interrupt Node Pointer      | Bit Field | EVINP<br>7 | EVINP<br>6 | EVINP<br>5 | EVINP<br>4 | (          | D          | EVINP<br>1 | EVINP<br>0 |

|                 | Register                                                               | Туре      | rw         | rw         | rw         | rw         |            | r          | rw         | rw         |

| RMAP =          | 0, PAGE 6                                                              |           |            |            |            |            |            |            |            |            |

| CA <sub>H</sub> | ADC_CRCR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CH7        | CH6        | CH5        | CH4        |            | (          | 0          |            |

|                 | Conversion Request Control<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            |            | r          |            |

| св <sub>Н</sub> | ADC_CRPR1 Reset: 00 <sub>H</sub>                                       | Bit Field | CHP7       | CHP6       | CHP5       | CHP4       |            | (          | 0          |            |

|                 | Conversion Request Pending<br>Register 1                               | Туре      | rwh        | rwh        | rwh        | rwh        |            |            | r          |            |

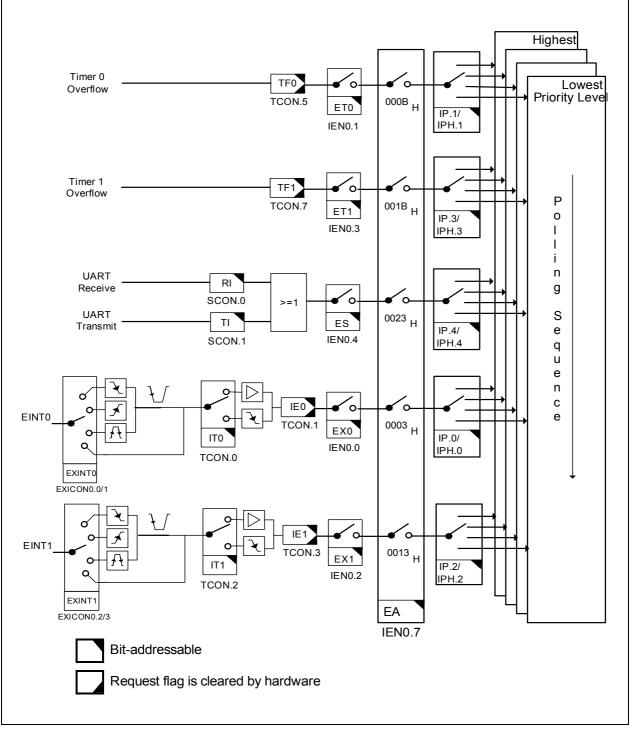

Figure 13 Interrupt Request Sources (Part 1)

#### XC87xCLM

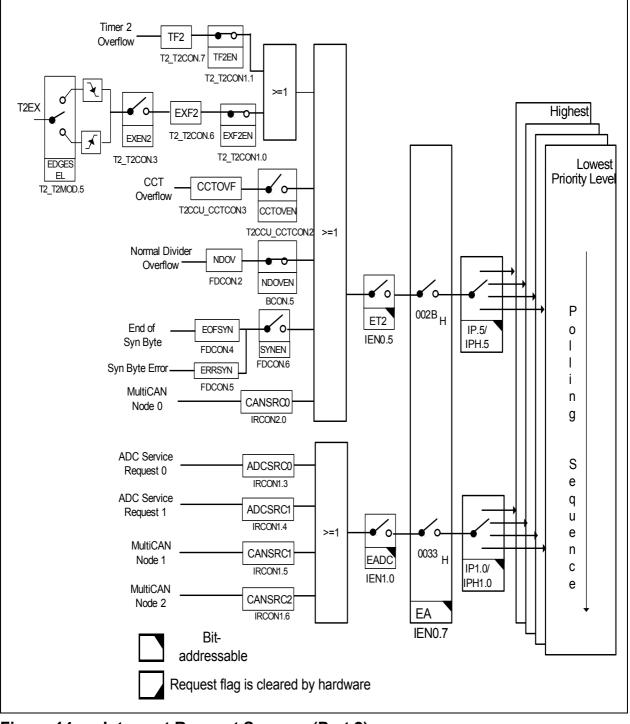

Figure 14 Interrupt Request Sources (Part 2)

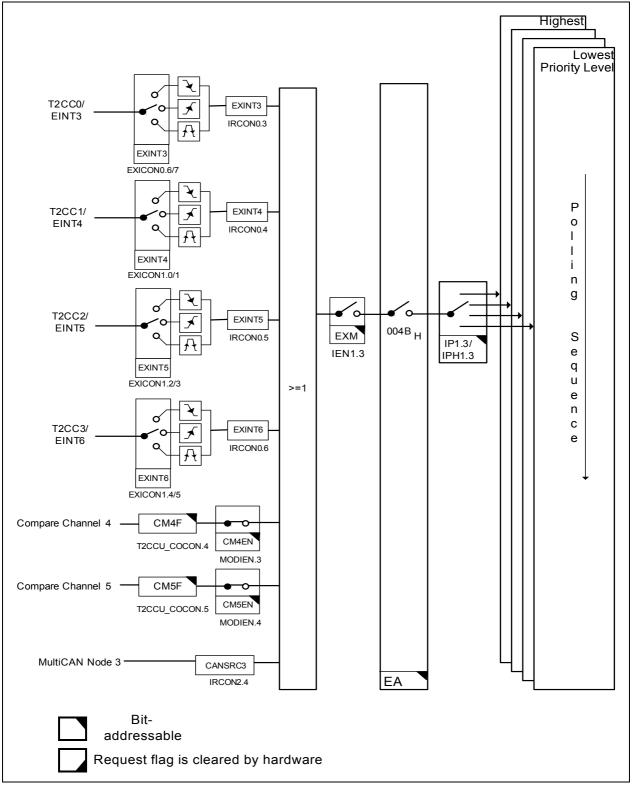

Figure 16 Interrupt Request Sources (Part 4)

#### 3.5 Parallel Ports

The XC87x has 40 port pins organized into five parallel ports: Port 0 (P0), Port 1 (P1), Port 3 (P3), Port 4 (P4) and Port 5 (P5). Each pin has a pair of internal pull-up and pull-down devices that can be individually enabled or disabled. These ports are bidirectional and can be used as general purpose input/output (GPIO) or to perform alternate input/output functions for the on-chip peripherals. When configured as an output, the open drain mode can be selected.

#### **Bidirectional Port Features**

- Configurable pin direction

- Configurable pull-up/pull-down devices

- Configurable open drain mode

- Configurable drive strength

- Transfer of data through digital inputs and outputs (general purpose I/O)

- Alternate input/output for on-chip peripherals

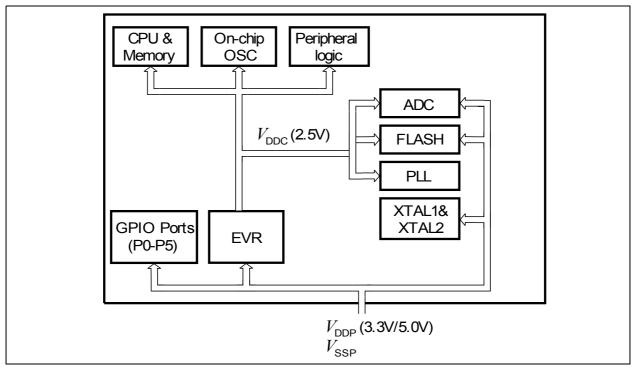

#### 3.6 Power Supply System with Embedded Voltage Regulator

The XC87x microcontroller requires two different levels of power supply:

- 3.3 V or 5.0 V for the Embedded Voltage Regulator (EVR) and Ports

- 2.5 V for the core, memory, on-chip oscillator, and peripherals

**Figure 19** shows the XC87x power supply system. A power supply of 3.3 V or 5.0 V must be provided from the external power supply pin. The 2.5 V power supply for the logic is generated by the EVR. The EVR helps to reduce the power consumption of the whole chip and the complexity of the application board design.

The EVR consists of a main voltage regulator and a low power voltage regulator. In active mode, both voltage regulators are enabled. In power-down mode<sup>1)</sup>, the main voltage regulator is switched off, while the low power voltage regulator continues to function and provide power supply to the system with low power consumption.

72

Figure 19 XC87x Power Supply System

#### **EVR Features**

- Input voltage ( $V_{\text{DDP}}$ ): 3.3 V/5.0 V

- Output voltage ( $V_{DDC}$ ): 2.5 V ± 7.5%

- Low power voltage regulator provided in power-down mode<sup>1)</sup>

- $V_{\text{DDP}}$  prewarning detection

- V<sub>DDC</sub> brownout detection

<sup>1)</sup> SAK product variant does not support power-down mode.

#### 3.11 Multiplication/Division Unit

The Multiplication/Division Unit (MDU) provides fast 16-bit multiplication, 16-bit and 32-bit division as well as shift and normalize features. It has been integrated to support the XC87x Core in real-time control applications, which require fast mathematical computations.

#### Features

- Fast signed/unsigned 16-bit multiplication

- Fast signed/unsigned 32-bit divide by 16-bit and 16-bit divide by 16-bit operations

- 32-bit unsigned normalize operation

- 32-bit arithmetic/logical shift operations

Table 29 specifies the number of clock cycles used for calculation in various operations.

| Operation                | Result | Remainder | No. of Clock Cycles<br>used for calculation |

|--------------------------|--------|-----------|---------------------------------------------|

| Signed 32-bit/16-bit     | 32-bit | 16-bit    | 33                                          |

| Signed 16-bit/16bit      | 16-bit | 16-bit    | 17                                          |

| Signed 16-bit x 16-bit   | 32-bit | -         | 16                                          |

| Unsigned 32-bit/16-bit   | 32-bit | 16-bit    | 32                                          |

| Unsigned 16-bit/16-bit   | 16-bit | 16-bit    | 16                                          |

| Unsigned 16-bit x 16-bit | 32-bit | -         | 16                                          |

| 32-bit normalize         | -      | -         | No. of shifts + 1 (Max. 32)                 |

| 32-bit shift L/R         | -      | -         | No. of shifts + 1 (Max. 32)                 |

Table 29

MDU Operation Characteristics

#### 3.12 CORDIC Coprocessor

The CORDIC Coprocessor provides CPU with hardware support for the solving of circular (trigonometric), linear (multiply-add, divide-add) and hyperbolic functions.

#### Features

- Modes of operation

- Supports all CORDIC operating modes for solving circular (trigonometric), linear (multiply-add, divide-add) and hyperbolic functions

- Integrated look-up tables (LUTs) for all operating modes

- Circular vectoring mode: Extended support for values of initial X and Y data up to full range of [-2<sup>15</sup>,(2<sup>15</sup>-1)] for solving angle and magnitude

- Circular rotation mode: Extended support for values of initial Z data up to full range of  $[-2^{15},(2^{15}-1)]$ , representing angles in the range  $[-\pi,((2^{15}-1)/2^{15})\pi]$  for solving trigonometry

- Implementation-dependent operational frequency of up to 80 MHz

- Gated clock input to support disabling of module

- 16-bit accessible data width

- 24-bit kernel data width plus 2 overflow bits for X and Y each

- 20-bit kernel data width plus 1 overflow bit for Z

- With KEEP bit to retain the last value in the kernel register for a new calculation

- 16 iterations per calculation: Approximately 41 clock-cycles or less, from set of start (ST) bit to set of end-of-calculation flag, excluding time taken for write and read access of data bytes.

- Twos complement data processing

- Only exception: X result data with user selectable option for unsigned result

- X and Y data generally accepted as integer or rational number; X and Y must be of the same data form

- Entries of LUTs are 20-bit signed integers

- Entries of atan and atanh LUTs are integer representations (S19) of angles with the scaling such that  $[-2^{15},(2^{15}-1)]$  represents the range  $[-\pi,((2^{15}-1)/2^{15})\pi]$

- Accessible Z result data for circular and hyperbolic functions is integer in data form of S15

- Emulated LUT for linear function

- Data form is 1 integer bit and 15-bit fractional part (1.15)

- Accessible Z result data for linear function is rational number with fixed data form of S4.11 (signed 4Q16)

- Truncation Error

- The result of a CORDIC calculation may return an approximation due to truncation of LSBs

- Good accuracy of the CORDIC calculated result data, especially in circular mode

- Interrupt

- On completion of a calculation

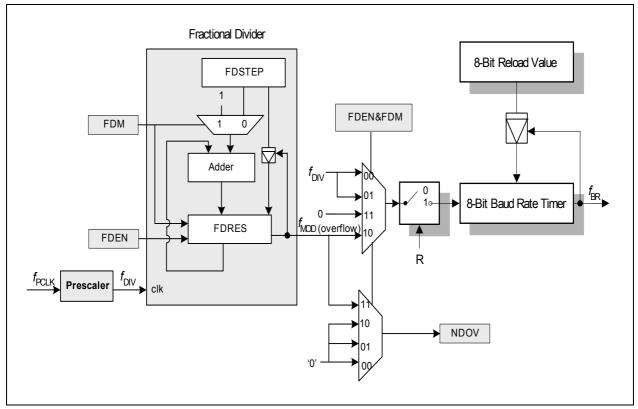

fractional divider) for generating a wide range of baud rates based on its input clock  $f_{\text{PCLK}}$ , see **Figure 26**.

#### Figure 26Baud-rate Generator Circuitry

The baud rate timer is a count-down timer and is clocked by either the output of the fractional divider ( $f_{MOD}$ ) if the fractional divider is enabled (FDCON.FDEN = 1), or the output of the prescaler ( $f_{DIV}$ ) if the fractional divider is disabled (FDEN = 0). For baud rate generation, the fractional divider must be configured to fractional divider mode (FDCON.FDM = 0). This allows the baud rate control run bit BCON.R to be used to start or stop the baud rate timer. At each timer underflow, the timer is reloaded with the 8-bit reload value in register BG and one clock pulse is generated for the serial channel.

Enabling the fractional divider in normal divider mode (FDEN = 1 and FDM = 1) stops the baud rate timer and nullifies the effect of bit BCON.R. See **Section 3.14**.

The baud rate ( $f_{BR}$ ) value is dependent on the following parameters:

- Input clock  $f_{PCLK}$

- Prescaling factor (2<sup>BRPRE</sup>) defined by bit field BRPRE in register BCON

- Fractional divider (STEP/256) defined by register FDSTEP (to be considered only if fractional divider is enabled and operating in fractional divider mode)

- 8-bit reload value (BR\_VALUE) for the baud rate timer defined by register BG

### XC87xCLM

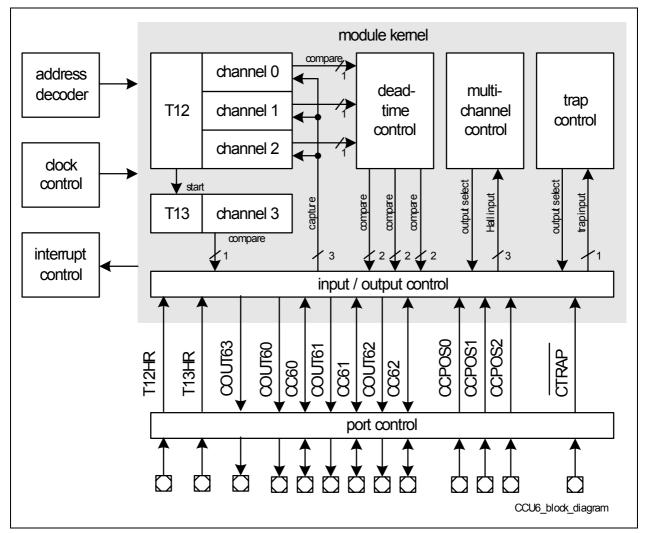

Figure 29 CCU6 Block Diagram

#### **Electrical Parameters**

#### 4.1.3 Operating Conditions

The following operating conditions must not be exceeded in order to ensure correct operation of the XC87x. All parameters mentioned in the following table refer to these operating conditions, unless otherwise noted.

| Table 39 | Operating | Condition | Parameters |

|----------|-----------|-----------|------------|

|----------|-----------|-----------|------------|

| Parameter                         | Symbol            | Limit Values |                     | Unit | Notes/        |

|-----------------------------------|-------------------|--------------|---------------------|------|---------------|

|                                   |                   | min.         | max.                |      | Conditions    |

| Digital power supply voltage      | $V_{DDP}$         | 4.5          | 5.5                 | V    | 5V Device     |

| Digital power supply voltage      | V <sub>DDP</sub>  | 3.0          | 3.6                 | V    | 3.3V Device   |

| Digital ground voltage            | V <sub>SS</sub>   | 0            |                     | V    |               |

| CPU Clock Frequency <sup>1)</sup> | f <sub>cclk</sub> |              | 26.67 <sup>2)</sup> | MHz  |               |

| Ambient temperature               | T <sub>A</sub>    | -40          | 85                  | °C   | SAF-XC878/874 |

|                                   |                   | -40          | 105                 | °C   | SAX-XC878     |

|                                   |                   | -40          | 125                 | °C   | SAK-XC878/874 |

1)  $f_{CCLK}$  is the input frequency to the XC800 core. Please refer to Figure 22 for detailed description.

2)Default setting of  $f_{CCLK}$  upon reset is 24 MHz.

#### **Electrical Parameters**

# Table 45Power Supply Current Parameters<sup>1)</sup> (Operating Conditions apply; $V_{\text{DDP}} = 3.3V$ range)

| Parameter                          | Symbol           | Limit Values       |                    | Unit | Test       |

|------------------------------------|------------------|--------------------|--------------------|------|------------|

|                                    |                  | typ. <sup>2)</sup> | max. <sup>3)</sup> |      | Conditions |

| $V_{\text{DDP}}$ = 3.3V Range      |                  |                    |                    |      |            |

| Active Mode                        | I <sub>DDP</sub> | 35.4               | 43                 | mA   | 4)         |

| Idle Mode                          | I <sub>DDP</sub> | 27.6               | 33                 | mA   | 5)         |

| Active Mode with slow-down enabled | I <sub>DDP</sub> | 8.6                | 13                 | mA   | 6)         |

| Idle Mode with slow-down enabled   | I <sub>DDP</sub> | 8                  | 12                 | mA   | 7)         |

1) The table is only applicable to SAF and SAX variants.

2) The typical  $I_{\text{DDP}}$  values are based on preliminary measurements and are to be used as reference only. These values are periodically measured at  $T_{\text{A}}$  = + 25 °C and  $V_{\text{DDP}}$  = 3.3 V.

3) The maximum  $I_{\text{DDP}}$  values are measured under worst case conditions ( $T_{\text{A}}$  = + 105 °C and  $V_{\text{DDP}}$  = 3.6 V).

4)  $I_{\text{DDP}}$  (active mode) is measured with: CPU clock and input clock to all peripherals running at 24 MHz with onchip oscillator of 4 MHz, RESET =  $V_{\text{DDP}}$ ; all other pins are disconnected, no load on ports.

5)  $I_{\text{DDP}}$  (idle mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 24 MHz, RESET =  $V_{\text{DDP}}$ ; all other pins are disconnected, no load on ports.

- 6)  $I_{\text{DDP}}$  (active mode with slow-down mode) is measured with: CPU clock and input clock to all peripherals running at 1 MHz by setting CLKREL in CMCON to  $1000_{\text{B}}$ ,  $\overline{\text{RESET}} = V_{\text{DDP}}$ ; all other pins are disconnected, no load on ports.

- 7)  $I_{\text{DDP}}$  (idle mode with slow-down mode) is measured with: CPU clock disabled, watchdog timer disabled, input clock to all peripherals enabled and running at 1 MHz by setting CLKREL in CMCON to  $1000_{\text{B}}$ , RESET =  $V_{\text{DDP}}$ ; all other pins are disconnected, no load on ports.

#### Package and Quality Declaration

# 5.3 Quality Declaration

Table 57 shows the characteristics of the quality parameters in the XC87x.

| Table 57 | Quality Parameters |

|----------|--------------------|

|----------|--------------------|

| Parameter                                                                       | Symbol           | Limit Values |       | Unit  | Notes                                  |

|---------------------------------------------------------------------------------|------------------|--------------|-------|-------|----------------------------------------|

|                                                                                 |                  | Min.         | Max.  |       |                                        |

| Operation Lifetime when<br>the device is used at the<br>two stated $T_J^{(1)}$  | t <sub>OP1</sub> | -            | 15000 | hours | $T_{\rm J} = 110^{\circ}{\rm C}$       |

|                                                                                 |                  | -            | 2000  | hours | $T_{\rm J}$ = -40°C                    |

| Operation Lifetime when<br>the device is used at the<br>five stated $T_J^{(1)}$ | t <sub>OP2</sub> | -            | 120   | hours | $T_{\rm J} = 140^{\circ}{\rm C}$       |

|                                                                                 |                  | -            | 960   | hours | <i>T</i> <sub>J</sub> = 135°C          |

|                                                                                 |                  | -            | 7800  | hours | $T_{\rm J} = 91^{\circ}{\rm C}$        |

|                                                                                 |                  | -            | 2400  | hours | $T_{\rm J} = 38^{\circ}{\rm C}$        |

|                                                                                 |                  | -            | 720   | hours | $T_{\rm J}$ = -25°C                    |

| ESD susceptibility<br>according to Human Body<br>Model (HBM)                    | V <sub>HBM</sub> | -            | 2000  | V     | Conforming to<br>EIA/JESD22-<br>A114-B |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM) pins           | V <sub>CDM</sub> | -            | 750   | V     | Conforming to<br>JESD22-C101-C         |

1) This lifetime refers only to the time when device is powered-on.