Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                             |

| Core Processor             | SH-2                                                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, SCI, SSU                                     |

| Peripherals                | POR, PWM, WDT                                                                   |

| Number of I/O              | 57                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 12x12b                                                                      |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LFQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df71374an80fpv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

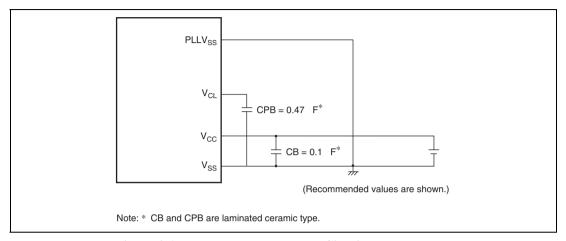

A circuitry shown in figure 4.6 is recommended as an external circuitry around the PLL. Separate the PLL power lines (PLLVss) and the system power lines (Vcc, Vss) at the board power supply source, and be sure to insert bypass capacitors CB and CPB close to the pins.

Figure 4.6 Recommended External Circuitry around PLL

|     |          | Initial |     |                                                                                                                                                                   |

|-----|----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                                       |

| 15  | SCMFCA   | 0       | R/W | L Bus Cycle Condition Match Flag A                                                                                                                                |

|     |          |         |     | When the L bus cycle condition in the break conditions set for channel A is satisfied, this flag is set to 1. In order to clear this flag, write 0 into this bit. |

|     |          |         |     | 0: The L bus cycle condition for channel A does not match                                                                                                         |

|     |          |         |     | 1: The L bus cycle condition for channel A matches                                                                                                                |

| 14  | SCMFCB   | 0       | R/W | L Bus Cycle Condition Match Flag B                                                                                                                                |

|     |          |         |     | When the L bus cycle condition in the break conditions set for channel B is satisfied, this flag is set to 1. In order to clear this flag, write 0 into this bit. |

|     |          |         |     | The L bus cycle condition for channel B does not match                                                                                                            |

|     |          |         |     | 1: The L bus cycle condition for channel B matches                                                                                                                |

| 13  | SCMFDA   | 0       | R/W | I Bus Cycle Condition Match Flag A                                                                                                                                |

|     |          |         |     | When the I bus cycle condition in the break conditions set for channel A is satisfied, this flag is set to 1. In order to clear this flag, write 0 into this bit. |

|     |          |         |     | 0: The I bus cycle condition for channel A does not match                                                                                                         |

|     |          |         |     | 1: The I bus cycle condition for channel A matches                                                                                                                |

| 12  | SCMFDB   | 0       | R/W | I Bus Cycle Condition Match Flag B                                                                                                                                |

|     |          |         |     | When the I bus cycle condition in the break conditions set for channel B is satisfied, this flag is set to 1. In order to clear this flag, write 0 into this bit. |

|     |          |         |     | The I bus cycle condition for channel B does not match                                                                                                            |

|     |          |         |     | 1: The I bus cycle condition for channel B matches                                                                                                                |

| 11  | PCTE     | 0       | R/W | PC Trace Enable                                                                                                                                                   |

|     |          |         |     | 0: Disables PC trace                                                                                                                                              |

|     |          |         |     | 1: Enables PC trace                                                                                                                                               |

**Table 10.35 TIOC4C Output Level Select Function**

| Bit 3 | Function  |

|-------|-----------|

| טונט  | i unclion |

|       |                |                     | Compare Match Output |            |  |  |  |  |  |

|-------|----------------|---------------------|----------------------|------------|--|--|--|--|--|

| OLS2N | Initial Output | <b>Active Level</b> | Up Count             | Down Count |  |  |  |  |  |

| 0     | High level     | Low level           | High level           | Low level  |  |  |  |  |  |

| 1     | Low level      | High level          | Low level            | High level |  |  |  |  |  |

Note: The reverse phase waveform initial output value changes to the active level after elapse of the dead time after count start.

## **Table 10.36 TIOC4A Output Level Select Function**

| Bit 2 |                |                     | Function   | ction              |  |  |  |  |  |

|-------|----------------|---------------------|------------|--------------------|--|--|--|--|--|

|       | -              |                     | Com        | npare Match Output |  |  |  |  |  |

| OLS2P | Initial Output | <b>Active Level</b> | Up Count   | Down Count         |  |  |  |  |  |

| 0     | High level     | Low level           | Low level  | High level         |  |  |  |  |  |

| 1     | Low level      | High level          | High level | Low level          |  |  |  |  |  |

## Table 10.37 TIOC3D Output Level Select Function

| Bit 1 |                |                     | Function             |            |  |  |  |  |  |  |  |

|-------|----------------|---------------------|----------------------|------------|--|--|--|--|--|--|--|

|       |                |                     | Compare Match Output |            |  |  |  |  |  |  |  |

| OLS1N | Initial Output | <b>Active Level</b> | Up Count             | Down Count |  |  |  |  |  |  |  |

| 0     | High level     | Low level           | High level           | Low level  |  |  |  |  |  |  |  |

| 1     | Low level      | High level          | Low level            | High level |  |  |  |  |  |  |  |

Note: The reverse phase waveform initial output value changes to the active level after elapse of the dead time after count start.

# **Table 10.38 TIOC4B Output Level Select Function**

| Bit 0 | Function       |                     |                      |            |  |  |  |  |  |  |  |

|-------|----------------|---------------------|----------------------|------------|--|--|--|--|--|--|--|

|       |                |                     | Compare Match Output |            |  |  |  |  |  |  |  |

| OLS1P | Initial Output | <b>Active Level</b> | Up Count             | Down Count |  |  |  |  |  |  |  |

| 0     | High level     | Low level           | Low level            | High level |  |  |  |  |  |  |  |

| 1     | Low level      | High level          | High level           | Low level  |  |  |  |  |  |  |  |

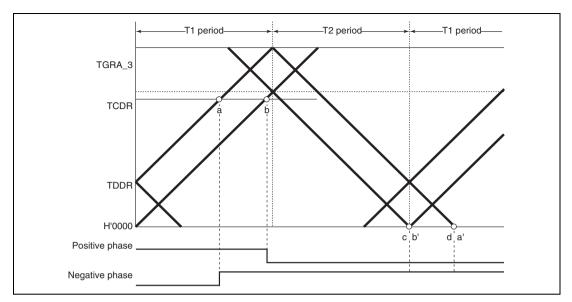

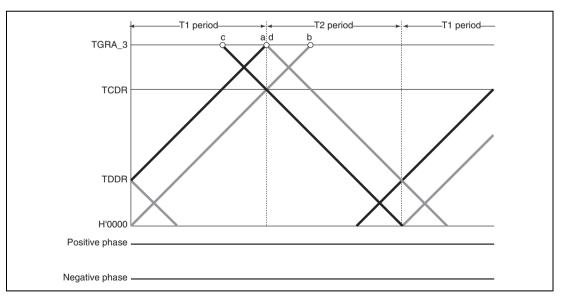

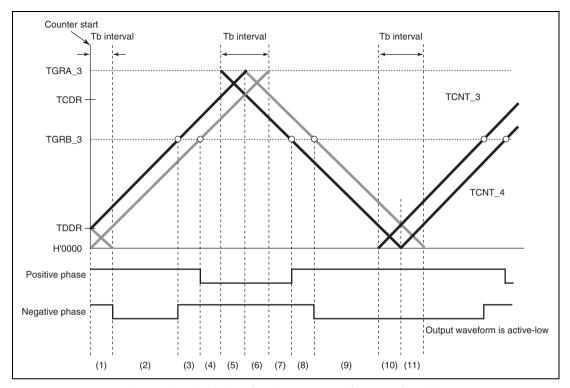

### 7. PWM Cycle Setting

In complementary PWM mode, the PWM pulse cycle is set in two registers—TGRA\_3, in which the TCNT\_3 upper limit value is set, and TCDR, in which the TCNT\_4 upper limit value is set. The settings should be made so as to achieve the following relationship between these two registers:

With dead time: TGRA\_3 set value = TCDR set value + TDDR set value Without dead time: TGRA\_3 set value = TCDR set value + 1

The TGRA\_3 and TCDR settings are made by setting the values in buffer registers TGRC\_3 and TCBR. The values set in TGRC\_3 and TCBR are transferred simultaneously to TGRA\_3 and TCDR in accordance with the transfer timing selected with bits MD3 to MD0 in the timer mode register (TMDR).

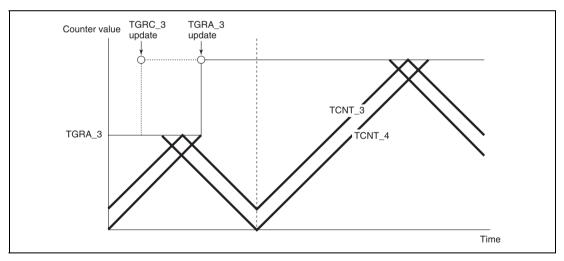

The updated PWM cycle is reflected from the next cycle when the data update is performed at the crest, and from the current cycle when performed in the trough. Figure 10.42 illustrates the operation when the PWM cycle is updated at the crest.

See the following section, Register Data Updating, for the method of updating the data in each buffer register.

Figure 10.42 Example of PWM Cycle Updating

Figure 10.52 Example of Complementary PWM Mode 0% and 100% Waveform Output (4)

Figure 10.53 Example of Complementary PWM Mode 0% and 100% Waveform Output (5)

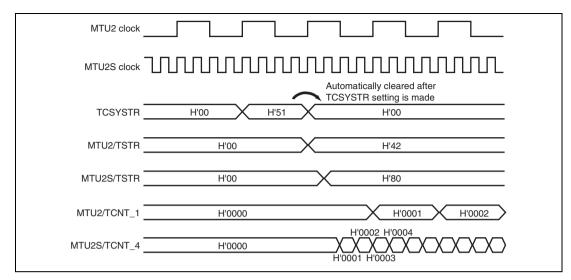

Figure 10.56 Timing for Synchronous Counter Clearing

Figure 10.84 (4) Example of Synchronous Counter Start Operation (MTU2-to-MTU2S Clock Frequency Ratio = 1:4)

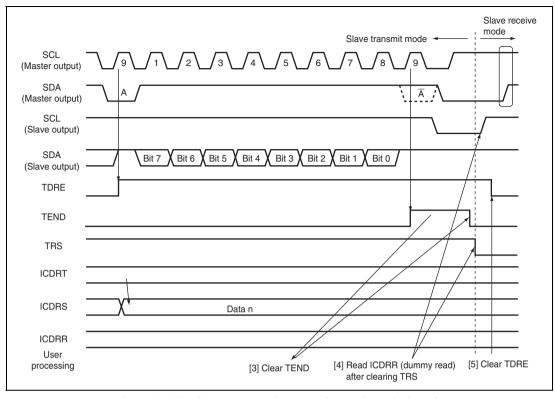

Figure 16.10 Slave Transmit Mode Operation Timing (2)

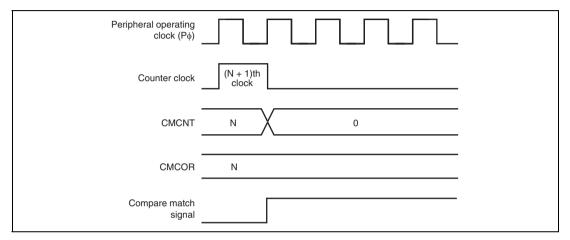

### 18.4.2 Timing of Setting Compare Match Flag

When CMCOR and CMCNT match, a compare match signal is generated and the CMF bit in CMCSR is set to 1. The compare match signal is generated in the last cycle in which the values match (when the CMCNT value is updated to H'0000). That is, after a match between CMCOR and CMCNT, the compare match signal is not generated until the next CMCNT counter clock input. Figure 18.4 shows the timing of CMF bit setting.

Figure 18.4 Timing of CMF Setting

## 18.4.3 Timing of Clearing Compare Match Flag

The CMF bit in CMCSR is cleared by reading 1 from this bit, then writing 0.

#### Mailbox-0

| Bit           | : 15 | 14 | 13  | 12 | 11 | 10  | 9       | 8   | 7 | 6 | 5 | 4 | 3   | 2   | 1     | 0   |

|---------------|------|----|-----|----|----|-----|---------|-----|---|---|---|---|-----|-----|-------|-----|

|               | 0    | 0  | NMC | 0  | 0  |     | MBC[2:0 | ]   | 0 | 0 | 0 | 0 |     | DLC | [3:0] |     |

| Initial value | : 0  | 0  | 0   | 0  | 0  | 1   | 1       | 1   | 0 | 0 | 0 | 0 | 0   | 0   | 0     | 0   |

| R/W           | : R  | R  | R/W | R  | R  | R/W | R/W     | R/W | R | R | R | R | R/W | R/W | R/W   | R/W |

Note: MBC[1] of MB0 is always "1".

#### Mailbox-15 to 1

| Bit            | : 15 | 14 | 13  | 12  | 11   | 10  | 9       | 8   | 7 | 6 | 5 | 4 | 3   | 2   | 1     | 0   |

|----------------|------|----|-----|-----|------|-----|---------|-----|---|---|---|---|-----|-----|-------|-----|

| [              | 0    | 0  | NMC | ATX | DART |     | MBC[2:0 | ]   | 0 | 0 | 0 | 0 |     | DLC | [3:0] |     |

| Initial value: | : 0  | 0  | 0   | 0   | 0    | 1   | 1       | 1   | 0 | 0 | 0 | 0 | 0   | 0   | 0     | 0   |

| R/W            | : R  | R  | R/W | R/W | R/W  | R/W | R/W     | R/W | R | R | R | R | R/W | R/W | R/W   | R/W |

**NMC** (**New Message Control**): When this bit is set to '0', the Mailbox of which the RXPR or RFPR bit is already set does not store the new message but maintains the old one and sets the UMSR correspondent bit. When this bit is set to '1', the Mailbox of which the RXPR or RFPR bit is already set overwrites with the new message and sets the UMSR correspondent bit.

**Important:** Please note that if a remote frame is overwritten with a data frame or vice versa could be that both RXPR and RFPR flags (together with UMSR) are set for the same Mailbox. In this case the RTR bit within the Mailbox Control Field should be relied upon.

| NMC | Description                  |

|-----|------------------------------|

| 0   | Overrun mode (Initial value) |

| 1   | Overwrite mode               |

ATX (Automatic Transmission of Data Frame): When this bit is set to '1' and a Remote Frame is received into the Mailbox DLC is stored. Then, a Data Frame is transmitted from the same Mailbox using the current contents of the message data and updated DLC by setting the corresponding TXPR automatically. The scheduling of transmission is still governed by ID priority or Mailbox priority as configured with the Message Transmission Priority control bit (MCR.2). In order to use this function, MBC[2:0] needs to be programmed to be '001' (Bin). When a transmission is performed by this function, the DLC (Data Length Code) to be used is the one that has been received. Application needs to guarantee that the DLC of the remote frame correspond to the DLC of the data frame requested.

**Important:** When ATX is used and MBC=001 (Bin) the filter for the IDE bit cannot be used since ID of remote frame has to be exactly the same as that of data frame as the reply message.

## SH7132/SH7137:

# • Port B Control Register L2 (PBCRL2)

| Bit:           | 15 | 14         | 13         | 12         | 11 | 10         | 9          | 8          | 7 | 6          | 5          | 4          | 3 | 2          | 1          | 0          |

|----------------|----|------------|------------|------------|----|------------|------------|------------|---|------------|------------|------------|---|------------|------------|------------|

| [              | -  | PB7<br>MD2 | PB7<br>MD1 | PB7<br>MD0 | -  | PB6<br>MD2 | PB6<br>MD1 | PB6<br>MD0 | - | PB5<br>MD2 | PB5<br>MD1 | PB5<br>MD0 | - | PB4<br>MD2 | PB4<br>MD1 | PB4<br>MD0 |

| Initial value: | 0  | 0          | 0          | 0          | 0  | 0          | 0          | 0          | 0 | 0          | 0          | 0          | 0 | 0          | 0          | 0          |

| R/W:           | R  | R/W        | R/W        | R/W        | R  | R/W        | R/W        | R/W        | R | R/W        | R/W        | R/W        | R | R/W        | R/W        | R/W        |

|     |          | Initial |     |                                                                   |

|-----|----------|---------|-----|-------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                       |

| 15  | _        | 0       | R   | Reserved                                                          |

|     |          |         |     | This bit is always read as 0. The write value should always be 0. |

| 14  | PB7MD2   | 0       | R/W | PB7 Mode                                                          |

| 13  | PB7MD1   | 0       | R/W | Select the function of the PB7/CS1/CRx0 pin.                      |

| 12  | PB7MD0   | 0       | R/W | 000: PB7 I/O (port)                                               |

|     |          |         |     | 101: CS1 output (BSC)*                                            |

|     |          |         |     | 110: CRx0 input (RCAN-ET)                                         |

|     |          |         |     | Other than above: Setting prohibited                              |

| 11  | _        | 0       | R   | Reserved                                                          |

|     |          |         |     | This bit is always read as 0. The write value should always be 0. |

| 10  | PB6MD2   | 0       | R/W | PB6 Mode                                                          |

| 9   | PB6MD1   | 0       | R/W | Select the function of the PB6/WAIT/CTx0 pin.                     |

| 8   | PB6MD0   | 0       | R/W | 000: PB6 I/O (port)                                               |

|     |          |         |     | 101: WAIT input (BSC)*                                            |

|     |          |         |     | 110: CTx0 output (RCAN-ET)                                        |

|     |          |         |     | Other than above: Setting prohibited                              |

| 7   | _        | 0       | R   | Reserved                                                          |

|     |          |         |     | This bit is always read as 0. The write value should always be 0. |

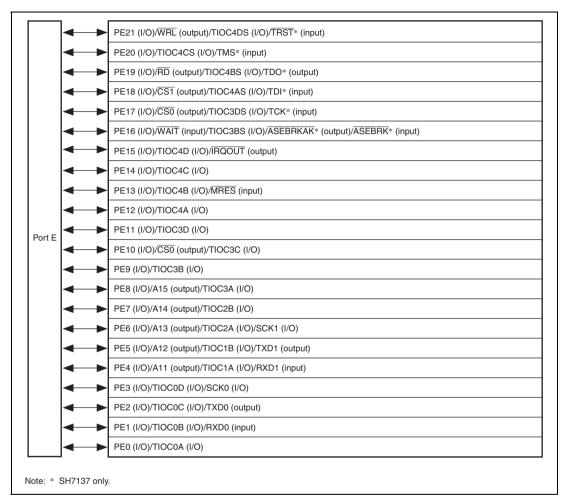

Port E in the SH7132 and SH7137 is an input/output port with the 22 pins shown in figure 21.7.

Figure 21.7 Port E (SH7132/SH7137)

All commands in the above table, except for the boot program state inquiry command (H'4F), are valid until the boot program accepts the transition-to-programming/erasure state command (H'40). That is, until the transition command is accepted, the host can continue to send commands listed in the above table until it has made the necessary inquiries and selections. The host can send the boot program state inquiry command (H'4F) even after acceptance of the transition-to-programming/erasure state command (H'40) by the boot program.

### (1) Inquiry on supported devices

In response to the inquiry on supported devices, the boot program returns the device codes of the devices it supports and the product names of their respective boot programs.

Command H'20

— Command H'20 (1 byte): Inquiry on supported devices

#### Response

| H'30                 | Size        | No. of devices |              |

|----------------------|-------------|----------------|--------------|

| Number of characters | Device code |                | Product name |

|                      |             |                |              |

| SUM                  |             |                |              |

- Response H'30 (1 byte): Response to the inquiry on supported devices

- Size (1 byte): The length of data for transfer excluding the command code, this field (size), and the checksum. Here, it is the total number of bytes taken up by the number of devices, number of characters, device code, and product name fields.

- Number of devices (1 byte): The number of device models supported by the boot program embedded in the microcomputer.

- Number of characters (1 byte): The number of characters in the device code and product name fields.

- Device code (4 bytes): Device code of a supported device (ASCII encoded)

- Product name (n bytes): Product code of the boot program (ASCII encoded)

- SUM (1 byte): Checksum

This is set so that the total sum of all bytes from the command code to the checksum is H'00.

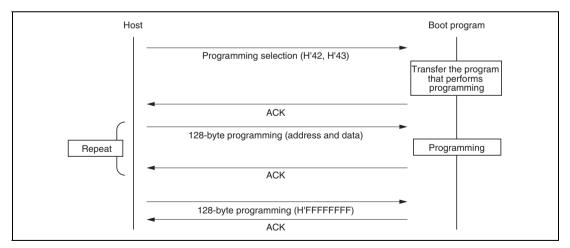

### Programming

Programming is performed by issuing a programming-selection command and the 128-byte programming command.

Firstly, the host issues the programming-selection command to select the MAT to be programmed. Two programming-selection commands are provided for the selection of either of the two target areas.

- 1. Selection of user boot MAT programming

- 2. Selection of user MAT programming

Next, the host issues a 128-byte programming command. 128 bytes of data for programming by the method selected by the preceding programming selection command are expected to follow the command. To program more than 128 bytes, repeatedly issue 128-byte programming commands. To terminate programming, the host should send another 128-byte programming command with the address H'FFFFFFF. On completion of programming, the boot program waits for the next programming/erasure selection command.

To then program the other MAT, start by sending the programming select command.

The sequence of programming by programming-selection and 128-byte programming commands is shown in figure 22.26.

Figure 22.26 Sequence of Programming

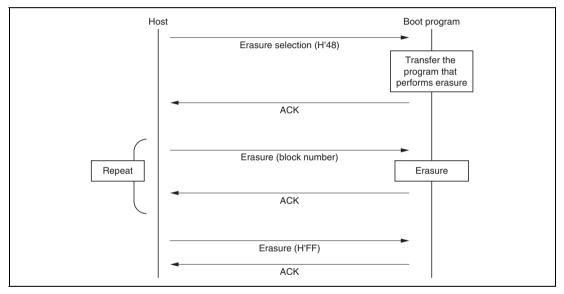

#### Erasure

Erasure is performed by issuing the erasure selection command and then one or more block erasure commands.

Firstly, the host sends the erasure selection command to select erasure; after that, it sends a block erasure command to actually erase a specific block. To erase multiple blocks, send further block erasure commands. To terminate erasure, the host should send a block erasure command with the block number H'FF. After this, the boot program waits for the next programming/erasure selection command.

The sequence of erasure by the erasure selection command and block erasure command is shown in figure 22.27.

Figure 22.27 Sequence of Erasure

| Register Name                                                    | Abbreviation   | No. of<br>Bits | Address    | Module | Access Size | No. of Access Cycles          | Connected<br>Bus Width |

|------------------------------------------------------------------|----------------|----------------|------------|--------|-------------|-------------------------------|------------------------|

| Timer A/D converter start request cycle set register B_4S        | TADCORB_4<br>S | 16             | H'FFFFC646 | MTU2S  | 16          | MIφ (reference clock)<br>B: 2 | 16 bits                |

| Timer A/D converter start request cycle set buffer register A_4S | TADCOBRA_4S    | 16             | H'FFFFC648 | -      | 16, 32      | W: 2<br>L: 4                  |                        |

| Timer A/D converter start request cycle set buffer register B_4S | TADCOBRB_4S    | 16             | H'FFFFC64A | _      | 16          |                               |                        |

| Timer synchronous clear register S                               | TSYCRS         | 8              | H'FFFFC650 | _      | 8           |                               |                        |

| Timer waveform control register S                                | TWCRS          | 8              | H'FFFC660  | _      | 8           | •                             |                        |

| Timer start register S                                           | TSTRS          | 8              | H'FFFFC680 | _      | 8, 16       | •                             |                        |

| Timer synchronous register S                                     | TSYRS          | 8              | H'FFFFC681 | =      | 8           | •                             |                        |

| Timer read/write enable register S                               | TRWERS         | 8              | H'FFFFC684 | =      | 8           | •                             |                        |

| Timer counter U_5S                                               | TCNTU_5S       | 16             | H'FFFFC880 | _      | 16, 32      | •                             |                        |

| Timer general register U_5S                                      | TGRU_5S        | 16             | H'FFFFC882 | _      | 16          | •                             |                        |

| Timer control register U_5S                                      | TCRU_5S        | 8              | H'FFFFC884 | _      | 8           | •                             |                        |

| Timer I/O control register U_5S                                  | TIORU_5S       | 8              | H'FFFC886  | -      | 8           | •                             |                        |

| Timer counter V_5S                                               | TCNTV_5S       | 16             | H'FFFFC890 | -      | 16, 32      | •                             |                        |

| Timer general register V_5S                                      | TGRV_5S        | 16             | H'FFFFC892 | -      | 16          | •                             |                        |

| Timer control register V_5S                                      | TCRV_5S        | 8              | H'FFFC894  | =      | 8           | •                             |                        |

| Timer I/O control register V_5S                                  | TIORV_5S       | 8              | H'FFFFC896 | _      | 8           | •                             |                        |

| Timer counter W_5S                                               | TCNTW_5S       | 16             | H'FFFFC8A0 | -      | 16, 32      | •                             |                        |

| Timer general register W_5S                                      | TGRW_5S        | 16             | H'FFFFC8A2 | -      | 16          | •                             |                        |

| Timer control register W_5S                                      | TCRW_5S        | 8              | H'FFFC8A4  | -      | 8           | •                             |                        |

| Timer I/O control register W_5S                                  | TIORW_5S       | 8              | H'FFFC8A6  | -      | 8           | •                             |                        |

| Timer status register_5S                                         | TSR_5S         | 8              | H'FFFFC8B0 | -      | 8           | •                             |                        |

| Timer interrupt enable register_5S                               | TIER_5S        | 8              | H'FFFFC8B2 | _      | 8           | •                             |                        |

| Timer start register_5S                                          | TSTR_5S        | 8              | H'FFFC8B4  | -      | 8           | •                             |                        |

| Timer compare match clear register S                             | TCNTCMPCLRS    | 8              | H'FFFFC8B6 | -      | 8           | •                             |                        |

| Flash code control/status register                               | FCCS           | 8              | H'FFFFCC00 | FLASH  | 8           | Pφ (reference clock)          | 16 bits                |

| Flash program code select register                               | FPCS           | 8              | H'FFFFCC01 | _      | 8           | B: 5                          |                        |

| Flash erase code select register                                 | FECS           | 8              | H'FFFFCC02 | _      | 8           | •                             |                        |

| Flash key code register                                          | FKEY           | 8              | H'FFFFCC04 | _      | 8           | •                             |                        |

| Register<br>Abbreviation | Power-on reset | Manual reset | Software<br>Standby | Deep Software<br>Standby | Module<br>Standby | Sleep    | Module       |

|--------------------------|----------------|--------------|---------------------|--------------------------|-------------------|----------|--------------|

| BARA                     | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | UBC          |

| BAMRA                    | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | ='           |

| BBRA                     | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | ='           |

| BDRA                     | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | -            |

| BDMRA                    | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | -            |

| BARB                     | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | ='           |

| BAMRB                    | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | -            |

| BBRB                     | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | -            |

| BDRB                     | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | -            |

| BDMRB                    | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | -            |

| BRCR                     | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | -            |

| BRSR                     | Initialized    | Initialized  | Retained            | Initialized              | Initialized       | Retained | ='           |

| BRDR                     | Initialized    | Initialized  | Retained            | Initialized              | Initialized       | Retained | <del>-</del> |

| BETR                     | Initialized    | Retained     | Retained            | Initialized              | Initialized       | Retained | -            |

Notes: 1. Not initialized by a WDT power-on reset.

- 2. The OSCSTOP bit is not initialized by a WDT power-on reset.

- 3. The OSCSTOP bit is initialized.

| Item                                       |                                                                                 | Symbol             | Min.                 | Тур. | Max. | Unit | Test<br>Conditions                                                                                                             |

|--------------------------------------------|---------------------------------------------------------------------------------|--------------------|----------------------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------|

| Three-state<br>leak current<br>(OFF state) | Ports A, B, D, E                                                                | l l <sub>tsi</sub> | _                    | _    | 1.0  | μΑ   |                                                                                                                                |

| Output high-                               | All output pins                                                                 | $V_{\text{OH}}$    | V <sub>cc</sub> -0.5 | _    | _    | V    | $I_{\text{OH}} = -200 \ \mu\text{A}$                                                                                           |

| level voltage                              |                                                                                 |                    | V <sub>cc</sub> -1.0 | _    | _    | V    | $I_{OH} = -1 \text{ mA}$                                                                                                       |

|                                            | TIOC3B, TIOC3D, TIOC4A to TIOC4D, TIOC3BS, TIOC3DS, TIOC4AS to TIOC4DS          | -                  | V <sub>cc</sub> -1.0 | _    | _    | V    | I <sub>OH</sub> = -5 mA                                                                                                        |

|                                            | PE9, PE11 to PE21                                                               | -                  | V <sub>cc</sub> -2.0 | _    | _    | V    | I <sub>OH</sub> = -5 mA                                                                                                        |

| Output low-                                | All output pins                                                                 | V <sub>OL</sub>    | _                    | _    | 0.4  | ٧    | I <sub>oL</sub> = 1.6 mA                                                                                                       |

| level voltage                              | SCL, SDA                                                                        | -                  | _                    | _    | 0.4  | ٧    | I <sub>oL</sub> = 3 mA                                                                                                         |

|                                            |                                                                                 |                    | _                    | _    | 0.5  | V    | I <sub>oL</sub> = 8 mA                                                                                                         |

|                                            | TIOC3B, TIOC3D,<br>TIOC4A to TIOC4D,<br>TIOC3BS, TIOC3DS,<br>TIOC4AS to TIOC4DS | -                  |                      | _    | 1.4  | V    | I <sub>OL</sub> = 15 mA                                                                                                        |

|                                            | PE9, PE11 to PE21                                                               | _                  | _                    | _    | 1.5  | V    | I <sub>oL</sub> = 15 mA                                                                                                        |

| Input capacitance                          | All input pins                                                                  | C <sub>in</sub>    | _                    |      | 20   | pF   | $V_{in} = 0 \text{ V}$ $f = 1 \text{ MHz}$ $Ta = 25^{\circ}\text{C}$                                                           |

| Supply current                             | Normal operation                                                                | I <sub>cc</sub>    | _                    | 80   | 105  | mA   | $I\phi = 80 \text{ MHz}$ $B\phi = 40 \text{ MHz}$ $P\phi = 40 \text{ MHz}$ $MP\phi = 40 \text{ MHz}$ $MI\phi = 80 \text{ MHz}$ |

|                                            | Sleep                                                                           | -                  | _                    | 55   | 85   | mA   | $B\phi = 40 \text{ MHz}$<br>$P\phi = 40 \text{ MHz}$<br>$MP\phi = 40 \text{ MHz}$<br>$MI\phi = 80 \text{ MHz}$                 |

|                                            | Software standby                                                                | =                  | _                    | 8    | 20   | mA   | $T_a \le 50^{\circ}C$                                                                                                          |

|                                            |                                                                                 |                    |                      |      | 30   | mA   | 50°C < T <sub>a</sub>                                                                                                          |

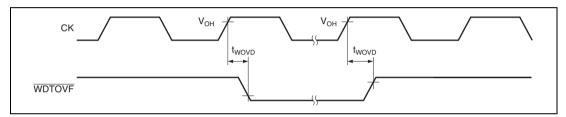

## 26.3.7 Watchdog Timer (WDT) Timing

## Table 26.12 Watchdog Timer (WDT) Timing

Conditions:  $V_{cc} = 3.0 \text{ V}$  to 3.6 V or 4.0 V to 5.5 V,  $AV_{cc} = 4.5 \text{ V}$  to 5.5 V,  $AV_{refh} = 4.5 \text{ V}$  to  $AV_{cc}$ ,  $AV_{ss} = PLLV_{ss} = AV_{ss} = AV_{refl} = 0 \text{ V}$ ,  $AV_{refl} = 0 \text{ V}$ ,  $AV_{cc} = 0 \text{ V}$ ,  $AV_{c$

| Item              | Symbol            | Min. | Max. | Unit | Reference<br>Figure |

|-------------------|-------------------|------|------|------|---------------------|

| WDTOVF delay time | t <sub>wovd</sub> | _    | 50   | ns   | Figure 26.20        |

Figure 26.20 WDT Timing