Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 40                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 18K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 9x10b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-64-6                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe162fn16f80laafxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Edition 2013-02 Published by Infineon Technologies AG 81726 Munich, Germany © 2013 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

**Summary of Features**

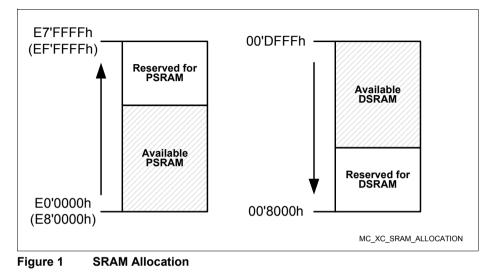

For example 8 Kbytes of PSRAM will be allocated at E0'0000h-E0'1FFFh and 8 Kbytes of DSRAM will be at 00'C000h-00'DFFFh.

## XE162FN, XE162HN XE166 Family / Value Line

## **General Device Information**

| Table | Table 5Pin Definitions and Functions (cont'd) |        |      |                                                   |  |  |

|-------|-----------------------------------------------|--------|------|---------------------------------------------------|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                          |  |  |

| 47    | P10.7                                         | O0 / I | St/B | Bit 7 of Port 10, General Purpose Input/Output    |  |  |

|       | U0C1_DOUT                                     | 01     | St/B | USIC0 Channel 1 Shift Data Output                 |  |  |

|       | CCU60_COU<br>T63                              | O2     | St/B | CCU60 Channel 3 Output                            |  |  |

|       | U0C1_DX0B                                     | I      | St/B | USIC0 Channel 1 Shift Data Input                  |  |  |

|       | CCU60_CCP<br>OS0A                             | 1      | St/B | CCU60 Position Input 0                            |  |  |

|       | T4INB                                         | I      | St/B | GPT12E Timer T4 Count/Gate Input                  |  |  |

| 51    | P10.8                                         | O0 / I | St/B | Bit 8 of Port 10, General Purpose Input/Output    |  |  |

|       | U0C0_MCLK<br>OUT                              | 01     | St/B | USIC0 Channel 0 Master Clock Output               |  |  |

|       | U0C1_SELO<br>0                                | 02     | St/B | USIC0 Channel 1 Select/Control 0 Output           |  |  |

|       | U2C1_DOUT                                     | O3     | St/B | USIC2 Channel 1 Shift Data Output                 |  |  |

|       | CCU60_CCP<br>OS1A                             | I      | St/B | CCU60 Position Input 1                            |  |  |

|       | U0C0_DX1C                                     | I      | St/B | USIC0 Channel 0 Shift Clock Input                 |  |  |

|       | BRKIN_B                                       | I      | St/B | OCDS Break Signal Input                           |  |  |

|       | T3EUDB                                        | 1      | St/B | GPT12E Timer T3 External Up/Down Control<br>Input |  |  |

## XE162FN, XE162HN XE166 Family / Value Line

#### **Functional Description**

With this hardware most XE162xN instructions are executed in a single machine cycle of 12.5 ns @ 80-MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 wordwide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XE162xN instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

## XE162FN, XE162HN XE166 Family / Value Line

## **Functional Description**

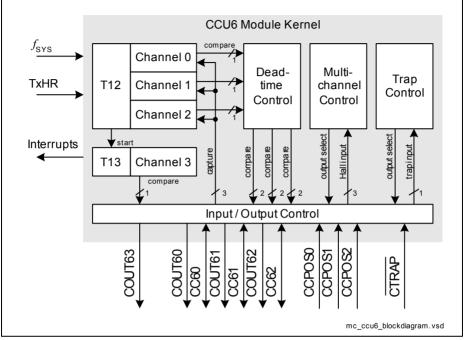

### Figure 7 CCU6 Block Diagram

Timer T12 can work in capture and/or compare mode for its three channels. The modes can also be combined. Timer T13 can work in compare mode only. The multi-channel control unit generates output patterns that can be modulated by timer T12 and/or timer T13. The modulation sources can be selected and combined for signal modulation.

### **Functional Description**

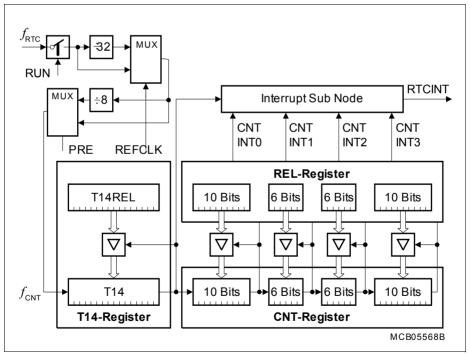

## 3.10 Real Time Clock

The Real Time Clock (RTC) module of the XE162xN can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of: – a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

### Figure 10 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

### **Functional Description**

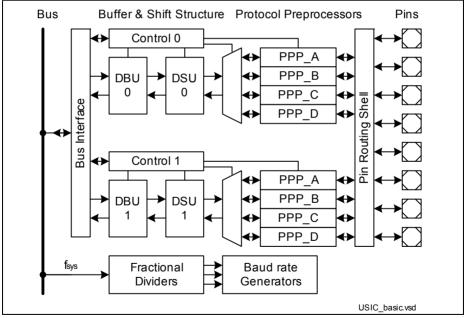

# 3.12 Universal Serial Interface Channel Modules (USIC)

The XE162xN features the USIC modules USIC0, USIC1, USIC2. Each module provides two serial communication channels.

The Universal Serial Interface Channel (USIC) module is based on a generic data shift and data storage structure which is identical for all supported serial communication protocols. Each channel supports complete full-duplex operation with a basic data buffer structure (one transmit buffer and two receive buffer stages). In addition, the data handling software can use FIFOs.

The protocol part (generation of shift clock/data/control signals) is independent of the general part and is handled by protocol-specific preprocessors (PPPs).

The USIC's input/output lines are connected to pins by a pin routing unit. The inputs and outputs of each USIC channel can be assigned to different interface pins, providing great flexibility to the application software. All assignments can be made during runtime.

### Figure 11 General Structure of a USIC Module

The regular structure of the USIC module brings the following advantages:

- Higher flexibility through configuration with same look-and-feel for data management

- Reduced complexity for low-level drivers serving different protocols

- Wide range of protocols with improved performances (baud rate, buffer handling)

## 4.1.1 Operating Conditions

The following operating conditions must not be exceeded to ensure correct operation of the XE162xN. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Note: Typical parameter values refer to room temperature and nominal supply voltage, minimum/maximum parameter values also include conditions of minimum/maximum temperature and minimum/maximum supply voltage. Additional details are described where applicable.

| Parameter                                                        | Symbol                 | Values |                           |                           | Unit | Note /                                                              |

|------------------------------------------------------------------|------------------------|--------|---------------------------|---------------------------|------|---------------------------------------------------------------------|

|                                                                  |                        | Min.   | Тур.                      | Max.                      |      | Test Condition                                                      |

| Voltage Regulator Buffer<br>Capacitance for DMP_M                | $C_{\rm EVRM}$ SR      | 1.0    | -                         | 4.7                       | μF   | 1)                                                                  |

| Voltage Regulator Buffer<br>Capacitance for DMP_1                | $C_{\rm EVR1}$ SR      | 0.47   | -                         | 2.2                       | μF   | 2)1)                                                                |

| External Load<br>Capacitance                                     | $C_{L}$ SR             | -      | 20 <sup>3)</sup>          | -                         | pF   | pin out<br>driver= default                                          |

| System frequency                                                 | $f_{\rm SYS}{\rm SR}$  | -      | -                         | 80                        | MHz  | 5)                                                                  |

| Overload current for analog inputs <sup>6)</sup>                 | $I_{\rm OVA}{\rm SR}$  | -2     | -                         | 5                         | mA   | not subject to production test                                      |

| Overload current for digital inputs <sup>6)</sup>                | $I_{\rm OVD}{\rm SR}$  | -5     | -                         | 5                         | mA   | not subject to production test                                      |

| Overload current coupling factor for analog inputs <sup>7)</sup> | K <sub>OVA</sub><br>CC | -      | 2.5 x<br>10 <sup>-4</sup> | 1.5 x<br>10 <sup>-3</sup> | -    | <i>I</i> <sub>OV</sub> < 0 mA; not<br>subject to<br>production test |

|                                                                  |                        | _      | 1.0 x<br>10 <sup>-6</sup> | 1.0 x<br>10 <sup>-4</sup> | -    | I <sub>OV</sub> > 0 mA; not<br>subject to<br>production test        |

## Table 12 Operating Conditions

| Parameter                         | Symbol             | Values                 |      |      | Unit | Note /                                       |

|-----------------------------------|--------------------|------------------------|------|------|------|----------------------------------------------|

|                                   |                    | Min.                   | Тур. | Max. |      | Test Condition                               |

| Output High voltage <sup>7)</sup> | V <sub>OH</sub> CC | V <sub>DDP</sub> - 1.0 | -    | -    | V    | $I_{\rm OH} \ge I_{\rm OHmax}$               |

|                                   |                    | V <sub>DDP</sub> - 0.4 | -    | -    | V    | $I_{\text{OH}} \ge I_{\text{OHnom}}^{8}$     |

| Output Low Voltage <sup>7)</sup>  | V <sub>OL</sub> CC | -                      | -    | 0.4  | V    | $I_{\rm OL} \le I_{\rm OLnom}$ <sup>8)</sup> |

|                                   |                    | -                      | -    | 1.0  | V    | $I_{\rm OL} \leq I_{\rm OLmax}$              |

#### Table 15 DC Characteristics for Upper Voltage Range (cont'd)

1) Because each double bond pin is connected to two pads (standard pad and high-speed pad), it has twice the normal value. For a list of affected pins refer to the pin definitions table in chapter 2.

Not subject to production test - verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 3) If the input voltage exceeds the respective supply voltage due to ground bouncing ( $V_{\rm IN} < V_{\rm SS}$ ) or supply ripple ( $V_{\rm IN} > V_{\rm DDP}$ ), a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current ( $I_{\rm INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm CV}$ .

- 4) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (*T*<sub>J</sub> = junction temperature [°C]): *I*<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 x T,J>)</sup> [µA]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 µA. Leakage derating depending on voltage level (DV = *V*<sub>DDP</sub> *V*<sub>PIN</sub> [V]): *I*<sub>OZ</sub> = *I*<sub>OZtempmax</sub> (1.6 x DV) (µA]. This voltage derating formula is an approximation which applies for maximum temperature.

- Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device.

- 6) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level.

- 7) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 8) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL}$ -> $V_{SS}$ ,  $V_{OH}$ -> $V_{DDP}$ ). However, only the levels for nominal output currents are verified.

| Parameter                         | Symbol             | Values                 |      |      | Unit | Note /                                   |  |

|-----------------------------------|--------------------|------------------------|------|------|------|------------------------------------------|--|

|                                   |                    | Min.                   | Тур. | Max. |      | Test Condition                           |  |

| Output High voltage <sup>7)</sup> | V <sub>OH</sub> CC | V <sub>DDP</sub> - 1.0 | _    | -    | V    | $I_{\text{OH}} \ge I_{\text{OHmax}}$     |  |

|                                   |                    | V <sub>DDP</sub> - 0.4 | -    | -    | V    | $I_{\text{OH}} \ge I_{\text{OHnom}}^{8}$ |  |

| Output Low Voltage <sup>7)</sup>  | V <sub>OL</sub> CC | -                      | -    | 0.4  | V    | $I_{\rm OL} \le I_{\rm OLnom}^{8)}$      |  |

|                                   |                    | -                      | -    | 1.0  | V    | $I_{\rm OL} \le I_{\rm OLmax}$           |  |

#### Table 16 DC Characteristics for Lower Voltage Range (cont'd)

1) Because each double bond pin is connected to two pads (standard pad and high-speed pad), it has twice the normal value. For a list of affected pins refer to the pin definitions table in chapter 2.

Not subject to production test - verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 3) If the input voltage exceeds the respective supply voltage due to ground bouncing ( $V_{\rm IN} < V_{\rm SS}$ ) or supply ripple ( $V_{\rm IN} > V_{\rm DDP}$ ), a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current ( $I_{\rm INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm CV}$ .

- 4) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (*T*<sub>J</sub> = junction temperature [°C]): *I*<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 x T,J>)</sup> [µA]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 µA. Leakage derating depending on voltage level (DV = *V*<sub>DDP</sub> *V*<sub>PIN</sub> [V]): *I*<sub>OZ</sub> = *I*<sub>OZtempmax</sub> (1.6 x DV) (µA]. This voltage derating formula is an approximation which applies for maximum temperature.

- Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device: V<sub>PIN</sub> <= V<sub>IL</sub> for a pullup; V<sub>PIN</sub> >= V<sub>IH</sub> for a pulldown.

- 6) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level: V<sub>PIN</sub> >= V<sub>IL</sub> for a pullup; V<sub>PIN</sub> <= V<sub>IL</sub> for a pulldown.

- 7) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- 8) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL}$ -> $V_{SS}$ ,  $V_{OH}$ -> $V_{DDP}$ ). However, only the levels for nominal output currents are verified.

Sample time and conversion time of the XE162xN's A/D converters are programmable. The timing above can be calculated using Table 20.

The limit values for  $f_{ADCI}$  must not be exceeded when selecting the prescaler value.

| GLOBCTR.5-0<br>(DIVA) | A/D Converter<br>Analog Clock $f_{ADCI}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup><br>t <sub>S</sub> |

|-----------------------|------------------------------------------|---------------------|---------------------------------------------|

| 000000 <sub>B</sub>   | f <sub>SYS</sub>                         | 00 <sub>H</sub>     | $t_{ADCI} \times 2$                         |

| 000001 <sub>B</sub>   | f <sub>SYS</sub> / 2                     | 01 <sub>H</sub>     | $t_{ADCI} 	imes 3$                          |

| 000010 <sub>B</sub>   | f <sub>SYS</sub> / 3                     | 02 <sub>H</sub>     | $t_{ADCI} \times 4$                         |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                 | :                   | $t_{ADCI} \times (STC+2)$                   |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                    | FE <sub>H</sub>     | $t_{ADCI} 	imes 256$                        |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                    | FF <sub>H</sub>     | $t_{\rm ADCI} 	imes 257$                    |

Table 20

A/D Converter Computation Table

1) The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

### **Converter Timing Example A:**

| Assumptions:       | $f_{\rm SYS}$           | = 80 MHz (i.e. $t_{SYS}$ = 12.5 ns), DIVA = 03 <sub>H</sub> , STC = 00 <sub>H</sub>                  |  |  |  |  |

|--------------------|-------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

| Analog clock       | $f_{\sf ADCI}$          | $= f_{SYS} / 4 = 20 \text{ MHz}$ , i.e. $t_{ADCI} = 50 \text{ ns}$                                   |  |  |  |  |

| Sample time        | t <sub>S</sub>          | $= t_{ADCI} \times 2 = 100 \text{ ns}$                                                               |  |  |  |  |

| Conversion 10-bit: |                         |                                                                                                      |  |  |  |  |

|                    | <i>t</i> <sub>C10</sub> | = $13 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $13 \times 50$ ns + $2 \times 12.5$ ns = 0.675 $\mu$ s |  |  |  |  |

| Conversion 8-b     | oit:                    |                                                                                                      |  |  |  |  |

|                    | t <sub>C8</sub>         | = $11 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $11 \times 50$ ns + $2 \times 12.5$ ns = 0.575 $\mu$ s |  |  |  |  |

### **Converter Timing Example B:**

| Assumptions:   | $f_{\rm SYS}$           | = 40 MHz (i.e. $t_{SYS}$ = 25 ns), DIVA = 02 <sub>H</sub> , STC = 03 <sub>H</sub> |

|----------------|-------------------------|-----------------------------------------------------------------------------------|

| Analog clock   | $f_{\rm ADCI}$          | $= f_{SYS} / 3 = 13.3 \text{ MHz}$ , i.e. $t_{ADCI} = 75 \text{ ns}$              |

| Sample time    | t <sub>S</sub>          | $= t_{ADCI} \times 5 = 375 \text{ ns}$                                            |

| Conversion 10- | -bit:                   |                                                                                   |

|                | <i>t</i> <sub>C10</sub> | = $16 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 16 × 75 ns + 2 × 25 ns = 1.25 µs         |

| Conversion 8-b | oit:                    |                                                                                   |

|                | t <sub>C8</sub>         | = $14 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 14 × 75 ns + 2 × 25 ns = 1.10 µs         |

|                |                         |                                                                                   |

## 4.6 Flash Memory Parameters

The XE162xN is delivered with all Flash sectors erased and with no protection installed.

The data retention time of the XE162xN's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                  | Symbol                |      | Values          | 6               | Unit   | Note /<br>Test Condition                                                          |

|------------------------------------------------------------|-----------------------|------|-----------------|-----------------|--------|-----------------------------------------------------------------------------------|

|                                                            |                       | Min. | Тур.            | Max.            |        |                                                                                   |

| Parallel Flash module                                      | $N_{\rm PP}~{\rm SR}$ | -    | -               | 2 <sup>1)</sup> |        | $N_{\rm FL_RD} \leq 1$                                                            |

| program/erase limit<br>depending on Flash read<br>activity |                       | _    | -               | 1 <sup>2)</sup> |        | N <sub>FL_RD</sub> > 1                                                            |

| Flash erase endurance for security pages                   | $N_{\rm SEC}{ m SR}$  | 10   | -               | _               | cycles | $t_{\rm RET} \ge 20$ years                                                        |

| Flash wait states <sup>3)</sup>                            | $N_{\rm WSFLAS}$      | 1    | -               | -               |        | $f_{\rm SYS} \le 8  \rm MHz$                                                      |

|                                                            | <sub>н</sub> SR       | 2    | _               | _               |        | $f_{\rm SYS} \le 13 \ {\rm MHz}$                                                  |

|                                                            |                       | 3    | -               | -               |        | $f_{\rm SYS} \le 17 \ \rm MHz$                                                    |

|                                                            |                       | 4    | -               | -               |        | $f_{\rm SYS}$ > 17 MHz                                                            |

| Erase time per<br>sector/page                              | t <sub>ER</sub> CC    | _    | 7 <sup>4)</sup> | 8.0             | ms     |                                                                                   |

| Programming time per page                                  | t <sub>PR</sub> CC    | -    | 3 <sup>4)</sup> | 3.5             | ms     |                                                                                   |

| Data retention time                                        | t <sub>RET</sub> CC   | 20   | -               | -               | years  | $N_{\rm ER} \le$ 1,000 cycl es                                                    |

| Drain disturb limit                                        | $N_{\rm DD}{\rm SR}$  | 32   | -               | -               | cycles |                                                                                   |

| Number of erase cycles                                     | $N_{ER}SR$            | _    | -               | 15.000          | cycles | $t_{\text{RET}} \ge 5$ years;<br>Valid for Flash<br>module 1 (up to<br>64 kbytes) |

|                                                            |                       | -    | _               | 1.000           | cycles | $t_{\text{RET}} \ge 20 \text{ years}$                                             |

#### Table 24 Flash Parameters

The unused Flash module(s) can be erased/programmed while code is executed and/or data is read from only one Flash module or from PSRAM. The Flash module that delivers code/data can, of course, not be erased/programmed.

# 4.7.2 Definition of Internal Timing

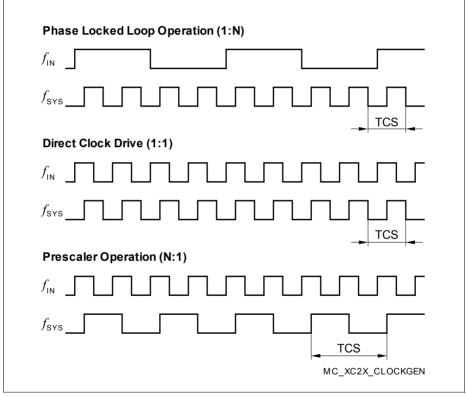

The internal operation of the XE162xN is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XE162xN.

Figure 19 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 19** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

## **Direct Drive**

When direct drive operation is selected (SYSCON0.CLKSEL =  $11_B$ ), the system clock is derived directly from the input clock signal CLKIN1:

$f_{\text{SYS}} = f_{\text{IN}}$ .

The frequency of  $f_{SYS}$  is the same as the frequency of  $f_{IN}$ . In this case the high and low times of  $f_{SYS}$  are determined by the duty cycle of the input clock  $f_{IN}$ .

Selecting Bypass Operation from the XTAL1<sup>1)</sup> input and using a divider factor of 1 results in a similar configuration.

### **Prescaler Operation**

When prescaler operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $1_B$ ), the system clock is derived either from the crystal oscillator (input clock signal XTAL1) or from the internal clock source through the output prescaler K1 (= K1DIV+1):

$f_{\text{SYS}} = f_{\text{OSC}} / \text{K1}.$

If a divider factor of 1 is selected, the frequency of  $f_{\rm SYS}$  equals the frequency of  $f_{\rm OSC}$ . In this case the high and low times of  $f_{\rm SYS}$  are determined by the duty cycle of the input clock  $f_{\rm OSC}$  (external or internal).

The lowest system clock frequency results from selecting the maximum value for the divider factor K1:

$f_{\rm SYS} = f_{\rm OSC} / 1024.$

## 4.7.2.1 Phase Locked Loop (PLL)

When PLL operation is selected (SYSCON0.CLKSEL =  $10_B$ , PLLCON0.VCOBY =  $0_B$ ), the on-chip phase locked loop is enabled and provides the system clock. The PLL multiplies the input frequency by the factor **F** ( $f_{SYS} = f_{IN} \times F$ ).

**F** is calculated from the input divider P (= PDIV+1), the multiplication factor N (= NDIV+1), and the output divider K2 (= K2DIV+1):

$(F = N / (P \times K2)).$

The input clock can be derived either from an external source at XTAL1 or from the onchip clock source.

The PLL circuit synchronizes the system clock to the input clock. This synchronization is performed smoothly so that the system clock frequency does not change abruptly.

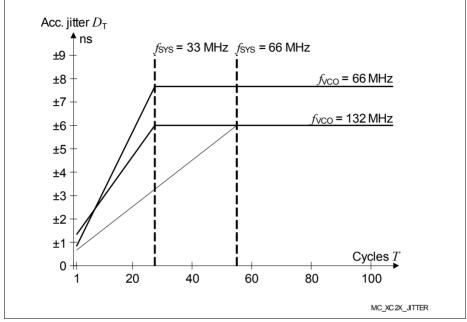

Adjustment to the input clock continuously changes the frequency of  $f_{\text{SYS}}$  so that it is locked to  $f_{\text{IN}}$ . The slight variation causes a jitter of  $f_{\text{SYS}}$  which in turn affects the duration of individual TCSs.

<sup>1)</sup> Voltages on XTAL1 must comply to the core supply voltage  $V_{\text{DDIM}}$ .

The timing in the AC Characteristics refers to TCSs. Timing must be calculated using the minimum TCS possible under the given circumstances.

The actual minimum value for TCS depends on the jitter of the PLL. Because the PLL is constantly adjusting its output frequency to correspond to the input frequency (from crystal or oscillator), the accumulated jitter is limited. This means that the relative deviation for periods of more than one TCS is lower than for a single TCS (see formulas and **Figure 20**).

This is especially important for bus cycles using waitstates and for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler K2 to generate the system clock signal  $f_{SYS}$ . The number of VCO cycles is K2 × **T**, where **T** is the number of consecutive  $f_{SYS}$  cycles (TCS).

The maximum accumulated jitter (long-term jitter) D<sub>Tmax</sub> is defined by:

$D_{\text{Tmax}}$  [ns] = ±(220 / (K2 ×  $f_{\text{SYS}}$ ) + 4.3)

This maximum value is applicable, if either the number of clock cycles T > ( $f_{SYS}$  / 1.2) or the prescaler value K2 > 17.

In all other cases for a timeframe of  $\mathbf{T} \times TCS$  the accumulated jitter  $D_T$  is determined by:

$D_{T}$  [ns] =  $D_{Tmax} \times [(1 - 0.058 \times K2) \times (T - 1) / (0.83 \times f_{SYS} - 1) + 0.058 \times K2]$

$f_{SYS}$  in [MHz] in all formulas.

Example, for a period of 3 TCSs @ 33 MHz and K2 = 4:

$D_{max} = \pm (220 / (4 \times 33) + 4.3) = 5.97$  ns (Not applicable directly in this case!)

$\mathsf{D_3} = 5.97 \times [(1 - 0.058 \times 4) \times (3 - 1) / (0.83 \times 33 - 1) + 0.058 \times 4]$

= 5.97 × [0.768 × 2 / 26.39 + 0.232]

Example, for a period of 3 TCSs @ 33 MHz and K2 = 2:

$D_{max} = \pm (220 / (2 \times 33) + 4.3) = 7.63$  ns (Not applicable directly in this case!)

$\begin{array}{l} \mathsf{D}_3 = 7.63 \times [(1 - 0.058 \times 2) \times (3 - 1) \, / \, (0.83 \times 33 - 1) + 0.058 \times 2] \\ = 7.63 \times [0.884 \times 2 \, / \, 26.39 + 0.116] \end{array}$

## XE162FN, XE162HN XE166 Family / Value Line

### **Electrical Parameters**

Figure 20 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_L$  = 20 pF.

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{\text{DDPB}}$  pin 64 and  $V_{\text{SS}}$  pin 1) is limited to a peak-to-peak voltage of  $V_{\text{PP}}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

### PLL frequency band selection

Different frequency bands can be selected for the VCO so that the operation of the PLL can be adjusted to a wide range of input and output frequencies:

- 1) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

- 2) Overload conditions must not occur on pin XTAL1.

### Figure 21 External Clock Drive XTAL1

Note: For crystal or ceramic resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation.

The manufacturers of crystals and ceramic resonators offer an oscillator evaluation service. This evaluation checks the crystal/resonator specification limits to ensure a reliable oscillator operation.

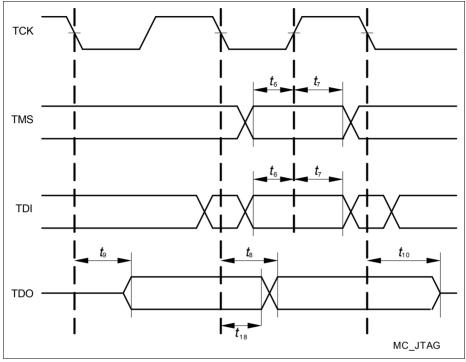

| Table 35 | JTAG Interface Timing for Upper Voltage Range (cont'd) |

|----------|--------------------------------------------------------|

|----------|--------------------------------------------------------|

| Parameter                                                                | Symbol                    | Values |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                          |                           | Min.   | Тур. | Max. |      | Test Condition |

| TCK low time                                                             | t <sub>3</sub> SR         | 16     | -    | -    | ns   |                |

| TCK clock rise time                                                      | $t_4$ SR                  | -      | -    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -      | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6      | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6      | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>2)</sup>        | t <sub>8</sub> CC         | -      | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>3)2)</sup> | t <sub>9</sub> CC         | -      | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>2)</sup>   | <i>t</i> <sub>10</sub> CC | -      | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>2)</sup>                            | <i>t</i> <sub>18</sub> CC | 5      | -    | -    | ns   |                |

1) Under typical conditions, the JTAG interface can operate at transfer rates up to 20 MHz.

2) The falling edge on TCK is used to generate the TDO timing.

3) The setup time for TDO is given implicitly by the TCK cycle time.

**Table 36** is valid under the following conditions:  $C_1 = 20 \text{ pF}$ ; voltage\_range= lower

| Parameter                        | Symbol            | Values |      |      | Unit | Note /         |

|----------------------------------|-------------------|--------|------|------|------|----------------|

|                                  |                   | Min.   | Тур. | Max. |      | Test Condition |

| TCK clock period                 | t <sub>1</sub> SR | 50     | -    | _    | ns   |                |

| TCK high time                    | t <sub>2</sub> SR | 16     | -    | -    | ns   |                |

| TCK low time                     | t <sub>3</sub> SR | 16     | -    | -    | ns   |                |

| TCK clock rise time              | t <sub>4</sub> SR | _      | -    | 8    | ns   |                |

| TCK clock fall time              | t <sub>5</sub> SR | _      | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge | t <sub>6</sub> SR | 6      | -    | -    | ns   |                |

Table 36

JTAG Interface Timing for Lower Voltage Range

## XE162FN, XE162HN XE166 Family / Value Line

### **Electrical Parameters**

Figure 27 JTAG Timing

### Package and Reliability

# Package Outlines

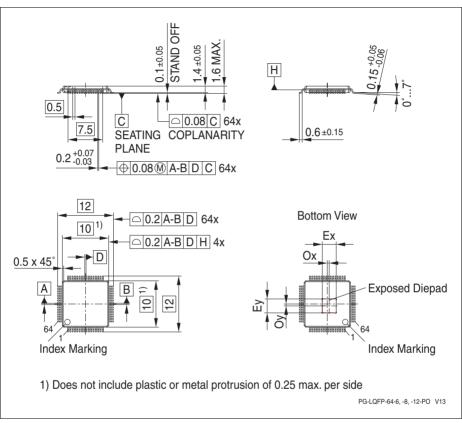

Figure 28 PG-LQFP-64-6 (Plastic Green Thin Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages