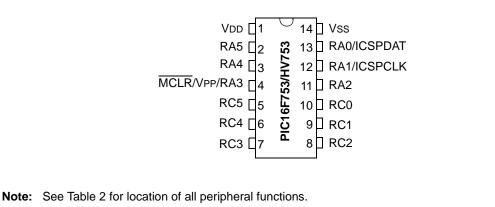

# Microchip Technology - PIC16F753-E/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 11                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x9b                                                     |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 14-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f753-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|  |  |  | - |  |  |   |

|--|--|--|---|--|--|---|

|  |  |  |   |  |  |   |

|  |  |  |   |  |  | 1 |

|  |  |  |   |  |  | 1 |

|  |  |  |   |  |  | 1 |

|  |  |  |   |  |  | 1 |

|  |  |  |   |  |  | 1 |

|  |  |  |   |  |  | 1 |

|  |  |  |   |  |  | 1 |

|  |  |  |   |  |  |   |

| 180h | INDF       |         |          |          | IND           | )F<7:0>            |            |          |           | XXXX XXXX | นนนน นนนน |

|------|------------|---------|----------|----------|---------------|--------------------|------------|----------|-----------|-----------|-----------|

| 181h | OPTION_REG | RAPU    | INTEDG   | TOCS     | TOSE          | PSA PS<2:0>        |            |          |           | 1111 1111 | 1111 1111 |

| 182h | PCL        |         |          |          |               | L<7:0>             | 1          |          |           | 0000 0000 | 0000 0000 |

| 183h | STATUS     | IRP     | RP1      | RP0      | TO            | PD                 | Z          | DC       | С         | 0001 1xxx | 000q quuu |

| 184h | FSR        |         |          |          | FSI           | R<7:0>             | •          | I.       |           | XXXX XXXX | uuuu uuuu |

| 185h | ANSELA     |         | _        | _        | ANSA4         | —                  | ANSA2      | ANSA1    | ANSA0     | 1 -111 -  | 1 -111    |

| 186h | _          |         |          |          | Unimp         | plemented          | •          |          |           | _         | _         |

| 187h | ANSELC     |         | _        | _        | _             | ANSC3              | ANSC2      | ANSC1    | ANSC0     | 0000      | 0000      |

| 188h | APFCON     | -       |          | -        | T1GSEL        | —                  | —          | —        | —         | 0         | -0        |

| 189h | OSCTUNE    | _       | _        | _        |               |                    | TUN<4:0>   | •        | •         | 0 0000    | 0 0000    |

| 18Ah | PCLATH     |         | _        | -        |               | Р                  | CLATH<4:0> |          |           | 0 0000    | 0 0000    |

| 18Bh | INTCON     | GIE     | PEIE     | TOIE     | INTE          | IOCIE              | T0IF       | INTF     | IOCIF     | 0000 0000 | 0000 0000 |

| 18Ch | PMCON1     | _       | _        | _        | _             | —                  | WREN       | WR       | RD        | 000 -     | 000       |

| 18Dh | PMCON2     |         |          |          | Program Memor | ry Control Registe | r 2        |          |           |           |           |

| 18Eh | PMADRL     |         |          |          | PMA           | ORL<7:0>           |            |          |           | 0000 0000 | 0000 0000 |

| 18Fh | PMADRH     | _       | _        | _        | _             | _                  | —          | 00       | 00        |           |           |

| 190h | PMDATL     |         |          |          | PMD           | ATL<7:0>           |            |          |           | 0000 0000 | 0000 0000 |

| 191h | PMDATH     | _       |          |          |               | PMDATH             |            |          |           | 00 0000   | 00 0000   |

| 192h | COG1PHR    | —       |          | —        | _             |                    | G1PHR      | <3:0>    |           | XXXX      | uuuu      |

| 193h | COG1PHF    | _       |          | _        |               |                    | G1PHF      |          |           | XXXX      | uuuu      |

| 194h | COG1BKR    | _       | _        | _        | —             |                    | G1BKR      |          |           | XXXX      | uuuu      |

| 195h | COG1BKF    | _       | _        | —        | —             |                    | G1BKF      |          |           | XXXX      | uuuu      |

| 196h | COG1DBR    | _       |          | _        | _             |                    | G1DBR      |          |           | XXXX      | uuuu      |

| 197h | COG1DBF    | _       | —        | —        | _             |                    | G1DBF      | <3:0>    | 1         | XXXX      | uuuu      |

| 198h | COG1CON0   | G1EN    | G10E1    | G1OE0    | G1POL1        | G1POL0             | G1LD       | —        | G1MD      | 0000 00-0 | 0000 00-0 |

| 199h | COG1CON1   | G1RDBTS | G1FDBTS  | _        | _             | _                  | _          | G1CS     | 5<1:0>    | 0000      | 0000      |

| 19Ah | COG1RIS    |         | G1RIHLT2 | G1RIHLT1 | G1RIT2M       | G1RIFLT            | G1RICCP1   | G1RIC2   | G1RIC1    | 0000 0000 | 0000 0000 |

| 19Bh | COG1RSIM   |         | G1RMHLT2 | G1RMHLT1 | G1RMT2M       | G1RMFLT            | G1RMCCP1   | G1RMC2   | G1RMC1    | 0000 0000 | 0000 0000 |

| 19Ch | COG1FIS    | _       | G1FIHLT2 | G1FIHLT1 | G1FIT2M       | G1FIFLT            | G1FICCP1   | G1FIC2   | G1FIC1    | 0000 0000 | 0000 0000 |

| 19Dh | COG1FSIM   |         | G1FMHLT2 | G1FMHLT1 | G1FMT2M       | G1FMFLT            | G1FMCCP1   | G1FMC2   | G1FMC1    | 0000 0000 | 0000 0000 |

| 19Eh | COG1ASD0   | C1ASDE  | C1ARSEN  | G1AS     | D1L<1:0>      | G1ASD0             | L<1:0>     | _        | _         | 0000 00   | 0000 00   |

| 19Fh | COG1ASD1   | _       | _        | _        | G1ASDSHLT2    | G1ASDSHLT1         | G1ASDSC2   | G1ASDSC1 | G1ASDSFLT | 0000 0000 | 0000 0000 |

- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition shaded = unimplemented

To read a program memory location, the user must write two bytes of the address to the PMADRL and PMADRH registers, and then set control bit RD (PMCON1<0>). Once the read control bit is set, the program memory Flash controller will use the second instruction cycle after to read the data. This causes the second instruction immediately following the "BSF PMCON1,RD instruction to be ignored. The data is available in the very next cycle in the PMDATL and PMDATH registers; it can be read as two bytes in the following instructions. PMDATL and PMDATH registers will hold this value until another read or until it is written to by the user (during a write operation).

| BANKSEL | PM_ADR        | ; Change STATUS bits RP1:0 to select bank with PMADRL     |

|---------|---------------|-----------------------------------------------------------|

| MOVLW   | MS_PROG_PM_AI | DDR ;                                                     |

| MOVWF   | PMADRH        | ; MS Byte of Program Address to read                      |

| MOVLW   | LS_PROG_PM_AD | DR ;                                                      |

| MOVWF   | PMADRL        | ; LS Byte of Program Address to read                      |

| BANKSEL | PMCON1        | ; Bank to containing PMCON1                               |

| BSF     | PMCON1, RD    | ; PM Read                                                 |

| NOP     |               | ; First instruction after BSF PMCON1,RD executes normally |

| NOP     |               | ; Any instructions here are ignored as program            |

|         |               | ; memory is read in second cycle after BSF PMCON1,RD<br>: |

| BANKSEL | PMDATL        | ; Bank to containing PMADRL                               |

| MOVF    | PMDATL, W     | ; W = LS Byte of Program PMDATL                           |

| MOVF    | PMDATH, W     | ; W = MS Byte of Program PMDATL                           |

The CLKOUT pin is available for general purpose I/O or system clock output. The CLKOUTEN bit of the Configuration Word controls the function of the CLKOUT pin.

When the CLKOUTEN bit is cleared, the CLKOUT pin is driven by the selected internal oscillator frequency divided by 4. The corresponding I/O pin always reads 'O' in this configuration.

The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

When the CLKOUTEN bit is set, the system clock out function is disabled and the CLKOUT pin is available for general purpose I/O.

In applications where the OSCTUNE register is used to shift the HFINTOSC frequency, the application should not expect the frequency to stabilize immediately. In this case, the frequency may shift gradually toward the new value. The time for this frequency shift is less than eight cycles of the base frequency.

A short delay is invoked upon power-up and when waking from sleep to allow the memory bias circuitry to stabilize. Table 4-1 shows examples where the oscillator delay is invoked.

| Sleep/POR | INTOSC | 31 kHz to 8 MHz | 10 B internal delay to allow memory |

|-----------|--------|-----------------|-------------------------------------|

| Sleep/POR | EC     | DC – 20 MHz     | bias to stabilize.                  |

| U-0                                                                                           | U-0                               | R/W-0/0                                                                                                                      | R/W-0/0                                                                    | R/W-0/0                                                                             | R/W-0/0            | R/W-0/0             | R/W-0/0           |

|-----------------------------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------|---------------------|-------------------|

| —                                                                                             | —                                 | IOCAP5                                                                                                                       | IOCAP4                                                                     | IOCAP3                                                                              | IOCAP2             | IOCAP1              | IOCAP0            |

| pit 7                                                                                         |                                   |                                                                                                                              |                                                                            |                                                                                     |                    |                     | bit 0             |

|                                                                                               |                                   |                                                                                                                              |                                                                            |                                                                                     |                    |                     |                   |

| R = Readable bit                                                                              |                                   | W = Writable b                                                                                                               | it                                                                         | U = Unimpleme                                                                       | ented bit, read as | ʻ0'                 |                   |

| u = Bit is unchang                                                                            | ed                                | x = Bit is unkno                                                                                                             | own                                                                        | -n/n = Value at                                                                     | POR and BOR/V      | alue at all other F | Resets            |

| 1' = Bit is set                                                                               |                                   | '0' = Bit is clear                                                                                                           | red                                                                        |                                                                                     |                    |                     |                   |

| bit 7-6                                                                                       |                                   | : Read as 'O'                                                                                                                |                                                                            |                                                                                     |                    |                     |                   |

| bit 5-0                                                                                       |                                   | Interrupt-on-Chai                                                                                                            | nae Positive Ed                                                            | ge Enable bits                                                                      |                    |                     |                   |

|                                                                                               | 1 = Interrupt-                    | -on-Change enabl                                                                                                             | 0                                                                          | 0                                                                                   | edge. Associate    | d Status bit and i  | nterrupt flag wil |

|                                                                                               |                                   | oon detecting an e                                                                                                           | 0                                                                          |                                                                                     |                    |                     |                   |

| (                                                                                             | 0 = Interrupt-                    | -on-Change disab                                                                                                             | led for the asso                                                           | clated pin.                                                                         |                    |                     |                   |

|                                                                                               |                                   |                                                                                                                              |                                                                            |                                                                                     |                    |                     |                   |

| 11-0                                                                                          | U-0                               | R/W-0/0                                                                                                                      | R/W-0/0                                                                    | R/W-0/0                                                                             | R/W-0/0            | R/W-0/0             | R/W-0/0           |

| U-0                                                                                           | U-0                               | R/W-0/0                                                                                                                      | R/W-0/0                                                                    | R/W-0/0                                                                             | R/W-0/0            | R/W-0/0             | R/W-0/0           |

| U-0<br>—                                                                                      | U-0<br>—                          |                                                                                                                              |                                                                            | 1 1                                                                                 |                    |                     |                   |

| _                                                                                             | U-0<br>—                          |                                                                                                                              |                                                                            | 1 1                                                                                 |                    |                     | IOCAN0            |

| bit 7                                                                                         | U-0<br>—                          | IOCAN5                                                                                                                       | IOCAN4                                                                     | IOCAN3                                                                              | IOCAN2             | IOCAN1              | IOCAN0            |

| bit 7<br>R = Readable bit                                                                     | _                                 | UOCAN5<br>W = Writable b                                                                                                     | IOCAN4                                                                     | U = Unimpleme                                                                       | IOCAN2             | 10CAN1              | IOCAN0<br>bit 0   |

| bit 7<br>Br = Readable bit<br>u = Bit is unchang                                              | _                                 | UOCAN5<br>W = Writable b<br>x = Bit is unkno                                                                                 | it                                                                         | U = Unimpleme                                                                       | IOCAN2             | IOCAN1              | IOCAN0<br>bit 0   |

| bit 7<br>R = Readable bit                                                                     | _                                 | UOCAN5<br>W = Writable b                                                                                                     | it                                                                         | U = Unimpleme                                                                       | IOCAN2             | 10CAN1              | IOCAN0<br>bit 0   |

| bit 7<br>Br = Readable bit<br>u = Bit is unchang                                              | _                                 | UOCAN5<br>W = Writable b<br>x = Bit is unkno                                                                                 | it                                                                         | U = Unimpleme                                                                       | IOCAN2             | 10CAN1              | IOCAN0<br>bit (   |

| —<br>bit 7<br>R = Readable bit<br>u = Bit is unchang<br>1' = Bit is set<br>bit 7-6<br>bit 5-0 | ed                                | W = Writable b<br>x = Bit is unkno<br>'0' = Bit is clean<br>: Read as '0'<br>Interrupt-on-Cha                                | IOCAN4<br>it<br>own<br>red                                                 | IOCAN3<br>U = Unimpleme<br>-n/n = Value at<br>dge Enable bits                       | IOCAN2             | IOCAN1              | IOCAN0<br>bit (   |

| —<br>bit 7<br>R = Readable bit<br>u = Bit is unchang<br>1' = Bit is set<br>bit 7-6<br>bit 5-0 | ed<br>1 = Interrupt-              | IOCAN5<br>W = Writable b<br>x = Bit is unkno<br>'0' = Bit is clean<br>: Read as '0'<br>Interrupt-on-Chai<br>-on-Change enabl | IOCAN4<br>it<br>own<br>red<br>nge Negative Ed                              | IOCAN3<br>U = Unimpleme<br>-n/n = Value at<br>dge Enable bits                       | IOCAN2             | IOCAN1              | IOCAN0<br>bit (   |

| —<br>bit 7<br>R = Readable bit<br>u = Bit is unchang<br>1' = Bit is set<br>bit 7-6<br>bit 5-0 | ed<br>1 = Interrupt-<br>be set up | IOCAN5<br>W = Writable b<br>x = Bit is unkno<br>'0' = Bit is clean<br>: Read as '0'<br>Interrupt-on-Cha                      | IOCAN4<br>it<br>own<br>red<br>nge Negative Ed<br>ed on the pin fo<br>edge. | IOCAN3<br>U = Unimpleme<br>-n/n = Value at<br>dge Enable bits<br>r a negative going | IOCAN2             | IOCAN1              | IOCAN0<br>bit     |

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | —   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| R = Readable bit   | W = Writable bit                                                                           | U = Unimplemented bit, read as '0'                                                                |

|--------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| u = Bit is unchang | ed x = Bit is unknown                                                                      | -n/n = Value at POR and BOR/Value at all other Resets                                             |

| '1' = Bit is set   | '0' = Bit is cleared                                                                       | HS - Bit is set in hardware                                                                       |

|                    |                                                                                            |                                                                                                   |

| bit 7-6            | : Read as 'O'                                                                              |                                                                                                   |

| bit 5-0            | Interrupt-on-Change Fla                                                                    | ig bits                                                                                           |

|                    | 1 = An enabled change was detected<br>Set when IOCAPx = 1 and a rising<br>detected on RAx. | l on the associated pin.<br>g edge was detected on RBx, or when IOCANx = 1 and a falling edge was |

|                    | 0 = No change was detected, or the u                                                       | user cleared the detected change.                                                                 |

| U-0   | U-0 | R/W-x/u | R/W-x/u | R-x/x | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|-------|---------|---------|---------|

| —     | _   | RC5     | RC4     | RC3   | RC2     | RC1     | RC0     |

| bit 7 |     |         |         |       |         |         | bit 0   |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Read as 'O'                     |

|---------|---------------------------------|

| bit 5-0 | : PORTC I/O Value bits          |

|         | 1 = Port pin is <u>&gt;</u> Viн |

|         | O = Port pin is <u>&lt;</u> VIL |

Г

Γ

Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R-1/1  | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|--------|---------|---------|---------|

| —     | —   | TRISC5  | TRISC4  | TRISC3 | TRISC2  | TRISC1  | TRISC0  |

| bit 7 |     |         |         |        |         |         | bit 0   |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Read as 'O'                                                                                |

|---------|--------------------------------------------------------------------------------------------|

| bit 5-0 | PORTC Tri-State Control bits                                                               |

|         | 1 = PORTC pin configured as an input (tri-stated)<br>0 = PORTC pin configured as an output |

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7 |     |         |         |         |         |         | bit 0   |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Read as 'O'

bit 5-0

Γ

: PORTC Output Latch Value bits

Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

Timer1 has four prescaler options allowing one, two, four or eight divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

If control bit  $\overline{T1SYNC}$  of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see

When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

).

#### 7.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair. Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 gate count enable.

Timer1 gate can also be driven by multiple selectable sources.

# 7.5.1 TIMER1 GATE COUNT ENABLE

The Timer1 gate is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 gate is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate (T1G) input is active, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 gate input is inactive, no incrementing will occur and Timer1 will hold the current count. See Figure 7-3 for timing details.

| n | 0 | 0 | Counts      |

|---|---|---|-------------|

| n | 0 | 1 | Holds Count |

| n | 1 | 0 | Holds Count |

| n | 1 | 1 | Counts      |

### 7.5.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

| 11 | SYNCC2OUT                                               |

|----|---------------------------------------------------------|

| 10 | SYNCC1OUT                                               |

| 01 | Overflow of Timer0<br>(TMR0 increments from FFh to 00h) |

| 00 | Timer1 Gate Pin                                         |

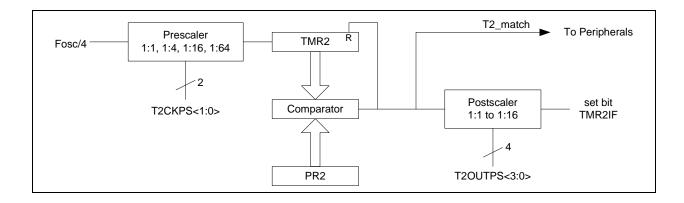

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16, 1:64)

- Software programmable postscaler (1:1 to 1:16)

See Figure 8-1 for a block diagram of Timer2.

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle.

- The Timer2 postscaler is incremented

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register. The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by clearing the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the T2OUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset).

TMR2 is not cleared when T2CON is written.

# 10.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

| CCP1CON | —            | _      | DC1B   | <1:0>  |                | CCP1M<            | 3:0>   | 1      | 80  |

|---------|--------------|--------|--------|--------|----------------|-------------------|--------|--------|-----|

| CCPR1L  |              |        |        | CCF    | PR1L<7:0>      |                   |        |        | 74  |

| CCPR1H  |              |        |        | CCP    | R1H<7:0>       |                   |        |        | 74  |

| INTCON  | GIE          | PEIE   | TOIE   | INTE   | IOCIE          | T0IF              | INTF   | IOCIF  | 17  |

| PIE1    | TMR1-<br>GIE | ADIE   | —      | —      | HLTMR2IE       | HLTMR1IE          | TMR2IE | TMR1IE | 18  |

| PIE2    | —            |        | C2IE   | C1IE   |                | COG1IE            |        | CCP1IE | 19  |

| PIR1    | TMR1-<br>GIF | ADIF   |        |        | HLTMR2IF       | HLTMR1IF          | TMR2IF | TMR1IF | 20  |

| PIR2    | —            |        | C2IF   | C1IF   |                | COG1IF            |        | CCP1IF | 21  |

| T1CON   | TMR1C        | S<1:0> | T1CKP  | S<1:0> | T1OSCEN        | T1SYNC            |        | TMR10N | 65  |

| T1GCON  | TMR1GE       | T1GPOL | T1GTM  | T1GSPM | T1GGO/<br>DONE | T1GVAL T1GSS<1:0> |        |        | 66  |

| TMR1H   | TMR1H<7:0>   |        |        |        |                |                   |        |        | 57* |

| TMR1L   |              |        |        | TMI    | R1L<7:0>       |                   |        |        | 57* |

| TRISA   | _            |        | TRISA5 | TRISA4 | TRISA3         | TRISA2            | TRISA1 | TRISA0 | 43  |

— = Unimplemented location, read as '0'. Shaded cells are not used by Compare mode.

\* Page provides register information. TRISA3 always reads '1'.

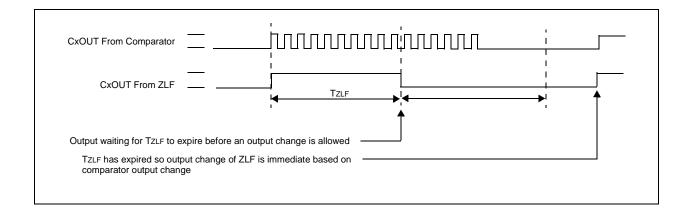

In high-speed operation, and under proper circuit conditions, it is possible for the comparator output to oscillate. This oscillation can have adverse effects on the hardware and software relying on this signal. Therefore, a digital filter has been added to the comparator output to suppress the comparator output oscillation. Once the comparator output changes, the output is prevented from reversing the change for a nominal time of 20 ns. This allows the comparator output to stabilize without affecting other dependent devices. Refer to Figure 15-3.

| CxINTP       CxINTN       CxPCH<1:0>       CxNCH<2:0>         bit 7         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         '1' = Bit is set       '0' = Bit is cleared       -n/n = Value at POR and BOR/Value at all other Res         bit 7       Comparator Interrupt on Positive Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit         0 = No interrupt flag will be set on a nositive Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = CxVP connects to CxIN+ pin         000 = CxVP connects to CxIN+ pin         001 = CxVP connects to CxINO- pin         001 = CxVN connects to CxINO- pin         001 = CxVN connects to CxINO- pin                                                                                                                                                 | R/W-0/0          | R/W-0/0                                 | R/W-0/0                                                                             | R/W-0/0          | R/W-0/0        | R/W-0/0        | R/W-0/0           | R/W-0/0      |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|-------------------------------------------------------------------------------------|------------------|----------------|----------------|-------------------|--------------|--|--|--|

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         '1' = Bit is set       '0' = Bit is cleared         bit 7       Comparator Interrupt on Positive Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit         0 = No interrupt flag will be set on a positive going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = CxVP connects to CxIN+ pin         0 = CxVP connects to AGND         0 = CxVP connects to CxIN0- pin         0 = CxVN connects to CxIN0- pin         0 = CxVN connects to CxIN2- pin <td>CxINTP</td> <td colspan="4">CxINTP CxINTN CxPCH&lt;1:0&gt;</td> <td></td> <td>CxNCH&lt;2:0&gt;</td> <td></td> | CxINTP           | CxINTP CxINTN CxPCH<1:0>                |                                                                                     |                  |                |                | CxNCH<2:0>        |              |  |  |  |

| u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         '1' = Bit is set       '0' = Bit is cleared         bit 7       Comparator Interrupt on Positive Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit         0 = No interrupt flag will be set on a positive going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = CxVP connects to CxIN+ pin         0 = CxVP connects to Slope Compensator Output         1xx = CxVP connects to CxIN0- pin         0 = Cx                                                                                   | bit 7            |                                         |                                                                                     |                  |                |                |                   | bit 0        |  |  |  |

| u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         '1' = Bit is set       '0' = Bit is cleared         bit 7       Comparator Interrupt on Positive Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit         0 = No interrupt flag will be set on a positive going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = CxVP connects to CxIN+ pin         0 = CxVP connects to Slope Compensator Output         1xx = CxVP connects to CxIN0- pin         0 = Cx                                                                                   |                  |                                         |                                                                                     |                  |                |                |                   |              |  |  |  |

| u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Res         '1' = Bit is set       '0' = Bit is cleared         bit 7       Comparator Interrupt on Positive Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit         0 = No interrupt flag will be set on a positive going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = CxVP connects to CxIN+ pin         0 = CxVP connects to Slope Compensator Output         1xx = CxVP connects to CxIN0- pin         0 = Cx                                                                                   |                  |                                         |                                                                                     |                  |                |                |                   |              |  |  |  |

| '1' = Bit is set       '0' = Bit is cleared         bit 7       Comparator Interrupt on Positive Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit         0 = No interrupt flag will be set on a positive going edge of the CxOUT bit         bit 6       Comparator Interrupt on Negative Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = CxVP connects to CxIN+ pin         0 = CxVP connects to AGND         bit 2-0       Comparator Negative Input Channel Select bits         0 = CxVN connects to CxIN0- pin <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>      |                  |                                         |                                                                                     |                  |                |                |                   |              |  |  |  |

| bit 7 Comparator Interrupt on Positive Going Edge Enable bit<br>1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit<br>0 = No interrupt flag will be set on a positive going edge of the CxOUT bit<br>bit 6 Comparator Interrupt on Negative Going Edge Enable bit<br>1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit<br>0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit<br>0 = No interrupt flag will be set on a negative going edge of the CxOUT bit<br>0 = No interrupt flag will be set on a negative going edge of the CxOUT bit<br>0 = No interrupt flag will be set on a negative going edge of the CxOUT bit<br>000 = CxVP connects to CxIN+ pin<br>001 = CxVP connects to dac_out<br>010 = CxVP connects to AGND<br>011 = CxVP connects to Slope Compensator Output<br>1xx = CxVP connects to AGND<br>bit 2-0 Comparator Negative Input Channel Select bits<br>000 = CxVN connects to CxIN0- pin<br>001 = CxVN connects to CxIN1- pin<br>010 = CxVN connects to CxIN2- pin<br>011 = CxVN connects to CxIN3- pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | u = Bit is unch  | anged                                   | x = Bit is unk                                                                      | nown             | -n/n = Value   | at POR and BO  | OR/Value at all c | other Resets |  |  |  |

| 1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit         0 = No interrupt flag will be set on a positive going edge of the CxOUT bit         bit 6       Comparator Interrupt on Negative Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = CxVP connects to CxIN+ pin         0 = CxVP connects to Slope Compensator Output         1 = CxVP connects to CxIN0- pin         0 = CxVN connects to CxIN0- pin         0 = CxVN connects to CxIN1- pin         0 = CxVN connects to CxIN2- pin         0 = CxVN connects to CxIN3- pin                                                                                                                                                                                       | '1' = Bit is set |                                         | '0' = Bit is cle                                                                    | eared            |                |                |                   |              |  |  |  |

| 1 = The CxIF interrupt flag will be set upon a positive going edge of the CxOUT bit         0 = No interrupt flag will be set on a positive going edge of the CxOUT bit         bit 6       Comparator Interrupt on Negative Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = CxVP connects to CxIN+ pin         0 = CxVP connects to Slope Compensator Output         1xx = CxVP connects to CxIN0- pin         0 = CxVN connects to CxIN0- pin         0 = CxVN connects to CxIN1- pin         0 = CxVN connects to CxIN2- pin         0 = CxVN connects to CxIN3- pin                                                                                                                                                                                       |                  |                                         |                                                                                     |                  |                |                |                   |              |  |  |  |

| 0 = No interrupt flag will be set on a positive going edge of the CxOUT bit         bit 6       Comparator Interrupt on Negative Going Edge Enable bit         1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         0 = CxVP connects to CXIN+ pin         0 = CxVN connects to CXIN0- pin         0 = CxVN connects to CXIN1- pin         0 = CxVN connects to CXIN2- pin         0 = CxVN connects to CXIN3- pin                                                                                                                                                                                                                                                                                               | bit 7            | Cor                                     | mparator Interr                                                                     | upt on Positive  | Going Edge E   | nable bit      |                   |              |  |  |  |

| bit 6 Comparator Interrupt on Negative Going Edge Enable bit<br>1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit<br>0 = No interrupt flag will be set on a negative going edge of the CxOUT bit<br>bit 5-3 Comparator Positive Input Channel Select bits<br>000 = CxVP connects to CxIN+ pin<br>001 = CxVP connects to dac_out<br>010 = CxVP connects to FVR<br>011 = CxVP connects to Slope Compensator Output<br>1xx = CxVP connects to AGND<br>bit 2-0 Comparator Negative Input Channel Select bits<br>000 = CxVN connects to CxIN0- pin<br>001 = CxVN connects to CXIN1- pin<br>010 = CxVN connects to CXIN2- pin<br>011 = CxVN connects to CXIN2- pin<br>011 = CxVN connects to CXIN3- pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |                                         |                                                                                     |                  |                | • •            |                   |              |  |  |  |

| 1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit         0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         bit 5-3       Comparator Positive Input Channel Select bits         000 = CxVP connects to CxIN+ pin         001 = CxVP connects to dac_out         010 = CxVP connects to FVR         011 = CxVP connects to Slope Compensator Output         1xx = CxVP connects to AGND         bit 2-0         Comparator Negative Input Channel Select bits         000 = CxVN connects to CxIN0 - pin         001 = CxVN connects to CxIN1 - pin         010 = CxVN connects to CXIN2 - pin         011 = CxVN connects to CXIN3 - pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | O = No inter                            | rupt flag will be                                                                   | set on a positiv | ve going edge  | of the CxOUT   | bit               |              |  |  |  |

| 0 = No interrupt flag will be set on a negative going edge of the CxOUT bit         bit 5-3       Comparator Positive Input Channel Select bits         000 = CxVP connects to CxIN+ pin       001 = CxVP connects to dac_out         010 = CxVP connects to FVR       011 = CxVP connects to Slope Compensator Output         1xx = CxVP connects to AGND       Comparator Negative Input Channel Select bits         000 = CxVN connects to CxIN0- pin       001 = CxVN connects to CxIN1- pin         010 = CxVN connects to CXIN1- pin       010 = CxVN connects to CXIN2- pin         011 = CxVN connects to CXIN3- pin       011 = CxVN connects to CXIN3- pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 6            | Co                                      | mparator Interr                                                                     | upt on Negative  | e Going Edge   | Enable bit     |                   |              |  |  |  |

| bit 5-3 Comparator Positive Input Channel Select bits<br>OOO= CxVP connects to CxIN+ pin<br>OO1= CxVP connects to dac_out<br>O10= CxVP connects to dac_out<br>O10= CxVP connects to FVR<br>O11= CxVP connects to Slope Compensator Output<br>1xx = CxVP connects to AGND<br>bit 2-0 Comparator Negative Input Channel Select bits<br>OOO= CxVN connects to CxIN0- pin<br>O01= CxVN connects to CxIN1- pin<br>O10= CxVN connects to CxIN2- pin<br>O11= CxVN connects to CxIN3- pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                                         | 1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit |                  |                |                |                   |              |  |  |  |

| $000= CxVP \text{ connects to } CxIN+ \text{ pin}$ $001= CxVP \text{ connects to } dac_out$ $010= CxVP \text{ connects to } FVR$ $011= CxVP \text{ connects to } Slope \text{ Compensator } Output$ $1xx = CxVP \text{ connects to } AGND$ bit 2-0 $000= CxVN \text{ connects to } CxIN0- \text{ pin}$ $001= CxVN \text{ connects to } CxIN0- \text{ pin}$ $010= CxVN \text{ connects to } CxIN1- \text{ pin}$ $010= CxVN \text{ connects to } CxIN2- \text{ pin}$ $011= CxVN \text{ connects to } CxIN3- \text{ pin}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  | 0 = No inter                            | rupt flag will be                                                                   | set on a negat   | ive going edge | e of the CxOUT | bit               |              |  |  |  |

| 001 = CxVP connects to dac_out         010 = CxVP connects to FVR         011 = CxVP connects to Slope Compensator Output         1xx = CxVP connects to AGND         bit 2-0       Comparator Negative Input Channel Select bits         000 = CxVN connects to CxIN0- pin         001 = CxVN connects to CxIN1- pin         010 = CxVN connects to CxIN2- pin         011 = CxVN connects to CxIN3- pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 5-3          |                                         | Comparator                                                                          | Positive Input C | Channel Select | t bits         |                   |              |  |  |  |

| 010 = CxVP connects to FVR<br>011 = CxVP connects to Slope Compensator Output<br>1xx = CxVP connects to AGND<br>bit 2-0 Comparator Negative Input Channel Select bits<br>000 = CxVN connects to CxIN0- pin<br>001 = CxVN connects to CxIN1- pin<br>010 = CxVN connects to CxIN2- pin<br>011 = CxVN connects to CxIN3- pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  | 000= CxVP                               | connects to C                                                                       | xIN+ pin         |                |                |                   |              |  |  |  |

| 011 = CxVP connects to Slope Compensator Output         1xx = CxVP connects to AGND         bit 2-0       Comparator Negative Input Channel Select bits         000= CxVN connects to CxIN0- pin         001 = CxVN connects to CxIN1- pin         010 = CxVN connects to CxIN2- pin         011 = CxVN connects to CxIN3- pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                                         |                                                                                     | —                |                |                |                   |              |  |  |  |

| 1xx = CxVP connects to AGND         bit 2-0       Comparator Negative Input Channel Select bits         000= CxVN connects to CxIN0- pin         001 = CxVN connects to CxIN1- pin         010 = CxVN connects to CxIN2- pin         011 = CxVN connects to CxIN3- pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  | ••••••••••••••••••••••••••••••••••••••• |                                                                                     | •••              |                |                |                   |              |  |  |  |

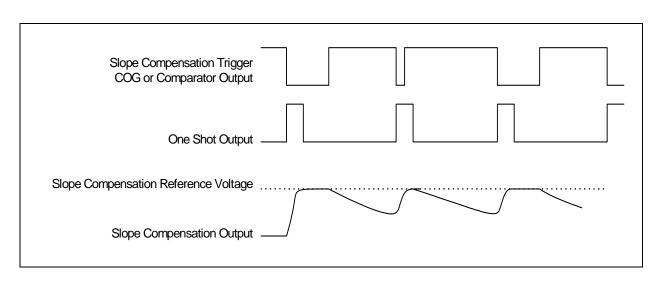

| bit 2-0 Comparator Negative Input Channel Select bits<br>000= CxVN connects to CxIN0- pin<br>001 = CxVN connects to CxIN1- pin<br>010 = CxVN connects to CxIN2- pin<br>011 = CxVN connects to CxIN3- pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                                         |                                                                                     |                  | ator Output    |                |                   |              |  |  |  |

| $\begin{array}{l} 000 = \text{CxVN connects to CxIN0- pin} \\ 001 = \text{CxVN connects to CxIN1- pin} \\ 010 = \text{CxVN connects to CxIN2- pin} \\ 011 = \text{CxVN connects to CxIN3- pin} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  | 1xx = CxVP                              |                                                                                     |                  |                |                |                   |              |  |  |  |