# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x9b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f753-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADL |         | 101755/1 | 10733 31                                                                                                    |                 |                |                         |                 |               |           |                     |                                 |

|------|---------|----------|-------------------------------------------------------------------------------------------------------------|-----------------|----------------|-------------------------|-----------------|---------------|-----------|---------------------|---------------------------------|

| Addr | Name    | Bit 7    | Bit 6                                                                                                       | Bit 5           | Bit 4          | Bit 3                   | Bit 2           | Bit 1         | Bit 0     | Value on<br>POR/BOR | Value on<br>all other<br>Resets |

| Bank | Bank 0  |          |                                                                                                             |                 |                |                         |                 |               |           |                     |                                 |

| 00h  | INDF    |          |                                                                                                             |                 | IND            | F<7:0>                  |                 |               |           | xxxx xxxx           | XXXX XXXX                       |

| 01h  | TMR0    |          |                                                                                                             |                 | TMR            | 0<7:0>                  |                 |               |           | XXXX XXXX           | uuuu uuuu                       |

| 02h  | PCL     |          |                                                                                                             |                 | PCL            | _<7:0>                  |                 |               |           | 0000 0000           | 0000 0000                       |

| 03h  | STATUS  | IRP      | RP1                                                                                                         | RP0             | TO             | PD                      | Z               | DC            | С         | 0001 1xxx           | 000q quuu                       |

| 04h  | FSR     |          |                                                                                                             |                 | FSF            | R<7:0>                  |                 |               |           | XXXX XXXX           | uuuu uuuu                       |

| 05h  | PORTA   | -        | _                                                                                                           | RA5             | RA4            | RA3                     | RA2             | RA1           | RA0       | xx xxxx             | uu uuuu                         |

| 06h  | —       |          | <u>.                                    </u>                                                                |                 | Unimp          | lemented                |                 |               | <u> </u>  | _                   | _                               |

| 07h  | PORTC   | -        | —                                                                                                           | RC5             | RC4            | RC3                     | RC2             | RC1           | RC0       | xx xxxx             | uu uuuu                         |

| 08h  | IOCAF   | _        | —                                                                                                           | IOCAF5          | IOCAF4         | IOCAF3                  | IOCAF2          | IOCAF1        | IOCAF0    | 00 0000             | 00 0000                         |

| 09h  | IOCCF   | —        | —                                                                                                           | IOCCF5          | IOCCF4         | IOCCF3                  | IOCCF2          | IOCCF1        | IOCCF0    | 00 0000             | 00 0000                         |

| 0Ah  | PCLATH  | _        | _                                                                                                           | _               |                |                         | PCLATH<4:0>     | >             |           | 0 0000              | 0 0000                          |

| 0Bh  | INTCON  | GIE      | PEIE                                                                                                        | T0IE            | INTE           | IOCIE                   | TOIF            | INTF          | IOCIF     | 0000 0000           | 0000 0000                       |

| 0Ch  | PIR1    | TMR1GIF  | ADIF                                                                                                        | —               | —              | HLTMR2IF                | HLTMR1IF        | TMR2IF        | TMR1IF    | 000000              | 000000                          |

| 0Dh  | PIR2    | —        | —                                                                                                           | C2IF            | C1IF           | —                       | COG1IF          | _             | CCP1IF    | 00 -0-0             | 00 -0-0                         |

| 0Eh  | —       |          | Unimplemented                                                                                               |                 |                |                         |                 |               |           | -                   | —                               |

| 0Fh  | TMR1L   |          | TMR1L<7:0>                                                                                                  |                 |                |                         |                 |               |           | xxxx xxxx           | uuuu uuuu                       |

| 10h  | TMR1H   |          |                                                                                                             |                 | TMR1           | IH<7:0>                 |                 |               |           | XXXX XXXX           | uuuu uuuu                       |

| 11h  | T1CON   | TMR1C    | S<1:0>                                                                                                      | T1CKP           | PS<1:0>        | T1OSCEN                 | T1SYNC          | _             | TMR10N    | 0000 00-0           | 0000 00-0                       |

| 12h  | T1GCON  | TMR1GE   | T1GPOL                                                                                                      | T1GTM           | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL          | T1GS          | S<1:0>    | 00x0 0x00           | 00x0 0x00                       |

| 13h  | CCPR1L  |          |                                                                                                             |                 | CCPR           | 1L<7:0>                 |                 |               |           | xxxx xxxx           | uuuu uuuu                       |

| 14h  | CCPR1H  |          |                                                                                                             |                 | CCPR           | 1H<7:0>                 |                 |               |           | xxxx xxxx           | uuuu uuuu                       |

| 15h  | CCP1CON | —        | —                                                                                                           | DC1E            | 3<1:0>         |                         | CCP1N           | 1<3:0>        |           | 00 0000             | 00 0000                         |

| 16h  | —       |          | Unimplemented                                                                                               |                 |                |                         |                 |               | —         | —                   |                                 |

| 17h  | —       |          | Unimplemented                                                                                               |                 |                |                         |                 |               |           | _                   | —                               |

| 18h  | —       |          | Unimplemented                                                                                               |                 |                |                         |                 |               |           | _                   | —                               |

| 19h  | —       |          | Unimplemented                                                                                               |                 |                |                         |                 |               | _         | —                   |                                 |

| 1Ah  | _       |          | Unimplemented                                                                                               |                 |                |                         |                 |               | —         | —                   |                                 |

| 1Bh  | —       |          | Unimplemented                                                                                               |                 |                |                         |                 |               | —         | —                   |                                 |

| 1Ch  | ADRESL  |          | Least Significant two bits of the left shifted result or eight bits of the right shifted result xxxx xxxx u |                 |                |                         |                 |               | uuuu uuuu |                     |                                 |

| 1Dh  | ADRESH  | Most     | Significant e                                                                                               | ight bits of th | e left shifted | A/D result or           | two bits of the | right shifted | result    | XXXX XXXX           | uuuu uuuu                       |

| 1Eh  | ADCON0  | ADFM     | —                                                                                                           |                 | CHS            | 8<3:0>                  |                 | GO/DONE       | ADON      | 0-00 0000           | 0-00 0000                       |

| 1Fh  | ADCON1  | —        |                                                                                                             | ADCS<2:0>       |                | -                       | -               | —             | ADPREF1   | -0000               | -0000                           |

|      |         |          |                                                                                                             |                 |                |                         |                 |               |           |                     |                                 |

TABLE 2-1: PIC16F753/HV753 SPECIAL REGISTERS SUMMARY BANK 0

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition shaded = unimplemented.

.

| IADI  | ADLE 2-3: PICTOF733/HV733 SPECIAL REGISTERS SUMMART DANK 2 |                                                                                                                                           |                                                            |                               |                  |                |               |           |           |                     |                                 |

|-------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------|------------------|----------------|---------------|-----------|-----------|---------------------|---------------------------------|

| Addr  | Name                                                       | Bit 7                                                                                                                                     | Bit 6                                                      | Bit 5                         | Bit 4            | Bit 3          | Bit 2         | Bit 1     | Bit 0     | Value on<br>POR/BOR | Value on<br>all other<br>Resets |

| Ban   | Bank 2                                                     |                                                                                                                                           |                                                            |                               |                  |                |               |           |           |                     |                                 |

| 100h  | INDF                                                       |                                                                                                                                           |                                                            |                               | INDF             | <7:0>          |               |           |           | XXXX XXXX           | XXXX XXXX                       |

| 101h  | TMR0                                                       |                                                                                                                                           |                                                            |                               | TMR              | )<7:0>         |               |           |           | xxxx xxxx           | uuuu uuuu                       |

| 102h  | PCL                                                        |                                                                                                                                           |                                                            |                               | PCL              | <7:0>          |               |           |           | 0000 0000           | 0000 0000                       |

| 103h  | STATUS                                                     | IRP                                                                                                                                       | RP1                                                        | RP0                           | TO               | PD             | Z             | DC        | С         | 0001 1xxx           | 000q quuu                       |

| 104h  | FSR                                                        |                                                                                                                                           |                                                            | •                             | FSR              | <7:0>          | •             | •         |           | xxxx xxxx           | uuuu uuuu                       |

| 105h  | LATA                                                       | —                                                                                                                                         | _                                                          | LATA5                         | LATA4            | _              | LATA2         | LATA1     | LATA0     | xx -xxx             | uu -uuu                         |

| 106h  | —                                                          |                                                                                                                                           |                                                            |                               | Unimple          | emented        |               |           |           | _                   | _                               |

| 107h  | LATC                                                       | _                                                                                                                                         | _                                                          | LATC5                         | LATC4            | LATC3          | LATC2         | LATC1     | LATC0     | xx xxxx             | uu uuuu                         |

| 108h  | IOCAN                                                      | _                                                                                                                                         | _                                                          | IOCAN5                        | IOCAN4           | IOCAN3         | IOCAN2        | IOCAN1    | IOCAN0    | 00 0000             | 00 0000                         |

| 109h  | IOCCN                                                      | —                                                                                                                                         | _                                                          | IOCCN5                        | IOCCN4           | IOCCN3         | IOCCN2        | IOCCN1    | IOCCN0    | 00 0000             | 00 0000                         |

| 10Ah  | PCLATH                                                     | _                                                                                                                                         |                                                            | —                             |                  | F              | PCLATH<4:0:   | >         |           | 0 0000              | 0 0000                          |

| 10Bh  | INTCON                                                     | GIE                                                                                                                                       | PEIE                                                       | TOIE                          | INTE             | IOCIE          | T0IF          | INTF      | IOCIF     | 0000 0000           | 0000 0000                       |

| 10Ch  | WPUA                                                       | —                                                                                                                                         | _                                                          | WPUA5                         | WPUA4            | WPUA3          | WPUA2         | WPUA1     | WPUA0     | 11 1111             | 11 1111                         |

| 10Dh  | WPUC                                                       | _                                                                                                                                         |                                                            | WPUC5                         | WPUC4            | WPUC3          | WPUC2         | WPUC1     | WPUC0     | 11 1111             | 11 1111                         |

| 10Eh  | SLRCONC                                                    | _                                                                                                                                         |                                                            | SLRC5                         | SLRC4            | -              | —             | _         | _         | 00                  | 00                              |

| 10Fh  | PCON                                                       | —                                                                                                                                         | -                                                          | _                             | _                | —              | —             | POR       | BOR       | qq                  | uu                              |

| 110h  | TMR2                                                       |                                                                                                                                           |                                                            |                               | TMR2             | 2<7:0>         |               |           |           | 0000 0000           | 0000 0000                       |

| 111h  | PR2                                                        |                                                                                                                                           |                                                            |                               | PR2-             | <7:0>          |               |           |           | 1111 1111           | 1111 1111                       |

| 112h  | T2CON                                                      | —                                                                                                                                         |                                                            | T2OUTF                        | PS<3:0>          |                | TMR2ON        | T2CKF     | PS<1:0>   | -000 0000           | -000 0000                       |

| 113h  | HLTMR1                                                     |                                                                                                                                           | F                                                          | Iolding Registe               | er for the 8-bit | Hardware Lim   | nit Timer1 Co | unt       |           | 0000 0000           | 0000 0000                       |

| 114h  | HLTPR1                                                     |                                                                                                                                           |                                                            | HL                            | TMR1 Module      | e Period Regis | ster          |           |           | 1111 1111           | 1111 1111                       |

| 115h  | HLT1CON0                                                   | —                                                                                                                                         |                                                            | H1OUT                         | PS<3:0>          |                | H1ON          | H1CKF     | PS<1:0>   | -000 0000           | -000 0000                       |

| 116h  | HLT1CON1                                                   | H1FES                                                                                                                                     | H1RES                                                      | _                             |                  | H1ERS<2:0>     |               | H1FEREN   | H1REREN   | 11-0 0000           | 11-0 0000                       |

| 117h  | HLTMR2                                                     |                                                                                                                                           | Holding Register for the 8-bit Hardware Limit Timer2 Count |                               |                  |                |               | 0000 0000 | 0000 0000 |                     |                                 |

| 118h  | HLTPR2                                                     |                                                                                                                                           | HLTMR2 Module Period Register                              |                               |                  |                |               | 1111 1111 | 1111 1111 |                     |                                 |

| 119h  | HLT2CON0                                                   | _                                                                                                                                         |                                                            | H2OUTPS<3:0> H2ON H2CKPS<1:0> |                  |                |               | -000 0000 | -000 0000 |                     |                                 |

| 11Ah  | HLT2CON1                                                   | H2FES                                                                                                                                     | S H2RES — H2ERS<2:0> H2FEREN H2REREN                       |                               |                  |                | 11-0 0000     | 11-0 0000 |           |                     |                                 |

| 11Bh  | _                                                          |                                                                                                                                           | Unimplemented                                              |                               |                  |                |               |           |           | _                   | —                               |

| 11Ch  | _                                                          |                                                                                                                                           | Unimplemented                                              |                               |                  |                |               |           |           | _                   | _                               |

| 11Dh  | —                                                          |                                                                                                                                           |                                                            |                               | Unimple          | emented        |               |           |           | _                   | _                               |

| 11Eh  | SLPCCON0                                                   | SC1EN                                                                                                                                     | _                                                          | —                             | SC1POL           | SC1TS          | S<1:0>        | —         | SC1INS    | 0-00 00-0           | 0-00 00-0                       |

| 11Fh  | SLPCCON1                                                   |                                                                                                                                           | _                                                          | _                             | SC1RNG           |                | SC1ISI        | ET<3:0>   |           | 0 0000              | 0 0000                          |

| Logor | ale llaiman la                                             | $-$ = Unimplemented locations read as $(0^{2})_{11}$ = unchanged x = unknown $\alpha$ = value depends on condition shaded = unimplemented |                                                            |                               |                  |                |               |           |           |                     |                                 |

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition shaded = unimplemented.

| Name   | Bit 7           | Bit 6                             | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|--------|-----------------|-----------------------------------|-------------|-------|-------|-------|-------|-------|---------------------|

| PMCON1 | _               | _                                 |             | _     | _     | WREN  | WR    | RD    | 27                  |

| PMCON2 |                 | Program Memory Control Register 2 |             |       |       |       |       |       | 27                  |

| PMADRL | PMADRL<7:0>     |                                   |             |       |       |       |       |       | 26                  |

| PMADRH | _               | _                                 | PMADRH<1:0> |       |       |       |       |       | 26                  |

| PMDATL | PMDATL<7:0>     |                                   |             |       |       |       | 26    |       |                     |

| PMDATH | — — PMDATH<5:0> |                                   |             |       |       |       | 26    |       |                     |

| INTCON | GIE             | PEIE                              | TOIE        | INTE  | IOCIE | T0IF  | INTF  | IOCIF | 17                  |

### TABLE 3-1: SUMMARY OF REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Flash program memory module. \* Page provides register information.

#### TABLE 3-2: SUMMARY OF CONFIGURATION WORD WITH FLASH PROGRAM MEMORY

| Name                  | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|-----------------------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG <sup>(1)</sup> | 13:8 |         |         | DEBUG    | CLKOUTEN | WRT<1:0> |          | BOREI   | N<1:0>  | 450                 |

| CONFIG                | 7:0  | _       | CP      | MCLRE    | PWRTE    | WDTE     |          |         | FOSC0   | 150                 |

Legend: — = unimplemented location, read as '1'. Shaded cells are not used by Flash program memory.

Note 1: See Configuration Word register (Register 19-1) for operation of all register bits.

## 5.3 PORTA and TRISA Registers

PORTA is a 6-bit wide port with five bidirectional and one input-only pin. The corresponding data direction register is TRISA (Register 5-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input-only and its TRIS bit will always read as '1'. Example 5-1 shows how to initialize PORTA.

Reading the PORTA register (Register 5-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. RA3 reads '0' when MCLRE = 1.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSEL register must be initialized to    |

|-------|----------------------------------------------|

|       | configure an analog channel as a digital     |

|       | input. Pins configured as analog inputs will |

|       | read '0' and cannot generate an interrupt.   |

#### 5.3.1 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 5-1.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as comparator inputs, are not shown in the priority lists. These inputs are active when the peripheral is enabled and the input multiplexer for the pin is selected. The Analog mode, set with the ANSELA register, disables the digital input buffer thereby preventing excessive input current when the analog input voltage is between logic states. Digital output functions may control the pin when it is in Analog mode with the priority shown in Table 5-1.

#### TABLE 5-1: PORTA OUTPUT PRIORITY

| Pin Name | Function Priority                                    |

|----------|------------------------------------------------------|

| RAO      | ICSPDAT<br>FVROUT<br>DACOUT<br>C1IN0+<br>RA0         |

| RA1      | FVRIN<br>ICSPCLK<br>VREF+<br>C1IN0-<br>C2IN0-<br>RA1 |

| RA2      | COG1FLT<br>T0CKI<br>C1OUT<br>INT<br>RA2              |

| RA3      | MCLR<br>VPP<br>T1G<br>RA3                            |

| RA4      | CLKOUT<br>T1G<br>RA4                                 |

| RA5      | CLKIN<br>T1CKI<br>RA5                                |

# 5.4 Additional Pin Functions

Every PORTA pin on the PIC16F753 has an interrupton-change option and a weak pull-up option. The next three sections describe these functions.

#### 5.4.1 ANSELA REGISTER

The ANSELA register (Register 5-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 5.4.2 WEAK PULL-UPS

Each of the PORTA pins, except RA3, has an individually configurable internal weak pull-up. Control bits WPUx enable or disable each pull-up. Refer to Register 5-6. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RAPU bit of the OPTION\_REG register. A weak pull-up is automatically enabled for RA3 when configured as MCLR and disabled when RA3 is an I/O. There is no software control of the MCLR pull-up.

#### 5.4.3 INTERRUPT-ON-CHANGE

Each PORTA pin is individually configurable as an interrupt-on-change pin. Control bits IOCA enable or disable the interrupt function for each pin. Refer to Register 5-7. The interrupt-on-change is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTA. The 'mismatch' outputs of the last read are OR'd together to set the PORTA Change Interrupt Flag bit (IOCIF) in the INTCON register (Register 2-3).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

a) Any read of PORTA AND Clear flag bit IOCIF. This will end the mismatch condition;

OR

Any write of PORTA AND Clear flag bit IOCIF will end the mismatch condition;

A mismatch condition will continue to set flag bit IOCIF. Reading PORTA will end the mismatch condition and allow flag bit IOCIF to be cleared. The latch holding the last read value is not affected by a MCLR nor BOR Reset. After these Resets, the IOCIF flag will continue to be set if a mismatch is present.

**Note:** If a change on the I/O pin should occur when any PORTA operation is being executed, then the IOCIF interrupt flag may not get set.

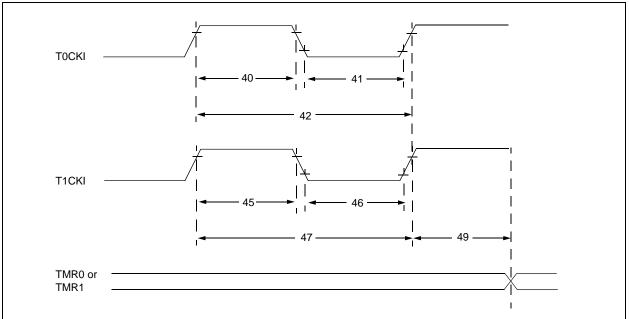

# 7.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 7-1 displays the Timer1 enable selections.

| TABLE 7-1: | TIMER1 ENABLE |

|------------|---------------|

|            | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 7.2 Clock Source Selection

The TMR1CS<1:0> bits of the T1CON register are used to select the clock source for Timer1. Table 7-2 displays the clock source selections.

# TABLE 7-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> Clock Source |                                |  |

|--------------------------|--------------------------------|--|

| 11                       | Temperature Sense Oscillator   |  |

| 10                       | External Clocking on T1CKI Pin |  |

| 01                       | System Clock (Fosc)            |  |

| 00                       | Instruction Clock (Fosc/4)     |  |

#### 7.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc or Fosc/4 as determined by the Timer1 prescaler.

## 7.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter. When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI.

| Note: | In Counter mode, a falling edge must be<br>registered by the counter prior to the first<br>incrementing rising edge (see Figure 7-2)<br>after any one or more of the following<br>conditions: |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Timer1 enabled after POR Reset                                                                                                                                                                |

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON = 1) when T1CKI is low.

### 7.2.3 WDT OSCILLATOR

When the Watchdog is selected, Timer 1 will use the LFINTOSC that is used to operate the Watchdog Timer. This is the same oscillator as the LFINTOSC used as the system clock. Selecting this option will enable the oscillator even when the LFINTOSC or the Watchdog are not in use. This oscillator will continue to operate when in Sleep mode.

## 9.1 HLT Operation

The clock input to the HLT module is the system instruction clock (Fosc/4). HLTMRx increments on each rising clock edge.

A 4-bit counter/prescaler on the clock input provides the following prescale options:

- Direct input

- Divide-by-4

- Divide-by-16

- Divide-by-64

The prescale options are selected by the prescaler control bits, HxCKPS<1:0> of the HLTxCON0 register.

The value of HLTMRx is compared to that of the Period register, HLTPRx, on each clock cycle. When the two values match, then the comparator generates a match signal as the HLTimerx output. This signal also resets the value of HLTMRx to 00h on the next clock rising edge and drives the output counter/postscaler (see **Section 9.2 "HLT Interrupt"**).

The HLTMRx and HLTPRx registers are both directly readable and writable. The HLTMRx register is cleared on any device Reset, whereas the HLTPRx register initializes to FFh. Both the prescaler and postscaler counters are cleared on any of the following events:

- A write to the HLTMRx register

- A write to the HLTxCON0 register

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- Watchdog Timer (WDT) Reset

- Stack Overflow Reset

- Stack Underflow Reset

- RESET Instruction

Note: HLTMRx is not cleared when HLTxCON0 is written.

# 9.2 HLT Interrupt

The HLT can also generate an optional device interrupt. The HLTMRx output signal (HLTMRx-to-HLTPRx match) provides the input for the 4-bit counter/postscaler. The overflow output of the postscaler sets the HLTMRxIF bit of the PIR1 register. The interrupt is enabled by setting the HLTMRx Match Interrupt Enable bit, HLTMRxIE of the PIE1 register.

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, HxOUTPS<3:0>, of the HLTxCON0 register.

## 9.3 Peripheral Resets

Resets driven from the selected peripheral output prevents the HLTMRx from matching the HLTPRx register and generating an output. In this manner, the HLT can be used as a hardware time limit to other peripherals.

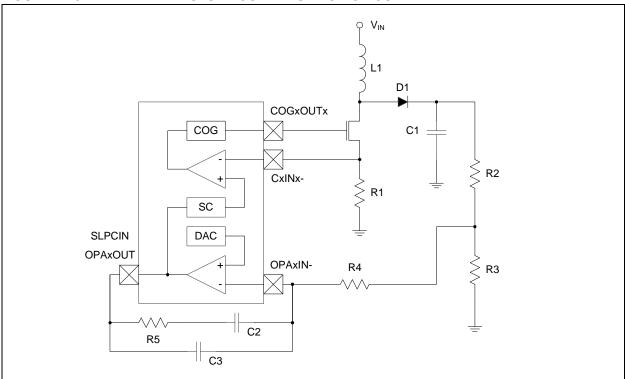

In this device, the primary purpose of the HLT is to limit the COG PWM duty cycle. Normally, the COG operation uses analog feedback to determine the PWM duty cycle. The same feedback signal is used as an HLT Reset input. The HLTPRx register is set to occur at the maximum allowed duty cycle. If the analog feedback to the COG exceeds the maximum time, then an HLTMRx-to-HLTPRx match will occur and generate the output needed to limit the COG drive output.

The HLTMRx can be reset by one of several selectable peripheral sources. Reset inputs include:

- CCP1 output

- · Comparator 1 output

- · Comparator 2 output

- COGxFLT pin

- COG1OUT0

- COG10UT1

The external Reset input is selected with the HxERS<2:0> bits of the HLTxCON1 register. High and low Reset enables are selected with the HxREREN and HxFEREN bits, respectively. Setting the HxRES and HxFES bits makes the respective rising and falling Reset events edge sensitive. Reset inputs that are not edge sensitive are level sensitive.

HLTMRx Resets are synchronous with the HLT clock. In other words, HLTMRx is cleared on the rising edge of the HLT clock after the enabled Reset event occurs.

If an enabled external Reset occurs at the same time a write occurs to the TMR4A register, the write to the timer takes precedence and pending Resets are cleared.

# 9.4 HLTimerx Output

The unscaled output of HLTMRx is available only to the COG module, where it is used as a selectable limit to the maximum COG period.

# 9.5 HLT Operation During Sleep

The HLT cannot be operated while the processor is in Sleep mode. The contents of the HLTMRx register will remain unchanged while the processor is in Sleep mode.

#### 10.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

| Name    | Bit 7        | Bit 6      | Bit 5  | Bit 4   | Bit 3 Bit 2                    |          | Bit 2 Bit 1 |        | Register<br>on Page |

|---------|--------------|------------|--------|---------|--------------------------------|----------|-------------|--------|---------------------|

| CCP1CON | —            | —          | DC1E   | 8<1:0>  |                                | CCP1M<   | 3:0>        |        | 80                  |

| CCPR1L  |              |            |        | CCF     | PR1L<7:0>                      |          |             |        | 74                  |

| CCPR1H  |              |            |        | CCP     | R1H<7:0>                       |          |             |        | 74                  |

| INTCON  | GIE          | PEIE       | T0IE   | INTE    | IOCIE                          | T0IF     | INTF        | IOCIF  | 17                  |

| PIE1    | TMR1-<br>GIE | ADIE       | —      | —       | — HLTMR2IE H                   |          | TMR2IE      | TMR1IE | 18                  |

| PIE2    | —            | —          | C2IE   | C1IE    | _                              | COG1IE   |             | CCP1IE | 19                  |

| PIR1    | TMR1-<br>GIF | ADIF       |        | _       | HLTMR2IF                       | HLTMR1IF | TMR2IF      | TMR1IF | 20                  |

| PIR2    | —            | —          | C2IF   | C1IF    | _                              | COG1IF   | _           | CCP1IF | 21                  |

| T1CON   | TMR1C        | S<1:0>     | T1CKP  | 2S<1:0> | T1OSCEN                        | T1SYNC   |             | TMR1ON | 65                  |

| T1GCON  | TMR1GE       | T1GPOL     | T1GTM  | T1GSPM  | T1GGO/ T1GVAL T1GSS<1:<br>DONE |          | S<1:0>      | 66     |                     |

| TMR1H   |              | TMR1H<7:0> |        |         |                                |          |             |        | 57*                 |

| TMR1L   |              |            |        | TM      | R1L<7:0>                       |          |             |        | 57*                 |

| TRISA   |              |            | TRISA5 | TRISA4  | TRISA3 <sup>(1)</sup>          | TRISA2   | TRISA1      | TRISA0 | 43                  |

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by Compare mode.

\* Page provides register information.

Note 1: TRISA3 always reads '1'.

When the phase delay count value is zero, phase delay is disabled and the phase delay counter output is true, thereby allowing the event signal to pass straight through to complementary output driver flop.

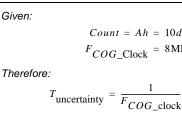

#### CUMULATIVE UNCERTAINTY 11.7.1

It is not possible to create more than one COG\_clock of uncertainty by successive stages. Consider that the phase delay stage comes after the blanking stage, the dead-band stage comes after either the blanking or phase delay stages, and the blanking stage comes after the dead-band stage. When the preceding stage is enabled, the output of that stage is necessarily synchronous with the COG\_clock, which removes any possibility of uncertainty in the succeeding stage.

#### EQUATION 11-1: PHASE, DEAD-BAND AND **BLANKING TIME** CALCULATION

$$T_{\min} = \frac{\text{Count}}{F_{COG\_clock}}$$

$$T_{\max} = \frac{\text{Count} + 1}{F_{COG\_clock}}$$

$$T_{\text{uncertainty}} = T_{\max} - T_{\min}$$

Also:

$$T_{\text{uncertainty}} = \frac{1}{F_{COG\_clock}}$$

Where:

| т                      | Count   |

|------------------------|---------|

| Rising Phase Delay     | COGxPHR |

| Falling Phase Delay    | COGxPHF |

| Rising Dead Band       | COGxDBR |

| Falling Dead Band      | COGxDBF |

| Rising Event Blanking  | COGxBKR |

| Falling Event Blanking | COGxBKF |

#### EQUATION 11-2: TIMER UNCERTAINTY

Count = Ah = 10d

$F_{COG\_Clock} = 8MHz$

$$= \frac{1}{8MHz} = 125ns$$

Proof:

$$T_{\min} = \frac{Count}{F_{COG\_clock}}$$

$$= 125ns \bullet 10d \qquad = 1.25\mu s$$

$$T_{\max} = \frac{Count + 1}{F_{COG\_clock}}$$

$$= 125 ns \bullet (10d + 1)$$

$$= 1.375 \, \mu s$$

Therefore:

$$T_{\text{uncertainty}} = T_{\text{max}} - T_{\text{min}}$$

$$= 1.375 \,\mu s - 1.25 \,\mu s$$

$$= 125 \,n s$$

| U-0                              | R/W-0/0                                                                                   | R/W-0/0                                                                                                   | R/W-0/0           | R/W-0/0                     | R/W-0/0                     | R/W-0/0         | R/W-0/0   |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|-----------------------------|-----------------|-----------|--|--|--|

| —                                | GxRMHLT2                                                                                  | GxRMHLT1                                                                                                  | GxRMT2M           | GxRMFLT                     | GxRMCCP1                    | GxRMC2          | GxRMC1    |  |  |  |

| bit 7                            |                                                                                           |                                                                                                           |                   |                             |                             |                 | bit       |  |  |  |

|                                  |                                                                                           |                                                                                                           |                   |                             |                             |                 |           |  |  |  |

| <b>Legend:</b><br>R = Readable I | nit                                                                                       | W = Writable t                                                                                            | sit               | II – I Inimplen             | nented bit, read a          | e 'O'           |           |  |  |  |

| u = Bit is uncha                 |                                                                                           | x = Bit is unkn                                                                                           |                   | •                           | at POR and BOR/             |                 | er Resets |  |  |  |

| '1' = Bit is set                 |                                                                                           | '0' = Bit is clea                                                                                         |                   |                             | ends on conditior           |                 |           |  |  |  |

|                                  |                                                                                           | 0 21110 0100                                                                                              |                   | <u>q</u>                    |                             | ·               |           |  |  |  |

| bit 7                            | Unimplement                                                                               | ed: Read as '0'                                                                                           |                   |                             |                             |                 |           |  |  |  |

| bit 6                            | GxRMHLT2: (<br>GxRIHLT2 = 1                                                               | COGx Rising Ev                                                                                            | ent Input Sour    | ce 6 Mode bit <sup>(1</sup> | )                           |                 |           |  |  |  |

|                                  | 1 = HLTimer2                                                                              | low-to-high tra<br>high level will d                                                                      |                   |                             | nt after rising ever<br>ent | nt phase delay  |           |  |  |  |

|                                  |                                                                                           | no effect on ris                                                                                          | ng event          |                             |                             |                 |           |  |  |  |

| bit 5                            | <b>GxRMHLT1:</b> (<br><u>GxRIHLT1 = 1</u>                                                 | COGx Rising Ev<br><u>:</u>                                                                                | ent Input Sour    | ce 5 Mode bit <sup>(1</sup> | )                           |                 |           |  |  |  |

|                                  |                                                                                           | high level will o                                                                                         |                   |                             | nt after rising ever<br>ent | nt phase delay  |           |  |  |  |

|                                  |                                                                                           | no effect on ris                                                                                          | -                 | (4)                         |                             |                 |           |  |  |  |

| bit 4                            | <b>GxRMT2M:</b> C<br>GxRIT2M = 1:                                                         | OGx Rising Eve                                                                                            | ent Input Sourc   | e 4 Mode bit <sup>(1)</sup> |                             |                 |           |  |  |  |

|                                  | 1 = Timer2 m                                                                              | 1 = Timer2 match with PR2 low-to-high transition will cause a rising event after rising event phase delay |                   |                             |                             |                 |           |  |  |  |

|                                  | 0 = Timer2 match with PR2 high level will cause an immediate rising event<br>GxRIT2M = 0: |                                                                                                           |                   |                             |                             |                 |           |  |  |  |

|                                  |                                                                                           | with PR2 has n                                                                                            | o effect on risir | ng event                    |                             |                 |           |  |  |  |

| bit 3                            | GxRMFLT: CO<br>GxRIFLT = 1:                                                               | OGx Rising Eve                                                                                            | nt Input Source   | e 3 Mode bit                |                             |                 |           |  |  |  |

|                                  | 1 = COGxFL                                                                                | Г pin low-to-higł<br>Г pin high level                                                                     |                   |                             | event after rising<br>event | event phase de  | lay       |  |  |  |

|                                  |                                                                                           | has no effect or                                                                                          | n rising event    |                             |                             |                 |           |  |  |  |

| bit 2                            | GxRMCCP1:<br>GxRICCP1 = 1                                                                 | COGx Rising Ev                                                                                            | vent Input Sour   | ce 2 Mode bit               |                             |                 |           |  |  |  |

|                                  | 1 = CCP1 lov                                                                              | v-to-high transiti<br>h level will caus                                                                   |                   |                             | fter rising event pł        | nase delay      |           |  |  |  |

|                                  |                                                                                           | effect on rising                                                                                          | event             |                             |                             |                 |           |  |  |  |

| bit 1                            |                                                                                           | Gx Rising Even                                                                                            | t Input Source    | 1 Mode bit                  |                             |                 |           |  |  |  |

|                                  |                                                                                           | tor 2 low-to-high<br>tor 2 high level                                                                     |                   | -                           | event after rising<br>event | event phase de  | lay       |  |  |  |

|                                  |                                                                                           | has no effect or                                                                                          | n rising event    |                             |                             |                 |           |  |  |  |

| bit 0                            |                                                                                           | Gx Rising Even                                                                                            | t Input Source    | 0 Mode bit                  |                             |                 |           |  |  |  |

|                                  | 0 = Compara GxRIC1 = 0:                                                                   | tor 1 high level                                                                                          | will cause an in  |                             | event after rising<br>event | event phase de  | lay       |  |  |  |

|                                  | Comparator 1                                                                              | has no effect or                                                                                          | n rising event    |                             |                             |                 |           |  |  |  |

| Note 1: The                      | ese sources are                                                                           | pulses and ther                                                                                           | efore the only b  | penefit of Edge             | mode over Level             | mode is that th | ev can be |  |  |  |

#### REGISTER 11-4: COGxRSIM: COG RISING EVENT SOURCE INPUT MODE REGISTER

**Note 1:** These sources are pulses and therefore the only benefit of Edge mode over Level mode is that they can be delayed by rising event phase delay.

| U-0                                                                      | R/W-0/0                                                                                                              | R/W-0/0                                                                                                                                             | R/W-0/0          | R/W-0/0       | R/W-0/0          | R/W-0/0 | R/W-0/0   |  |  |  |  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------------|---------|-----------|--|--|--|--|

| _                                                                        | GxFIHLT2                                                                                                             | GxFIHLT1                                                                                                                                            | GxFIT2M          | GxFIFLT       | GxFICCP1         | GxFIC2  | GxFIC1    |  |  |  |  |

| oit 7                                                                    |                                                                                                                      |                                                                                                                                                     |                  |               |                  |         | bit       |  |  |  |  |

| Legend:                                                                  |                                                                                                                      |                                                                                                                                                     |                  |               |                  |         |           |  |  |  |  |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |                                                                                                                      |                                                                                                                                                     |                  |               |                  |         |           |  |  |  |  |

| u = Bit is uncl                                                          | hanged                                                                                                               | x = Bit is unkn                                                                                                                                     | own              | •             | at POR and BOR   |         | er Resets |  |  |  |  |

| 1' = Bit is set                                                          |                                                                                                                      | '0' = Bit is clea                                                                                                                                   | red              | q = Value dep | ends on conditio | n       |           |  |  |  |  |

|                                                                          |                                                                                                                      |                                                                                                                                                     |                  |               |                  |         |           |  |  |  |  |

| oit 7                                                                    | Unimplement                                                                                                          | ed: Read as '0'                                                                                                                                     |                  |               |                  |         |           |  |  |  |  |

| oit 6                                                                    |                                                                                                                      | OGx Falling Eve                                                                                                                                     |                  |               |                  |         |           |  |  |  |  |

|                                                                          |                                                                                                                      | output is enabl<br>has no effect o                                                                                                                  |                  |               |                  |         |           |  |  |  |  |

| oit 5                                                                    |                                                                                                                      | DGx Falling Eve                                                                                                                                     | -                |               |                  |         |           |  |  |  |  |

|                                                                          |                                                                                                                      | output is enabl                                                                                                                                     |                  |               |                  |         |           |  |  |  |  |

|                                                                          | 0 = HLTimer1                                                                                                         | has no effect o                                                                                                                                     | n the falling ev | rent          |                  |         |           |  |  |  |  |

| oit 4                                                                    |                                                                                                                      | Gx Falling Ever                                                                                                                                     | •                |               |                  |         |           |  |  |  |  |

|                                                                          |                                                                                                                      | atch with PR2 is<br>atch with PR2 h                                                                                                                 |                  | •             | •                |         |           |  |  |  |  |

| oit 3                                                                    | GxFIFLT: COO                                                                                                         | Gx Falling Even                                                                                                                                     | Input Source     | 3 Enable bit  |                  |         |           |  |  |  |  |

|                                                                          |                                                                                                                      | r pin is enabled                                                                                                                                    | •                | •             |                  |         |           |  |  |  |  |

|                                                                          |                                                                                                                      | F pin has no effe                                                                                                                                   |                  | -             |                  |         |           |  |  |  |  |

| oit 2                                                                    | <b>GxFICCP1:</b> COGx Falling Event Input Source 2 Enable bit<br>1 = CCP1 output is enabled as a falling event input |                                                                                                                                                     |                  |               |                  |         |           |  |  |  |  |

|                                                                          |                                                                                                                      | s no effect on th                                                                                                                                   |                  |               |                  |         |           |  |  |  |  |

| oit 1                                                                    |                                                                                                                      | x Falling Event                                                                                                                                     | •                |               |                  |         |           |  |  |  |  |

|                                                                          | •                                                                                                                    | <ul> <li>1 = Comparator 2 output is enabled as a falling event input</li> <li>0 = Comparator 2 output has no effect on the falling event</li> </ul> |                  |               |                  |         |           |  |  |  |  |

|                                                                          |                                                                                                                      | •                                                                                                                                                   |                  | •             |                  |         |           |  |  |  |  |

| oit 0                                                                    |                                                                                                                      | x Falling Event<br>tor 1 output is e                                                                                                                | •                |               | t                |         |           |  |  |  |  |

|                                                                          | 0 = Compara                                                                                                          |                                                                                                                                                     |                  |               | -                |         |           |  |  |  |  |

#### REGISTER 11-5: COGxFIS: COG FALLING EVENT INPUT SELECTION REGISTER

## 17.3 Inputs

The SC module connects to the following inputs:

- COG1

- COG2

- Comparator C1

- Comparator C2

# 17.4 Outputs

The SC module connects to the following outputs:

- Comparator C1

- Comparator C2

- Op amp

## 17.5 Operation During Sleep

The SC module is unaffected by Sleep.

### 17.6 Effects of a Reset

The SC module resets to a disabled condition.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                       |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                    |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                            |  |  |  |  |  |