Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               |                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                |                                                                          |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b; D/A 1x9b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 14-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f753-i-st |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

.

| IADI  | ABLE 2-3: PICTOF/33/HV/33 SPECIAL REGISTERS SUMMART BANK 2                                                                                                                         |       |                                                            |                               |                  |                |               |           |           |                     |                                 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------|-------------------------------|------------------|----------------|---------------|-----------|-----------|---------------------|---------------------------------|

| Addr  | Name                                                                                                                                                                               | Bit 7 | Bit 6                                                      | Bit 5                         | Bit 4            | Bit 3          | Bit 2         | Bit 1     | Bit 0     | Value on<br>POR/BOR | Value on<br>all other<br>Resets |

| Ban   | Bank 2                                                                                                                                                                             |       |                                                            |                               |                  |                |               |           |           |                     |                                 |

| 100h  | INDF                                                                                                                                                                               |       |                                                            |                               | INDF             | <7:0>          |               |           |           | XXXX XXXX           | XXXX XXXX                       |

| 101h  | TMR0                                                                                                                                                                               |       |                                                            |                               | TMR              | )<7:0>         |               |           |           | XXXX XXXX           | uuuu uuuu                       |

| 102h  | PCL                                                                                                                                                                                |       |                                                            |                               | PCL              | <7:0>          |               |           |           | 0000 0000           | 0000 0000                       |

| 103h  | STATUS                                                                                                                                                                             | IRP   | RP1                                                        | RP0                           | TO               | PD             | Z             | DC        | С         | 0001 1xxx           | 000q quuu                       |

| 104h  | FSR                                                                                                                                                                                |       |                                                            | •                             | FSR              | <7:0>          | •             | •         |           | xxxx xxxx           | uuuu uuuu                       |

| 105h  | LATA                                                                                                                                                                               | —     | _                                                          | LATA5                         | LATA4            | _              | LATA2         | LATA1     | LATA0     | xx -xxx             | uu -uuu                         |

| 106h  | —                                                                                                                                                                                  |       |                                                            |                               | Unimple          | emented        |               |           |           | _                   | _                               |

| 107h  | LATC                                                                                                                                                                               | _     | _                                                          | LATC5                         | LATC4            | LATC3          | LATC2         | LATC1     | LATC0     | xx xxxx             | uu uuuu                         |

| 108h  | IOCAN                                                                                                                                                                              | _     | _                                                          | IOCAN5                        | IOCAN4           | IOCAN3         | IOCAN2        | IOCAN1    | IOCAN0    | 00 0000             | 00 0000                         |

| 109h  | IOCCN                                                                                                                                                                              | —     | _                                                          | IOCCN5                        | IOCCN4           | IOCCN3         | IOCCN2        | IOCCN1    | IOCCN0    | 00 0000             | 00 0000                         |

| 10Ah  | PCLATH                                                                                                                                                                             | _     |                                                            | —                             |                  | F              | PCLATH<4:0:   | >         |           | 0 0000              | 0 0000                          |

| 10Bh  | INTCON                                                                                                                                                                             | GIE   | PEIE                                                       | TOIE                          | INTE             | IOCIE          | T0IF          | INTF      | IOCIF     | 0000 0000           | 0000 0000                       |

| 10Ch  | WPUA                                                                                                                                                                               | —     | _                                                          | WPUA5                         | WPUA4            | WPUA3          | WPUA2         | WPUA1     | WPUA0     | 11 1111             | 11 1111                         |

| 10Dh  | WPUC                                                                                                                                                                               | _     |                                                            | WPUC5                         | WPUC4            | WPUC3          | WPUC2         | WPUC1     | WPUC0     | 11 1111             | 11 1111                         |

| 10Eh  | SLRCONC                                                                                                                                                                            | _     |                                                            | SLRC5                         | SLRC4            | -              | —             | _         | _         | 00                  | 00                              |

| 10Fh  | PCON                                                                                                                                                                               | —     | -                                                          | _                             | _                | —              | —             | POR       | BOR       | qq                  | uu                              |

| 110h  | TMR2                                                                                                                                                                               |       | TMR2<7:0>                                                  |                               |                  |                |               |           |           | 0000 0000           | 0000 0000                       |

| 111h  | PR2                                                                                                                                                                                |       | PR2<7:0>                                                   |                               |                  |                |               |           | 1111 1111 | 1111 1111           |                                 |

| 112h  | T2CON                                                                                                                                                                              | —     |                                                            | T2OUTF                        | PS<3:0>          |                | TMR2ON        | T2CKF     | PS<1:0>   | -000 0000           | -000 0000                       |

| 113h  | HLTMR1                                                                                                                                                                             |       | F                                                          | Iolding Registe               | er for the 8-bit | Hardware Lim   | nit Timer1 Co | unt       |           | 0000 0000           | 0000 0000                       |

| 114h  | HLTPR1                                                                                                                                                                             |       |                                                            | HL                            | TMR1 Module      | e Period Regis | ster          |           |           | 1111 1111           | 1111 1111                       |

| 115h  | HLT1CON0                                                                                                                                                                           | —     |                                                            | H1OUT                         | PS<3:0>          |                | H1ON          | H1CKF     | PS<1:0>   | -000 0000           | -000 0000                       |

| 116h  | HLT1CON1                                                                                                                                                                           | H1FES | H1RES                                                      | _                             |                  | H1ERS<2:0>     |               | H1FEREN   | H1REREN   | 11-0 0000           | 11-0 0000                       |

| 117h  | HLTMR2                                                                                                                                                                             |       | Holding Register for the 8-bit Hardware Limit Timer2 Count |                               |                  |                |               |           | 0000 0000 | 0000 0000           |                                 |

| 118h  | HLTPR2                                                                                                                                                                             |       | HLTMR2 Module Period Register                              |                               |                  |                |               |           |           | 1111 1111           | 1111 1111                       |

| 119h  | HLT2CON0                                                                                                                                                                           | _     |                                                            | H2OUTPS<3:0> H2ON H2CKPS<1:0> |                  |                |               | -000 0000 | -000 0000 |                     |                                 |

| 11Ah  | HLT2CON1                                                                                                                                                                           | H2FES | H2RES — H2ERS<2:0> H2FEREN H2REREN                         |                               |                  |                | 11-0 0000     | 11-0 0000 |           |                     |                                 |

| 11Bh  | _                                                                                                                                                                                  |       | Unimplemented                                              |                               |                  |                |               |           |           | _                   | —                               |

| 11Ch  | _                                                                                                                                                                                  |       |                                                            |                               | Unimple          | emented        |               |           |           | _                   | _                               |

| 11Dh  | —                                                                                                                                                                                  |       |                                                            |                               | Unimple          | emented        |               |           |           | _                   | _                               |

| 11Eh  | SLPCCON0                                                                                                                                                                           | SC1EN | _                                                          | —                             | SC1POL           | SC1TS          | S<1:0>        | —         | SC1INS    | 0-00 00-0           | 0-00 00-0                       |

| 11Fh  | SLPCCON1                                                                                                                                                                           |       | _                                                          | _                             | SC1RNG           |                | SC1ISI        | ET<3:0>   |           | 0 0000              | 0 0000                          |

| Logor | $\mathbf{n}$ , $\mathbf{n}$ = Unimplemented locations read as (i) $\mathbf{u}$ = unchanged $\mathbf{x}$ = unknown $\mathbf{a}$ = value depends on condition shaded = unimplemented |       |                                                            |                               |                  |                |               |           |           |                     |                                 |

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition shaded = unimplemented.

#### 2.3.7 PIR2 REGISTER

The PIR2 register contains the Peripheral Interrupt flag bits, as shown in Register 2-7.

| Note: | Interrupt flag bits are set when an interrupt<br>condition occurs, regardless of the state of<br>its corresponding enable bit or the Global |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | Enable bit, GIE of the INTCON register.                                                                                                     |  |  |  |  |  |

|       | User software should ensure the                                                                                                             |  |  |  |  |  |

|       | appropriate interrupt flag bits are clear prior                                                                                             |  |  |  |  |  |

|       | to enabling an interrupt.                                                                                                                   |  |  |  |  |  |

### REGISTER 2-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | U-0 | R/W-0 | R/W-0 | U-0 | R/W-0  | U-0 | R/W-0  |

|-------|-----|-------|-------|-----|--------|-----|--------|

| —     | —   | C2IF  | C1IF  | —   | COG1IF |     | CCP1IF |

| bit 7 |     |       |       |     |        |     | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | C2IF: Comparator 1 Interrupt Flag bit                                                                                                             |

|         | 1 = Comparator output (C2OUT bit) has changed (must be cleared in software)                                                                       |

|         | 0 = Comparator output (C2OUT bit) has not changed                                                                                                 |

| bit 4   | C1IF: Comparator 1 Interrupt Flag bit                                                                                                             |

|         | 1 = Comparator output (C1OUT bit) has changed (must be cleared in software)                                                                       |

|         | 0 = Comparator output (C1OUT bit) has not changed                                                                                                 |

| bit 3   | Unimplemented: Read as '0'                                                                                                                        |

| bit 2   | COG1IF: COG 1 Interrupt Flag bit                                                                                                                  |

|         | 1 = COG1 has generated an auto-shutdown interrupt                                                                                                 |

|         | 0 = COG1 has NOT generated an auto-shutdown interrupt                                                                                             |

| bit 1   | Unimplemented: Read as '0'                                                                                                                        |

| bit 0   | CCP1IF: ECCP Interrupt Flag bit                                                                                                                   |

|         | Capture Mode                                                                                                                                      |

|         | 1 = A TMR1 register capture occurred (must be cleared in software)                                                                                |

|         | 0 = No TMR1 register capture occurred                                                                                                             |

|         | Compare Mode                                                                                                                                      |

|         | <ul> <li>1 = A TMR1 register compare match occurred (must be cleared in software)</li> <li>0 = No TMR1 register compare match occurred</li> </ul> |

|         | PWM mode                                                                                                                                          |

|         | Unused in this mode                                                                                                                               |

|         |                                                                                                                                                   |

| U-0     | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | WPUC5 | WPUC4 | WPUC3 | WPUC2 | WPUC1 | WPUC0 |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Legend: |     |       |       |       |       |       |       |

#### REGISTER 5-15: WPUC: WEAK PULL-UP PORTC REGISTER

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 5-0 WPUC<5:0>: Weak Pull-up Control bits<sup>(1,2,3)</sup> 1 = Pull-up enabled

0 = Pull-up disabled

**Note 1:** Global RAPU must be enabled for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in Output mode (TRISC = 0).

- **3:** The RC3 pull-up is enabled when configured as MCLR in the Configuration Word, otherwise it is disabled as an input and reads as '0'.

#### REGISTER 5-16: IOCCP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOCCP<5:0>:** Interrupt-on-Change Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

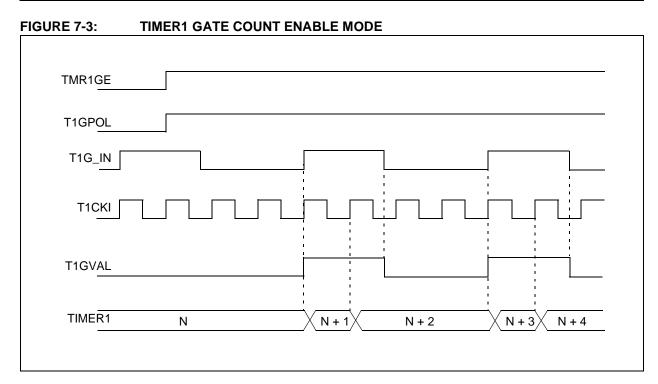

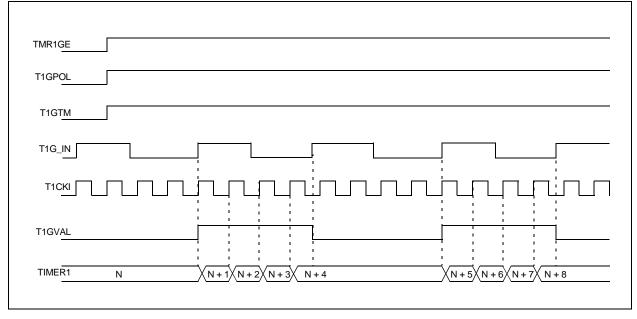

# FIGURE 7-4: TIMER1 GATE TOGGLE MODE

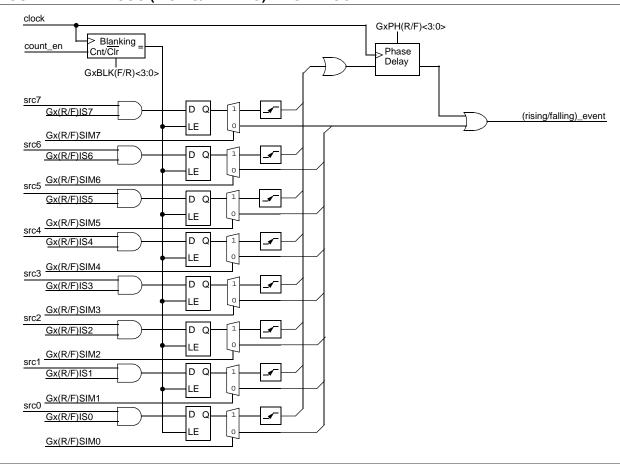

# FIGURE 11-2: COG (RISING/FALLING) INPUT BLOCK

|                  |                                                                                                                                                                                                                                                                                                                                                                                                     |                    |      |                                                       |                                | DAM O/C | D 444 0/2 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------------------------------------------------------|--------------------------------|---------|-----------|

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                             | U-0                | U-0  | U-0                                                   | U-0                            | R/W-0/0 | R/W-0/0   |

| GxRDBTS          | GxFDBTS                                                                                                                                                                                                                                                                                                                                                                                             | —                  | —    | —                                                     | —                              | GxCS    | i<1:0>    |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                                     |                    |      |                                                       |                                |         | bit (     |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                                     |                    |      |                                                       |                                |         |           |

| R = Readable     | bit                                                                                                                                                                                                                                                                                                                                                                                                 | W = Writable       | bit  | U = Unimpler                                          | mented bit, read               | as '0'  |           |

| u = Bit is unch  | anged                                                                                                                                                                                                                                                                                                                                                                                               | x = Bit is unknown |      | -n/n = Value at POR and BOR/Value at all other Resets |                                |         |           |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                     | '0' = Bit is clea  | ared | q = Value dep                                         | q = Value depends on condition |         |           |

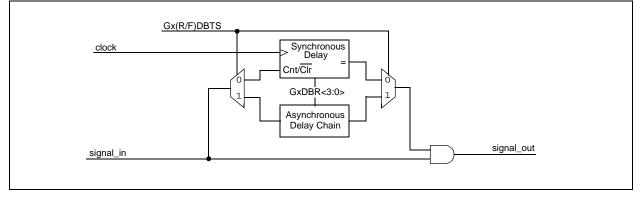

| bit 6            | <ul> <li>1 = Delay chain and COGxDBR are used for dead-band timing generation</li> <li>0 = COGx_clk and COGxDBR are used for dead-band timing generation</li> <li>GxFDBTS: COGx Falling Event Dead-band Timing Source Select bit</li> <li>1 = Delay chain and COGxDF are used for dead-band timing generation</li> <li>0 = COGx_clk and COGxDBF are used for dead-band timing generation</li> </ul> |                    |      |                                                       |                                |         |           |

| bit 5-2          | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                          |                    |      |                                                       |                                |         |           |

| bit 1-0          | GxCS<1:0>: COGx Clock Source Select bits<br>11 = Reserved<br>10 = HFINTOSC (stays active during Sleep)<br>01 = Fosc/4<br>00 = Fosc                                                                                                                                                                                                                                                                  |                    |      |                                                       |                                |         |           |

### REGISTER 11-2: COGxCON1: COG CONTROL REGISTER 1

| ADC Clock Period (TAD) |           | Device Frequency (Fosc) |                         |                               |                               |

|------------------------|-----------|-------------------------|-------------------------|-------------------------------|-------------------------------|

| ADC Clock Source       | ADCS<2:0> | 20 MHz                  | 8 MHz                   | 4 MHz                         | 1 MHz                         |

| Fosc/2                 | 000       | 100 ns <sup>(2)</sup>   | 250 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>         | 2.0 μs                        |

| Fosc/4                 | 100       | 200 ns <sup>(2)</sup>   | 500 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>         | 4.0 μs                        |

| Fosc/8                 | 001       | 400 ns <sup>(2)</sup>   | 1.0 μs <sup>(2)</sup>   | 2.0 μs                        | 8.0 μs <sup>(3)</sup>         |

| Fosc/16                | 101       | 800 ns <sup>(2)</sup>   | 2.0 μs                  | 4.0 μs                        | 16.0 μs <b><sup>(3)</sup></b> |

| Fosc/32                | 010       | 1.6 μs                  | 4.0 μs                  | 8.0 μs <sup>(3)</sup>         | 32.0 μs <sup>(3)</sup>        |

| Fosc/64                | 110       | 3.2 μs                  | 8.0 μs <sup>(3)</sup>   | 16.0 μs <b><sup>(3)</sup></b> | 64.0 μs <sup>(3)</sup>        |

| FRC                    | x11       | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup> | 2-6 μs <sup>(1,4)</sup>       | 2-6 μs <sup>(1,4)</sup>       |

### TABLE 12-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES (VDD $\geq$ 3.0V)

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

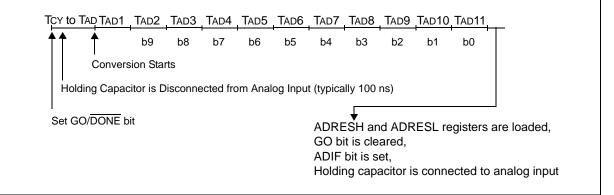

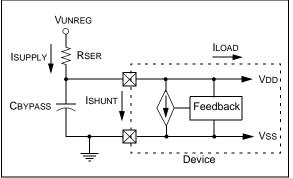

### FIGURE 12-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 12.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note: | The ADIF bit is set at the completion of |

|-------|------------------------------------------|

|       | every conversion, regardless of whether  |

|       | or not the ADC interrupt is enabled.     |

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the Interrupt Service Routine.

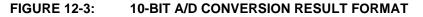

#### 12.1.6 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON0 register controls the output format.

Figure 12-4 shows the two output formats.

### 12.2 ADC Operation

#### 12.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |  |  |

|-------|------------------------------------------|--|--|

|       | same instruction that turns on the ADC.  |  |  |

|       | Refer to Section 12.2.6 "A/D Conver-     |  |  |

|       | sion Procedure".                         |  |  |

### 12.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF flag bit

- Update the ADRESH:ADRESL registers with new conversion result

#### 12.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete Analog-to-Digital conversion sample. Instead, the ADRESH:ADRESL register pair will retain the value of the previous conversion. Additionally, a 2 TAD delay is required before another acquisition can be initiated. Following this delay, an input acquisition is automatically started on the selected channel.

| Note: | A device Reset forces all registers to their |  |  |

|-------|----------------------------------------------|--|--|

|       | Reset state. Thus, the ADC module is         |  |  |

|       | turned off and any pending conversion is     |  |  |

|       | terminated.                                  |  |  |

### 12.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

### 12.2.5 SPECIAL EVENT TRIGGER

The CCP Special Event Trigger allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

# See Section 10.0 "Capture/Compare/PWM Modules" for more information.

### 12.4 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 12-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 12-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed),

an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 12-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### EQUATION 12-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{I}{2047}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} \ charged \ to \ within \ 1/2 \ lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED}$$

$$V_{APPLIED}\left(1-e^{\frac{-1}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{2047}\right) \quad (combining [1] and [2])$$

Solving for TC:

$$Tc = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37us$

Therefore:

$$TACQ = 2\mu s + 1.37\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.67\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

# 18.2 Instruction Descriptions

| ADDLW            | Add literal and W                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDLW k                                                                                                      |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | $(W) + k \to (W)$                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                               |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                           |

| Operands:        | $0 \leq k \leq 255$                                                                                                |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                    |

| Status Affected: | Z                                                                                                                  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W<br>register. |

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                         |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                        |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' is '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |

Bit Test f, Skip if Clear

BTFSC

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

AND W with f

ANDWF

| Name                  | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 Bit 10/2 |       | Bit 9/1 | Bit 8/0 | Register<br>on Page |  |

|-----------------------|------|---------|---------|----------|----------|-------------------|-------|---------|---------|---------------------|--|

| CONFIG <sup>(1)</sup> | 13:8 | _       | _       | DEBUG    | CLKOUTEN | WRT<              | <1:0> | BOREI   | N<1:0>  | 150                 |  |

| CONFIG                | 7:0  | —       | CP      | MCLRE    | PWRTE    | WDTE              |       |         | FOSC0   | 150                 |  |

TABLE 19-9: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

Legend: — = unimplemented location, read as '1'. Shaded cells are not used by Watchdog Timer.

**Note 1:** See Register 19-1 for operation of all Configuration Word register bits.

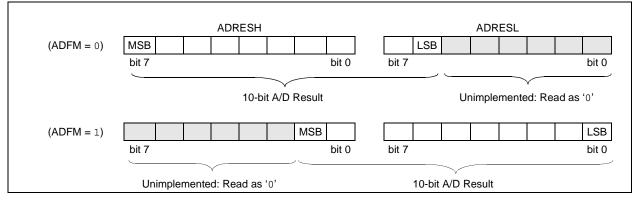

### 19.10 In-Circuit Serial Programming™

The PIC16F753/HV753 microcontrollers can be serially programmed while in the end application circuit. This is simply done with five connections for:

- clock

- data

- power

- ground

- programming voltage

This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the ICSPDAT and ICSPCLK pins low, while raising the MCLR (VPP) pin from VIL to VIHH. See the *PIC16F753/HV753 Flash Memory Programming Specification* (DS41686) for more information. ICSPDAT becomes the programming data and ICSPCLK becomes the programming clock. Both ICSPDAT and ICSPCLK are Schmitt Trigger inputs in Program/Verify mode.

A typical In-Circuit Serial Programming connection is shown in Figure 19-11.

#### FIGURE 19-11: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

Note: To erase the device, VDD must be above the Bulk Erase VDD minimum given in the *PIC16F753/HV753* Flash Memory *Programming Specification* (DS41686).

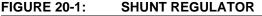

# 20.0 SHUNT REGULATOR (PIC16HV753 ONLY)

The PIC16HV753 devices include a permanent internal 5 volt (nominal) shunt regulator in parallel with the VDD pin. This eliminates the need for an external voltage regulator in systems sourced by an unregulated supply. All external devices connected directly to the VDD pin will share the regulated supply voltage and contribute to the total VDD supply current (ILOAD).

# 20.1 Regulator Operation

A shunt regulator generates a specific supply voltage by creating a voltage drop across a pass resistor RSER. The voltage at the VDD pin of the microcontroller is monitored and compared to an internal voltage reference. The current through the resistor is then adjusted, based on the result of the comparison, to produce a voltage drop equal to the difference between the supply voltage VUNREG and the VDD of the microcontroller. See Figure 20-1 for voltage regulator schematic.

An external current limiting resistor, RSER, located between the unregulated supply, VUNREG, and the VDD pin, drops the difference in voltage between VUNREG and VDD. RSER must be between RMAX and RMIN as defined by Equation 20-1.

### EQUATION 20-1: RSER LIMITING RESISTOR

$$RMAX = \frac{(VUMIN - 5V)}{1.05 \cdot (1 MA + ILOAD)}$$

$$RMIN = \frac{(VUMAX - 5V)}{0.95 \bullet (50 \text{ MA})}$$

Where:

- RMAX = maximum value of RSER (ohms)

- RMIN = minimum value of RSER (ohms)

- VUMIN = minimum value of VUNREG

- VUMAX = maximum value of VUNREG

- VDD = regulated voltage (5V nominal)

- ILOAD = maximum expected load current in mA including I/O pin currents and external circuits connected to VDD.

- 1.05 = compensation for +5% tolerance of RSER

- 0.95 = compensation for -5% tolerance of RSER

# 20.2 Regulator Considerations

The supply voltage VUNREG and load current are not constant. Therefore, the current range of the regulator is limited. Selecting a value for RSER must take these three factors into consideration.

Since the regulator uses the band gap voltage as the regulated voltage reference, this voltage reference is permanently enabled in the PIC16HV753 devices.

The shunt regulator will still consume current when below operating voltage range for the shunt regulator.

# 20.3 Design Considerations

For more information on using the shunt regulator and managing current load, see Application Note *AN1035*, *Designing with HV Microcontrollers* (DS01035).

### 21.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 21.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

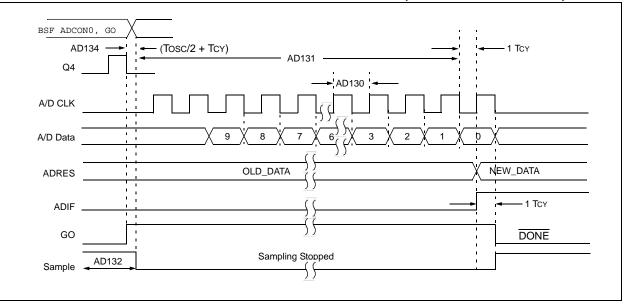

| PIC16F753    |                 | Standard Operating Conditions (unless otherwise stated)<br>Sleep mode |                         |       |       |       |            |                                               |  |  |

|--------------|-----------------|-----------------------------------------------------------------------|-------------------------|-------|-------|-------|------------|-----------------------------------------------|--|--|

| PIC16H       | V753            |                                                                       |                         |       |       |       |            |                                               |  |  |

| Param Device |                 | Min.                                                                  | Тур†                    | Max.  | Max.  | Units | Conditions |                                               |  |  |

| No.          | Characteristics | IVIIII.                                                               | турт                    | 85°C  | 125°C | Units | Vdd        | Note                                          |  |  |

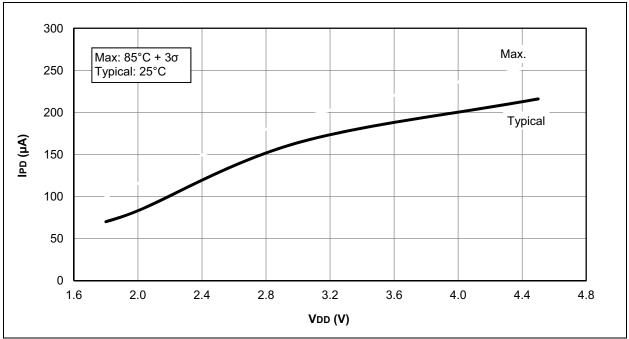

|              | Power-down Bas  | e Curre                                                               | ent (IPD) <sup>(2</sup> | 2)    |       |       |            |                                               |  |  |

| D020         |                 |                                                                       | 0.05                    | 0.50  | 3.50  | μA    | 2.0        | WDT, BOR, Comparator, VREF and                |  |  |

|              |                 | —                                                                     | 0.15                    | 1.00  | 4.00  | μA    | 3.0        | T1OSC disabled                                |  |  |

|              |                 | _                                                                     | 0.35                    | 1.50  | 5.00  | μA    | 5.0        |                                               |  |  |

| D020         |                 |                                                                       | 70                      | 130   | 140   | μA    | 2.0        |                                               |  |  |

|              |                 | _                                                                     | 140                     | 175   | 185   | μA    | 3.0        |                                               |  |  |

|              |                 | _                                                                     | 175                     | 230   | 250   | μA    | 4.5        |                                               |  |  |

|              | Power-down Bas  | e Curre                                                               | ent (IPD) <sup>(2</sup> | 2, 3) |       |       |            |                                               |  |  |

| D021         |                 |                                                                       | 0.96                    | 1.30  | 3.72  | μA    | 2.0        | WDT Current <sup>(1)</sup>                    |  |  |

|              |                 |                                                                       | 1.05                    | 2.10  | 6.50  | μA    | 3.0        |                                               |  |  |

|              |                 |                                                                       | 1.87                    | 2.92  | 6.86  | μA    | 5.0        |                                               |  |  |

| D021         |                 |                                                                       | 66                      | 127   | 141   | μA    | 2.0        |                                               |  |  |

|              |                 |                                                                       | 137                     | 172   | 176   | μA    | 3.0        | 7                                             |  |  |

|              |                 |                                                                       | 176                     | 228   | 233   | μA    | 4.5        |                                               |  |  |

| D022         |                 |                                                                       | 4                       | 7     | 10    | μA    | 3.0        | BOR Current <sup>(1)</sup>                    |  |  |

|              |                 |                                                                       | 5                       | 8     | 11    | μA    | 5.0        |                                               |  |  |

| D022         |                 |                                                                       | 140                     | 175   | 180   | μA    | 3.0        |                                               |  |  |

|              |                 |                                                                       | 178                     | 230   | 236   | μA    | 4.5        |                                               |  |  |

| D023         |                 |                                                                       | 160                     | 345   | 375   | μA    | 2.0        | CxSP = 1, Comparator Current <sup>(1)</sup> , |  |  |

|              |                 |                                                                       | 180                     | 370   | 405   | μA    | 3.0        | single comparator enabled                     |  |  |

|              |                 |                                                                       | 220                     | 410   | 445   | μA    | 5.0        |                                               |  |  |

| D023         |                 |                                                                       | 225                     | 380   | 380   | μA    | 2.0        |                                               |  |  |

|              |                 |                                                                       | 250                     | 420   | 420   | μA    | 3.0        | 7                                             |  |  |

|              |                 |                                                                       | 381                     | 500   | 500   | μA    | 4.5        |                                               |  |  |

| D024         |                 | _                                                                     | 50                      | 105   | 115   | μA    | 2.0        | CxSP = 0, Comparator Current <sup>(1)</sup> , |  |  |

|              |                 |                                                                       | 55                      | 110   | 120   | μA    | 3.0        | single comparator enabled                     |  |  |

|              |                 |                                                                       | 70                      | 120   | 132   | μA    | 5.0        | 7                                             |  |  |

| D024         |                 | —                                                                     | 115                     | 200   | 200   | μA    | 2.0        |                                               |  |  |

|              |                 | _                                                                     | 150                     | 220   | 220   | μA    | 3.0        |                                               |  |  |

|              |                 |                                                                       | 240                     | 277   | 277   | μA    | 4.5        | 1                                             |  |  |

#### TABLE 22-3: POWER-DOWN CURRENTS (IPD) (1,2)

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral △ current can be determined by subtracting the base IPD current from this limit. Max values should be used when calculating total current consumption.

- 2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

- 3: Shunt regulator is always ON and always draws operating current.

#### FIGURE 22-11: PIC16F753/HV753 A/D CONVERSION TIMING (ADC CLOCK FROM FRC)

#### TABLE 22-19: OPERATIONAL AMPLIFIER (OPA)

| DC CHARACTERISTICS |        |                        | Standard Operating Conditions (unless otherwise stated):<br>VDD = 3.0 Temperature 25°C, High-Power Mode |      |      |         |            |  |  |

|--------------------|--------|------------------------|---------------------------------------------------------------------------------------------------------|------|------|---------|------------|--|--|

| Param<br>No.       | Symbol | Parameters             | Min.                                                                                                    | Тур† | Max. | Units   | Conditions |  |  |

| OPA12              | GBWP   | Gain Bandwidth Product | -                                                                                                       | 3    | —    | MHz     |            |  |  |

| OPA13*             | Ton    | Turn on Time           |                                                                                                         | —    | 10   | μs      |            |  |  |

| OPA14*             | Рм     | Phase Margin           |                                                                                                         | 60   |      | degrees |            |  |  |

| OPA15*             | Sr     | Slew Rate              | 2                                                                                                       | —    | —    | V/µs    |            |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

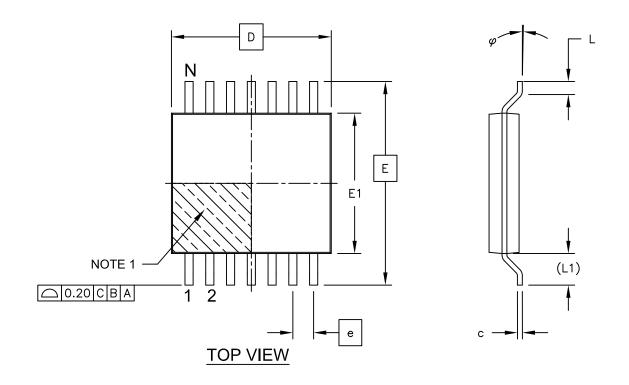

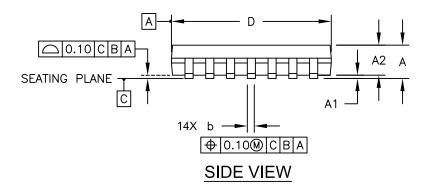

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087C Sheet 1 of 2

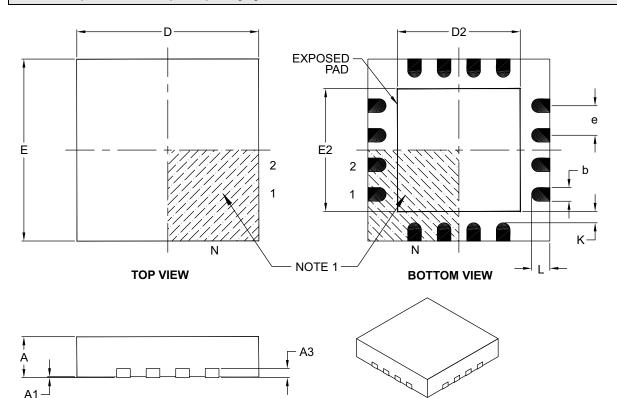

### 16-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS |          |      |  |  |  |

|------------------------|------------------|-------------|----------|------|--|--|--|

|                        | Dimension Limits | MIN         | NOM      | MAX  |  |  |  |

| Number of Pins         | N                |             | 16       |      |  |  |  |

| Pitch                  | e                | 0.65 BSC    |          |      |  |  |  |

| Overall Height         | A                | 0.80        | 0.90     | 1.00 |  |  |  |

| Standoff               | A1               | 0.00        | 0.02     | 0.05 |  |  |  |

| Contact Thickness      | A3               |             | 0.20 REF |      |  |  |  |

| Overall Width          | E                |             | 4.00 BSC |      |  |  |  |

| Exposed Pad Width      | E2               | 2.50        | 2.65     | 2.80 |  |  |  |

| Overall Length         | D                |             | 4.00 BSC |      |  |  |  |

| Exposed Pad Length     | D2               | 2.50        | 2.65     | 2.80 |  |  |  |

| Contact Width          | b                | 0.25        | 0.30     | 0.35 |  |  |  |

| Contact Length         | L                | 0.30        | 0.40     | 0.50 |  |  |  |

| Contact-to-Exposed Pad | К                | 0.20        | -        | _    |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-127B