## Microchip Technology - PIC16HV753-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                  |

| Data Converters            | A/D 8x10b; D/A 1x9b                                                      |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv753-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                            | Function     | Input<br>Type | Output<br>Type | Description                                |  |  |

|-----------------------------------------------------------------|--------------|---------------|----------------|--------------------------------------------|--|--|

| RA0/AN0/C1IN0+/DACOUT/                                          | RA0          | TTL           | HP             | General purpose I/O with IOC and WPU.      |  |  |

| FVROUT/ICSPDAT                                                  | AN0          | AN            | _              | A/D Channel 0 input.                       |  |  |

|                                                                 | C1IN0+       | AN            | _              | Comparator C1 positive input.              |  |  |

|                                                                 | DACOUT       |               | AN             | DAC unbuffered Voltage Reference output.   |  |  |

|                                                                 | FVROUT       |               | AN             | DAC/FVR buffered Voltage Reference output. |  |  |

|                                                                 | ICSPDAT      | ST            | HP             | Serial Programming Data I/O.               |  |  |

| RA1/AN1/C1IN0-/C2IN0-/                                          | RA1          | TTL           | CMOS           | General purpose I/O with IOC and WPU.      |  |  |

| VREF+/FVRIN/ICSPCLK                                             | AN1          | AN            | _              | A/D Channel 1 input.                       |  |  |

|                                                                 | C1IN0-       | AN            | _              | Comparator C1 negative input.              |  |  |

|                                                                 | C2IN0-       | AN            | _              | Comparator C2 negative input.              |  |  |

|                                                                 | VREF+        | AN            | _              | A/D Positive Voltage Reference input.      |  |  |

|                                                                 | FVRIN        | AN            | _              | Voltage reference input.                   |  |  |

|                                                                 | ICSPCLK      | ST            | _              | Serial Programming Clock.                  |  |  |

| RA2/AN2/INT/C1OUT/                                              | RA2          | ST            | HP             | General purpose I/O with IOC and WPU.      |  |  |

| T0CKI/COG1FLT                                                   | AN2          | AN            | _              | A/D Channel 2 input.                       |  |  |

|                                                                 | INT          | ST            | _              | External interrupt.                        |  |  |

|                                                                 | C1OUT        | _             | HP             | Comparator C1 output.                      |  |  |

|                                                                 | <b>T0CKI</b> | ST            | _              | Timer0 clock input.                        |  |  |

|                                                                 | COG1FLT      | ST            |                | COG auto-shutdown fault input.             |  |  |

| RA3 <sup>(1)</sup> /T1G <sup>(3)</sup> /VPP/MCLR <sup>(4)</sup> | RA3          | TTL           | _              | General purpose input with WPU.            |  |  |

|                                                                 | T1G          | ST            | —              | Timer1 Gate input.                         |  |  |

|                                                                 | Vpp          | HV            | _              | Programming voltage.                       |  |  |

|                                                                 | MCLR         | ST            | —              | Master Clear w/internal pull-up.           |  |  |

| RA4/AN3/T1G <sup>(2)</sup> /CLKOUT                              | RA4          | TTL           | CMOS           | General purpose I/O with IOC and WPU.      |  |  |

| ·                                                               | AN3          | AN            | _              | A/D Channel 3 input.                       |  |  |

| ·                                                               | T1G          | ST            | _              | Timer1 Gate input.                         |  |  |

| ·                                                               | CLKOUT       | _             | CMOS           | Fosc/4 output.                             |  |  |

| RA5/T1CKI/COG1OUT0 <sup>(3)</sup> /                             | RA5          | TTL           | CMOS           | General purpose I/O with IOC and WPU.      |  |  |

| C2IN1-/CLKIN                                                    | T1CKI        | ST            | _              | Timer1 clock input.                        |  |  |

| ·                                                               | CLKIN        | ST            |                | External Clock input (EC mode).            |  |  |

| RC0/AN4/OPA1IN+/C2IN0+                                          | RC0          | TTL           | CMOS           | General purpose I/O with IOC and WPU.      |  |  |

| ·                                                               | AN4          | AN            | _              | A/D Channel 4 input.                       |  |  |

| ·                                                               | OPA1IN+      | AN            |                | Op amp positive input.                     |  |  |

|                                                                 | C2IN0+       | AN            |                | Comparator C2 positive input.              |  |  |

| RC1/AN5/OPA1IN-/C1IN1-/                                         | RC1          | TTL           | CMOS           | General purpose I/O with IOC and WPU.      |  |  |

| C2IN1-                                                          | AN5          | AN            | _              | A/D Channel 5 input.                       |  |  |

|                                                                 | OPA1IN-      | AN            | _              | Op amp negative input.                     |  |  |

| ·                                                               | C1IN1-       | AN            |                | Comparator C1 negative input.              |  |  |

|                                                                 |              | AN            |                | Comparator C2 negative input.              |  |  |

PIC16F753/HV753 PINOUT DESCRIPTION TABLE 1-1:

Note 1: Input only.

2: Default pin function via the APFCON register.

3: Alternate pin function via the APFCON register.

4: RA3 pull-up is enabled when pin is configured as MCLR in Configuration Word.

#### **TABLE 1-1:** PIC16F753/HV753 PINOUT DESCRIPTION (CONTINUED)

| Name                  | Function | Input<br>Type | Output<br>Type | Description                           |

|-----------------------|----------|---------------|----------------|---------------------------------------|

| RC2/AN6/SLPCIN/       | RC2      | TTL           | CMOS           | General purpose I/O with IOC and WPU. |

| OPA1OUT/C1IN2-/C2IN2- | AN6      | AN            | _              | A/D Channel 6 input.                  |

|                       | OPA1OUT  | AN            | HP             | Op amp output.                        |

|                       | C1IN2-   | AN            |                | Comparator C1 negative input.         |

|                       | C2IN2-   | AN            | _              | Comparator C2 negative input.         |

| RC3/AN7/C1IN3-/C2IN3- | RC3      | TTL           | CMOS           | General purpose I/O with IOC and WPU. |

|                       | AN7      | AN            | —              | A/D Channel 7 input.                  |

|                       | C1IN3-   | AN            | _              | Comparator C1 negative input.         |

|                       | C2IN3-   | AN            | _              | Comparator C2 negative input.         |

| RC4/COG1OUT1/C2OUT    | RC4      | TTL           | CMOS           | General purpose I/O with IOC and WPU. |

|                       | COG1OUT1 |               | CMOS           | COG output Channel 1.                 |

|                       | C2OUT    | —             | HP             | Comparator C2 output.                 |

| RC5/COG1OUT0/CCP1     | RC5      | TTL           | CMOS           | General purpose I/O with IOC and WPU. |

|                       | COG1OUT0 | —             | CMOS           | COG output Channel 0.                 |

|                       | CCP1     | _             | HP             | Capture/Compare/PWM 1.                |

| Vdd                   | Vdd      | Power         | -              | Positive supply.                      |

| Vss                   | Vss      | Power         | _              | Ground reference.                     |

CMOS = CMOS compatible input or output **Legend:** AN = Analog input or output TTL = TTL compatible input

= Schmitt Trigger input with CMOS levels ST

HP = High Power \* Alternate pin function.

= High Voltage ΗV

Note 1: Input only.

2: Default pin function via the APFCON register.

3: Alternate pin function via the APFCON register.

4: RA3 pull-up is enabled when pin is configured as MCLR in Configuration Word.

# PIC16F753/HV753

.

| IADI  | ABLE 2-3: FIC 10F 733/HV 733 SPECIAL REGISTERS SUMMART BAINS 2 |              |                                                            |           |             |                |             |                |                   |                     |                                 |

|-------|----------------------------------------------------------------|--------------|------------------------------------------------------------|-----------|-------------|----------------|-------------|----------------|-------------------|---------------------|---------------------------------|

| Addr  | Name                                                           | Bit 7        | Bit 6                                                      | Bit 5     | Bit 4       | Bit 3          | Bit 2       | Bit 1          | Bit 0             | Value on<br>POR/BOR | Value on<br>all other<br>Resets |

| Ban   | Bank 2                                                         |              |                                                            |           |             |                |             |                |                   |                     |                                 |

| 100h  | INDF                                                           |              |                                                            |           | INDF        | <7:0>          |             |                |                   | XXXX XXXX           | xxxx xxxx                       |

| 101h  | TMR0                                                           |              |                                                            |           | TMR         | )<7:0>         |             |                |                   | XXXX XXXX           | uuuu uuuu                       |

| 102h  | PCL                                                            |              |                                                            |           | PCL         | <7:0>          |             |                |                   | 0000 0000           | 0000 0000                       |

| 103h  | STATUS                                                         | IRP          | RP1                                                        | RP0       | TO          | PD             | Z           | DC             | С                 | 0001 1xxx           | 000q quuu                       |

| 104h  | FSR                                                            |              |                                                            | •         | FSR         | <7:0>          | •           | •              |                   | xxxx xxxx           | uuuu uuuu                       |

| 105h  | LATA                                                           | —            | _                                                          | LATA5     | LATA4       | _              | LATA2       | LATA1          | LATA0             | xx -xxx             | uu -uuu                         |

| 106h  | —                                                              |              |                                                            |           | Unimple     | emented        |             |                |                   | _                   | —                               |

| 107h  | LATC                                                           | _            | _                                                          | LATC5     | LATC4       | LATC3          | LATC2       | LATC1          | LATC0             | xx xxxx             | uu uuuu                         |

| 108h  | IOCAN                                                          | _            | _                                                          | IOCAN5    | IOCAN4      | IOCAN3         | IOCAN2      | IOCAN1         | IOCAN0            | 00 0000             | 00 0000                         |

| 109h  | IOCCN                                                          | —            | _                                                          | IOCCN5    | IOCCN4      | IOCCN3         | IOCCN2      | IOCCN1         | IOCCN0            | 00 0000             | 00 0000                         |

| 10Ah  | PCLATH                                                         | _            |                                                            | —         |             | F              | PCLATH<4:0: | >              |                   | 0 0000              | 0 0000                          |

| 10Bh  | INTCON                                                         | GIE          | PEIE                                                       | TOIE      | INTE        | IOCIE          | T0IF        | INTF           | IOCIF             | 0000 0000           | 0000 0000                       |

| 10Ch  | WPUA                                                           | —            | _                                                          | WPUA5     | WPUA4       | WPUA3          | WPUA2       | WPUA1          | WPUA0             | 11 1111             | 11 1111                         |

| 10Dh  | WPUC                                                           | _            |                                                            | WPUC5     | WPUC4       | WPUC3          | WPUC2       | WPUC1          | WPUC0             | 11 1111             | 11 1111                         |

| 10Eh  | SLRCONC                                                        | _            |                                                            | SLRC5     | SLRC4       | -              | —           | _              | _                 | 00                  | 00                              |

| 10Fh  | PCON                                                           | —            | -                                                          | _         | _           | —              | —           | POR            | BOR               | qq                  | uu                              |

| 110h  | TMR2                                                           |              |                                                            |           | TMR2        | 2<7:0>         |             |                |                   | 0000 0000           | 0000 0000                       |

| 111h  | PR2                                                            |              |                                                            |           | PR2-        | <7:0>          |             |                |                   | 1111 1111           | 1111 1111                       |

| 112h  | T2CON                                                          | —            | - T2OUTPS<3:0> TMR2ON T2CKPS<1:0>                          |           |             |                |             |                | -000 0000         | -000 0000           |                                 |

| 113h  | HLTMR1                                                         |              | Holding Register for the 8-bit Hardware Limit Timer1 Count |           |             |                |             |                |                   | 0000 0000           | 0000 0000                       |

| 114h  | HLTPR1                                                         |              |                                                            | HL        | TMR1 Module | e Period Regis | ster        |                |                   | 1111 1111           | 1111 1111                       |

| 115h  | HLT1CON0                                                       | —            |                                                            | H1OUT     | PS<3:0>     |                | H1ON        | H1CKF          | PS<1:0>           | -000 0000           | -000 0000                       |

| 116h  | HLT1CON1                                                       | H1FES        | H1RES                                                      | _         |             | H1ERS<2:0>     |             | H1FEREN        | H1REREN           | 11-0 0000           | 11-0 0000                       |

| 117h  | HLTMR2                                                         |              | Holding Register for the 8-bit Hardware Limit Timer2 Count |           |             |                |             |                |                   | 0000 0000           | 0000 0000                       |

| 118h  | HLTPR2                                                         |              | HLTMR2 Module Period Register                              |           |             |                |             |                |                   | 1111 1111           | 1111 1111                       |

| 119h  | HLT2CON0                                                       | _            | H2OUTPS<3:0> H2ON H2CKPS<1:0>                              |           |             |                |             | -000 0000      | -000 0000         |                     |                                 |

| 11Ah  | HLT2CON1                                                       | H2FES        | H2RES — H2ERS<2:0> H2FEREN H2REREN                         |           |             |                |             | 11-0 0000      | 11-0 0000         |                     |                                 |

| 11Bh  | _                                                              |              |                                                            |           | Unimple     | emented        |             |                |                   | —                   | —                               |

| 11Ch  | _                                                              |              |                                                            |           | Unimple     | emented        |             |                |                   | —                   | _                               |

| 11Dh  | —                                                              |              |                                                            |           | Unimple     | emented        |             |                |                   | _                   | _                               |

| 11Eh  | SLPCCON0                                                       | SC1EN        | _                                                          | —         | SC1POL      | SC1TS          | S<1:0>      | —              | SC1INS            | 0-00 00-0           | 0-00 00-0                       |

| 11Fh  | SLPCCON1                                                       |              | _                                                          | _         | SC1RNG      |                | SC1ISI      | ET<3:0>        |                   | 0 0000              | 0 0000                          |

| Logor | d: — = Unimple                                                 | manted laget | and read on to                                             | , unahana | مما بسابسم  |                | denende en  | aan dition aha | ملية مناسب المحام | and a set of a      |                                 |

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition shaded = unimplemented.

### 2.3.5 PIE2 REGISTER

The PIE2 register contains the Peripheral Interrupt Enable bits, as shown in Register 2-5.

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

| U-0          | U-0          | R/W-0            | R/W-0          | U-0              | R/W-0            | U-0            | R/W-0  |

|--------------|--------------|------------------|----------------|------------------|------------------|----------------|--------|

| _            | —            | C2IE             | C1IE           |                  | COG1IE           |                | CCP1IE |

| bit 7        |              |                  |                |                  |                  |                | bit (  |

| Legend:      |              |                  |                |                  |                  |                |        |

| R = Readab   | le bit       | W = Writable     | bit            | U = Unimple      | mented bit, read | d as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is se  | t              | '0' = Bit is cle | eared            | x = Bit is unl | known  |

|              |              |                  |                |                  |                  |                |        |

| bit 7-6      | Unimplemer   | nted: Read as    | ʻ0'            |                  |                  |                |        |

| bit 5        | C2IE: Compa  | arator 2 Interru | pt Enable bit  |                  |                  |                |        |

|              |              | the Comparato    | •              |                  |                  |                |        |

|              | 0 = Disables | the Comparate    | or 2 interrupt |                  |                  |                |        |

| bit 4        |              | arator 1 Interru |                |                  |                  |                |        |

|              |              | the Comparato    |                |                  |                  |                |        |

| <b>1</b>     |              | the Comparate    | -              |                  |                  |                |        |

| bit 3        | -            | nted: Read as    |                |                  |                  |                |        |

| bit 2        |              | G 1 Interrupt F  | 0              |                  |                  |                |        |

|              | 1 = COG1 int | terrupt enabled  | l              |                  |                  |                |        |

|              | 0 = COG1 int | terrupt disabled | t              |                  |                  |                |        |

| bit 1        | Unimplemer   | nted: Read as    | ʻ0'            |                  |                  |                |        |

| bit 0        | CCP1IE: CC   | P1 Interrupt Er  | able bit       |                  |                  |                |        |

|              |              | the CCP1 inter   |                |                  |                  |                |        |

|              | 0 = Disables | the CCP1 inte    | rrupt          |                  |                  |                |        |

## 3.3 Register Definitions: Flash Program Memory Control

|                                                              |       |                  |       |                   |       | -                 |       |

|--------------------------------------------------------------|-------|------------------|-------|-------------------|-------|-------------------|-------|

| R/W-0                                                        | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0             | R/W-0 |

|                                                              |       |                  | PMDA  | TL<7:0>           |       |                   |       |

| bit 7                                                        |       |                  |       |                   |       |                   | bit C |

|                                                              |       |                  |       |                   |       |                   |       |

| Legend:                                                      |       |                  |       |                   |       |                   |       |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit,$ |       |                  |       |                   |       | d as '0'          |       |

| -n = Value at Po                                             | OR    | '1' = Bit is set |       | '0' = Bit is clea | red   | x = Bit is unknow | n     |

#### REGISTER 3-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

bit 7-0 PMDATL<7:0>: Eight Least Significant Data bits to Write or Read from Program Memory

#### REGISTER 3-2: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PMADRL<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7 bit 0 |       |       |       |       |       |       |       |  |  |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 7-0 PMADRL<7:0>: Eight Least Significant Address bits for Program Memory Read/Write Operation

#### REGISTER 3-3: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|

| —     | —   |       | PMDATH<5:0> |       |       |       |       |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMDATH<5:0>**: Six Most Significant Data bits from Program Memory

#### REGISTER 3-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-0               | U-0 | U-0              | U-0 | U-0                 | U-0                   | R/W-0              | R/W-0  |

|-------------------|-----|------------------|-----|---------------------|-----------------------|--------------------|--------|

| _                 | _   | -                | —   | -                   | -                     | PMADR              | H<1:0> |

| bit 7             |     |                  | •   | •                   |                       |                    | bit 0  |

|                   |     |                  |     |                     |                       |                    |        |

| Legend:           |     |                  |     |                     |                       |                    |        |

| R = Readable bit  |     | W = Writable bit |     | U = Unimplemer      | nted bit, read as '0' |                    |        |

| -n = Value at POR |     | '1' = Bit is set |     | '0' = Bit is cleare | d                     | x = Bit is unknown |        |

bit 7-2 Unimplemented: Read as '0'

PMADRH<1:0>: Specifies the two Most Significant Address bits or High bits for Program Memory Reads.

bit 1-0

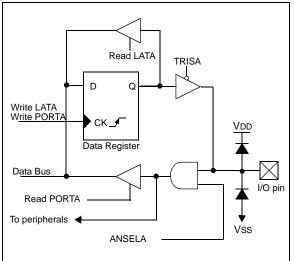

## 5.0 I/O PORTS

Depending on the device selected and peripherals enabled, there are up to two ports available. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three standard registers for its operation.

These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

- SLRCONx registers (slew rate)

The Data Latch (LATx registers) is useful for readmodify-write operations on the values that the I/O pins are driving.

A write operation to the LATx register has the same affect as a write to the corresponding PORTx register. A read of the LATx register reads the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports with analog functions also have an ANSELx register which can disable the digital input and save power. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 5-1.

#### FIGURE 5-1: GENERIC I/O PORTA OPERATION

#### EXAMPLE 5-1: INITIALIZING PORTA

| ; initializing the P | <pre>; This code example illustrates<br/>; initializing the PORTA register. The<br/>; other ports are initialized in the same<br/>; manner.</pre> |  |  |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| BANKSEL PORTA        | ;                                                                                                                                                 |  |  |  |  |  |  |  |  |

| CLRF PORTA           | ;Init PORTA                                                                                                                                       |  |  |  |  |  |  |  |  |

| BANKSEL LATA         | ;Data Latch                                                                                                                                       |  |  |  |  |  |  |  |  |

| CLRF LATA            | ;                                                                                                                                                 |  |  |  |  |  |  |  |  |

| BANKSEL ANSELA       | ;                                                                                                                                                 |  |  |  |  |  |  |  |  |

| CLRF ANSELA          | ;digital I/O                                                                                                                                      |  |  |  |  |  |  |  |  |

| BANKSEL TRISA        | ;                                                                                                                                                 |  |  |  |  |  |  |  |  |

| MOVLW B'00111000'    | ;Set RA<5:3> as inputs                                                                                                                            |  |  |  |  |  |  |  |  |

| MOVWF TRISA          | ;and set RA<2:0> as                                                                                                                               |  |  |  |  |  |  |  |  |

|                      | ;outputs                                                                                                                                          |  |  |  |  |  |  |  |  |

## 5.4 Additional Pin Functions

Every PORTA pin on the PIC16F753 has an interrupton-change option and a weak pull-up option. The next three sections describe these functions.

#### 5.4.1 ANSELA REGISTER

The ANSELA register (Register 5-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELA bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 5.4.2 WEAK PULL-UPS

Each of the PORTA pins, except RA3, has an individually configurable internal weak pull-up. Control bits WPUx enable or disable each pull-up. Refer to Register 5-6. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RAPU bit of the OPTION\_REG register. A weak pull-up is automatically enabled for RA3 when configured as MCLR and disabled when RA3 is an I/O. There is no software control of the MCLR pull-up.

### 5.4.3 INTERRUPT-ON-CHANGE

Each PORTA pin is individually configurable as an interrupt-on-change pin. Control bits IOCA enable or disable the interrupt function for each pin. Refer to Register 5-7. The interrupt-on-change is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTA. The 'mismatch' outputs of the last read are OR'd together to set the PORTA Change Interrupt Flag bit (IOCIF) in the INTCON register (Register 2-3).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

a) Any read of PORTA AND Clear flag bit IOCIF. This will end the mismatch condition;

OR

Any write of PORTA AND Clear flag bit IOCIF will end the mismatch condition;

A mismatch condition will continue to set flag bit IOCIF. Reading PORTA will end the mismatch condition and allow flag bit IOCIF to be cleared. The latch holding the last read value is not affected by a MCLR nor BOR Reset. After these Resets, the IOCIF flag will continue to be set if a mismatch is present.

**Note:** If a change on the I/O pin should occur when any PORTA operation is being executed, then the IOCIF interrupt flag may not get set.

| U-0     | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | WPUC5 | WPUC4 | WPUC3 | WPUC2 | WPUC1 | WPUC0 |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Legend: |     |       |       |       |       |       |       |

#### REGISTER 5-15: WPUC: WEAK PULL-UP PORTC REGISTER

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 5-0 WPUC<5:0>: Weak Pull-up Control bits<sup>(1,2,3)</sup> 1 = Pull-up enabled

0 = Pull-up disabled

**Note 1:** Global RAPU must be enabled for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in Output mode (TRISC = 0).

- **3:** The RC3 pull-up is enabled when configured as MCLR in the Configuration Word, otherwise it is disabled as an input and reads as '0'.

#### REGISTER 5-16: IOCCP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCCP5  | IOCCP4  | IOCCP3  | IOCCP2  | IOCCP1  | IOCCP0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOCCP<5:0>:** Interrupt-on-Change Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

## PIC16F753/HV753

| FIGURE 7-5:    | TIMER1 GATE SINGLE-PULSE MODE                                         |

|----------------|-----------------------------------------------------------------------|

|                |                                                                       |

| TMR1GE         |                                                                       |

| T1GPOL         |                                                                       |

| T1GSPM         |                                                                       |

| T1GG <u>O/</u> | <ul> <li>Cleared by hardware on<br/>falling edge of T1GVAL</li> </ul> |

| DONE           | Counting enabled on rising edge of T1G                                |

| T1G_IN         |                                                                       |

| Т1СКІ          |                                                                       |

| T1GV <u>AL</u> |                                                                       |

| TIMER1         | N N + 1 N + 2                                                         |

| TMR1GIF ◀      | Cleared by software Set by hardware on falling edge of T1GVAL         |

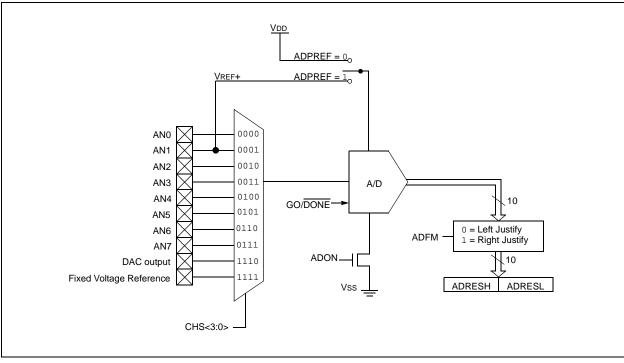

## 12.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

The ADC voltage reference is software selectable to either VDD or a voltage applied to the external reference pins.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake up the device from Sleep.

Figure 12-1 shows the block diagram of the ADC.

## FIGURE 12-1: ADC BLOCK DIAGRAM

Note: The ADRESL and ADRESH registers are read-only.

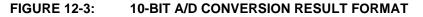

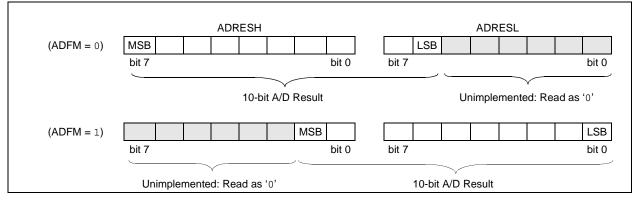

### 12.1.6 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON0 register controls the output format.

Figure 12-4 shows the two output formats.

## 12.2 ADC Operation

### 12.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|

|       | same instruction that turns on the ADC.  |  |  |  |  |  |  |  |  |

|       | Refer to Section 12.2.6 "A/D Conver-     |  |  |  |  |  |  |  |  |

|       | sion Procedure".                         |  |  |  |  |  |  |  |  |

## 12.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF flag bit

- Update the ADRESH:ADRESL registers with new conversion result

#### 12.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete Analog-to-Digital conversion sample. Instead, the ADRESH:ADRESL register pair will retain the value of the previous conversion. Additionally, a 2 TAD delay is required before another acquisition can be initiated. Following this delay, an input acquisition is automatically started on the selected channel.

| Note: | A device Reset forces all registers to their |  |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|--|

|       | Reset state. Thus, the ADC module is         |  |  |  |  |  |  |  |  |

|       | turned off and any pending conversion is     |  |  |  |  |  |  |  |  |

|       | terminated.                                  |  |  |  |  |  |  |  |  |

## 12.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

## 12.2.5 SPECIAL EVENT TRIGGER

The CCP Special Event Trigger allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

## See Section 10.0 "Capture/Compare/PWM Modules" for more information.

| Name                  | Bit 7                                                                                              | Bit 6                                                                                           | Bit 5     | Bit 4  | Bit 3                 | Bit 2    | Bit 1   | Bit 0   | Register<br>on Page |

|-----------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------|--------|-----------------------|----------|---------|---------|---------------------|

| ADCON0                | ADFM                                                                                               | _                                                                                               |           | CHS    | <3:0>                 |          | GO/DONE | ADON    | 109                 |

| ADCON1                | -                                                                                                  |                                                                                                 | ADCS<2:0> |        | —                     | —        | _       | ADPREF1 | 110                 |

| ANSELA                | _                                                                                                  | _                                                                                               | _         | ANSA4  | _                     | ANSA2    | ANSA1   | ANSA0   | 44                  |

| ADRESH <sup>(2)</sup> | Most Significant eight bits of the left shifted A/D result or two bits of the right shifted result |                                                                                                 |           |        |                       |          |         |         | 111*                |

| ADRESL <sup>(2)</sup> | Lea                                                                                                | Least Significant two bits of the left shifted result or eight bits of the right shifted result |           |        |                       |          |         |         | 109*                |

| PORTA                 | _                                                                                                  | _                                                                                               | RA5       | RA4    | RA3                   | RA2      | RA1     | RA0     | 43                  |

| INTCON                | GIE                                                                                                | PEIE                                                                                            | TOIE      | INTE   | IOCIE                 | T0IF     | INTF    | IOCIF   | 17                  |

| PIE1                  | TMR1GIE                                                                                            | ADIE                                                                                            | _         | _      | HLTMR2IE              | HLTMR1IE | TMR2IE  | TMR1IE  | 18                  |

| PIR1                  | TMR1GIF                                                                                            | ADIF                                                                                            | _         |        | HLTMR2IF              | HLTMR1IF | TMR2IF  | TMR1IF  | 20                  |

| TRISA                 | _                                                                                                  | —                                                                                               | TRISA5    | TRISA4 | TRISA3 <sup>(1)</sup> | TRISA2   | TRISA1  | TRISA0  | 43                  |

## TABLE 12-2: SUMMARY OF ASSOCIATED ADC REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

\* Page provides register information.

Note 1: TRISA3 always reads '1'.

2: Read-only register.

## 15.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed-signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- Independent comparator control

- Programmable input selection

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- Programmable Speed/Power optimization

- PWM shutdown

- Programmable and Fixed Voltage Reference

## 15.1 Comparator Overview

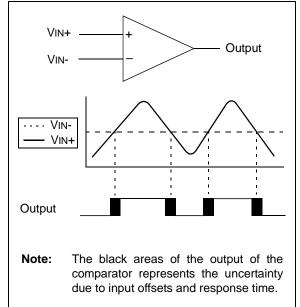

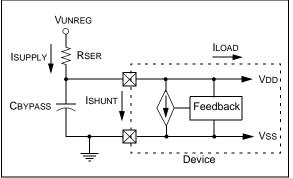

A single comparator is shown in Figure 15-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

#### FIGURE 15-1:

#### SINGLE COMPARATOR

### **19.5 Context Saving During Interrupts**

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Temporary holding registers W\_TEMP and STATUS\_TEMP should be placed in the last 16 bytes of GPR (see Figure 2-2). These 16 locations are common to all banks and do not require banking. This makes context save and restore operations simpler. The code shown in Example 19-1 can be used to:

- Store the W register

- Store the STATUS register

- · Execute the ISR code

- Restore the Status (and Bank Select Bit register)

- · Restore the W register

| Note: | The PIC16F753/HV753 does not require    |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | saving the PCLATH. However, if          |  |  |  |  |  |  |

|       | computed GOTOs are used in both the ISR |  |  |  |  |  |  |

|       | and the main code, the PCLATH must be   |  |  |  |  |  |  |

|       | saved and restored in the ISR.          |  |  |  |  |  |  |

#### EXAMPLE 19-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits |

|----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| MOVWF          | STATUS_TEMP        | ;Save status to bank zero STATUS_TEMP register                                                                            |

| :(ISR)         |                    | ;Insert user code here                                                                                                    |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                                                       |

| MOVWF          | STATUS             | ;Move W into STATUS register                                                                                              |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                                                                              |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                                                                                       |

#### 19.6 Watchdog Timer (WDT)

The Watchdog Timer is a free running timer, using LFINTOSC oscillator as its clock source. The WDT is enabled by setting the WDTE bit of the Configuration Word (default setting). When WDTE is set, the LFINTOSC will always be enabled to provide a clock source to the WDT module.

During normal operation, a WDT time-out generates a device Reset. If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation.

The WDT can be permanently disabled by programming the Configuration bit, WDTE, as clear (Section 19.1 "Configuration Bits").

#### 19.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

## 20.0 SHUNT REGULATOR (PIC16HV753 ONLY)

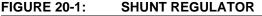

The PIC16HV753 devices include a permanent internal 5 volt (nominal) shunt regulator in parallel with the VDD pin. This eliminates the need for an external voltage regulator in systems sourced by an unregulated supply. All external devices connected directly to the VDD pin will share the regulated supply voltage and contribute to the total VDD supply current (ILOAD).

## 20.1 Regulator Operation

A shunt regulator generates a specific supply voltage by creating a voltage drop across a pass resistor RSER. The voltage at the VDD pin of the microcontroller is monitored and compared to an internal voltage reference. The current through the resistor is then adjusted, based on the result of the comparison, to produce a voltage drop equal to the difference between the supply voltage VUNREG and the VDD of the microcontroller. See Figure 20-1 for voltage regulator schematic.

An external current limiting resistor, RSER, located between the unregulated supply, VUNREG, and the VDD pin, drops the difference in voltage between VUNREG and VDD. RSER must be between RMAX and RMIN as defined by Equation 20-1.

## EQUATION 20-1: RSER LIMITING RESISTOR

$$RMAX = \frac{(VUMIN - 5V)}{1.05 \cdot (1 MA + ILOAD)}$$

$$RMIN = \frac{(VUMAX - 5V)}{0.95 \bullet (50 \text{ MA})}$$

Where:

- RMAX = maximum value of RSER (ohms)

- RMIN = minimum value of RSER (ohms)

- VUMIN = minimum value of VUNREG

- VUMAX = maximum value of VUNREG

- VDD = regulated voltage (5V nominal)

- ILOAD = maximum expected load current in mA including I/O pin currents and external circuits connected to VDD.

- 1.05 = compensation for +5% tolerance of RSER

- 0.95 = compensation for -5% tolerance of RSER

## 20.2 Regulator Considerations

The supply voltage VUNREG and load current are not constant. Therefore, the current range of the regulator is limited. Selecting a value for RSER must take these three factors into consideration.

Since the regulator uses the band gap voltage as the regulated voltage reference, this voltage reference is permanently enabled in the PIC16HV753 devices.

The shunt regulator will still consume current when below operating voltage range for the shunt regulator.

## 20.3 Design Considerations

For more information on using the shunt regulator and managing current load, see Application Note *AN1035*, *Designing with HV Microcontrollers* (DS01035).

## 22.1 Standard Operating Conditions

The standard operating conditions for any device are defined as: **Operating Voltage:**  $VDDMIN \le VDD \le VDDMAX$ Operating Temperature:  $TA\_MIN \le TA \le TA\_MAX$ VDD — Operating Supply Voltage<sup>(1)</sup> PIC16F753 VDDMIN (FOSC ≤ 8 MHz) ...... +2.0V VDDMAX (10 MHz < Fosc  $\leq$  20 MHz)......+5.5V PIC16HV753 VDDMIN (FOSC ≤ 8 MHz) ...... +2.0V VDDMAX (10 MHz < Fosc  $\leq$  20 MHz).....+5.0V TA — Operating Ambient Temperature Range Industrial Temperature Ta\_MIN .....--40°C Extended Temperature Note 1: See Parameter D001, DS Characteristics: Supply Voltage.

## PIC16F753/HV753

## TABLE 22-3: POWER-DOWN CURRENTS (IPD) (CONTINUED)<sup>(1,2)</sup>

| PIC16F753 |                 | Standard Operating Conditions (unless otherwise stated)<br>Sleep mode |                         |       |       |       |     |                                               |  |  |

|-----------|-----------------|-----------------------------------------------------------------------|-------------------------|-------|-------|-------|-----|-----------------------------------------------|--|--|

| PIC16H    | V753            |                                                                       |                         |       |       |       |     |                                               |  |  |

| Param     | Device          | Min.                                                                  | Тур†                    | Max.  | Max.  | Units |     | Conditions                                    |  |  |

| No.       | Characteristics |                                                                       |                         | 85°C  | 125°C |       | Vdd | Note                                          |  |  |

|           | Power-down Bas  | e Curre                                                               | ent (IPD) <sup>(2</sup> | 2, 3) |       |       |     |                                               |  |  |

| D025      |                 |                                                                       | 0.10                    | 0.41  | 3.51  | μA    | 3.0 | A/D Current <sup>(1)</sup> , no conversion in |  |  |

|           |                 | —                                                                     | 0.12                    | 0.55  | 4.41  | μA    | 5.0 | progress                                      |  |  |

| D025      |                 |                                                                       | 145                     | 171   | 175   | μA    | 3.0 |                                               |  |  |

|           |                 | _                                                                     | 185                     | 226   | 231   | μA    | 4.5 |                                               |  |  |

| D026      |                 | _                                                                     | 20                      | 37    | 37    | μA    | 2.0 | DAC Current <sup>(1)</sup>                    |  |  |

|           |                 |                                                                       | 30                      | 46    | 46    | μA    | 3.0 |                                               |  |  |

|           |                 | _                                                                     | 50                      | 76    | 76    | μA    | 5.0 |                                               |  |  |

| D026      |                 |                                                                       | 85                      | 155   | 155   | μA    | 2.0 |                                               |  |  |

|           |                 |                                                                       | 165                     | 213   | 213   | μA    | 3.0 |                                               |  |  |

|           |                 |                                                                       | 215                     | 284   | 284   | μA    | 4.5 | 7                                             |  |  |

| D027      |                 | _                                                                     | 115                     | 185   | 203   | μA    | 2.0 | FVR Current <sup>(1)</sup> , FVRBUFEN = 1,    |  |  |

|           |                 |                                                                       | 120                     | 193   | 219   | μA    | 3.0 | FVROUT buffer enabled                         |  |  |

|           |                 |                                                                       | 125                     | 196   | 224   | μA    | 5.0 | 7                                             |  |  |

| D027      |                 |                                                                       | 65                      | 126   | 145   | μA    | 2.0 |                                               |  |  |

|           |                 |                                                                       | 136                     | 171   | 182   | μA    | 3.0 | 7                                             |  |  |

|           |                 |                                                                       | 175                     | 226   | 231   | μA    | 4.5 | 7                                             |  |  |

| D028      |                 |                                                                       | 1                       | 2     | 4     | μA    | 2.0 | T1OSC Current,                                |  |  |

|           |                 |                                                                       | 2                       | 3     | 5     | μA    | 3.0 | TMR1CS <1:0> = 11                             |  |  |

|           |                 |                                                                       | 9                       | 20    | 21    | μA    | 5.0 | 7                                             |  |  |

| D028      |                 |                                                                       | 65                      | 126   | 140   | μA    | 2.0 |                                               |  |  |

|           |                 |                                                                       | 136                     | 172   | 180   | μA    | 3.0 |                                               |  |  |

|           |                 |                                                                       | 175                     | 228   | 235   | μA    | 4.5 |                                               |  |  |

| D029      |                 |                                                                       | 140                     | 258   | 265   | μA    | 2.0 | Op-Amp Current <sup>(1)</sup>                 |  |  |

|           |                 | _                                                                     | 155                     | 326   | 340   | μA    | 3.0 | 1                                             |  |  |

|           |                 |                                                                       | 165                     | 421   | 422   | μA    | 5.0 | 1                                             |  |  |

| D029      |                 |                                                                       | 140                     | 260   | 265   | μA    | 2.0 |                                               |  |  |

|           |                 |                                                                       | 155                     | 325   | 340   | μA    | 3.0 |                                               |  |  |

|           |                 |                                                                       | 165                     | 400   | 410   | μA    | 4.5 |                                               |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral △ current can be determined by subtracting the base IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

3: Shunt regulator is always ON and always draws operating current.

| DC CHARACTERISTICS |      |                                      | Standard Operating Conditions (unless otherwise stated) |       |          |            |                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------------|------|--------------------------------------|---------------------------------------------------------|-------|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Sym. | Characteristic                       | Characteristic Min. Typ† Max.                           |       | Units    | Conditions |                                                                                                                                                                                                                                                                                      |  |  |  |

|                    | VIL  | Input Low Voltage                    |                                                         |       |          |            |                                                                                                                                                                                                                                                                                      |  |  |  |

|                    |      | I/O PORT:                            |                                                         |       |          |            |                                                                                                                                                                                                                                                                                      |  |  |  |

| D030               |      | with TTL buffer                      | —                                                       | -     | 0.8      | V          | $4.5V \leq V\text{DD} \leq 5.5V$                                                                                                                                                                                                                                                     |  |  |  |

| D030A              |      |                                      | —                                                       | —     | 0.15 Vdd | V          | $2.0V \leq V\text{DD} \leq 4.5V$                                                                                                                                                                                                                                                     |  |  |  |

| D031               |      | with Schmitt Trigger buffer          | —                                                       | -     | 0.2 Vdd  | V          | $2.0V \leq V\text{DD} \leq 5.5V$                                                                                                                                                                                                                                                     |  |  |  |

|                    | VIH  | Input High Voltage                   |                                                         |       |          |            | •                                                                                                                                                                                                                                                                                    |  |  |  |

|                    |      | I/O PORT:                            |                                                         |       |          |            |                                                                                                                                                                                                                                                                                      |  |  |  |

| D040               |      | with TTL buffer                      | 2.0                                                     | _     | —        | V          | $4.5V \leq V\text{DD} \leq 5.5V$                                                                                                                                                                                                                                                     |  |  |  |

| D040A              |      |                                      | 0.25 Vdd + 0.8                                          | —     | _        | V          | $2.0V \le V\text{DD} \le 4.5V$                                                                                                                                                                                                                                                       |  |  |  |

| D041               |      | with Schmitt Trigger buffer          | 0.8 Vdd                                                 | _     | _        | V          | $2.0V \le V\text{DD} \le 5.5V$                                                                                                                                                                                                                                                       |  |  |  |

| D042               |      | MCLR                                 | 0.8 Vdd                                                 | _     | _        | V          |                                                                                                                                                                                                                                                                                      |  |  |  |

|                    | lı∟  | Input Leakage Current <sup>(1)</sup> |                                                         |       |          |            |                                                                                                                                                                                                                                                                                      |  |  |  |

| D060               |      | I/O ports                            | _                                                       | ± 0.1 | ± 1      | μA         | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance, 85°C                                                                                                                                                                                                                               |  |  |  |

| D061               |      | RA3/MCLR <sup>(2)</sup>              | _                                                       | ± 0.7 | ± 5      | μA         | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance, 85°C                                                                                                                                                                                                                           |  |  |  |

| D063               |      |                                      | _                                                       | ± 0.1 | ± 5      | μA         | EC Configuration                                                                                                                                                                                                                                                                     |  |  |  |

|                    | IPUR | Weak Pull-up Current <sup>(3)</sup>  |                                                         |       | •        |            |                                                                                                                                                                                                                                                                                      |  |  |  |

| D070*              |      |                                      | 50                                                      | 250   | 400      | μA         | VDD = 5.0V, VPIN = VSS                                                                                                                                                                                                                                                               |  |  |  |

|                    | Vol  | Output Low Voltage                   |                                                         |       |          |            |                                                                                                                                                                                                                                                                                      |  |  |  |

| D080               |      | I/O Ports (excluding RC4, RC5)       | _                                                       | _     | 0.6      | V          | $\begin{array}{l} \text{IOL} = 7 \text{ mA}, \text{ VDD} = 4.5 \text{V} \\ \text{-40}^\circ\text{C} \leq \text{TA} \leq +125^\circ\text{C} \\ \text{IOL} = 8.5 \text{ mA}, \text{ VDD} = 4.5 \text{V} \\ \text{-40}^\circ\text{C} \leq \text{TA} \leq +85^\circ\text{C} \end{array}$ |  |  |  |

|                    |      | I/O Ports RC4 and RC5                | _                                                       | _     | 0.6      | V          | IOL = 14  mA, VDD = 4.5V<br>-40°C $\leq$ TA $\leq$ +125°C<br>IOL = 17  mA, VDD = 4.5V<br>-40°C $\leq$ TA $\leq$ +85°C                                                                                                                                                                |  |  |  |