Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                    |

| Data Converters            | A/D 8x10b; D/A 1x9b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 16-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 16-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv753t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Complementary Output Generator (COG):

- Complementary Waveforms from selectable sources

- Two I/O (50 mA) for direct MOSFET drive

- Rising and/or Falling edge dead-band control

- Phase control, Blanking control

- Auto-shutdown

- Slope Compensation Circuit for use with SMPS power supplies

| TABLE 1: | PIC16F753/HV753 | FAMILY TYPES |

|----------|-----------------|--------------|

|          |                 |              |

| Device     | Data Sheet Index | Program Memory<br>Flash (words) | Self-Read/Write<br>Flash Memory | Data SRAM<br>(bytes) | I/OS <sup>(2)</sup> | 10-bit ADC (ch) | Comparators | Timers<br>(8/16-bit) | ССР | Complementary<br>Output Generator<br>(COG) | DAC   | Op Amp | Shunt Regulator | Debug <sup>(1)</sup> | XLP |

|------------|------------------|---------------------------------|---------------------------------|----------------------|---------------------|-----------------|-------------|----------------------|-----|--------------------------------------------|-------|--------|-----------------|----------------------|-----|

| PIC12F752  | (1)              | 1K                              | Y                               | 64                   | 6                   | 4               | 2           | 3/1                  | 1   | Y                                          | 5-bit | Ν      | Ν               | Н                    | Y   |

| PIC12HV752 | (1)              | 1K                              | Y                               | 64                   | 6                   | 4               | 2           | 3/1                  | 1   | Y                                          | 5-bit | Ν      | Y               | Н                    | Y   |

| PIC16F753  | (2)              | 2K                              | Y                               | 128                  | 12                  | 8               | 2           | 3/1                  | 1   | Y                                          | 9-bit | Y      | Ν               | I/H                  | Y   |

| PIC16HV753 | (2)              | 2K                              | Y                               | 128                  | 12                  | 8               | 2           | 3/1                  | 1   | Y                                          | 9-bit | Y      | Y               | I/H                  | Y   |

Note 1: I - Debugging, Integrated on Chip; H - Debugging, Requires Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS40001576 PIC12F752/HV752 Data Sheet, 8-Pin Flash-Based, 8-Bit CMOS Microcontrollers.

- 2: DS40001709 PIC16F753/HV753 Data Sheet, 14/16-Pin Flash-based, 8-Bit CMOS Microcontrollers.

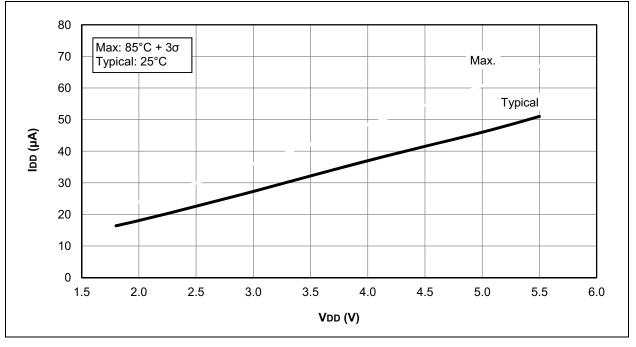

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

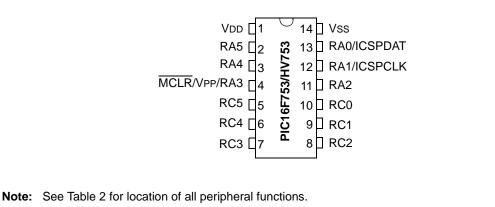

## FIGURE 1: 14-PIN PDIP, SOIC, TSSOP DIAGRAM

|                                                                                                                                    |              |                                    |                |                |                  | L                |              |

|------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------|----------------|----------------|------------------|------------------|--------------|

| U-0                                                                                                                                | U-0          | U-0                                | U-0            | U-0            | R/W-0/0          | R/S/HC-0/0       | R/S/HC-0/0   |

| _                                                                                                                                  | —            | —                                  | —              |                | WREN             | WR               | RD           |

| bit 7                                                                                                                              | ·            |                                    |                |                | •                | •                | bit 0        |

|                                                                                                                                    |              |                                    |                |                |                  |                  |              |

| Legend:                                                                                                                            |              |                                    |                |                |                  |                  |              |

| R = Readable                                                                                                                       | e bit        | W = Writable                       | bit            | U = Unimpler   | mented bit, read | l as '0'         |              |

| S = Bit can o                                                                                                                      | nly be set   | x = Bit is unkr                    | nown           | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set                                                                                                                   | t            | '0' = Bit is clea                  | ared           | HC = Bit is cl | eared by hardw   | are              |              |

|                                                                                                                                    |              |                                    |                |                |                  |                  |              |

| bit 7-3                                                                                                                            | Unimplemen   | ted: Read as '                     | 0'             |                |                  |                  |              |

| bit 2                                                                                                                              | WREN: Prog   | ram/Erase Ena                      | ble bit        |                |                  |                  |              |

|                                                                                                                                    | •            | rogram/erase c                     | •              |                |                  |                  |              |

|                                                                                                                                    |              | rogramming/er                      | asing of progi | am Flash       |                  |                  |              |

| bit 1                                                                                                                              | WR: Write Co |                                    |                |                |                  |                  |              |

|                                                                                                                                    |              | a program Flas                     |                |                |                  |                  |              |

|                                                                                                                                    | •            |                                    |                | •              | hardware once    | operation is co  | mplete.      |

|                                                                                                                                    |              | bit can only be<br>/erase operatio | •              | ,              |                  |                  |              |

| bit 0                                                                                                                              | •            | •                                  |                |                |                  |                  |              |

| bit 0 <b>RD:</b> Read Control bit<br>1 = Initiates a program Flash read. Read takes one cycle. RD is cleared in hardware. The RD b |              |                                    |                | he RD bit can  |                  |                  |              |

| only be set (not cleared) in software.                                                                                             |              |                                    |                |                |                  |                  |              |

|                                                                                                                                    |              | initiate a progi                   |                | d              |                  |                  |              |

|                                                                                                                                    |              |                                    |                |                |                  |                  |              |

#### REGISTER 3-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

## REGISTER 3-6: PMCON2: PROGRAM MEMORY CONTROL 2 REGISTER

| REGISTER 3-0.      | FINICC                          | INZ. FROGRAM        |                                                       |                  | ZREGISTER        | •        |       |

|--------------------|---------------------------------|---------------------|-------------------------------------------------------|------------------|------------------|----------|-------|

| W-0/0              | W-0/0                           | W-0/0               | W-0/0                                                 | W-0/0            | W-0/0            | W-0/0    | W-0/0 |

|                    |                                 | Progra              | m Memor                                               | y Control Regist | er 2             |          |       |

| bit 7              |                                 |                     |                                                       |                  |                  |          | bit 0 |

|                    |                                 |                     |                                                       |                  |                  |          |       |

| Legend:            |                                 |                     |                                                       |                  |                  |          |       |

| R = Readable bit   | = Readable bit W = Writable bit |                     |                                                       | U = Unimplen     | nented bit, read | l as '0' |       |

| S = Bit can only b | e set                           | x = Bit is unknow   | wn -n/n = Value at POR and BOR/Value at all other Res |                  | other Resets     |          |       |

| '1' = Bit is set   |                                 | '0' = Bit is cleare | d                                                     |                  |                  |          |       |

#### bit 7-0 Flash Memory Unlock Pattern bits:

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the PMCON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes.

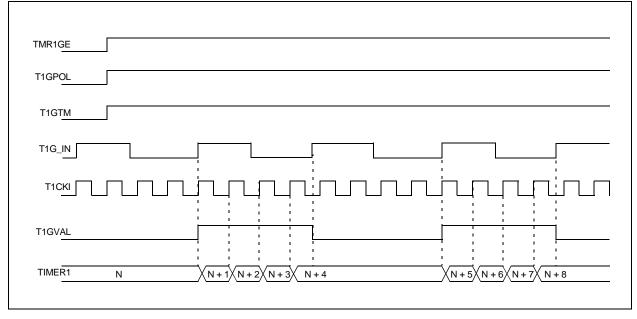

# FIGURE 7-4: TIMER1 GATE TOGGLE MODE

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                     |                   |      |                |                  | DAM O/C          | D 444 0/2   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|----------------|------------------|------------------|-------------|

| R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0/0                                                                                                                                             | U-0               | U-0  | U-0            | U-0              | R/W-0/0          | R/W-0/0     |

| GxRDBTS                                                                                                                                                                                                                                                                                                                                                                                                                                                          | GxFDBTS                                                                                                                                             | —                 | —    | —              | —                | GxCS             | i<1:0>      |

| bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                     |                   |      |                |                  |                  | bit (       |

| Legend:                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                     |                   |      |                |                  |                  |             |

| R = Readable                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit                                                                                                                                                 | W = Writable      | bit  | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is unch                                                                                                                                                                                                                                                                                                                                                                                                                                                  | anged                                                                                                                                               | x = Bit is unkr   | nown | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                     | '0' = Bit is clea | ared | q = Value dep  | pends on conditi | on               |             |

| 1 = Delay chain and COGxDBR are used for dead-band timing generation         0 = COGx_clk and COGxDBR are used for dead-band timing generation         bit 6 <b>GxFDBTS:</b> COGx Falling Event Dead-band Timing Source Select bit         1 = Delay chain and COGxDF are used for dead-band timing generation         0 = COGx_clk and COGxDF are used for dead-band timing generation         0 = COGx_clk and COGxDF are used for dead-band timing generation |                                                                                                                                                     |                   |      |                |                  |                  |             |

| bit 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Unimplemen                                                                                                                                          | ted: Read as '    | כ'   |                |                  |                  |             |

| bit 1-0                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-0 <b>GxCS&lt;1:0&gt;:</b> COGx Clock Source Select bits<br>11 = Reserved<br>10 = HFINTOSC (stays active during Sleep)<br>01 = Fosc/4<br>00 = Fosc |                   |      |                |                  |                  |             |

## REGISTER 11-2: COGxCON1: COG CONTROL REGISTER 1

## 12.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (See TRIS register)

- Configure pin as analog

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Select result format

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the  $GO/\overline{DONE}$  bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: See Section 12.4 "A/D Acquisition Requirements".

## EXAMPLE 12-1: A/D CONVERSION

```

;This code block configures the ADC

; for polling, Vdd reference, Frc clock

;and RA0 input.

;Conversion start & polling for completion

; are included.

BANKSEL TRISA

;

BSF TRISA,0

;Set RA0 to input

BANKSEL ADCON1

;

MOVLW B'01110000' ;ADC Frc clock,

IORWF ADCON1 ; and RAO as analog

BANKSEL ADCON0

;

MOVLW B'10000001' ;Right justify,

MOVWF ADCON0 ;Vdd Vref, AN0, On

CALL

SampleTime ;Acquisiton delay

ADCON0,GO ;Start conversion

BSF

TEST AGAIN

BTFSC ADCON0,GO ; Is conversion done?

TEST AGAIN ;No, test again

GOTO

BANKSEL ADRESH

;

MOVF ADRESH,W ;Read upper 2 bits

RESULTHI ;Store in GPR space

MOVWE

BANKSEL ADRESL ;

MOVF ADRESL,W ;Read lower 8 bits

MOVWF RESULTLO ;Store in GPR space

```

## **REGISTER 14-2:** DACxREFH: DAC REFERENCE HIGH REGISTER (DACxFM = 0)

|                 | -                                       | -                | -       |                                                      |                  | - /      |         |

|-----------------|-----------------------------------------|------------------|---------|------------------------------------------------------|------------------|----------|---------|

| R/W-0/0         | R/W-0/0                                 | R/W-0/0          | R/W-0/0 | R/W-0/0                                              | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|                 |                                         |                  | DACR    | <8:1>                                                |                  |          |         |

| bit 7           |                                         |                  |         |                                                      |                  |          | bit 0   |

|                 |                                         |                  |         |                                                      |                  |          |         |

| Legend:         |                                         |                  |         |                                                      |                  |          |         |

| R = Readable    | bit                                     | W = Writable bit | t       | U = Unimpler                                         | mented bit, read | 1 as '0' |         |

| u = Bit is unch | u = Bit is unchanged x = Bit is unknown |                  | wn      | -n/n = Value at POR and BOR/Value at all other Reset |                  |          |         |

bit 7-0 **DACR<8:1>**: DAC Reference Selection bits DACxOUT = (DACR<8:0> x (Vdac\_ref)/512)

'0' = Bit is cleared

# REGISTER 14-3: DACxREFL: DAC REFERENCE LOW REGISTER (DACxFM = 0)

| R/W-0/0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| DACR0   | —   | —   | —   | —   | —   | —   | —     |

| bit 7   |     |     |     |     |     |     | bit 0 |

# Legend:

'1' = Bit is set

| Logona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 DACR0: DAC Reference Selection bits

DACxOUT = (DACR<8:0> x (Vdac\_ref)/512)

bit 6-0 Unimplemented: Read as '0'

# 16.0 OPERATIONAL AMPLIFIER (OPA) MODULE

The Operational Amplifier (OPA) is a standard threeterminal device requiring external feedback to operate. The OPA module has the following features:

- External Connections to I/O Ports

- Selectable Unity Gain Bandwidth Product Option

- Low-Leakage Inputs

- Factory-Calibrated Input Offset Voltage

# 16.1 OPAxCON0 Register

The OPAxCON0 register, shown in Register 16-1, controls the OPA module.

The OPA module is enabled by setting the OPAxEN bit of the OPAxCON register. When enabled, the OPA forces the output driver of the OPAxOUT pin into tristate to prevent contention between the driver and the OPA output.

The OPAxUGM bit of the OPAxCON register enables the Unity Gain Bandwidth mode (voltage follower) of the amplifier. In Unity Gain mode, the OPAxNCH<1:0> inputs are disabled. The default mode is normal threeterminal operation.

Note: When the OPA module is enabled, the OPAxOUT pin is driven by the op amp output, not by the PORT digital driver. Refer to Section 22.0 "Electrical Specifications" for the op amp output drive capability.

## 16.2 Effects of a Reset

A device Reset forces all registers to their Reset state. This disables the OPA module.

# 16.3 OPA Module Performance

Common AC and DC performance specifications for the OPA module:

- Common Mode Voltage Range

- Leakage Current

- Input Offset Voltage

- Open Loop Gain

- Gain Bandwidth Product

Common mode voltage range is the specified voltage range for the OPAx+ and OPAx- inputs, for which the OPA module will perform within its specifications. The OPA module is designed to operate with input voltages between Vss and VDD. Behavior for Common mode voltages greater than VDD or below Vss is not guaranteed.

Leakage current is a measure of the small source or sink currents on the OPAx+ and OPAx- inputs. To minimize the effect of leakage currents, the effective impedances connected to the OPAx+ and OPAx- inputs should be kept as small as possible and equal. Input offset voltage is a measure of the voltage difference between the OPAx+ and OPAx- inputs in a closed loop circuit with the OPA in its linear region. The offset voltage will appear as a DC offset in the output equal to the input offset voltage, multiplied by the gain of the circuit.

The input offset voltage is also affected by the Common mode voltage. The OPA is factory-calibrated to minimize the input offset voltage of the module. Open loop gain is the ratio of the output voltage to the differential input voltage (OPAx+) - (OPAx-). The gain is greatest at DC and falls off with frequency.

Gain Bandwidth Product or GBWP is the frequency at which the open loop gain falls off to 0 dB. The lower GBWP is optimized for systems requiring low-frequency response and low-power consumption.

# 18.2 Instruction Descriptions

| ADDLW            | Add literal and W                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDLW k                                                                                                      |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | $(W) + k \to (W)$                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                               |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                           |

| Operands:        | $0 \leq k \leq 255$                                                                                                |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                    |

| Status Affected: | Z                                                                                                                  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W<br>register. |

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                         |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                        |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' is '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>2-cycle instruction. |

Bit Test f, Skip if Clear

BTFSC

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

AND W with f

ANDWF

| SUBWF            | Subtract W from f                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                             |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                                                    |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

|                  | C = 0 $W > f$                                                                                                                                                                               |

| <b>C</b> = 0     | W > f                     |

|------------------|---------------------------|

| <b>C</b> = 1     | $W \leq f$                |

| DC = 0           | W<3:0>>f<3:0>             |

| DC = 0<br>DC = 1 | $W < 3:0 > \le f < 3:0 >$ |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] XORWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                     |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |

| Status Affected: | Z                                                                                                                                                                               |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                        |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORLW            | Exclusive OR literal with W                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |

### **19.5 Context Saving During Interrupts**

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Temporary holding registers W\_TEMP and STATUS\_TEMP should be placed in the last 16 bytes of GPR (see Figure 2-2). These 16 locations are common to all banks and do not require banking. This makes context save and restore operations simpler. The code shown in Example 19-1 can be used to:

- Store the W register

- Store the STATUS register

- · Execute the ISR code

- Restore the Status (and Bank Select Bit register)

- · Restore the W register

| Note: | The PIC16F753/HV753 does not require    |  |  |  |

|-------|-----------------------------------------|--|--|--|

|       | saving the PCLATH. However, if          |  |  |  |

|       | computed GOTOs are used in both the ISR |  |  |  |

|       | and the main code, the PCLATH must be   |  |  |  |

|       | saved and restored in the ISR.          |  |  |  |

#### EXAMPLE 19-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits |

|----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| MOVWF          | STATUS_TEMP        | ;Save status to bank zero STATUS_TEMP register                                                                            |

| :(ISR)         |                    | ;Insert user code here                                                                                                    |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                                                       |

| MOVWF          | STATUS             | ;Move W into STATUS register                                                                                              |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                                                                              |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                                                                                       |

#### 19.6 Watchdog Timer (WDT)

The Watchdog Timer is a free running timer, using LFINTOSC oscillator as its clock source. The WDT is enabled by setting the WDTE bit of the Configuration Word (default setting). When WDTE is set, the LFINTOSC will always be enabled to provide a clock source to the WDT module.

During normal operation, a WDT time-out generates a device Reset. If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation.

The WDT can be permanently disabled by programming the Configuration bit, WDTE, as clear (Section 19.1 "Configuration Bits").

#### 19.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

# 22.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings<sup>(†)</sup>

| nbient temperature under bias40°                                                                                                                                                                                     | to +125°C  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| prage temperature                                                                                                                                                                                                    |            |

| Itage on pins with respect to Vss                                                                                                                                                                                    |            |

| on VDD pin                                                                                                                                                                                                           |            |

| -0.3 <sup>v</sup>                                                                                                                                                                                                    | V to +6.5V |

| PIC16F753                                                                                                                                                                                                            | V to +6.5V |

| on MCLR0.3V                                                                                                                                                                                                          | to +13.5V  |

| on all other pins0.3V to (Vi                                                                                                                                                                                         | dd + 0.3V) |

| aximum current                                                                                                                                                                                                       |            |

| on Vss pin <sup>(1)</sup>                                                                                                                                                                                            |            |

| $-40^{\circ}C \le TA \le +85^{\circ}C$                                                                                                                                                                               | 95 mA      |

| $-40^{\circ}C \leq TA \leq +125^{\circ}C$                                                                                                                                                                            | 95 mA      |

| on Vdd pin <sup>(1)</sup>                                                                                                                                                                                            |            |

| $-40^{\circ}C \leq TA \leq +85^{\circ}C$                                                                                                                                                                             | 95 mA      |

| $-40^{\circ}C \leq TA \leq +125^{\circ}C \dots$                                                                                                                                                                      | 95 mA      |

| on RA1, RA4, RA5                                                                                                                                                                                                     | 25 mA      |

| on RC4, RC5                                                                                                                                                                                                          | 50 mA      |

| amp current, Ικ (VPIN < 0 or VPIN >VDD)                                                                                                                                                                              | ± 20 mA    |

| <b>1:</b> Maximum current rating requires even load distribution across I/O pins. Maximum current ratin limited by the device package power dissipation characteristics. See Table 22-6 to calculate de limitations. |            |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

| PIC16F7      | 753                                    | Standard Operating Conditions (unless otherwise stated) |      |              |               |       |            |                                     |  |

|--------------|----------------------------------------|---------------------------------------------------------|------|--------------|---------------|-------|------------|-------------------------------------|--|

| PIC16HV753   |                                        |                                                         |      |              |               |       |            |                                     |  |

| Param<br>No. |                                        | Min.                                                    | Тур† | Max.<br>85°C | Max.<br>125°C | Units | Conditions |                                     |  |

|              | Device Characteristics                 |                                                         |      |              |               |       | Vdd        | Note                                |  |

|              | Supply Current (IDD) <sup>(1, 2)</sup> |                                                         |      |              |               |       |            |                                     |  |

| D014         |                                        |                                                         | 318  | 382          | 382           | μΑ    | 2.0        | Fosc = 4 MHz                        |  |

|              |                                        |                                                         | 450  | 502          | 502           | μA    | 3.0        | HFINTOSC mode                       |  |

|              |                                        |                                                         | 825  | 100          | 100           | μΑ    | 5.0        |                                     |  |

| D014         |                                        |                                                         | 330  | 485          | 485           | μΑ    | 2.0        | Fosc = 4 MHz                        |  |

|              |                                        |                                                         | 526  | 658          | 658           | μΑ    | 3.0        | HFINTOSC mode                       |  |

|              |                                        |                                                         | 775  | 980          | 980           | μΑ    | 4.5        |                                     |  |

| D015         |                                        |                                                         | 505  | 595          | 595           | μΑ    | 2.0        | Fosc = 8 MHz                        |  |

|              |                                        |                                                         | 740  | 1200         | 1200          | μΑ    | 3.0        | HFINTOSC mode                       |  |

|              |                                        |                                                         | 1.5  | 1.8          | 1.8           | mA    | 5.0        |                                     |  |

| D015         |                                        |                                                         | 500  | 690          | 690           | μA    | 2.0        | Fosc = 8 MHz                        |  |

|              |                                        |                                                         | 800  | 1100         | 1100          | μΑ    | 3.0        | HFINTOSC mode                       |  |

|              |                                        |                                                         | 1.23 | 1.7          | 1.7           | mA    | 4.5        |                                     |  |

| D016         |                                        |                                                         | 2.6  | 3.08         | 3.08          | mA    | 4.5        | Fosc = 20 MHz                       |  |

|              |                                        |                                                         | 2.97 | 3.53         | 3.53          | mA    | 5.0        | EC Oscillator mode                  |  |

| D016         |                                        | _                                                       | 2.6  | 3.3          | 3.3           | mA    | 4.5        | Fosc = 20 MHz<br>EC Oscillator mode |  |

# TABLE 22-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup> (CONTINUED)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss; MCLR = VDD; WDT disabled.

**2:** The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

## FIGURE 22-5: CLKOUT AND I/O TIMING

| <b>TABLE 22-9:</b> | <b>CLKOUT AND I/O TIMING PARAMETERS</b> |

|--------------------|-----------------------------------------|

|--------------------|-----------------------------------------|

| Standar      | Standard Operating Conditions (unless otherwise stated) |                                                            |               |          |          |           |                          |  |

|--------------|---------------------------------------------------------|------------------------------------------------------------|---------------|----------|----------|-----------|--------------------------|--|

| Param<br>No. | Sym.                                                    | Characteristic                                             | Min.          | Тур<br>† | Max.     | Unit<br>s | Conditions               |  |

| OS13         | ΤcκL2ιoV                                                | CLKOUT↓ to Port out valid <sup>(1)</sup>                   | —             | —        | 20       | ns        |                          |  |

| OS14         | ТюV2скН                                                 | Port input valid before CLKOUT <sup>(1)</sup>              | Tosc + 200 ns | —        | _        | ns        |                          |  |

| OS15         | TosH2IOV                                                | Fosc↑ (Q1 cycle) to Port out valid                         | —             | 50       | 70*      | ns        | VDD = 5.0V               |  |

| OS16         | TosH2ıol                                                | Fosc↑ (Q2 cycle) to Port input invalid (I/O in setup time) | 50            |          |          | ns        | VDD = 5.0V               |  |

| OS17         | TIOV20SH                                                | Port input valid to Fosc↑ (Q2 cycle) (I/O in setup time)   | 20            | _        | _        | ns        |                          |  |

| OS18         | TIOR                                                    | Port output rise time                                      | —             | 40<br>15 | 72<br>32 | ns<br>ns  | VDD = 2.0V<br>VDD = 5.0V |  |

|              |                                                         |                                                            |               |          |          | 115       | VDD = 5.0V               |  |

| OS19         | TIOF                                                    | Port output fall time                                      | —             | 28<br>15 | 55<br>30 | ns<br>ns  | VDD = 2.0V<br>VDD = 5.0V |  |

| OS20*        | TINP                                                    | INT pin input high or low time                             | 25            | _        | _        | ns        |                          |  |

| OS21*        | TIOC                                                    | Interrupt-on-change new input level time                   | Тсү           |          | _        | ns        |                          |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

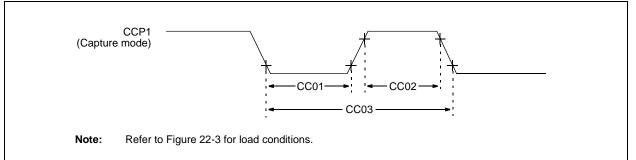

# FIGURE 22-9: PIC16F753/HV753 CAPTURE/COMPARE/PWM TIMINGS (CCP)

## TABLE 22-12: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

| Standar      | Standard Operating Conditions (unless otherwise stated) |                      |                |                       |      |      |       |                                       |

|--------------|---------------------------------------------------------|----------------------|----------------|-----------------------|------|------|-------|---------------------------------------|

| Param<br>No. | Sym.                                                    | Character            | Characteristic |                       | Тур† | Max. | Units | Conditions                            |

| CC01*        | TccL                                                    | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | —    | ns    |                                       |

|              |                                                         |                      | With Prescaler | 20                    | _    |      | ns    |                                       |

| CC02*        | TccH                                                    | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | _    |      | ns    |                                       |

|              |                                                         |                      | With Prescaler | 20                    |      |      | ns    |                                       |

| CC03*        | TccP                                                    | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —    |      | ns    | N = prescale<br>value (1, 4 or<br>16) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 22-13: COMPARATOR SPECIFICATIONS<sup>(1)</sup>

| Standard Operating Conditions (unless otherwise stated)<br>VDD = $5.0V$ , $-40^{\circ}C \le TA \le +125^{\circ}C$ |                    |                                          |      |              |              |          |                      |

|-------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------|------|--------------|--------------|----------|----------------------|

| Param<br>No.                                                                                                      | Sym.               | Characteristics                          | Min. | Тур†         | Max.         | Units    | Comments             |

| CM01                                                                                                              | VIOFF              | Input Offset Voltage <sup>(3)</sup>      |      | ± 10<br>± 10 | ± 20<br>± 20 | mV<br>mV | CxSP = 1<br>CxSP = 0 |

| CM02                                                                                                              | VICM               | Input Common Mode Voltage <sup>(2)</sup> | 0    | _            | Vdd - 1.5    | V        |                      |

| CM03                                                                                                              | CMRR               | Common Mode Rejection Ratio              | _    | 55           | _            | dB       |                      |

| CM04A*                                                                                                            | Trt <sup>(2)</sup> | Response Time                            | _    | 55           | 70           | ns       | CxSP = 1             |

|                                                                                                                   |                    |                                          | _    | 65           | 100          | ns       | CxSP = 0             |

| CM05*                                                                                                             | TMC20V             | Comparator Mode Change to Output Valid   | —    | —            | 10           | μS       |                      |

| CM06                                                                                                              | CHYSTER            | Comparator Hysteresis                    | _    | 20           | 50           | mV       |                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: See Section 23.0 "DC and AC Characteristics Graphs and Charts" and Section 22.0 "Electrical Specifications" for operating characterization.

Response time is measured with one comparator input at (VDD - 1.5V)/2 - 100 mV to (VDD - 1.5V)/ 2 + 20 mV. The other input is at (VDD -1.5V)/2.

3: Input offset voltage is measured with one comparator input at (VDD - 1.5V)/2.

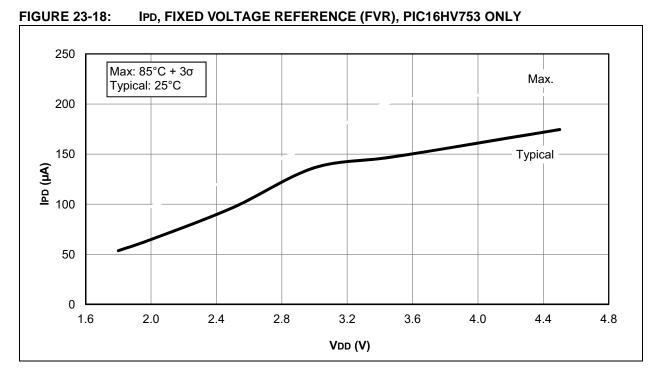

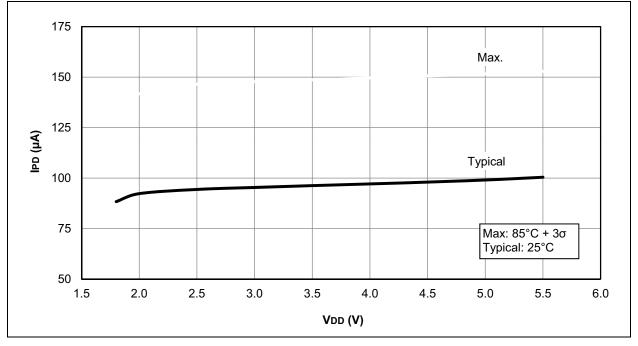

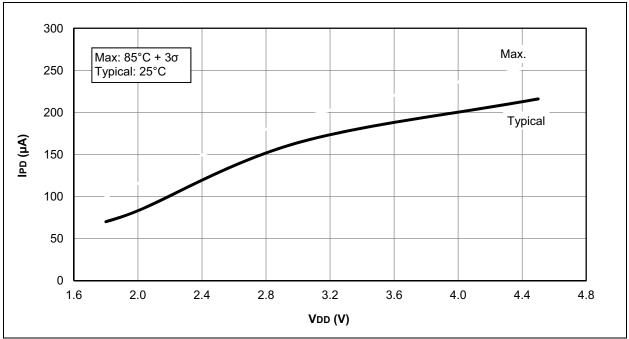

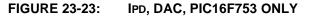

FIGURE 23-19: IPD, FIXED VOLTAGE REFERENCE (FVR), PIC16F753 ONLY

# 24.0 PACKAGING INFORMATION

# 24.1 Package Marking Information

| Legend: | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|---------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:   | carried over                             | nt the full Microchip part number cannot be marked on one line, it will be<br>er to the next line, thus limiting the number of available characters for<br>pecific information.                                                                                                                                                                                                           |

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> - <u>X</u> <u>/XX XXX</u><br>☐ ☐ ☐<br>Tape and Reel Temperature Package Pattern<br>Option Range                                                                                                                            | Examples:<br>a) PIC16F753-I/ML301<br>Tape and Reel,<br>Industrial temperature,<br>QFN 4x43 package,                                                                                                                                                                          |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F753<br>PIC16HV753                                                                                                                                                                                                                       | QTP pattern #301<br>b) PIC16F753-E/P<br>Extended temperature<br>PDIP package<br>c) PIC16F753-E/SL                                                                                                                                                                            |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                                                                                                                                                 | <ul> <li>Extended temperature,<br/>SOIC package</li> <li>d) PIC16HV753-E/ST</li> </ul>                                                                                                                                                                                       |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                                                                                                                                     | Extended temperature,<br>TSSOP 4.4 mm package                                                                                                                                                                                                                                |

| Package:                 | P = 14-lead Plastic Dual In-line (PDIP)<br>SL = 14-lead Plastic Small Outline (3.90 mm) (SOIC)<br>ST = 14-lead Plastic Thin Shrink Small Outline<br>(4.4 mm) (TSSOP)<br>ML = 16-lead Plastic Quad Flat, No Lead Package<br>(4x4x0.9 mm) (QFN) | Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option. |

| Pattern:                 | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                                                                                                                                                     |                                                                                                                                                                                                                                                                              |

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

Fax: 852-2401-3431

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

## ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

06/23/16