Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·><Fl

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                    |

| Data Converters            | A/D 8x10b; D/A 1x9b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv753t-i-sl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 17100 |            |               |                                                                                                      |                   |                     |                     |                   |              |          |                     |                                  |

|-------|------------|---------------|------------------------------------------------------------------------------------------------------|-------------------|---------------------|---------------------|-------------------|--------------|----------|---------------------|----------------------------------|

| Addr  | Name       | Bit 7         | Bit 6                                                                                                | Bit 5             | Bit 4               | Bit 3               | Bit 2             | Bit 1        | Bit 0    | Value on<br>POR/BOR | Values on<br>all other<br>Resets |

| Banl  | Bank 1     |               |                                                                                                      |                   |                     |                     |                   |              |          |                     |                                  |

| 80h   | INDF       |               |                                                                                                      |                   | IND                 | F<7:0>              |                   |              |          | xxxx xxxx           | uuuu uuuu                        |

| 81h   | OPTION_REG | RAPU          | INTEDG                                                                                               | TOCS              | TOSE                | PSA                 |                   | PS<2:0>      |          | 1111 1111           | 1111 1111                        |

| 82h   | PCL        |               |                                                                                                      |                   | PC                  | L<7:0>              | •                 |              |          | 0000 0000           | 0000 0000                        |

| 83h   | STATUS     | IRP           | RP1                                                                                                  | RP0               | TO                  | PD                  | Z                 | DC           | С        | 0001 1xxx           | 000q quuu                        |

| 84h   | FSR        |               |                                                                                                      |                   |                     | FSR                 |                   |              | I.       | xxxx xxxx           | uuuu uuuu                        |

| 85h   | TRISA      |               | _                                                                                                    | TRISA5            | TRISA4              | TRISA3              | TRISA2            | TRISA1       | TRISA0   | 11 1111             | 11 1111                          |

| 86h   | —          |               |                                                                                                      |                   | Unimp               | lemented            |                   |              |          | _                   | —                                |

| 87h   | TRISC      | _             | _                                                                                                    | TRISC5            | TRISC4              | TRISC3              | TRISC2            | TRISC1       | TRISC0   | 11 1111             | 11 1111                          |

| 88h   | IOCAP      |               | _                                                                                                    | IOCAP5            | IOCAP4              | IOCAP3              | IOCAP2            | IOCAP1       | IOCAP0   | 00 0000             | 00 0000                          |

| 89h   | IOCCP      | -             | _                                                                                                    | IOCCP5            | IOCCP4              | IOCCP3              | IOCCP2            | IOCCP1       | IOCCP0   | 00 0000             | 00 0000                          |

| 8Ah   | PCLATH     |               | _                                                                                                    |                   |                     | P                   | CLATH<4:0>        | -            | _        | 0 0000              | 0 0000                           |

| 8Bh   | INTCON     | GIE           | PEIE                                                                                                 | TOIE              | INTE                | IOCIE               | TOIF              | INTF         | IOCIF    | 0000 0000           | 0000 0000                        |

| 8Ch   | PIE1       | TMR1GIE       | ADIE                                                                                                 | -                 | _                   | HLTMR2IE            | HLTMR1IE          | TMR2IE       | TMR1IE   | 00 0000             | 00 0000                          |

| 8Dh   | PIE2       | _             | _                                                                                                    | C2IE              | C1IE                | —                   | COG1IE            | _            | CCP1IE   | 00 - 0 - 0          | 00 - 0 - 0                       |

| 8Eh   | _          |               |                                                                                                      |                   | Unimp               | lemented            |                   |              |          | —                   | —                                |

| 8Fh   | OSCCON     | _             | _                                                                                                    | IRCI              | F<1:0>              | _                   | HTS               | LTS          | _        | 01 -00-             | uu -uu-                          |

| 90h   | FVR1CON0   | FVREN         | FVRRDY                                                                                               | FVROE             | FVRBUFSS1           | FVRBUFSS0           | —                 | -            | FVRBUFEN | 0000 00             | 0000 00                          |

| 91h   | DAC1CON0   | DACEN         | DACFM                                                                                                | DACOE             | —                   | DACPSS1             | DACPSS0           | _            | —        | 000- 00             | 000- 00                          |

| 92h   | DAC1REFL   |               | Least Signif                                                                                         | ficant bit of the | e left shifted resu | It or eight bits of | f the right shift | ed DAC setti | ng       | 0000 0000           | 0000 0000                        |

| 93h   | DAC1REFH   |               | Most Significant eight bits of the left shifted DAC setting or first bit of the right shifted result |                   |                     |                     |                   |              |          | 0000 0000           | 0000 0000                        |

| 94h   | _          |               |                                                                                                      |                   | Unimp               | lemented            |                   |              |          | —                   | —                                |

| 95h   | _          |               |                                                                                                      |                   | Unimp               | lemented            |                   |              |          | —                   | —                                |

| 96h   | OPA1CON    | OPA1EN        | _                                                                                                    |                   | OPA1UGM             | OPA1NC              | H<1:0>            | OPA1F        | PCH<1:0> | 00 0000             | 00 0000                          |

| 97h   | _          |               |                                                                                                      |                   | Unimp               | lemented            |                   |              |          | —                   | —                                |

| 98h   | _          |               |                                                                                                      |                   | Unimp               | lemented            |                   |              |          | —                   | —                                |

| 99h   | _          | Unimplemented |                                                                                                      |                   |                     |                     |                   |              | —        | —                   |                                  |

| 9Ah   | _          |               |                                                                                                      |                   | Unimp               | lemented            |                   |              |          | —                   | —                                |

| 9Bh   | CM2CON0    | C2ON          | C2OUT                                                                                                | C2OE              | C2POL               | C2ZLF               | C2SP              | C2HYS        | C2SYNC   | 0000 0100           | 0000 0100                        |

| 9Ch   | CM2CON1    | C2INTP        | C2INTN                                                                                               |                   | C2PCH<2:0>          |                     |                   | C2NCH<2:0    | >        | 0000 0000           | 0000 0000                        |

| 9Dh   | CM1CON0    | C10N          | C10UT                                                                                                | C10E              | C1POL               | C1ZLF               | C1SP              | C1HYS        | C1SYNC   | 0000 0100           | 0000 0100                        |

| 9Eh   | CM1CON1    | C1INTP        | C1INTN                                                                                               |                   | C1PCH<2:0>          |                     |                   | C1NCH<2:0    | >        | 0000 0000           | 0000 0000                        |

| 9Fh   | CMOUT      | _             | —                                                                                                    |                   | —                   | —                   | —                 | MCOUT2       | MCOUT1   | 00                  | 00                               |

|       |            |               |                                                                                                      |                   |                     |                     |                   |              |          |                     |                                  |

#### TABLE 2-2: PIC16F753/HV753 SPECIAL REGISTERS SUMMARY BANK 1

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition shaded = unimplemented.

.

| IADI  | ABLE 2-3: PICTOF / 33/HV / 33 SPECIAL REGISTERS SUMMART BANK 2 |              |                                                                                                              |                 |                  |                |               |         |         |                     |                                 |

|-------|----------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------|-----------------|------------------|----------------|---------------|---------|---------|---------------------|---------------------------------|

| Addr  | Name                                                           | Bit 7        | Bit 6                                                                                                        | Bit 5           | Bit 4            | Bit 3          | Bit 2         | Bit 1   | Bit 0   | Value on<br>POR/BOR | Value on<br>all other<br>Resets |

| Ban   | Bank 2                                                         |              |                                                                                                              |                 |                  |                |               |         |         |                     |                                 |

| 100h  | INDF                                                           |              |                                                                                                              |                 | INDF             | <7:0>          |               |         |         | XXXX XXXX           | XXXX XXXX                       |

| 101h  | TMR0                                                           |              |                                                                                                              |                 | TMR              | )<7:0>         |               |         |         | XXXX XXXX           | uuuu uuuu                       |

| 102h  | PCL                                                            |              |                                                                                                              |                 | PCL              | <7:0>          |               |         |         | 0000 0000           | 0000 0000                       |

| 103h  | STATUS                                                         | IRP          | RP1                                                                                                          | RP0             | TO               | PD             | Z             | DC      | С       | 0001 1xxx           | 000q quuu                       |

| 104h  | FSR                                                            |              |                                                                                                              | •               | FSR              | <7:0>          | •             | •       |         | xxxx xxxx           | uuuu uuuu                       |

| 105h  | LATA                                                           | —            | _                                                                                                            | LATA5           | LATA4            | _              | LATA2         | LATA1   | LATA0   | xx -xxx             | uu -uuu                         |

| 106h  | —                                                              |              |                                                                                                              |                 | Unimple          | emented        |               |         |         | _                   | _                               |

| 107h  | LATC                                                           | _            | _                                                                                                            | LATC5           | LATC4            | LATC3          | LATC2         | LATC1   | LATC0   | xx xxxx             | uu uuuu                         |

| 108h  | IOCAN                                                          | _            | _                                                                                                            | IOCAN5          | IOCAN4           | IOCAN3         | IOCAN2        | IOCAN1  | IOCAN0  | 00 0000             | 00 0000                         |

| 109h  | IOCCN                                                          | —            | _                                                                                                            | IOCCN5          | IOCCN4           | IOCCN3         | IOCCN2        | IOCCN1  | IOCCN0  | 00 0000             | 00 0000                         |

| 10Ah  | PCLATH                                                         | _            |                                                                                                              | —               |                  | F              | PCLATH<4:0:   | >       |         | 0 0000              | 0 0000                          |

| 10Bh  | INTCON                                                         | GIE          | PEIE                                                                                                         | TOIE            | INTE             | IOCIE          | T0IF          | INTF    | IOCIF   | 0000 0000           | 0000 0000                       |

| 10Ch  | WPUA                                                           | —            | _                                                                                                            | WPUA5           | WPUA4            | WPUA3          | WPUA2         | WPUA1   | WPUA0   | 11 1111             | 11 1111                         |

| 10Dh  | WPUC                                                           | _            |                                                                                                              | WPUC5           | WPUC4            | WPUC3          | WPUC2         | WPUC1   | WPUC0   | 11 1111             | 11 1111                         |

| 10Eh  | SLRCONC                                                        | _            |                                                                                                              | SLRC5           | SLRC4            | -              | —             | _       | _       | 00                  | 00                              |

| 10Fh  | PCON                                                           | —            | -                                                                                                            | _               | _                | —              | —             | POR     | BOR     | qq                  | uu                              |

| 110h  | TMR2                                                           |              |                                                                                                              |                 | TMR2             | 2<7:0>         |               |         |         | 0000 0000           | 0000 0000                       |

| 111h  | PR2                                                            |              |                                                                                                              |                 | PR2-             | <7:0>          |               |         |         | 1111 1111           | 1111 1111                       |

| 112h  | T2CON                                                          | —            |                                                                                                              | T2OUTF          | PS<3:0>          |                | TMR2ON        | T2CKF   | PS<1:0> | -000 0000           | -000 0000                       |

| 113h  | HLTMR1                                                         |              | F                                                                                                            | Iolding Registe | er for the 8-bit | Hardware Lim   | nit Timer1 Co | unt     |         | 0000 0000           | 0000 0000                       |

| 114h  | HLTPR1                                                         |              |                                                                                                              | HL              | TMR1 Module      | e Period Regis | ster          |         |         | 1111 1111           | 1111 1111                       |

| 115h  | HLT1CON0                                                       | _            |                                                                                                              | H1OUT           | PS<3:0>          |                | H1ON          | H1CKF   | PS<1:0> | -000 0000           | -000 0000                       |

| 116h  | HLT1CON1                                                       | H1FES        | H1RES                                                                                                        | _               |                  | H1ERS<2:0>     |               | H1FEREN | H1REREN | 11-0 0000           | 11-0 0000                       |

| 117h  | HLTMR2                                                         |              | F                                                                                                            | Iolding Registe | er for the 8-bit | Hardware Lim   | nit Timer2 Co | unt     |         | 0000 0000           | 0000 0000                       |

| 118h  | HLTPR2                                                         |              |                                                                                                              | HL              | TMR2 Module      | e Period Regis | ster          |         |         | 1111 1111           | 1111 1111                       |

| 119h  | HLT2CON0                                                       | _            |                                                                                                              | H2OUTF          | PS<3:0>          |                | H2ON          | H2CKF   | PS<1:0> | -000 0000           | -000 0000                       |

| 11Ah  | HLT2CON1                                                       | H2FES        | H2RES                                                                                                        | _               |                  | H2ERS<2:0>     |               | H2FEREN | H2REREN | 11-0 0000           | 11-0 0000                       |

| 11Bh  | _                                                              |              |                                                                                                              |                 | Unimple          | emented        |               |         |         | _                   | —                               |

| 11Ch  | _                                                              |              |                                                                                                              |                 | Unimple          | emented        |               |         |         | _                   | _                               |

| 11Dh  | —                                                              |              |                                                                                                              |                 | Unimple          | emented        |               |         |         | _                   | _                               |

| 11Eh  | SLPCCON0                                                       | SC1EN        | _                                                                                                            | —               | SC1POL           | SC1TS          | S<1:0>        | —       | SC1INS  | 0-00 00-0           | 0-00 00-0                       |

| 11Fh  | SLPCCON1                                                       |              | _                                                                                                            | _               | SC1RNG           |                | SC1ISI        | ET<3:0> |         | 0 0000              | 0 0000                          |

| Logor | ale llaiman la                                                 | manted laget | ted locations read as $(0, u) = unchanged x = unknown x = value depends on condition shaded = unimplemented$ |                 |                  |                |               |         |         |                     |                                 |

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition shaded = unimplemented.

# 2.3.8 PCON REGISTER

The Power Control (PCON) register (see Table 19-2) contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the  $\overline{\text{BOR}}.$

The PCON register bits are shown in Register 2-8.

# REGISTER 2-8: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-q/u | R/W-q/u |

|-------|-----|-----|-----|-----|-----|---------|---------|

|       | _   | _   | _   | _   | —   | POR     | BOR     |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = unchanged                                         |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                                       |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>    |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                                      |

|         | <ul> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)</li> </ul> |

# 3.3 Register Definitions: Flash Program Memory Control

|                                                                      |       |                  |       |                   |       | -                 |       |

|----------------------------------------------------------------------|-------|------------------|-------|-------------------|-------|-------------------|-------|

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0             | R/W-0 |

|                                                                      |       |                  | PMDA  | TL<7:0>           |       |                   |       |

| bit 7                                                                |       |                  |       |                   |       |                   | bit C |

|                                                                      |       |                  |       |                   |       |                   |       |

| Legend:                                                              |       |                  |       |                   |       |                   |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                   |       | d as '0'          |       |

| -n = Value at Po                                                     | OR    | '1' = Bit is set |       | '0' = Bit is clea | red   | x = Bit is unknow | n     |

#### REGISTER 3-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

bit 7-0 PMDATL<7:0>: Eight Least Significant Data bits to Write or Read from Program Memory

#### REGISTER 3-2: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0       | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|

| PMADRL<7:0> |             |       |       |       |       |       |       |  |  |  |

| bit 7       | bit 7 bit 0 |       |       |       |       |       |       |  |  |  |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

bit 7-0 PMADRL<7:0>: Eight Least Significant Address bits for Program Memory Read/Write Operation

#### REGISTER 3-3: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|--|

| —     | —   |       | PMDATH<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMDATH<5:0>**: Six Most Significant Data bits from Program Memory

### REGISTER 3-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-0               | U-0              | U-0              | U-0 | U-0                                | U-0 | R/W-0              | R/W-0  |

|-------------------|------------------|------------------|-----|------------------------------------|-----|--------------------|--------|

| _                 | _                | -                | —   | -                                  | -   | PMADR              | H<1:0> |

| bit 7             |                  |                  | •   | •                                  |     |                    | bit 0  |

|                   |                  |                  |     |                                    |     |                    |        |

| Legend:           |                  |                  |     |                                    |     |                    |        |

| R = Readable bit  | W = Writable bit |                  |     | U = Unimplemented bit, read as '0' |     |                    |        |

| -n = Value at POR |                  | '1' = Bit is set |     | '0' = Bit is cleare                | d   | x = Bit is unknown |        |

bit 7-2 Unimplemented: Read as '0'

PMADRH<1:0>: Specifies the two Most Significant Address bits or High bits for Program Memory Reads.

bit 1-0

# 5.5 Register Definitions: PORTA Control

| REGISTE         | R 5-2:               | PORTA                                                                 | A: PORTA RE          | GISTER          |                                                       |                      |                       |                |  |

|-----------------|----------------------|-----------------------------------------------------------------------|----------------------|-----------------|-------------------------------------------------------|----------------------|-----------------------|----------------|--|

| U-0             | ι                    | J-0                                                                   | R/W-x/u              | R/W-x/u         | R-x/x                                                 | R/W-x/u              | R/W-x/u               | R/W-x/u        |  |

| _               | -                    | _                                                                     | RA5                  | RA4             | RA3                                                   | RA2                  | RA1                   | RA0            |  |

| bit 7           |                      |                                                                       |                      |                 |                                                       |                      |                       | bit C          |  |

|                 |                      |                                                                       |                      |                 |                                                       |                      |                       |                |  |

| Legend:         |                      |                                                                       |                      |                 |                                                       |                      |                       |                |  |

| R = Readab      | le bit               |                                                                       | W = Writable bit     |                 | U = Unimpleme                                         | nted bit, read as '0 | ,                     |                |  |

| u = Bit is und  | changed              |                                                                       | x = Bit is unknow    | 'n              | -n/n = Value at POR and BOR/Value at all other Resets |                      |                       |                |  |

| '1' = Bit is se | et                   |                                                                       | '0' = Bit is cleare  | d               |                                                       |                      |                       |                |  |

| bit 7-6         | Unimp                | lemented                                                              | : Read as '0'        |                 |                                                       |                      |                       |                |  |

| bit 5-0         | 1 = Po               | <b>0&gt;</b> : PORT<br>rt pin is <u>&gt;</u><br>rt pin is <u>&lt;</u> |                      |                 |                                                       |                      |                       |                |  |

| Note 1:         | Writes to PO values. | RTA are a                                                             | ctually written to o | corresponding L | ATA register. Rea                                     | ds from PORTA re     | gister is return of a | actual I/O pin |  |

# REGISTER 5-3: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R-1/1                 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----------------------|---------|---------|---------|

| —     | —   | TRISA5  | TRISA4  | TRISA3 <sup>(1)</sup> | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |         |         |                       |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0'                              |

|---------|---------------------------------------------------------|

| bit 5-0 | TRISA<5:0>: PORTA Tri-State Control bits <sup>(1)</sup> |

|         | 1 = PORTA pin configured as an input (tri-stated)       |

|         | 0 = PORTA pin configured as an output                   |

Note 1: TRISA3 always reads '1'.

#### REGISTER 5-4: LATA: PORTA DATA LATCH REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | U-0 | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|-----|---------|---------|---------|

| —     | —   | LATA5   | LATA4   | —   | LATA2   | LATA1   | LATA0   |

| bit 7 |     |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 5-4 LATA<5:4>: PORTA Output Latch Value bits<sup>(1)</sup>

bit 3 Unimplemented: Read as '0'

- bit 2-0 LATA<2:0>: PORTA Output Latch Value bits<sup>(1)</sup>

- Note 1: Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

| U-0                                               | U-0                            | R/W-1/1          | R/W-1/1 | U-0                                      | U-0 | U-0 | U-0   |  |  |

|---------------------------------------------------|--------------------------------|------------------|---------|------------------------------------------|-----|-----|-------|--|--|

| _                                                 | —                              | SLRC5            | SLRC4   | _                                        | _   | _   | —     |  |  |

| bit 7                                             |                                |                  |         | -                                        | •   |     | bit 0 |  |  |

|                                                   |                                |                  |         |                                          |     |     |       |  |  |

| Legend:                                           |                                |                  |         |                                          |     |     |       |  |  |

| R = Readabl                                       | le bit                         | W = Writable     | bit     | U = Unimplemented bit, read as '0'       |     |     |       |  |  |

| -n = Value at                                     | t POR                          | '1' = Bit is set |         | 0' = Bit is cleared $x = Bit is unknown$ |     |     | nown  |  |  |

|                                                   |                                |                  |         |                                          |     |     |       |  |  |

| bit 7-6                                           | Unimplemen                     | ted: Read as '   | 0'      |                                          |     |     |       |  |  |

| bit 5-4 SLRC<5:4>: Slew Rate Control Register bit |                                |                  |         |                                          |     |     |       |  |  |

|                                                   | 1 = Slew rate                  | control enabled  |         |                                          |     |     |       |  |  |

|                                                   | 0 = Slew rate                  | control disabled | 1       |                                          |     |     |       |  |  |

| bit 3-0                                           | 3-0 Unimplemented: Read as '0' |                  |         |                                          |     |     |       |  |  |

# REGISTER 5-13: SLRCONC: SLEW RATE CONTROL REGISTER

### REGISTER 5-14: ANSELC: PORTC ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     |     | —   | —   | ANSC3 | ANSC2 | ANSC1 | ANSC0 |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 **ANSC<3:0>:** Analog Select Between Analog or Digital Function on Pin RC<3:0> bits 1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup>

- 0 = Digital I/O. Pin is assigned to port or special function.

- **Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-onchange if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

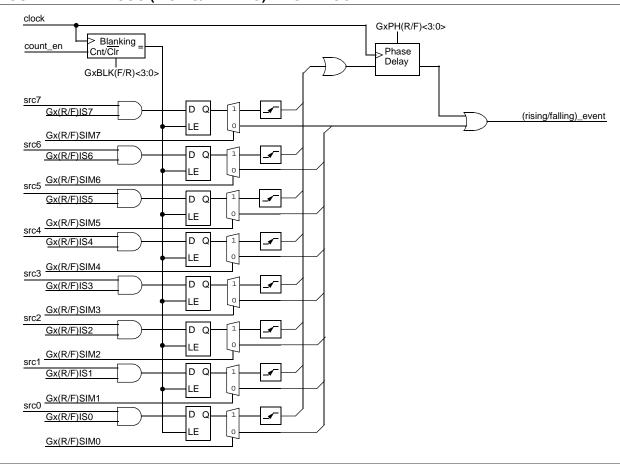

# FIGURE 11-2: COG (RISING/FALLING) INPUT BLOCK

When the phase delay count value is zero, phase delay is disabled and the phase delay counter output is true, thereby allowing the event signal to pass straight through to complementary output driver flop.

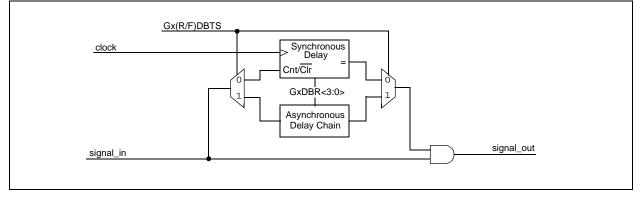

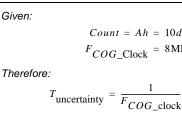

#### CUMULATIVE UNCERTAINTY 11.7.1

It is not possible to create more than one COG\_clock of uncertainty by successive stages. Consider that the phase delay stage comes after the blanking stage, the dead-band stage comes after either the blanking or phase delay stages, and the blanking stage comes after the dead-band stage. When the preceding stage is enabled, the output of that stage is necessarily synchronous with the COG\_clock, which removes any possibility of uncertainty in the succeeding stage.

#### EQUATION 11-1: PHASE, DEAD-BAND AND **BLANKING TIME** CALCULATION

$$T_{\min} = \frac{\text{Count}}{F_{COG\_clock}}$$

$$T_{\max} = \frac{\text{Count} + 1}{F_{COG\_clock}}$$

$$T_{\text{uncertainty}} = T_{\max} - T_{\min}$$

Also:

$$T_{\text{uncertainty}} = \frac{1}{F_{COG\_clock}}$$

Where:

| т                      | Count   |

|------------------------|---------|

| Rising Phase Delay     | COGxPHR |

| Falling Phase Delay    | COGxPHF |

| Rising Dead Band       | COGxDBR |

| Falling Dead Band      | COGxDBF |

| Rising Event Blanking  | COGxBKR |

| Falling Event Blanking | COGxBKF |

### EQUATION 11-2: TIMER UNCERTAINTY

Count = Ah = 10d

$F_{COG\_Clock} = 8MHz$

$$= \frac{1}{8MHz} = 125ns$$

Proof:

$$T_{\min} = \frac{Count}{F_{COG\_clock}}$$

$$= 125ns \bullet 10d \qquad = 1.25\mu s$$

$$T_{\max} = \frac{Count + 1}{F_{COG\_clock}}$$

$$= 125 ns \bullet (10d + 1)$$

$$= 1.375 \, \mu s$$

Therefore:

$$T_{\text{uncertainty}} = T_{\text{max}} - T_{\text{min}}$$

$$= 1.375 \,\mu s - 1.25 \,\mu s$$

$$= 125 \,n s$$

# 11.9 Buffer Updates

Changes to the phase, dead-band, and blanking count registers need to occur simultaneously during COG operation to avoid unintended operation that may occur as a result of delays between each register write. This is accomplished with the GxLD bit of the COGxCON0 register and double buffering of the phase, blanking, and dead-band count registers.

Before the COG module is enabled, writing the count registers loads the count buffers without need of the GxLD bit. However, when the COG is enabled, the count buffers updates are suspended after writing the count registers until after the GxLD bit is set. When the GxLD bit is set, the phase, dead-band, and blanking register values are transferred to the corresponding buffers synchronous with COG operation. The GxLD bit is cleared by hardware when the transfer is complete.

# 11.10 Alternate Pin Selection

The COGxOUT0, COGxOUT1 and COGxFLT functions can be directed to alternate pins with control bits of the APFCON register. Refer to Register 5-1.

**Note:** The default COG outputs have high drive strength capability, whereas the alternate outputs do not.

## 11.11 Operation During Sleep

The COG continues to operate in Sleep provided that the COG\_clock, rising event, and falling event sources remain active.

The HFINTSOC remains active during Sleep when the COG is enabled and the HFINTOSC is selected as the COG\_clock source.

# 11.12 Configuring the COG

The following steps illustrate how to properly configure the COG to ensure a synchronous start with the rising event input:

- 1. Configure the desired COGxFLT input, COGxOUT0 and COGxOUT1 pins with the corresponding bits in the APFCON register.

- 2. Clear all ANSELA register bits associated with pins that are used for COG functions.

- Ensure that the TRIS control bits corresponding to COGxOUT0 and COGxOUT1 are set so that both are configured as inputs. These will be set as outputs later.

- 4. Clear the GxEN bit, if not already cleared.

- 5. Set desired dead-band times with the COGxDBR and COGxDBF registers.

- 6. Set desired blanking times with the COGxBKR and COGxBKF registers.

- 7. Set desired phase delay with the COGxPHR and COGxPHF registers.

- 8. Select the desired shutdown sources with the COGxASD1 register.

- 9. Set up the following controls in COGxASD0 auto-shutdown register:

- Select both output overrides to the desired levels (this is necessary, even if not using auto-shutdown because start-up will be from a shutdown state).

- Set the GxASDE bit and clear the GxARSEN bit.

- 10. Select the desired rising and falling event sources with the COGxRIS and COGxFIS registers.

- 11. Select the desired rising and falling event modes with the COGxRSIM and COGxFSIM registers.

- 12. Configure the following controls in the COGxCON1 register:

- Select the desired clock source

- Select the desired dead-band timing sources

- 13. Configure the following controls in the COGxCON0 register:

- Select the desired output polarities.

- Set the output enables of the outputs to be used.

- 14. Set the GxEN bit.

- 15. Clear TRIS control bits corresponding to COGxOUT0 and COGxOUT1 to be used, thereby configuring those pins as outputs.

- 16. If auto-restart is to be used, set the GxARSEN bit and the GxASDE will be cleared automatically. Otherwise, clear the GxASDE bit to start the COG.

| U-0              | R/W-0/0                                                                                                                    | R/W-0/0                                                                                      | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------|----------------|------------------|------------------|-------------|--|--|

| —                | GxRIHLT2                                                                                                                   | GxRIHLT1                                                                                     | GxRIT2M         | GxRIFLT        | GxRICCP1         | GxRIC2           | GxRIC1      |  |  |

| bit 7            |                                                                                                                            |                                                                                              |                 |                |                  |                  | bit         |  |  |

| Legend:          |                                                                                                                            |                                                                                              |                 |                |                  |                  |             |  |  |

| R = Readable     | bit                                                                                                                        | W = Writable                                                                                 | bit             | U = Unimplei   | mented bit, read | as '0'           |             |  |  |

| u = Bit is unch  | nanged                                                                                                                     | x = Bit is unkr                                                                              | nown            | -n/n = Value   | at POR and BOF   | R/Value at all c | ther Resets |  |  |

| '1' = Bit is set |                                                                                                                            | '0' = Bit is clea                                                                            | ared            | q = Value de   | pends on conditi | on               |             |  |  |

|                  |                                                                                                                            |                                                                                              |                 |                |                  |                  |             |  |  |

| bit 7            | Unimplemen                                                                                                                 | ted: Read as '                                                                               | 0'              |                |                  |                  |             |  |  |

| bit 6            |                                                                                                                            | OGx Rising Ev                                                                                | •               |                | oit              |                  |             |  |  |

|                  |                                                                                                                            | 2 output is enal<br>2 has no effect                                                          |                 |                |                  |                  |             |  |  |

| bit 5            |                                                                                                                            | COGx Rising Ev                                                                               | •               |                | oit              |                  |             |  |  |

| Sit 0            |                                                                                                                            | 1 output is enal                                                                             |                 |                |                  |                  |             |  |  |

|                  | 0 = HLTimer                                                                                                                | 1 has no effect                                                                              | on the rising e | event          |                  |                  |             |  |  |

| bit 4            |                                                                                                                            | OGx Rising Eve                                                                               |                 |                |                  |                  |             |  |  |

|                  |                                                                                                                            | natch with PR2<br>natch with PR2                                                             |                 |                |                  |                  |             |  |  |

| bit 3            |                                                                                                                            | Gx Rising Eve                                                                                |                 | •              |                  |                  |             |  |  |

| Sit 0            |                                                                                                                            | T pin is enable                                                                              |                 |                |                  |                  |             |  |  |

|                  | 0 = COGxFLT pin has no effect on the rising event                                                                          |                                                                                              |                 |                |                  |                  |             |  |  |

| bit 2            |                                                                                                                            | COGx Rising E                                                                                |                 |                | bit              |                  |             |  |  |

|                  | <ul> <li>1 = CCP1 output is enabled as a rising event input</li> <li>0 = CCP1 has no effect on the rising event</li> </ul> |                                                                                              |                 |                |                  |                  |             |  |  |

| bit 1            |                                                                                                                            |                                                                                              | 0               |                |                  |                  |             |  |  |

|                  |                                                                                                                            | Bx Rising Event Input Source 1 Enable bit<br>tor 2 output is enabled as a rising event input |                 |                |                  |                  |             |  |  |

|                  |                                                                                                                            | ator 2 output ha                                                                             |                 |                |                  |                  |             |  |  |

| bit 0            | GxRIC1: CO                                                                                                                 | Gx Rising Even                                                                               | t Input Source  | e 0 Enable bit |                  |                  |             |  |  |

|                  |                                                                                                                            | ator 1 output is                                                                             |                 |                |                  |                  |             |  |  |

|                  | 0 - Compare                                                                                                                | ator 1 output ha                                                                             | a no offect on  |                |                  |                  |             |  |  |

# REGISTER 11-3: COGxRIS: COG RISING EVENT INPUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|-----|-----|------------|---------|---------|---------|

| —     | —   | —   | —   | GxDBR<3:0> |         |         |         |

| bit 7 | •   |     |     |            |         |         | bit 0   |

|       |     |     |     |            |         |         |         |

#### REGISTER 11-9: COGxDBR: COG RISING EVENT DEAD-BAND COUNT REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-4 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

bit 3-0 **GxDBR<3:0>:** Rising Event Dead-band Count Value bits <u>GxRDBTS = 1:</u> = Number of delay chain element periods to delay primary output after rising event <u>GxRDBTS = 0:</u> = Number of COGx clock periods to delay primary output after rising event

### REGISTER 11-10: COGxDBF: COG FALLING EVENT DEAD-BAND COUNT REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|-----|-----|------------|---------|---------|---------|

| —     | —   |     | —   | GxDBF<3:0> |         |         |         |

| bit 7 |     |     |     |            |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

## bit 7-4 Unimplemented: Read as '0'

bit 3-0 GxDBF<3:0>: Falling Event Dead-Band Count Value bits

GxFDBTS = 1:

= Number of delay chain element periods to delay complementary output after falling event input GxFDBTS = 0:

= Number of COGx clock periods to delay complementary output after falling event input

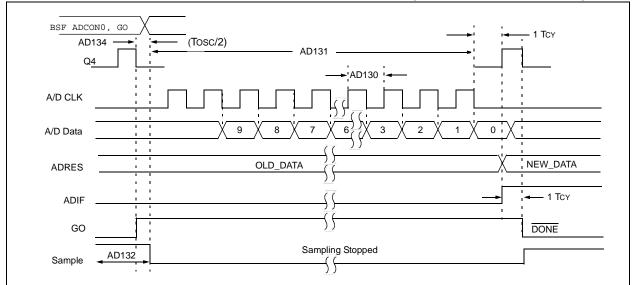

#### REGISTER 12-3: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0 (READ-ONLY)

| R-x               | R-x | R-x              | R-x  | R-x                                | R-x | R-x                | R-x   |

|-------------------|-----|------------------|------|------------------------------------|-----|--------------------|-------|

|                   |     |                  | ADRE | SH<9:2>                            |     |                    |       |

| bit 7             |     |                  |      |                                    |     |                    | bit 0 |

|                   |     |                  |      |                                    |     |                    |       |

| Legend:           |     |                  |      |                                    |     |                    |       |

| R = Readable bit  |     | W = Writable bit |      | U = Unimplemented bit, read as '0' |     |                    |       |

| -n = Value at POR |     | '1' = Bit is set |      | '0' = Bit is cleared               |     | x = Bit is unknown |       |

bit 7-0 ADRESH<9:2>: ADC Result Register bits

Upper eight bits of 10-bit conversion result

#### REGISTER 12-4: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0 (READ-ONLY)

|         |     |     |       | •      | ,   | •   | ,     |

|---------|-----|-----|-------|--------|-----|-----|-------|

| R-x     | R-x | U-0 | U-0   | U-0    | U-0 | U-0 | U-0   |

|         |     |     | ADRES | L<7:0> |     |     |       |

| bit 7   |     |     |       |        |     |     | bit 0 |

|         |     |     |       |        |     |     |       |

| Legend: |     |     |       |        |     |     |       |

|         |     |     |       |        |     |     |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 7-0

**ADRESL<7:0>**: ADC Result Register bits Lower two bits of 10-bit conversion result

#### REGISTER 12-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1 (READ-ONLY)

|       |     |     |     | •   |     | •     | ,      |

|-------|-----|-----|-----|-----|-----|-------|--------|

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-x   | R-x    |

| —     | —   | —   | —   | —   | —   | ADRES | H<9:8> |

| bit 7 |     |     |     |     |     |       | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 ADRESH<9:8>: ADC Result Register bits

Upper two bits of 10-bit conversion result

#### REGISTER 12-6: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1 (READ-ONLY)

| R-x   | R-x         | R-x | R-x | R-x | R-x | R-x | R-x   |  |  |  |

|-------|-------------|-----|-----|-----|-----|-----|-------|--|--|--|

|       | ADRESL<7:0> |     |     |     |     |     |       |  |  |  |

| bit 7 |             |     |     |     |     |     | bit 0 |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 7-0 ADRESL<7:0>: ADC Result Register bits Lower eight bits of 10-bit conversion result

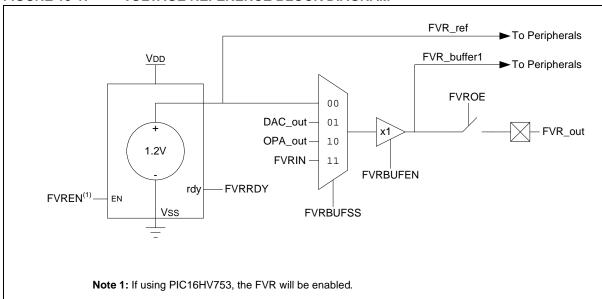

# 13.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference (FVR) is a stable voltage reference, independent of VDD, with 1.2V output level. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- Comparator 1 positive input (C1VP)

- Comparator 2 positive input (C2VP)

- FVR\_out pin

- Shunt regulator

On the PIC16F753, the FVR is enabled by setting the FVREN bit of the FVRCON register. The FVR is always enabled on the PIC16HV753 device.

# 13.1 Fixed Voltage Reference Output

The FVR output can be applied to the FVROUT pin by setting the FVRBUFSS and FVRBUFEN bits of the FVRCON register. The FVRBUFSS bit selects the op amp, FVR or DAC output reference to the FVROUT pin buffer. The FVRBUFEN bit enables the output buffer to the FVROUT pin.

Enabling the FVROUT pin automatically overrides any digital input or output functions of the pin. Reading the FVROUT pin when it has been configured for a reference voltage output will always return a '0'.

# 13.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference circuit to stabilize. Once the circuit stabilizes and is ready for use, the FVRRDY bit of the FVRCON register will be set. See **Section 22.0 "Electrical Specifications"** for the minimum delay requirement.

# 13.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the FVRCON register are not affected. To minimize current consumption in Sleep mode, the FVR voltage reference should be disabled.

# 13.4 Effects of a Reset

A device Reset clears the FVRCON register. As a result:

- The FVR module is disabled

- The FVR voltage output is disabled on the FVROUT pin

# FIGURE 13-1: VOLTAGE REFERENCE BLOCK DIAGRAM

# 14.7 Register Definitions: DAC Control

| D // / 0 /0      | D / 1 / 2 / 2                                                        | <b>D M M M</b>                                              |               |               | D // / 0 / 0     | ERU    |            |  |  |

|------------------|----------------------------------------------------------------------|-------------------------------------------------------------|---------------|---------------|------------------|--------|------------|--|--|

| R/W-0/0          | R/W-0/0                                                              | R/W-0/0                                                     | U-0           | R/W-0/0       | R/W-0/0          | U-0    | U-0        |  |  |

| DACEN            | DACFM                                                                | DACOE                                                       | —             | DACPS         | SS<1:0>          | —      |            |  |  |

| bit 7            |                                                                      |                                                             |               |               |                  |        | bit (      |  |  |

| Legend:          |                                                                      |                                                             |               |               |                  |        |            |  |  |

| R = Readable     | bit                                                                  | W = Writable                                                | bit           | U = Unimplen  | nented bit, read | as '0' |            |  |  |

| u = Bit is unch  |                                                                      | x = Bit is unkr                                             |               | •             | t POR and BO     |        | her Resets |  |  |

| '1' = Bit is set | ungou                                                                | $(0)^{2} = Bit is clear$                                    |               |               |                  |        |            |  |  |

|                  |                                                                      |                                                             |               |               |                  |        |            |  |  |

| bit 7            | DACEN: DAC Enable bit<br>1 = DACx is enabled<br>0 = DACx is disabled |                                                             |               |               |                  |        |            |  |  |

| bit 6            | 1 = DACx ou                                                          | C Output Forma<br>itput result is rig<br>itput result is le | ght justified |               |                  |        |            |  |  |

| bit 5            | 1 = DACx vo                                                          | •                                                           | so an output  | on the DACxOL |                  |        |            |  |  |

| bit 4            | Unimplemen                                                           | ted: Read as '                                              | o'            |               |                  |        |            |  |  |

| bit 3-2          | DACPSS<1:0<br>11 = FVR ou<br>10 = VREF+<br>01 = OPA1C<br>00 = VDD    | pin                                                         | ve Source Se  | lect bits     |                  |        |            |  |  |

|                  |                                                                      |                                                             |               |               |                  |        |            |  |  |

# REGISTER 14-1: DACxCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| TADLE 19-4. | INITIALIZATION CONDITION FOR REGISTERS (CONTINUED) |                |                                                           |                                                                                       |  |  |  |  |  |  |

|-------------|----------------------------------------------------|----------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Register    | Address                                            | Power-on Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup> | Wake-up from Sleep through<br>Interrupt<br>Wake-up from Sleep through<br>WDT Time-out |  |  |  |  |  |  |

| CM1CON0     | 9Dh                                                | 0000 0100      | 0000 0100                                                 | uuuu uuuu                                                                             |  |  |  |  |  |  |

| CM1CON1     | 9Eh                                                | 00000          | 00000                                                     | uuuuu                                                                                 |  |  |  |  |  |  |

| CMOUT       | 9Fh                                                | 00             | 00                                                        | uu                                                                                    |  |  |  |  |  |  |

| LATA        | 105h                                               | xx -xxx        | uu -uuu                                                   | uu -uuu                                                                               |  |  |  |  |  |  |

| IOCAN       | 108h                                               | 00 0000        | 00 0000                                                   | uu uuuu                                                                               |  |  |  |  |  |  |

| WPUA        | 10Ch                                               | 00 0000        | 00 0000                                                   | uu uuuu                                                                               |  |  |  |  |  |  |

| SLRCON0     | 10Dh                                               | 0-0            | 0-0                                                       | u-u                                                                                   |  |  |  |  |  |  |

| PCON        | 10Fh                                               | dd             | (1, 5)                                                    | uu                                                                                    |  |  |  |  |  |  |

| TMR2        | 110h                                               | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |  |  |  |  |

| PR2         | 111h                                               | 1111 1111      | 1111 1111                                                 | uuuu uuuu                                                                             |  |  |  |  |  |  |

| T2CON       | 112h                                               | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                             |  |  |  |  |  |  |

| HLTMR1      | 113h                                               | 0000 0000      | 0000 0000                                                 | uuuu uuuu                                                                             |  |  |  |  |  |  |

| HLTPR1      | 114h                                               | 1111 1111      | 1111 1111                                                 | <u>uuuu</u> uuuu                                                                      |  |  |  |  |  |  |

| HLT1CON0    | 115h                                               | -000 0000      | -000 0000                                                 | -uuu uuuu                                                                             |  |  |  |  |  |  |

| HLT1CON1    | 116h                                               | 0 0000         | 0 0000                                                    | u uuuu                                                                                |  |  |  |  |  |  |

| ANSELA      | 185h                                               | 11 -111        | 11 -111                                                   | uu -uuu                                                                               |  |  |  |  |  |  |

| APFCON      | 188h                                               | 0 -000         | 0 -000                                                    | u -uuu                                                                                |  |  |  |  |  |  |

| OSCTUNE     | 189h                                               | 0 0000         | u uuuu                                                    | u uuuu                                                                                |  |  |  |  |  |  |

| PMCON1      | 18Ch                                               | 000            | 000                                                       | uuu                                                                                   |  |  |  |  |  |  |

| PMCON2      | 18Dh                                               |                |                                                           |                                                                                       |  |  |  |  |  |  |