Welcome to **E-XFL.COM**

Understanding <u>Embedded - DSP (Digital Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

## Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Obsolete                                                               |

| Туре                    | SC140 Core                                                             |

| Interface               | DSI, Ethernet, RS-232                                                  |

| Clock Rate              | 500MHz                                                                 |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 1.436MB                                                                |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.20V                                                                  |

| Operating Temperature   | 0°C ~ 90°C (TJ)                                                        |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 431-BFBGA, FCBGA                                                       |

| Supplier Device Package | 431-FCPBGA (20x20)                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmsc8122mp8000 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1   | Pin A  | Assignments4                                                                      | Figure 10.Internal Tick Spacing for Memory Controller Signals 22 | 2 |

|-----|--------|-----------------------------------------------------------------------------------|------------------------------------------------------------------|---|

|     | 1.1    | FC-PBGA Ball Layout Diagrams4                                                     | Figure 11. SIU Timing Diagram                                    | 5 |

|     | 1.2    | Signal List By Ball Location7                                                     | Figure 12.CLKOUT and CLKIN Signals                               | 6 |

| 2   | Elect  | rical Characteristics                                                             | Figure 13.DMA Signals 2                                          | 7 |

|     | 2.1    | Maximum Ratings                                                                   | Figure 14.Asynchronous Single- and Dual-Strobe Modes Read        |   |

|     | 2.2    | Recommended Operating Conditions14                                                | Timing Diagram                                                   | 9 |

|     | 2.3    | Thermal Characteristics                                                           | Figure 15.Asynchronous Single- and Dual-Strobe Modes Write       |   |

|     | 2.4    | DC Electrical Characteristics                                                     | Timing Diagram                                                   | 0 |

|     | 2.5    | AC Timings                                                                        | Figure 16. Asynchronous Broadcast Write Timing Diagram 30        | 0 |

| 3   | Hard   | ware Design Considerations39                                                      | Figure 17.DSI Synchronous Mode Signals Timing Diagram 3          | 1 |

|     | 3.1    | Start-up Sequencing Recommendations39                                             | Figure 18.TDM Inputs Signals                                     | 2 |

|     | 3.2    | Power Supply Design Considerations                                                | Figure 19.TDM Output Signals                                     | 2 |

|     | 3.3    | Connectivity Guidelines41                                                         | Figure 20.UART Input Timing                                      | 3 |

|     | 3.4    | External SDRAM Selection                                                          | Figure 21.UART Output Timing                                     | 3 |

|     | 3.5    | Thermal Considerations                                                            | Figure 22.Timer Timing                                           | 4 |

| 4   |        | ring Information                                                                  | Figure 23.MDIO Timing Relationship to MDC                        | 4 |

| 5   | Pack   | age Information                                                                   | Figure 24.MII Mode Signal Timing                                 | 5 |

| 6   | Prod   | uct Documentation                                                                 | Figure 25.RMII Mode Signal Timing                                |   |

| 7   | Revi   | sion History                                                                      | Figure 26.SMII Mode Signal Timing                                | 6 |

| 1 : |        | Eiguros                                                                           | Figure 27.GPIO Timing                                            | 7 |

|     |        | Figures                                                                           | Figure 28.EE Pin Timing                                          |   |

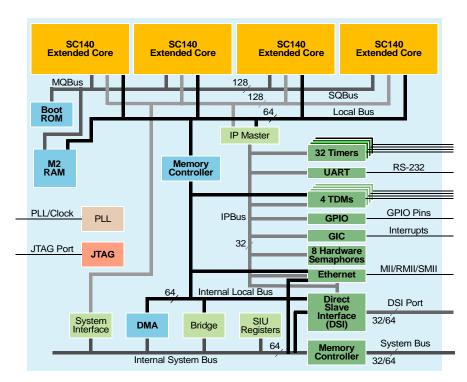

|     |        | MSC8122 Block Diagram                                                             | Figure 29.Test Clock Input Timing Diagram 38                     |   |

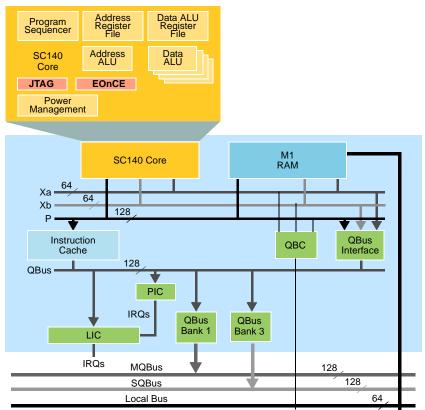

|     |        | StarCore SC140 DSP Extended Core Block Diagram 3                                  | Figure 30.Boundary Scan (JTAG) Timing Diagram                    | 8 |

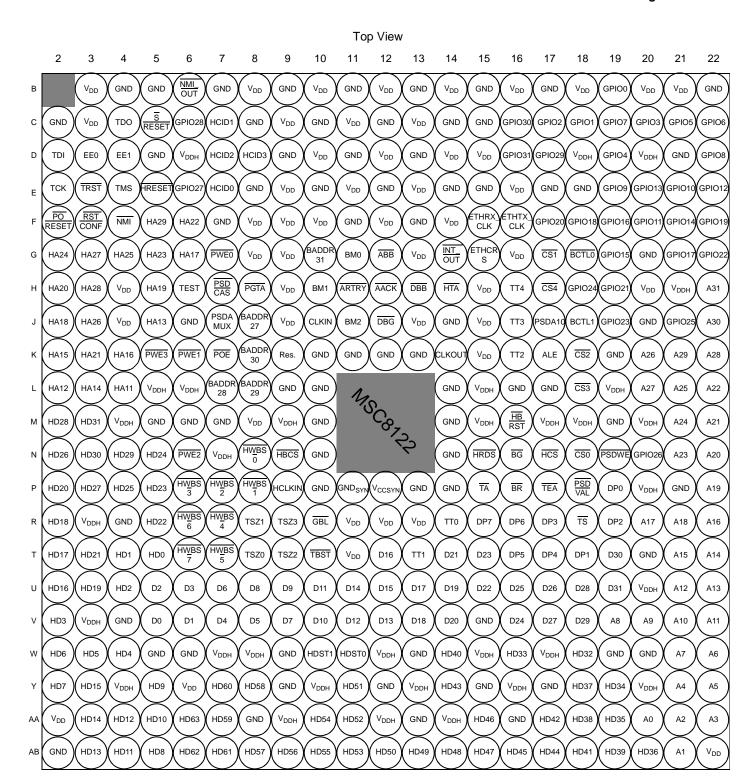

| _   |        | MSC8122 Package, Top View 5                                                       | Figure 31.Test Access Port Timing Diagram                        |   |

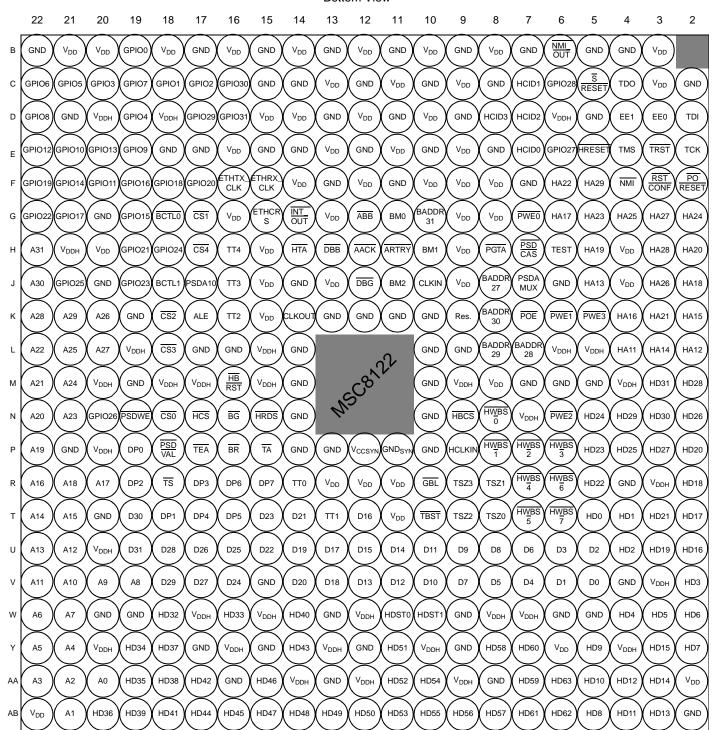

|     |        | MSC8122 Package, Bottom View                                                      | Figure 32.TRST Timing Diagram                                    |   |

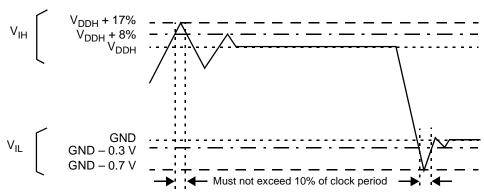

|     |        | Overshoot/Undershoot Voltage for V <sub>IH</sub> and V <sub>IL</sub> 16           | Figure 33.Core Power Supply Decoupling                           | 0 |

|     |        | Start-Up Sequence: V <sub>DD</sub> and V <sub>DDH</sub> Raised Together 17        | Figure 34.V <sub>CCSYN</sub> Bypass                              | 1 |

| Fig | ure 7. | Start-Up Sequence: V <sub>DD</sub> Raised Before V <sub>DDH</sub> with CLKIN      | Figure 35.MSC8122 Mechanical Information, 431-pin FC-PBGA        |   |

|     |        | Started with V <sub>DDH</sub>                                                     | Package 4-                                                       | 4 |

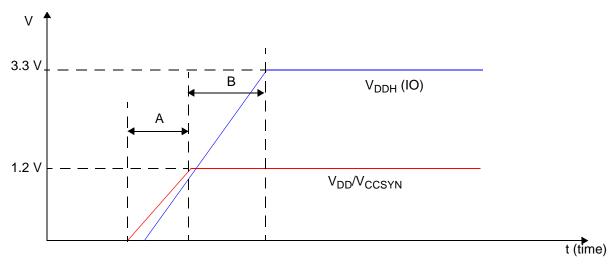

|     |        | Power-Up Sequence for V <sub>DDH</sub> and V <sub>DD</sub> /V <sub>CCSYN</sub> 18 |                                                                  |   |

| Fig | ure 9. | Timing Diagram for a Reset Configuration Write 21                                 |                                                                  |   |

Figure 1. MSC8122 Block Diagram

Notes: 1. The arrows show the data transfer direction.

2. The QBus interface includes a bus switch, write buffer, fetch unit, and a control unit that defines four QBus banks. In addition, the QBC handles internal memory contentions.

Figure 2. StarCore SC140 DSP Extended Core Block Diagram

# 1 Pin Assignments

This section includes diagrams of the MSC8122 package ball grid array layouts and pinout allocation tables.

### 1.1 FC-PBGA Ball Layout Diagrams

Top and bottom views of the FC-PBGA package are shown in Figure 3 and Figure 4 with their ball location index numbers.

Figure 3. MSC8122 Package, Top View

#### **Bottom View**

Figure 4. MSC8122 Package, Bottom View

## 1.2 Signal List By Ball Location

Table 1 presents signal list sorted by ball number. -

Table 1. MSC8122 Signal Listing by Ball Designator

| Des. | Signal Name                 | Des. | Signal Name                        |

|------|-----------------------------|------|------------------------------------|

| В3   | $V_{DD}$                    | C18  | GPIO1/TIMER0/CHIP_ID1/IRQ5/ETHTXD1 |

| B4   | GND                         | C19  | GPIO7/TDM3RCLK/IRQ5/ETHTXD3        |

| B5   | GND                         | C20  | GPIO3/TDM3TSYN/IRQ1/ETHTXD2        |

| В6   | NMI_OUT                     | C21  | GPIO5/TDM3TDAT/IRQ3/ETHRXD3        |

| B7   | GND                         | C22  | GPIO6/TDM3RSYN/IRQ4/ETHRXD2        |

| В8   | $V_{DD}$                    | D2   | TDI                                |

| В9   | GND                         | D3   | EE0                                |

| B10  | $V_{DD}$                    | D4   | EE1                                |

| B11  | GND                         | D5   | GND                                |

| B12  | $V_{DD}$                    | D6   | $V_{DDH}$                          |

| B13  | GND                         | D7   | HCID2                              |

| B14  | $V_{DD}$                    | D8   | HCID3/HA8                          |

| B15  | GND                         | D9   | GND                                |

| B16  | $V_{DD}$                    | D10  | $V_{DD}$                           |

| B17  | GND                         | D11  | GND                                |

| B18  | $V_{DD}$                    | D12  | $V_{DD}$                           |

| B19  | GPIO0/CHIP_ID0/IRQ4/ETHTXD0 | D13  | GND                                |

| B20  | $V_{DD}$                    | D14  | $V_{DD}$                           |

| B21  | $V_{DD}$                    | D15  | $V_{DD}$                           |

| B22  | GND                         | D16  | GPIO31/TIMER3/SCL                  |

| C2   | GND                         | D17  | GPIO29/CHIP_ID3/ETHTX_EN           |

| C3   | $V_{DD}$                    | D18  | $V_{DDH}$                          |

| C4   | TDO                         | D19  | GPIO4/TDM3TCLK/IRQ2/ETHTX_ER       |

| C5   | SRESET                      | D20  | $V_{DDH}$                          |

| C6   | GPIO28/UTXD/DREQ2           | D21  | GND                                |

| C7   | HCID1                       | D22  | GPIO8/TDM3RDAT/IRQ6/ETHCOL         |

| C8   | GND                         | E2   | TCK                                |

| C9   | $V_{DD}$                    | E3   | TRST                               |

| C10  | GND                         | E4   | TMS                                |

| C11  | $V_{DD}$                    | E5   | HRESET                             |

| C12  | GND                         | E6   | GPIO27/URXD/DREQ1                  |

| C13  | $V_{DD}$                    | E7   | HCID0                              |

| C14  | GND                         | E8   | GND                                |

| C15  | GND                         | E9   | $V_{DD}$                           |

| C16  | GPIO30/TIMER2/TMCLK/SDA     | E10  | GND                                |

| C17  | GPIO2/TIMER1/CHIP_ID2/IRQ6  | E11  | $V_{DD}$                           |

Table 1. MSC8122 Signal Listing by Ball Designator (continued)

| Des. | Signal Name                                | Des. | Signal Name                  |

|------|--------------------------------------------|------|------------------------------|

| E12  | GND                                        | G6   | HA17                         |

| E13  | $V_{DD}$                                   | G7   | PWE0/PSDDQM0/PBS0            |

| E14  | GND                                        | G8   | $V_{DD}$                     |

| E15  | GND                                        | G9   | $V_{DD}$                     |

| E16  | V <sub>DD</sub>                            | G10  | ĪRQ3/BADDR31                 |

| E17  | GND                                        | G11  | BM0/TC0/BNKSEL0              |

| E18  | GND                                        | G12  | ABB/IRQ4                     |

| E19  | GPIO9/TDM2TSYN/IRQ7/ETHMDIO                | G13  | V <sub>DD</sub>              |

| E20  | GPIO13/TDM2RCLK/IRQ11/ETHMDC               | G14  | ĪRQ7/ĪNT_OUT                 |

| E21  | GPIO10/TDM2TCLK/IRQ8/ETHRX_DV/ETHCRS_DV/NC | G15  | ETHCRS/ETHRXD                |

| E22  | GPIO12/TDM2RSYN/IRQ10/ETHRXD1/ETHSYNC      | G16  | V <sub>DD</sub>              |

| F2   | PORESET                                    | G17  | CS1                          |

| F3   | RSTCONF                                    | G18  | BCTL0                        |

| F4   | NMI                                        | G19  | GPIO15/TDM1TSYN/DREQ1        |

| F5   | HA29                                       | G20  | GND                          |

| F6   | HA22                                       | G21  | GPIO17/TDM1TDAT/DACK1        |

| F7   | GND                                        | G22  | GPIO22/TDM0TCLK/DONE2/DRACK2 |

| F8   | $V_{DD}$                                   | H2   | HA20                         |

| F9   | $V_{DD}$                                   | H3   | HA28                         |

| F10  | V <sub>DD</sub>                            | H4   | V <sub>DD</sub>              |

| F11  | GND                                        | H5   | HA19                         |

| F12  | $V_{DD}$                                   | H6   | TEST                         |

| F13  | GND                                        | H7   | PSDCAS/PGPL3                 |

| F14  | V <sub>DD</sub>                            | H8   | PGTA/PUPMWAIT/PGPL4/PPBS     |

| F15  | ETHRX_CLK/ETHSYNC_IN                       | H9   | V <sub>DD</sub>              |

| F16  | ETHTX_CLK/ETHREF_CLK/ETHCLOCK              | H10  | BM1/TC1/BNKSEL1              |

| F17  | GPIO20/TDM1RDAT                            | H11  | ARTRY                        |

| F18  | GPIO18/TDM1RSYN/DREQ2                      | H12  | ĀĀCK                         |

| F19  | GPIO16/TDM1TCLK/DONE1/DRACK1               | H13  | DBB/IRQ5                     |

| F20  | GPIO11/TDM2TDAT/IRQ9/ETHRX_ER/ETHTXD       | H14  | HTA                          |

| F21  | GPIO14/TDM2RDAT/IRQ12/ETHRXD0/NC           | H15  | V <sub>DD</sub>              |

| F22  | GPIO19/TDM1RCLK/DACK2                      | H16  | TT4/CS7                      |

| G2   | HA24                                       | H17  | <del>CS4</del>               |

| G3   | HA27                                       | H18  | GPIO24/TDM0RSYN/IRQ14        |

| G4   | HA25                                       | H19  | GPIO21/TDM0TSYN              |

| G5   | HA23                                       | H20  | $V_{DD}$                     |

Table 1. MSC8122 Signal Listing by Ball Designator (continued)

| Des. | Signal Name                               | Des. | Signal Name      |

|------|-------------------------------------------|------|------------------|

| T6   | HWBS7/HDBS7/HWBE7/HDBE7/PWE7/PSDDQM7/PBS7 | U21  | A12              |

| T7   | HWBS5/HDBS5/HWBE5/HDBE5/PWE5/PSDDQM5/PBS5 | U22  | A13              |

| T8   | TSZ0                                      | V2   | HD3/MODCK1       |

| T9   | TSZ2                                      | V3   | $V_{DDH}$        |

| T10  | TBST                                      | V4   | GND              |

| T11  | $V_{DD}$                                  | V5   | D0               |

| T12  | D16                                       | V6   | D1               |

| T13  | TT1                                       | V7   | D4               |

| T14  | D21                                       | V8   | D5               |

| T15  | D23                                       | V9   | D7               |

| T16  | IRQ5/DP5/DACK4/EXT_BG3                    | V10  | D10              |

| T17  | IRQ4/DP4/DACK3/EXT_DBG3                   | V11  | D12              |

| T18  | IRQ1/DP1/DACK1/EXT_BG2                    | V12  | D13              |

| T19  | D30                                       | V13  | D18              |

| T20  | GND                                       | V14  | D20              |

| T21  | A15                                       | V15  | GND              |

| T22  | A14                                       | V16  | D24              |

| U2   | HD16                                      | V17  | D27              |

| U3   | HD19                                      | V18  | D29              |

| U4   | HD2/DSI64                                 | V19  | A8               |

| U5   | D2                                        | V20  | A9               |

| U6   | D3                                        | V21  | A10              |

| U7   | D6                                        | V22  | A11              |

| U8   | D8                                        | W2   | HD6              |

| U9   | D9                                        | W3   | HD5/CNFGS        |

| U10  | D11                                       | W4   | HD4/MODCK2       |

| U11  | D14                                       | W5   | GND              |

| U12  | D15                                       | W6   | GND              |

| U13  | D17                                       | W7   | V <sub>DDH</sub> |

| U14  | D19                                       | W8   | V <sub>DDH</sub> |

| U15  | D22                                       | W9   | GND              |

| U16  | D25                                       | W10  | HDST1/HA10       |

| U17  | D26                                       | W11  | HDST0/HA9        |

| U18  | D28                                       | W12  | $V_{DDH}$        |

| U19  | D31                                       | W13  | GND              |

| U20  | $V_{DDH}$                                 | W14  | HD40/D40/ETHRXD0 |

Figure 5. Overshoot/Undershoot Voltage for VIH and VIL

#### 2.5 AC Timings

The following sections include illustrations and tables of clock diagrams, signals, and parallel I/O outputs and inputs. When systems such as DSP farms are developed using the DSI, use a device loading of 4 pF per pin. AC timings are based on a 20 pF load, except where noted otherwise, and a 50  $\Omega$  transmission line. For loads smaller than 20 pF, subtract 0.06 ns per pF down to 10 pF load. For loads larger than 20 pF, add 0.06 ns for SIU/Ethernet/DSI delay and 0.07 ns for GPIO/TDM/timer delay. When calculating overall loading, also consider additional RC delay.

#### 2.5.1 Output Buffer Impedances

| Output Buffers                                                                                                                       | Typical Impedance ( $\Omega$ ) |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|--|

| System bus                                                                                                                           | 50                             |  |  |  |  |

| Memory controller                                                                                                                    | 50                             |  |  |  |  |

| Parallel I/O                                                                                                                         | 50                             |  |  |  |  |

| <b>Note:</b> These are typical values at 65°C. The impedance may vary by ±25% depending on device process and operating temperature. |                                |  |  |  |  |

Table 6. Output Buffer Impedances

#### 2.5.2 Start-Up Timing

Starting the device requires coordination among several input sequences including clocking, reset, and power. **Section 2.5.3** describes the clocking characteristics. **Section 2.5.4** describes the reset and power-up characteristics. You must use the following guidelines when starting up an MSC8122 device:

- PORESET and TRST must be asserted externally for the duration of the power-up sequence. See **Table 11** for timing.

- If possible, bring up the  $V_{DD}$  and  $V_{DDH}$  levels together. For designs with separate power supplies, bring up the  $V_{DD}$  levels and then the  $V_{DDH}$  levels (see **Figure 7**).

- CLKIN should start toggling at least 16 cycles (starting after V<sub>DDH</sub> reaches its nominal level) before PORESET deassertion to guarantee correct device operation (see Figure 6 and Figure 7).

- CLKIN must not be pulled high during V<sub>DDH</sub> power-up. CLKIN can toggle during this period.

**Note:** See **Section 3.1** for start-up sequencing recommendations and **Section 3.2** for power supply design recommendations.

The following figures show acceptable start-up sequence examples. **Figure 6** shows a sequence in which  $V_{DD}$  and  $V_{DDH}$  are raised together. **Figure 7** shows a sequence in which  $V_{DDH}$  is raised after  $V_{DD}$  and CLKIN begins to toggle as  $V_{DDH}$  rises.

In all cases, the power-up sequence must follow the guidelines shown in Figure 8.

Figure 8. Power-Up Sequence for V<sub>DDH</sub> and V<sub>DD</sub>/V<sub>CCSYN</sub>

The following rules apply:

- 1. During time interval A,  $V_{DDH}$  should always be equal to or less than the  $V_{DD}/V_{CCSYN}$  voltage level. The duration of interval A should be kept below 10 ms.

- 2. The duration of timing interval B should be kept as small as possible and less than 10 ms.

#### 2.5.3 Clock and Timing Signals

The following sections include a description of clock signal characteristics. **Table 7** shows the maximum frequency values for internal (Core, Reference, Bus, and DSI) and external (CLKIN and CLKOUT) clocks. The user must ensure that maximum frequency values are not exceeded.

Characteristic

Maximum in MHz

Core frequency

300/400/500

Reference frequency (REFCLK)

100/133/166

Internal bus frequency (BLCK)

100/133/166

DSI clock frequency (HCLKIN)

HCLKIN ≤ (min{70 MHz, CLKOUT})

• Core frequency = 400/500 MHz

HCLKIN ≤ (min{100 MHz, CLKOUT})

External clock frequency (CLKIN or CLKOUT)

100/133/166

**Table 7. Maximum Frequencies**

**Table 8. Clock Frequencies**

| Charactaristics                                                        | Comple of           | 300 MHz Device |     | 400 MH | z Device | 500 MHz Device |       |  |

|------------------------------------------------------------------------|---------------------|----------------|-----|--------|----------|----------------|-------|--|

| Characteristics                                                        | Symbol              | Min            | Max | Min    | Max      | Min            | Max   |  |

| CLKIN frequency                                                        | F <sub>CLKIN</sub>  | 20             | 100 | 20     | 133.3    | 20             | 166.7 |  |

| BCLK frequency                                                         | F <sub>BCLK</sub>   | 40             | 100 | 40     | 133.3    | 40             | 166.7 |  |

| Reference clock (REFCLK) frequency                                     | F <sub>REFCLK</sub> | 40             | 100 | 40     | 133.3    | 40             | 166.7 |  |

| Output clock (CLKOUT) frequency                                        | F <sub>CLKOUT</sub> | 40             | 100 | 40     | 133.3    | 40             | 166.7 |  |

| SC140 core clock frequency                                             | F <sub>CORE</sub>   | 200            | 300 | 200    | 400      | 200            | 500   |  |

| Note: The rise and fall time of external clocks should be 3 ns maximum |                     |                |     |        |          |                |       |  |

| Table 9. | <b>System</b> | Clock I | <b>Parameters</b> |

|----------|---------------|---------|-------------------|

|----------|---------------|---------|-------------------|

| Characteristic                                                       | Min | Max         | Unit |

|----------------------------------------------------------------------|-----|-------------|------|

| Phase jitter between BCLK and CLKIN                                  | _   | 0.3         | ns   |

| CLKIN frequency                                                      | 20  | see Table 8 | MHz  |

| CLKIN slope                                                          | _   | 3           | ns   |

| CLKIN period jitter <sup>1</sup>                                     | _   | 150         | ps   |

| CLKIN jitter spectrum                                                | 150 | _           | KHz  |

| PLL input clock (after predivider)                                   | 20  | 100         | MHz  |

| PLL output frequency (VCO output)                                    | 800 |             | MHz  |

| 300 MHz core                                                         |     | 1200        | MHz  |

| 400 MHz core                                                         |     | 1600        | MHz  |

| 500 MHz core                                                         |     | 2000        | MHz  |

| CLKOUT frequency jitter <sup>1</sup>                                 | _   | 200         | ps   |

| CLKOUT phase jitter <sup>1</sup> with CLKIN phase jitter of ±100 ps. | _   | 500         | ps   |

Not tested. Guaranteed by design.

#### 2.5.4 **Reset Timing**

The MSC8122 has several inputs to the reset logic:

- Power-on reset (PORESET)

- External hard reset (HRESET)

- External soft reset (SRESET)

- Software watchdog reset

- Bus monitor reset

- Host reset command through JTAG

All MSC8122 reset sources are fed into the reset controller, which takes different actions depending on the source of the reset. The reset status register indicates the most recent sources to cause a reset. Table 10 describes the reset sources.

**Table 10. Reset Sources**

| Name                               | Direction     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset<br>(PORESET)        | Input         | Initiates the power-on reset flow that resets the MSC8122 and configures various attributes of the MSC8122. On PORESET, the entire MSC8122 device is reset. SPLL states is reset, HRESET and SRESET are driven, the SC140 extended cores are reset, and system configuration is sampled. The clock mode (MODCK bits), reset configuration mode, boot mode, Chip ID, and use of either a DSI 64 bits port or a System Bus 64 bits port are configured only when PORESET is asserted.                                       |

| External hard reset (HRESET)       | Input/ Output | Initiates the hard reset flow that configures various attributes of the MSC8122. While HRESET is asserted, SRESET is also asserted. HRESET is an open-drain pin. Upon hard reset, HRESET and SRESET are driven, the SC140 extended cores are reset, and system configuration is sampled. The most configurable features are reconfigured. These features are defined in the 32-bit hard reset configuration word described in Hard Reset Configuration Word section of the Reset chapter in the MSC8122 Reference Manual. |

| External soft reset (SRESET)       | Input/ Output | Initiates the soft reset flow. The MSC8122 detects an external assertion of SRESET only if it occurs while the MSC8122 is not asserting reset. SRESET is an open-drain pin. Upon soft reset, SRESET is driven, the SC140 extended cores are reset, and system configuration is maintained.                                                                                                                                                                                                                                |

| Software watchdog reset            | Internal      | When the MSC8122 watchdog count reaches zero, a software watchdog reset is signalled. The enabled software watchdog event then generates an internal hard reset sequence.                                                                                                                                                                                                                                                                                                                                                 |

| Bus monitor reset                  | Internal      | When the MSC8122 bus monitor count reaches zero, a bus monitor hard reset is asserted. The enabled bus monitor event then generates an internal hard reset sequence.                                                                                                                                                                                                                                                                                                                                                      |

| Host reset command through the TAP | Internal      | When a host reset command is written through the Test Access Port (TAP), the TAP logic asserts the soft reset signal and an internal soft reset sequence is generated.                                                                                                                                                                                                                                                                                                                                                    |

MSC8122 Quad Digital Signal Processor Data Sheet, Rev. 16

The UPM machine and GPCM machine outputs change on the internal tick selected by the memory controller configuration. The AC timing specifications are relative to the internal tick. SDRAM machine outputs change only on the REFCLK rising edge.

**Table 14. AC Timing for SIU Inputs**

| Table 14. Ao Timing for old inputs |                                                                                                                                                                             |                              |                              |                              |                           |          |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|---------------------------|----------|--|--|

|                                    |                                                                                                                                                                             | ٧                            |                              |                              |                           |          |  |  |

|                                    | Characteristic                                                                                                                                                              |                              | ef = CLK                     | IN                           | Ref = CLKOUT              |          |  |  |

| No.                                |                                                                                                                                                                             |                              | 1.2 V                        | 1.2 V                        | 1.2 V                     | Units    |  |  |

|                                    |                                                                                                                                                                             | 100/<br>133                  | 133                          | 166                          | 133                       |          |  |  |

| 10                                 | Hold time for all signals after the 50% level of the REFCLK rising edge                                                                                                     | 0.5                          | 0.5                          | 0.5                          | 0.5                       | ns       |  |  |

| 11a                                | ARTRY/ABB set-up time before the 50% level of the REFCLK rising edge                                                                                                        | 3.1                          | 3.0                          | 3.0                          | 3.0                       | ns       |  |  |

| 11b                                | DBG/DBB/BG/BR/TC set-up time before the 50% level of the REFCLK rising edge                                                                                                 | 3.6                          | 3.3                          | 3.3                          | 3.3                       | ns       |  |  |

| 11c                                | AACK set-up time before the 50% level of the REFCLK rising edge                                                                                                             | 3.0                          | 2.9                          | 2.9                          | 2.9                       | ns       |  |  |

| 11d                                | TA/TEA/PSDVAL set-up time before the 50% level of the REFCLK rising edge  • Data-pipeline mode                                                                              | 3.5                          | 3.4                          | 3.4                          | 3.4                       | ns       |  |  |

|                                    | Non-pipeline mode                                                                                                                                                           | 4.4                          | 4.0                          | 4.0                          | 4.0                       | ns       |  |  |

| 12                                 | Data bus set-up time before REFCLK rising edge in Normal mode  • Data-pipeline mode  • Non-pipeline mode                                                                    | 1.9<br>4.2                   | 1.8<br>4.0                   | 1.7<br>4.0                   | 1.8<br>4.0                | ns<br>ns |  |  |

| 13 <sup>1</sup>                    | Data bus set-up time before the 50% level of the REFCLK rising edge in ECC and PARITY modes  • Data-pipeline mode                                                           | 2.0                          | 2.0                          | 2.0                          | 2.0                       | ns       |  |  |

|                                    | Non-pipeline mode                                                                                                                                                           | 8.2                          | 7.3                          | 7.3                          | 7.3                       | ns       |  |  |

| 14 <sup>1</sup>                    | DP set-up time before the 50% level of the REFCLK rising edge  • Data-pipeline mode  • Non-pipeline mode                                                                    | 2.0<br>7.9                   | 2.0<br>6.1                   | 2.0<br>6.1                   | 2.0<br>6.1                | ns<br>ns |  |  |

| 15a                                | TS and Address bus set-up time before the 50% level of the REFCLK rising edge  Extra cycle mode (SIUBCR[EXDD] = 0)  No extra cycle mode (SIUBCR[EXDD] = 1)                  | 4.2<br>5.5                   | 3.8<br>5.0                   | 3.8<br>5.0                   | 3.8<br>5.0                | ns<br>ns |  |  |

| 15b                                | Address attributes: TT/TBST/TSZ/GBL set-up time before the 50% level of the REFCLK rising edge  Extra cycle mode (SIUBCR[EXDD] = 0)  No extra cycle mode (SIUBCR[EXDD] = 1) | 3.7<br>4.8                   | 3.5<br>4.4                   | 3.5<br>4.4                   | 3.5<br>4.4                | ns<br>ns |  |  |

| 16                                 | PUPMWAIT signal set-up time before the 50% level of the REFCLK rising edge                                                                                                  | 3.7                          | 3.7                          | 3.7                          | 3.7                       | ns       |  |  |

| 17                                 | IRQx setup time before the 50% level; of the REFCLK rising edge <sup>3</sup>                                                                                                | 4.0                          | 4.0                          | 4.0                          | 4.0                       | ns       |  |  |

| 18                                 | IRQx minimum pulse width <sup>3</sup>                                                                                                                                       | 6.0 +<br>T <sub>REFCLK</sub> | 6.0 +<br>T <sub>REFCLK</sub> | 6.0 +<br>T <sub>REFCLK</sub> | 6.0 + T <sub>REFCLK</sub> | ns       |  |  |

Notes:

- 1. Timings specifications 13 and 14 in non-pipeline mode are more restrictive than MSC8102 timings.

- 2. Values are measured from the 50% TTL transition level relative to the 50% level of the REFCLK rising edge.

- 3. Guaranteed by design.

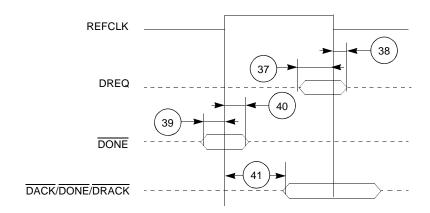

#### 2.5.5.3 DMA Data Transfers

**Table 17** describes the DMA signal timing.

**Table 17. DMA Signals**

| No. | Characteristic                                                      | Ref = | CLKIN | Ref = C<br>(1.2 V | Units |    |

|-----|---------------------------------------------------------------------|-------|-------|-------------------|-------|----|

|     |                                                                     | Min   | Max   | Min               | Max   |    |

| 37  | DREQ set-up time before the 50% level of the falling edge of REFCLK | 5.0   | _     | 5.0               | _     | ns |

| 38  | DREQ hold time after the 50% level of the falling edge of REFCLK    | 0.5   | _     | 0.5               | _     | ns |

| 39  | DONE set-up time before the 50% level of the rising edge of REFCLK  | 5.0   | _     | 5.0               | _     | ns |

| 40  | DONE hold time after the 50% level of the rising edge of REFCLK     | 0.5   | _     | 0.5               | _     | ns |

| 41  | DACK/DRACK/DONE delay after the 50% level of the REFCLK rising edge | 0.5   | 7.5   | 0.5               | 8.4   | ns |

The DREQ signal is synchronized with REFCLK. To achieve fast response, a synchronized peripheral should assert DREQ according to the timings in **Table 17**. **Figure 13** shows synchronous peripheral interaction.

Figure 13. DMA Signals

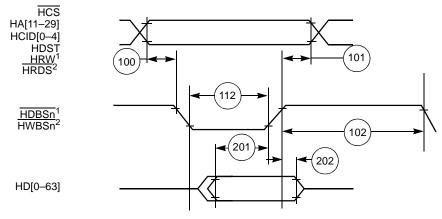

#### 2.5.6 DSI Timing

The timings in the following sections are based on a 20 pF capacitive load.

### 2.5.6.1 DSI Asynchronous Mode

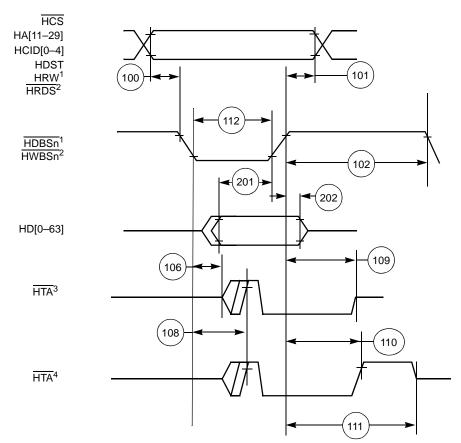

**Table 18. DSI Asynchronous Mode Timing**

| No.    | Characteristics                                                                                                                                                                                                                                                                                                      | Min                                                                                  | Max                              | Unit           |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------|----------------|

| 100    | Attributes <sup>1</sup> set-up time before strobe (HWBS[n]) assertion                                                                                                                                                                                                                                                | 1.5                                                                                  | _                                | ns             |

| 101    | Attributes <sup>1</sup> hold time after data strobe deassertion                                                                                                                                                                                                                                                      | 1.3                                                                                  | _                                | ns             |

| 102    | Read/Write data strobe deassertion width:  • DCR[HTAAD] = 1                                                                                                                                                                                                                                                          |                                                                                      | _                                |                |

|        | Consecutive access to the same DSI     Different device with DCR[HTADT] = 01  Different device with DCR[HTADT] = 40                                                                                                                                                                                                  | 1.8 + T <sub>REFCLK</sub><br>5 + T <sub>REFCLK</sub>                                 |                                  | ns<br>ns       |

|        | Different device with DCR[HTADT] = 10     Different device with DCR[HTADT] = 11     DCR[HTAAD] = 0                                                                                                                                                                                                                   | $5 + (1.5 \times T_{REFCLK})$<br>$5 + (2.5 \times T_{REFCLK})$<br>$1.8 + T_{REFCLK}$ |                                  | ns<br>ns<br>ns |

| 103    | Read data strobe deassertion to output data high impedance                                                                                                                                                                                                                                                           | —                                                                                    | 8.5                              | ns             |

| 104    | Read data strobe assertion to output data active from high impedance                                                                                                                                                                                                                                                 | 2.0                                                                                  | _                                | ns             |

| 105    | Output data hold time after read data strobe deassertion                                                                                                                                                                                                                                                             | 2.2                                                                                  | _                                | ns             |

| 106    | Read/Write data strobe assertion to HTA active from high impedance                                                                                                                                                                                                                                                   | 2.2                                                                                  | _                                | ns             |

| 107    | Output data valid to HTA assertion                                                                                                                                                                                                                                                                                   | 3.2                                                                                  | _                                | ns             |

| 108    | Read/Write data strobe assertion to HTA valid <sup>2</sup> 1.1 V core                                                                                                                                                                                                                                                | _                                                                                    | 7.4                              | ns             |

|        | • 1.2 V core                                                                                                                                                                                                                                                                                                         | _                                                                                    | 6.7                              | ns             |

| 109    | Read/Write data strobe deassertion to output HTA high impedance.  (DCR[HTAAD] = 0, HTA at end of access released at logic 0)                                                                                                                                                                                         | _                                                                                    | 6.5                              | ns             |

| 110    | Read/Write data strobe deassertion to output HTA deassertion.  (DCR[HTAAD] = 1, HTA at end of access released at logic 1)                                                                                                                                                                                            | _                                                                                    | 6.5                              | ns             |

| 111    | Read/Write data strobe deassertion to output HTA high impedance.  (DCR[HTAAD] = 1, HTA at end of access released at logic 1                                                                                                                                                                                          | _                                                                                    |                                  |                |

|        | DCR[HTADT] = 01                                                                                                                                                                                                                                                                                                      |                                                                                      | 5 + T <sub>REFCLK</sub>          | ns             |

|        | DCR[HTADT] = 10     DCR[HTADT] = 11                                                                                                                                                                                                                                                                                  |                                                                                      | 5 + (1.5 × T <sub>REFCLK</sub> ) | ns             |

| 112    | Read/Write data strobe assertion width                                                                                                                                                                                                                                                                               | 1.8 + T <sub>REFCLK</sub>                                                            | 5 + (2.5 × T <sub>REFCLK</sub> ) | ns<br>ns       |

|        |                                                                                                                                                                                                                                                                                                                      |                                                                                      | _                                |                |

| 201    | Host data input set-up time before write data strobe deassertion                                                                                                                                                                                                                                                     | 1.0                                                                                  | _                                | ns             |

| 202    | Host data input hold time after write data strobe deassertion  1.1 V core                                                                                                                                                                                                                                            | 1.7                                                                                  | _                                | ns             |

|        | • 1.2 V core                                                                                                                                                                                                                                                                                                         | 1.5                                                                                  | _                                | ns             |

| Notes: | <ol> <li>Attributes refers to the following signals: HCS, HA[11–29], HCID[0–4], HDST, HRW, HRDS, and HWBSn.</li> <li>This specification is tested in dual-strobe mode. Timing in single-strobe mode is guaranteed by design.</li> <li>All values listed in this table are tested or guaranteed by design.</li> </ol> |                                                                                      |                                  |                |

Figure 15 shows DSI asynchronous write signals timing.

Notes:

- 1. Used for single-strobe mode access.

- 2. Used for dual-strobe mode access.

- 3. HTA released at logic 0 (DCR[HTAAD] = 0) at end of access; used with pull-down implementation.

- 4. HTA released at logic 1 (DCR[HTAAD] = 1) at end of access; used with pull-up implementation.

Figure 15. Asynchronous Single- and Dual-Strobe Modes Write Timing Diagram

Figure 16 shows DSI asynchronous broadcast write signals timing.

Notes:

- 1. Used for single-strobe mode access.

- 2. Used for dual-strobe mode access.

Figure 16. Asynchronous Broadcast Write Timing Diagram

MSC8122 Quad Digital Signal Processor Data Sheet, Rev. 16

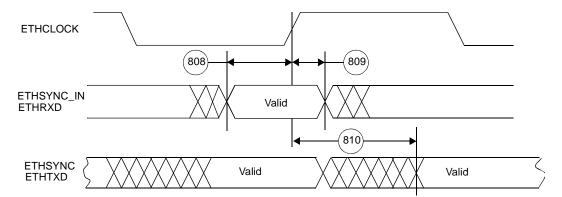

#### 2.5.10.4 SMII Mode

**Table 27. SMII Mode Signal Timing**

| No.    | Characteristics                                                                                                    | Min                                  | Max                                  | Unit     |

|--------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|----------|

| 808    | ETHSYNC_IN, ETHRXD to ETHCLOCK rising edge set-up time                                                             | 1.0                                  |                                      | ns       |

| 809    | ETHCLOCK rising edge to ETHSYNC_IN, ETHRXD hold time                                                               | 1.0                                  | _                                    | ns       |

| 810    | <ul> <li>ETHCLOCK rising edge to ETHSYNC, ETHTXD output delay</li> <li>1.1 V core.</li> <li>1.2 V core.</li> </ul> | 1.5 <sup>1</sup><br>1.5 <sup>1</sup> | 6.0 <sup>2</sup><br>5.0 <sup>2</sup> | ns<br>ns |

| Notes: | <ol> <li>Measured using a 5 pF load.</li> <li>Measured using a 15 pF load.</li> </ol>                              |                                      |                                      |          |

Figure 26. SMII Mode Signal Timing

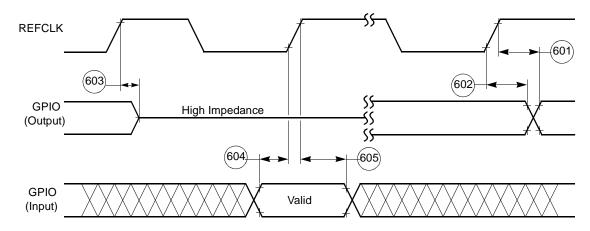

## 2.5.11 GPIO Timing

**Table 28. GPIO Timing**

| No. | Characteristics                                        | Ref = CLKIN |     | Ref = CLKOUT<br>(1.2 V only) |     | Unit |

|-----|--------------------------------------------------------|-------------|-----|------------------------------|-----|------|

|     |                                                        | Min         | Max | Min                          | Max |      |

| 601 | REFCLK edge to GPIO out valid (GPIO out delay time)    | _           | 6.1 | _                            | 6.9 | ns   |

| 602 | REFCLK edge to GPIO out not valid (GPIO out hold time) | 1.1         | _   | 1.3                          | _   | ns   |

| 603 | REFCLK edge to high impedance on GPIO out              | _           | 5.4 | _                            | 6.2 | ns   |

| 604 | GPIO in valid to REFCLK edge (GPIO in set-up time)     | 3.5         | _   | 3.7                          | _   | ns   |

| 605 | REFCLK edge to GPIO in not valid (GPIO in hold time)   | 0.5         | _   | 0.5                          | _   | ns   |

Figure 27. GPIO Timing

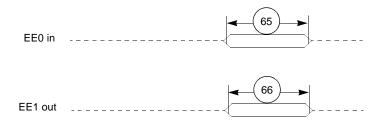

### 2.5.12 EE Signals

Table 29. EE Pin Timing

| Number | nber Characteristics Type |                           | Min                  |  |

|--------|---------------------------|---------------------------|----------------------|--|

| 65     | EE0 (input)               | Asynchronous              | 4 core clock periods |  |

| 66     | EE1 (output)              | Synchronous to Core clock | 1 core clock period  |  |

Notes: 1. The core clock is the SC140 core clock. The ratio between the core clock and CLKOUT is configured during power-on-reset.

2. Refer to **Table 1-4** on page 1-6 for details on EE pin functionality.

Figure 28 shows the signal behavior of the EE pins.

Figure 28. EE Pin Timing

### 2.5.13 JTAG Signals

**Table 30. JTAG Timing**

| No. | Characteristics                                                     | All frequencies |     | Unit |

|-----|---------------------------------------------------------------------|-----------------|-----|------|

|     |                                                                     | Min             | Max |      |

| 700 | TCK frequency of operation (1/(T <sub>C</sub> × 4); maximum 25 MHz) | 0.0             | 25  | MHz  |

| 701 | TCK cycle time                                                      | 40.0            | _   | ns   |

| 702 | TCK clock pulse width measured at V <sub>M</sub> = 1.6 V            |                 |     |      |

|     | High                                                                | 20.0            | _   | ns   |

|     | • Low                                                               | 16.0            | _   | ns   |

| 703 | TCK rise and fall times                                             | 0.0             | 3.0 | ns   |

#### ware Design Considerations

**Note:** The MSC8122 does not support DLL-enabled mode. For the following two clock schemes, ensure that the DLL is disabled (that is, the DLLDIS bit in the Hard Reset Configuration Word is set).

- If no system synchronization is required (for example, the design does not use SDRAM), you can use any of the

available clock modes.

- In the CLKIN synchronization mode, use the following connections:

- Connect the oscillator output through a buffer to CLKIN.

- Connect the CLKIN buffer output to the slave device (for example, SDRAM) making sure that the delay path between the clock buffer to the MSC8122 and the SDRAM is equal (that is, has a skew less than 100 ps).

- Valid clock modes in this scheme are: 0, 7, 15, 19, 21, 23, 28, 29, 30, and 31.

- In CLKOUT synchronization mode (for 1.2 V devices), CLKOUT is the main clock to SDRAM. Use the following connections:

- Connect the oscillator output through a buffer to CLKIN.

- Connect CLKOUT through a zero-delay buffer to the slave device (for example, SDRAM) using the following guidelines:

- The maximum delay between the slave and CLKOUT must not exceed 0.7 ns.

- The maximum load on CLKOUT must not exceed 10 pF.

- Use a zero-delay buffer with a jitter less than 0.3 ns.

- All clock modes are valid in this clock scheme.

**Note:** See the Clock chapter in the MSC8122 Reference Manual for details.

- If the 60x-compatible system bus is not used and SIUMCR[PBSE] is set, PPBS can be disconnected. Otherwise, it should be pulled up.

- The following signals: SWTE, DSISYNC, DSI64, MODCK[1–2], CNFGS, CHIPID[0–3], RSTCONF and BM[0–2] are used to configure the MSC8122 and are sampled on the deassertion of the PORESET signal. Therefore, they should be tied to GND or V<sub>DDH</sub> or through a pull-down or a pull-up resistor until the deassertion of the PORESET signal.

- When they are used, INT\_OUT (if SIUMCR[INTODC] is cleared), NMI\_OUT, and IRQxx (if not full drive) signals must be pulled up.

- When the Ethernet controller is enabled and the SMII mode is selected, GPIO10 and GPIO14 must not be connected externally to any signal line.

**Note:** For details on configuration, see the *MSC8122 User's Guide* and *MSC8122 Reference Manual*. For additional information, refer to the *MSC8122 Design Checklist* (AN2787).

#### 3.4 External SDRAM Selection

The external bus speed implemented in a system determines the speed of the SDRAM used on that bus. However, because of differences in timing characteristics among various SDRAM manufacturers, you may have use a faster speed rated SDRAM to assure efficient data transfer across the bus. For example, for 166 MHz operation, you may have to use 183 or 200 MHz SDRAM. Always perform a detailed timing analysis using the MSC8122 bus timing values and the manufacturer specifications for the SDRAM to ensure correct operation within your system design. The output delay listed in SDRAM specifications is usually given for a load of 30 pF. Scale the number to your specific board load using the typical scaling number provided by the SDRAM manufacturer.

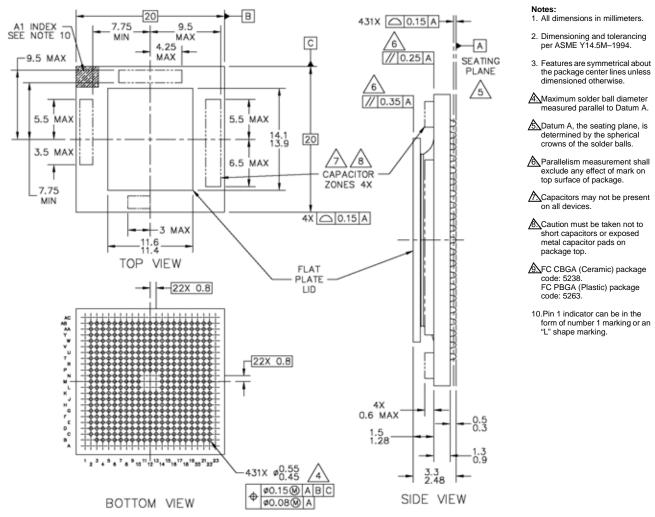

### 5 Package Information

Figure 35. MSC8122 Mechanical Information, 431-pin FC-PBGA Package

### 6 Product Documentation

- *MSC8122 Technical Data Sheet* (MSC8122). Details the signals, AC/DC characteristics, clock signal characteristics, package and pinout, and electrical design considerations of the MSC8122 device.

- *MSC8122 Reference Manual* (MSC8122RM). Includes functional descriptions of the extended cores and all the internal subsystems including configuration and programming information.

- Application Notes. Cover various programming topics related to the StarCore DSP core and the MSC8122 device.

- *SC140 DSP Core Reference Manual*. Covers the SC140 core architecture, control registers, clock registers, program control, and instruction set.