Welcome to **E-XFL.COM**

# Understanding <u>Embedded - DSP (Digital Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | SC140 Core                                                              |

| Interface               | DSI, Ethernet, RS-232                                                   |

| Clock Rate              | 400MHz                                                                  |

| Non-Volatile Memory     | External                                                                |

| On-Chip RAM             | 1.436MB                                                                 |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 1.20V                                                                   |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 431-BFBGA, FCBGA                                                        |

| Supplier Device Package | 431-FCPBGA (20x20)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmsc8122tmp6400 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

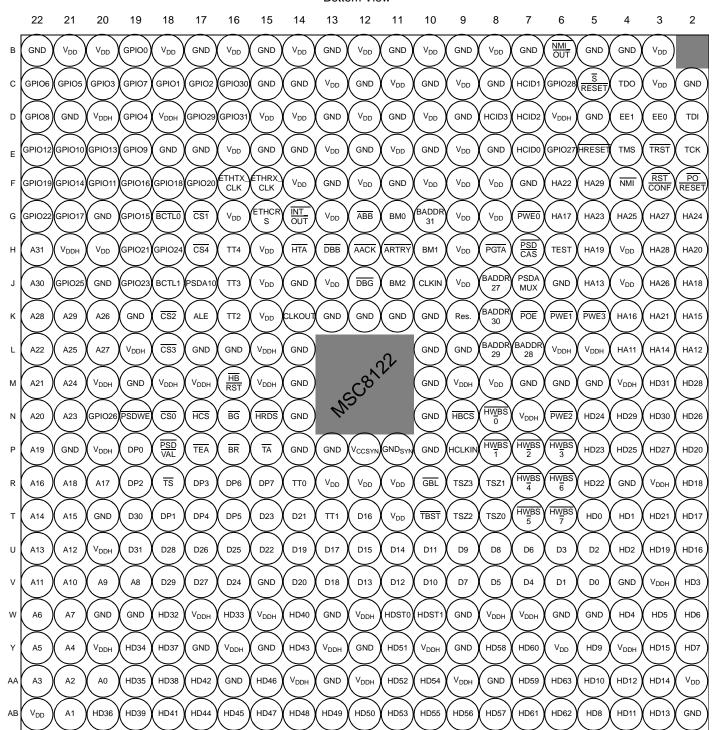

#### **Bottom View**

Figure 4. MSC8122 Package, Bottom View

# 1.2 Signal List By Ball Location

Table 1 presents signal list sorted by ball number. -

Table 1. MSC8122 Signal Listing by Ball Designator

| Des. | Signal Name                 | Des. | Signal Name                        |

|------|-----------------------------|------|------------------------------------|

| В3   | $V_{DD}$                    | C18  | GPIO1/TIMER0/CHIP_ID1/IRQ5/ETHTXD1 |

| B4   | GND                         | C19  | GPIO7/TDM3RCLK/IRQ5/ETHTXD3        |

| B5   | GND                         | C20  | GPIO3/TDM3TSYN/IRQ1/ETHTXD2        |

| В6   | NMI_OUT                     | C21  | GPIO5/TDM3TDAT/IRQ3/ETHRXD3        |

| B7   | GND                         | C22  | GPIO6/TDM3RSYN/IRQ4/ETHRXD2        |

| В8   | $V_{DD}$                    | D2   | TDI                                |

| В9   | GND                         | D3   | EE0                                |

| B10  | $V_{DD}$                    | D4   | EE1                                |

| B11  | GND                         | D5   | GND                                |

| B12  | $V_{DD}$                    | D6   | $V_{DDH}$                          |

| B13  | GND                         | D7   | HCID2                              |

| B14  | $V_{DD}$                    | D8   | HCID3/HA8                          |

| B15  | GND                         | D9   | GND                                |

| B16  | $V_{DD}$                    | D10  | $V_{DD}$                           |

| B17  | GND                         | D11  | GND                                |

| B18  | $V_{DD}$                    | D12  | $V_{DD}$                           |

| B19  | GPIO0/CHIP_ID0/IRQ4/ETHTXD0 | D13  | GND                                |

| B20  | $V_{DD}$                    | D14  | $V_{DD}$                           |

| B21  | $V_{DD}$                    | D15  | $V_{DD}$                           |

| B22  | GND                         | D16  | GPIO31/TIMER3/SCL                  |

| C2   | GND                         | D17  | GPIO29/CHIP_ID3/ETHTX_EN           |

| C3   | $V_{DD}$                    | D18  | $V_{DDH}$                          |

| C4   | TDO                         | D19  | GPIO4/TDM3TCLK/IRQ2/ETHTX_ER       |

| C5   | SRESET                      | D20  | $V_{DDH}$                          |

| C6   | GPIO28/UTXD/DREQ2           | D21  | GND                                |

| C7   | HCID1                       | D22  | GPIO8/TDM3RDAT/IRQ6/ETHCOL         |

| C8   | GND                         | E2   | TCK                                |

| C9   | $V_{DD}$                    | E3   | TRST                               |

| C10  | GND                         | E4   | TMS                                |

| C11  | $V_{DD}$                    | E5   | HRESET                             |

| C12  | GND                         | E6   | GPIO27/URXD/DREQ1                  |

| C13  | $V_{DD}$                    | E7   | HCID0                              |

| C14  | GND                         | E8   | GND                                |

| C15  | GND                         | E9   | $V_{DD}$                           |

| C16  | GPIO30/TIMER2/TMCLK/SDA     | E10  | GND                                |

| C17  | GPIO2/TIMER1/CHIP_ID2/IRQ6  | E11  | $V_{DD}$                           |

Table 1. MSC8122 Signal Listing by Ball Designator (continued)

| Des. | Signal Name             | Des. | Signal Name                               |  |

|------|-------------------------|------|-------------------------------------------|--|

| M15  | $V_{DDH}$               | P12  | V <sub>CCSYN</sub>                        |  |

| M16  | HBRST                   | P13  | GND                                       |  |

| M17  | $V_{DDH}$               | P14  | GND                                       |  |

| M18  | $V_{DDH}$               | P15  | TA                                        |  |

| M19  | GND                     | P16  | BR                                        |  |

| M20  | $V_{DDH}$               | P17  | TEA                                       |  |

| M21  | A24                     | P18  | PSDVAL                                    |  |

| M22  | A21                     | P19  | DP0/DREQ1/EXT_BR2                         |  |

| N2   | HD26                    | P20  | V <sub>DDH</sub>                          |  |

| N3   | HD30                    | P21  | GND                                       |  |

| N4   | HD29                    | P22  | A19                                       |  |

| N5   | HD24                    | R2   | HD18                                      |  |

| N6   | PWE2/PSDDQM2/PBS2       | R3   | V <sub>DDH</sub>                          |  |

| N7   | $V_{DDH}$               | R4   | GND                                       |  |

| N8   | HWBS0/HDBS0/HWBE0/HDBE0 | R5   | HD22                                      |  |

| N9   | HBCS                    | R6   | HWBS6/HDBS6/HWBE6/HDBE6/PWE6/PSDDQM6/PBS6 |  |

| N10  | GND                     | R7   | HWBS4/HDBS4/HWBE4/HDBE4/PWE4/PSDDQM4/PBS4 |  |

| N14  | GND                     | R8   | TSZ1                                      |  |

| N15  | HRDS/HRW/HRDE           | R9   | TSZ3                                      |  |

| N16  | BG                      | R10  | ĪRQ1/GBL                                  |  |

| N17  | HCS                     | R11  | V <sub>DD</sub>                           |  |

| N18  | CS0                     | R12  | V <sub>DD</sub>                           |  |

| N19  | PSDWE/PGPL1             | R13  | V <sub>DD</sub>                           |  |

| N20  | GPIO26/TDM0RDAT         | R14  | TT0/HA7                                   |  |

| N21  | A23                     | R15  | ĪRQ7/DP7/DREQ4                            |  |

| N22  | A20                     | R16  | ĪRQ6/DP6/DREQ3                            |  |

| P2   | HD20                    | R17  | ĪRQ3/DP3/DREQ2/ĒXT_BR3                    |  |

| P3   | HD27                    | R18  | TS                                        |  |

| P4   | HD25                    | R19  | IRQ2/DP2/DACK2/EXT_DBG2                   |  |

| P5   | HD23                    | R20  | A17                                       |  |

| P6   | HWBS3/HDBS3/HWBE3/HDBE3 | R21  | A18                                       |  |

| P7   | HWBS2/HDBS2/HWBE2/HDBE2 | R22  | A16                                       |  |

| P8   | HWBS1/HDBS1/HWBE1/HDBE1 | T2   | HD17                                      |  |

| P9   | HCLKIN                  | Т3   | HD21                                      |  |

| P10  | GND                     | T4   | HD1/DSISYNC                               |  |

| P11  | GND <sub>SYN</sub>      | T5   | HD0/SWTE                                  |  |

|      |                         |      |                                           |  |

Table 1. MSC8122 Signal Listing by Ball Designator (continued)

| Des. | Signal Name                               | Des. | Signal Name      |

|------|-------------------------------------------|------|------------------|

| T6   | HWBS7/HDBS7/HWBE7/HDBE7/PWE7/PSDDQM7/PBS7 | U21  | A12              |

| T7   | HWBS5/HDBS5/HWBE5/HDBE5/PWE5/PSDDQM5/PBS5 | U22  | A13              |

| T8   | TSZ0                                      | V2   | HD3/MODCK1       |

| T9   | TSZ2                                      | V3   | $V_{DDH}$        |

| T10  | TBST                                      | V4   | GND              |

| T11  | $V_{DD}$                                  | V5   | D0               |

| T12  | D16                                       | V6   | D1               |

| T13  | TT1                                       | V7   | D4               |

| T14  | D21                                       | V8   | D5               |

| T15  | D23                                       | V9   | D7               |

| T16  | IRQ5/DP5/DACK4/EXT_BG3                    | V10  | D10              |

| T17  | IRQ4/DP4/DACK3/EXT_DBG3                   | V11  | D12              |

| T18  | IRQ1/DP1/DACK1/EXT_BG2                    | V12  | D13              |

| T19  | D30                                       | V13  | D18              |

| T20  | GND                                       | V14  | D20              |

| T21  | A15                                       | V15  | GND              |

| T22  | A14                                       | V16  | D24              |

| U2   | HD16                                      | V17  | D27              |

| U3   | HD19                                      | V18  | D29              |

| U4   | HD2/DSI64                                 | V19  | A8               |

| U5   | D2                                        | V20  | A9               |

| U6   | D3                                        | V21  | A10              |

| U7   | D6                                        | V22  | A11              |

| U8   | D8                                        | W2   | HD6              |

| U9   | D9                                        | W3   | HD5/CNFGS        |

| U10  | D11                                       | W4   | HD4/MODCK2       |

| U11  | D14                                       | W5   | GND              |

| U12  | D15                                       | W6   | GND              |

| U13  | D17                                       | W7   | V <sub>DDH</sub> |

| U14  | D19                                       | W8   | V <sub>DDH</sub> |

| U15  | D22                                       | W9   | GND              |

| U16  | D25                                       | W10  | HDST1/HA10       |

| U17  | D26                                       | W11  | HDST0/HA9        |

| U18  | D28                                       | W12  | $V_{DDH}$        |

| U19  | D31                                       | W13  | GND              |

| U20  | $V_{DDH}$                                 | W14  | HD40/D40/ETHRXD0 |

# 2 Electrical Characteristics

This document contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications. For additional information, see the MSC8122 Reference Manual.

### 2.1 Maximum Ratings

#### **CAUTION**

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device with a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

**Table 2** describes the maximum electrical ratings for the MSC8122.

**Table 2. Absolute Maximum Ratings**

| Rating                                                           | Symbol           | Value       | Unit     |

|------------------------------------------------------------------|------------------|-------------|----------|

| Core and PLL supply voltage                                      | $V_{DD}$         | -0.2 to 1.6 | V        |

| I/O supply voltage                                               | V <sub>DDH</sub> | -0.2 to 4.0 | V        |

| Input voltage                                                    | V <sub>IN</sub>  | -0.2 to 4.0 | V        |

| Maximum operating temperature: • Standard range • Extended range | TJ               | 90<br>105   | °C<br>°C |

| Minimum operating temperature • Standard range • Extended range  | TJ               | 0<br>-40    | °C<br>°C |

| Storage temperature range                                        | T <sub>STG</sub> | -55 to +150 | °C       |

Notes: 1. Functional operating conditions are given in Table 3.

- 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.

- 3. Section 3.5, Thermal Considerations includes a formula for computing the chip junction temperature (T,j).

### 2.2 Recommended Operating Conditions

**Table 3** lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

**Table 3. Recommended Operating Conditions**

| Rating                                                                                      | Symbol                                | Value                                        | Unit                                   |

|---------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------|----------------------------------------|

| Core and PLL supply voltage:  • Standard  — 400 MHz  — 500 MHz  • Reduced (300 and 400 MHz) | V <sub>DD</sub><br>V <sub>CCSYN</sub> | 1.14 to 1.26<br>1.16 to 1.24<br>1.07 to 1.13 | V<br>V<br>V                            |

| I/O supply voltage                                                                          | $V_{DDH}$                             | 3.135 to 3.465                               | V                                      |

| Input voltage                                                                               | V <sub>IN</sub>                       | -0.2 to V <sub>DDH</sub> +0.2                | V                                      |

| Operating temperature range: • Standard • Extended                                          | T <sub>J</sub>                        | 0 to 90<br>–40 to 105                        | °°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°°° |

### 2.3 Thermal Characteristics

Table 4 describes thermal characteristics of the MSC8122 for the FC-PBGA packages.

Table 4. Thermal Characteristics for the MSC8122

| Charactaristic                                        | Comple at       | FC-I<br>20 × 2        | 1124                          |      |

|-------------------------------------------------------|-----------------|-----------------------|-------------------------------|------|

| Characteristic                                        | Symbol          | Natural<br>Convection | 200 ft/min<br>(1 m/s) airflow | Unit |

| Junction-to-ambient <sup>1, 2</sup>                   | $R_{	heta JA}$  | 26                    | 21                            | °C/W |

| Junction-to-ambient, four-layer board <sup>1, 3</sup> | $R_{	heta JA}$  | 19                    | 15                            | °C/W |

| Junction-to-board (bottom) <sup>4</sup>               | $R_{	heta JB}$  | 9                     |                               | °C/W |

| Junction-to-case <sup>5</sup>                         | $R_{\theta JC}$ | 0.9                   |                               | °C/W |

| Junction-to-package-top <sup>6</sup>                  | $\Psi_{JT}$     | 1                     |                               | °C/W |

#### Notes:

- Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD 51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

Section 3.5, Thermal Considerations provides a detailed explanation of these characteristics.

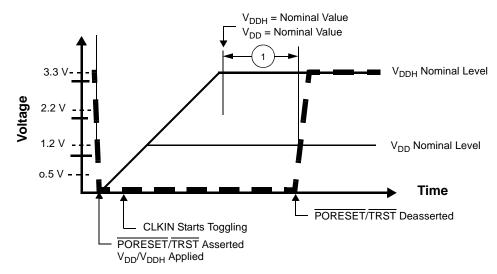

Figure 6. Start-Up Sequence:  $V_{DD}$  and  $V_{DDH}$  Raised Together

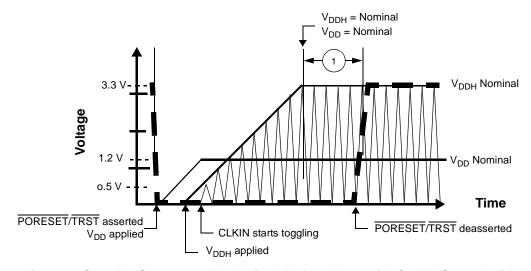

Figure 7. Start-Up Sequence:  $V_{DD}$  Raised Before  $V_{DDH}$  with CLKIN Started with  $V_{DDH}$

#### rical Characteristics

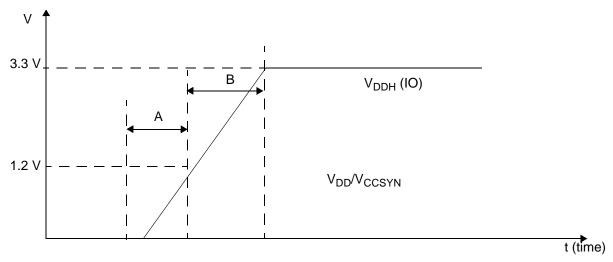

In all cases, the power-up sequence must follow the guidelines shown in **Figure 8**.

Figure 8. Power-Up Sequence for V<sub>DDH</sub> and V<sub>DD</sub>/V<sub>CCSYN</sub>

The following rules apply:

- 1. During time interval A,  $V_{DDH}$  should always be equal to or less than the  $V_{DD}/V_{CCSYN}$  voltage level. The duration of interval A should be kept below 10 ms.

- 2. The duration of timing interval B should be kept as small as possible and less than 10 ms.

### 2.5.3 Clock and Timing Signals

The following sections include a description of clock signal characteristics. **Table 7** shows the maximum frequency values for internal (Core, Reference, Bus, and DSI) and external (CLKIN and CLKOUT) clocks. The user must ensure that maximum frequency values are not exceeded.

Characteristic

Maximum in MHz

Core frequency

300/400/500

Reference frequency (REFCLK)

100/133/166

Internal bus frequency (BLCK)

100/133/166

DSI clock frequency (HCLKIN)

HCLKIN ≤ (min{70 MHz, CLKOUT})

• Core frequency = 300 MHz

HCLKIN ≤ (min{100 MHz, CLKOUT})

• Core frequency (CLKIN or CLKOUT)

100/133/166

**Table 7. Maximum Frequencies**

**Table 8. Clock Frequencies**

| Ols - I             | 300 MHz Device                                            |                                                                                                                                                       | 400 MHz Device                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                           | 500 MHz Device                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol              | Min                                                       | Max                                                                                                                                                   | Min                                                                                                                                                                                                               | Max                                                                                                                                                                                                                                                                       | Min                                                                                                                                                                                                                                                                                                                                           | Max                                                                                                                                                                                                                                                                                                                                                                                  |

| F <sub>CLKIN</sub>  | 20                                                        | 100                                                                                                                                                   | 20                                                                                                                                                                                                                | 133.3                                                                                                                                                                                                                                                                     | 20                                                                                                                                                                                                                                                                                                                                            | 166.7                                                                                                                                                                                                                                                                                                                                                                                |

| F <sub>BCLK</sub>   | 40                                                        | 100                                                                                                                                                   | 40                                                                                                                                                                                                                | 133.3                                                                                                                                                                                                                                                                     | 40                                                                                                                                                                                                                                                                                                                                            | 166.7                                                                                                                                                                                                                                                                                                                                                                                |

| F <sub>REFCLK</sub> | 40                                                        | 100                                                                                                                                                   | 40                                                                                                                                                                                                                | 133.3                                                                                                                                                                                                                                                                     | 40                                                                                                                                                                                                                                                                                                                                            | 166.7                                                                                                                                                                                                                                                                                                                                                                                |

| F <sub>CLKOUT</sub> | 40                                                        | 100                                                                                                                                                   | 40                                                                                                                                                                                                                | 133.3                                                                                                                                                                                                                                                                     | 40                                                                                                                                                                                                                                                                                                                                            | 166.7                                                                                                                                                                                                                                                                                                                                                                                |

| F <sub>CORE</sub>   | 200                                                       | 300                                                                                                                                                   | 200                                                                                                                                                                                                               | 400                                                                                                                                                                                                                                                                       | 200                                                                                                                                                                                                                                                                                                                                           | 500                                                                                                                                                                                                                                                                                                                                                                                  |

|                     | F <sub>BCLK</sub> F <sub>REFCLK</sub> F <sub>CLKOUT</sub> | Symbol           Min           F <sub>CLKIN</sub> 20           F <sub>BCLK</sub> 40           F <sub>REFCLK</sub> 40           F <sub>CLKOUT</sub> 40 | Symbol           Min         Max           F <sub>CLKIN</sub> 20         100           F <sub>BCLK</sub> 40         100           F <sub>REFCLK</sub> 40         100           F <sub>CLKOUT</sub> 40         100 | Symbol           Min         Max         Min           F <sub>CLKIN</sub> 20         100         20           F <sub>BCLK</sub> 40         100         40           F <sub>REFCLK</sub> 40         100         40           F <sub>CLKOUT</sub> 40         100         40 | Symbol           Min         Max         Min         Max           F <sub>CLKIN</sub> 20         100         20         133.3           F <sub>BCLK</sub> 40         100         40         133.3           F <sub>REFCLK</sub> 40         100         40         133.3           F <sub>CLKOUT</sub> 40         100         40         133.3 | Min         Max         Min         Max         Min           F <sub>CLKIN</sub> 20         100         20         133.3         20           F <sub>BCLK</sub> 40         100         40         133.3         40           F <sub>REFCLK</sub> 40         100         40         133.3         40           F <sub>CLKOUT</sub> 40         100         40         133.3         40 |

| Table 9. | <b>System</b> | Clock I | <b>Parameters</b> |

|----------|---------------|---------|-------------------|

|----------|---------------|---------|-------------------|

| Characteristic                                                       | Min | Max         | Unit |  |

|----------------------------------------------------------------------|-----|-------------|------|--|

| Phase jitter between BCLK and CLKIN                                  | _   | 0.3         | ns   |  |

| CLKIN frequency                                                      | 20  | see Table 8 | MHz  |  |

| CLKIN slope                                                          | _   | 3           | ns   |  |

| CLKIN period jitter <sup>1</sup>                                     | _   | 150         | ps   |  |

| CLKIN jitter spectrum                                                | 150 | _           | KHz  |  |

| PLL input clock (after predivider)                                   | 20  | 100         | MHz  |  |

| PLL output frequency (VCO output)                                    | 800 |             | MHz  |  |

| 300 MHz core                                                         |     | 1200        | MHz  |  |

| 400 MHz core                                                         |     | 1600        | MHz  |  |

| 500 MHz core                                                         |     | 2000        | MHz  |  |

| CLKOUT frequency jitter <sup>1</sup>                                 | _   | 200         | ps   |  |

| CLKOUT phase jitter <sup>1</sup> with CLKIN phase jitter of ±100 ps. | _   | 500         | ps   |  |

Not tested. Guaranteed by design.

#### 2.5.4 **Reset Timing**

The MSC8122 has several inputs to the reset logic:

- Power-on reset (PORESET)

- External hard reset (HRESET)

- External soft reset (SRESET)

- Software watchdog reset

- Bus monitor reset

- Host reset command through JTAG

All MSC8122 reset sources are fed into the reset controller, which takes different actions depending on the source of the reset. The reset status register indicates the most recent sources to cause a reset. Table 10 describes the reset sources.

**Table 10. Reset Sources**

| Name                               | Direction     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset<br>(PORESET)        | Input         | Initiates the power-on reset flow that resets the MSC8122 and configures various attributes of the MSC8122. On PORESET, the entire MSC8122 device is reset. SPLL states is reset, HRESET and SRESET are driven, the SC140 extended cores are reset, and system configuration is sampled. The clock mode (MODCK bits), reset configuration mode, boot mode, Chip ID, and use of either a DSI 64 bits port or a System Bus 64 bits port are configured only when PORESET is asserted.                                       |

| External hard reset (HRESET)       | Input/ Output | Initiates the hard reset flow that configures various attributes of the MSC8122. While HRESET is asserted, SRESET is also asserted. HRESET is an open-drain pin. Upon hard reset, HRESET and SRESET are driven, the SC140 extended cores are reset, and system configuration is sampled. The most configurable features are reconfigured. These features are defined in the 32-bit hard reset configuration word described in Hard Reset Configuration Word section of the Reset chapter in the MSC8122 Reference Manual. |

| External soft reset (SRESET)       | Input/ Output | Initiates the soft reset flow. The MSC8122 detects an external assertion of SRESET only if it occurs while the MSC8122 is not asserting reset. SRESET is an open-drain pin. Upon soft reset, SRESET is driven, the SC140 extended cores are reset, and system configuration is maintained.                                                                                                                                                                                                                                |

| Software watchdog reset            | Internal      | When the MSC8122 watchdog count reaches zero, a software watchdog reset is signalled. The enabled software watchdog event then generates an internal hard reset sequence.                                                                                                                                                                                                                                                                                                                                                 |

| Bus monitor reset                  | Internal      | When the MSC8122 bus monitor count reaches zero, a bus monitor hard reset is asserted. The enabled bus monitor event then generates an internal hard reset sequence.                                                                                                                                                                                                                                                                                                                                                      |

| Host reset command through the TAP | Internal      | When a host reset command is written through the Test Access Port (TAP), the TAP logic asserts the soft reset signal and an internal soft reset sequence is generated.                                                                                                                                                                                                                                                                                                                                                    |

MSC8122 Quad Digital Signal Processor Data Sheet, Rev. 16

**Table 11** summarizes the reset actions that occur as a result of the different reset sources.

Table 11. Reset Actions for Each Reset Source

| Reset Action/Reset Source                                                           | Power-On Reset (PORESET) | Hard Reset (HRESET)                                           | Soft     | Reset (SRESET)                              |

|-------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------|----------|---------------------------------------------|

| Reset Action/Reset Source                                                           | External only            | External or Internal<br>(Software Watchdog or<br>Bus Monitor) | External | JTAG Command:<br>EXTEST, CLAMP, or<br>HIGHZ |

| Configuration pins sampled (Refer to Section 2.5.4.1 for details).                  | Yes                      | No                                                            | No       | No                                          |

| SPLL state reset                                                                    | Yes                      | No                                                            | No       | No                                          |

| System reset configuration write through the DSI                                    | Yes                      | No                                                            | No       | No                                          |

| System reset configuration write though the system bus                              | Yes                      | Yes                                                           | No       | No                                          |

| HRESET driven                                                                       | Yes                      | Yes                                                           | No       | No                                          |

| SIU registers reset                                                                 | Yes                      | Yes                                                           | No       | No                                          |

| IPBus modules reset (TDM, UART,<br>Timers, DSI, IPBus master, GIC, HS, and<br>GPIO) | Yes                      | Yes                                                           | Yes      | Yes                                         |

| SRESET driven                                                                       | Yes                      | Yes                                                           | Yes      | Depends on command                          |

| SC140 extended cores reset                                                          | Yes                      | Yes                                                           | Yes      | Yes                                         |

| MQBS reset                                                                          | Yes                      | Yes                                                           | Yes      | Yes                                         |

# 2.5.4.1 Power-On Reset (PORESET) Pin

Asserting  $\overline{\text{PORESET}}$  initiates the power-on reset flow.  $\overline{\text{PORESET}}$  must be asserted externally for at least 16 CLKIN cycles after  $V_{DD}$  and  $V_{DDH}$  are both at their nominal levels.

### 2.5.4.2 Reset Configuration

The MSC8122 has two mechanisms for writing the reset configuration:

- Through the direct slave interface (DSI)

- Through the system bus. When the reset configuration is written through the system bus, the MSC8122 acts as a configuration master or a configuration slave. If configuration slave is selected, but no special configuration word is written, a default configuration word is applied.

Fourteen signal levels (see **Chapter 1** for signal description details) are sampled on PORESET deassertion to define the Reset Configuration Mode and boot and operating conditions:

- RSTCONF

- CNFGS

- DSISYNC

- DSI64

- CHIP\_ID[0-3]

- BM[0-2]

- SWTE

- MODCK[1–2]

21

### 2.5.4.3 Reset Timing Tables

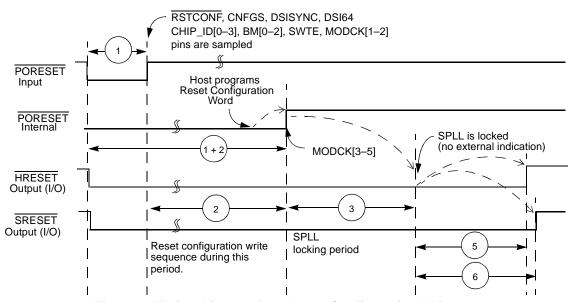

**Table 12** and **Figure 9** describe the reset timing for a reset configuration write through the direct slave interface (DSI) or through the system bus.

Table 12. Timing for a Reset Configuration Write through the DSI or System Bus

| No.   | Characteristics                                                                                                                                                                                                  | Expression                                                   | Min                     | Max                   | Unit           |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------|-----------------------|----------------|

| 1     | Required external PORESET duration minimum  CLKIN = 20 MHz  CLKIN = 100 MHz (300 MHz core)  CLKIN = 133 MHz (400 MHz core)  CLKIN = 166 MHz (500 MHz core)                                                       | 16/CLKIN                                                     | 800<br>160<br>120<br>96 |                       | ns<br>ns<br>ns |

| 2     | Delay from deassertion of external PORESET to deassertion of internal PORESET  • CLKIN = 20 MHz to 166 MHz                                                                                                       | 1024/CLKIN                                                   | 6.17                    | 51.2                  | μs             |

| 3     | Delay from de-assertion of internal PORESET to SPLL lock  CLKIN = 20 MHz (RDF = 1)  CLKIN = 100 MHz (RDF = 1) (300 MHz core)  CLKIN = 133 MHz (RDF = 2) (400 MHz core)  CLKIN = 166 MHz (RDF = 2) (500 MHz core) | 6400/(CLKIN/RDF)<br>(PLL reference<br>clock-division factor) | 320<br>64<br>96<br>77   | 320<br>64<br>96<br>77 | hs<br>hs<br>hs |

| 5     | Delay from SPLL to HRESET deassertion • REFCLK = 40 MHz to 166 MHz                                                                                                                                               | 512/REFCLK                                                   | 3.08                    | 12.8                  | μs             |

| 6     | Delay from SPLL lock to SRESET deassertion • REFCLK = 40 MHz to 166 MHz                                                                                                                                          | 515/REFCLK                                                   | 3.10                    | 12.88                 | μs             |

| 7     | Setup time from assertion of RSTCONF, CNFGS, DSISYNC, DSI64, CHIP_ID[0–3], BM[0–2], SWTE, and MODCK[1–2] before deassertion of PORESET                                                                           |                                                              | 3                       |                       | ns             |

| 8     | Hold time from deassertion of PORESET to deassertion of RSTCONF, CNFGS, DSISYNC, DSI64, CHIP_ID[0–3], BM[0–2], SWTE, and MODCK[1–2]                                                                              |                                                              | 5                       |                       | ns             |

| Note: | Timings are not tested, but are guaranteed by design.                                                                                                                                                            |                                                              |                         |                       |                |

Figure 9. Timing Diagram for a Reset Configuration Write

#### **Table 15. AC Timing for SIU Outputs**

| No.             |                                                                                                                                                   | V           | alue for    | Bus Spe    | ed in MHz <sup>3</sup>  |          |              |   |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------------|-------------------------|----------|--------------|---|--|

|                 |                                                                                                                                                   | R           | Ref = CLKIN |            | Ref = CLKIN Ref = CLKOU |          | Ref = CLKOUT | т |  |

|                 | Characteristic                                                                                                                                    | 1.1 V       | 1.2 V       | 1.2 V      | 1.2 V                   | Units    |              |   |  |

|                 |                                                                                                                                                   | 100/<br>133 | 133         | 166        | 100/133                 |          |              |   |  |

| 30 <sup>2</sup> | Minimum delay from the 50% level of the REFCLK for all signals                                                                                    | 0.9         | 0.8         | 0.8        | 1.0                     | ns       |              |   |  |

| 31              | PSDVAL/TEA/TA max delay from the 50% level of the REFCLK rising edge                                                                              | 6.0         | 4.9         | 4.9        | 5.8                     | ns       |              |   |  |

| 32a             | Address bus max delay from the 50% level of the REFCLK rising edge  • Multi-master mode (SIUBCR[EBM] = 1)  • Single-master mode (SIUBCR[EBM] = 0) | 6.4<br>5.3  | 5.5<br>4.2  | 5.5<br>3.9 | 6.4<br>5.1              | ns<br>ns |              |   |  |

| 32b             | Address attributes: TT[0–1]/TBST/TSZ/GBL max delay from the 50% level of the REFCLK rising edge                                                   | 6.4         | 5.1         | 5.1        | 6.0                     | ns       |              |   |  |

| 32c             | Address attributes: TT[2–4]/TC max delay from the 50% level of the REFCLK rising edge                                                             | 6.9         | 5.7         | 5.7        | 6.6                     | ns       |              |   |  |

| 32d             | BADDR max delay from the 50% level of the REFCLK rising edge                                                                                      | 5.2         | 4.2         | 4.2        | 5.1                     | ns       |              |   |  |

| 33a             | Data bus max delay from the 50% level of the REFCLK rising edge  • Data-pipeline mode  • Non-pipeline mode                                        | 4.8<br>7.1  | 3.9<br>6.1  | 3.7<br>6.1 | 4.8<br>7.0              | ns<br>ns |              |   |  |

| 33b             | DP max delay from the 50% level of the REFCLK rising edge     Data-pipeline mode     Non-pipeline mode                                            | 6.0<br>7.5  | 5.3<br>6.5  | 5.3<br>6.5 | 6.2<br>7.4              | ns<br>ns |              |   |  |

| 34              | Memory controller signals/ALE/CS[0–4] max delay from the 50% level of the REFCLK rising edge                                                      | 5.1         | 4.2         | 3.9        | 5.1                     | ns       |              |   |  |

| 35a             | DBG/BG/BR/DBB max delay from the 50% level of the REFCLK rising edge                                                                              | 6.0         | 4.7         | 4.7        | 5.6                     | ns       |              |   |  |

| 35b             | AACK/ABB/TS/CS[5–7] max delay from the 50% level of the REFCLK rising edge                                                                        | 5.5         | 4.5         | 4.5        | 5.4                     | ns       |              |   |  |

#### Notes:

- 1. Values are measured from the 50% level of the REFCLK rising edge to the 50% signal level and assume a 20 pF load except where otherwise specified.

- 2. Except for specification 30, which is specified for a 10 pF load, all timings in this table are specified for a 20 pF load. Decreasing the load results in a timing decrease at the rate of 0.3 ns per 5 pF decrease in load. Increasing the load results in a timing increase at the rate of 0.15 ns per 5 pF increase in load.

- 3. The maximum bus frequency depends on the mode:

- In 60x-compatible mode connected to another MSC8122 device, the frequency is determined by adding the input and output longest timing values, which results in the total delay for 20 pF output capacitance. You must also account for other influences that can affect timing, such as on-board clock skews, on-board noise delays, and so on.

- In single-master mode, the frequency depends on the timing of the devices connected to the MSC8122.

- To achieve maximum performance on the bus in single-master mode, disable the DBB signal by writing a 1 to the SIUMCR[BDD] bit. See the SIU chapter in the MSC8122 Reference Manual for details.

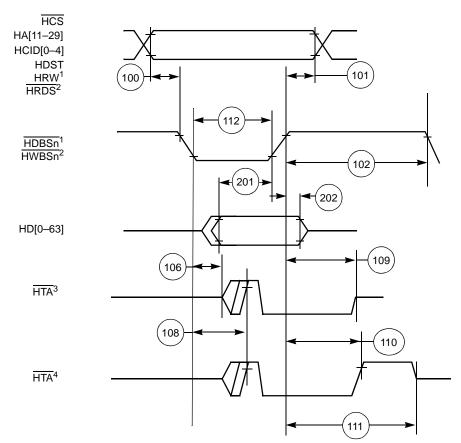

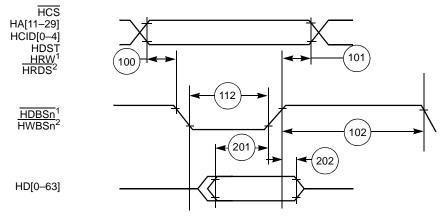

### 2.5.6 DSI Timing

The timings in the following sections are based on a 20 pF capacitive load.

# 2.5.6.1 DSI Asynchronous Mode

**Table 18. DSI Asynchronous Mode Timing**

| No.    | Characteristics                                                                                                              | Min                                                                                  | Max                              | Unit           |  |

|--------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------|----------------|--|

| 100    | Attributes <sup>1</sup> set-up time before strobe (HWBS[n]) assertion                                                        | 1.5                                                                                  | _                                | ns             |  |

| 101    | Attributes <sup>1</sup> hold time after data strobe deassertion                                                              | 1.3                                                                                  | _                                | ns             |  |

| 102    | Read/Write data strobe deassertion width:  • DCR[HTAAD] = 1                                                                  |                                                                                      | _                                |                |  |

|        | Consecutive access to the same DSI     Different device with DCR[HTADT] = 01  Different device with DCR[HTADT] = 40          | 1.8 + T <sub>REFCLK</sub><br>5 + T <sub>REFCLK</sub>                                 |                                  | ns<br>ns       |  |

|        | Different device with DCR[HTADT] = 10     Different device with DCR[HTADT] = 11     DCR[HTAAD] = 0                           | $5 + (1.5 \times T_{REFCLK})$<br>$5 + (2.5 \times T_{REFCLK})$<br>$1.8 + T_{REFCLK}$ |                                  | ns<br>ns<br>ns |  |

| 103    | Read data strobe deassertion to output data high impedance                                                                   | —                                                                                    | 8.5                              | ns             |  |

| 104    | Read data strobe assertion to output data active from high impedance                                                         | 2.0                                                                                  | _                                | ns             |  |

| 105    | Output data hold time after read data strobe deassertion                                                                     | 2.2                                                                                  | _                                | ns             |  |

| 106    | Read/Write data strobe assertion to HTA active from high impedance                                                           | 2.2                                                                                  | _                                | ns             |  |

| 107    | Output data valid to HTA assertion                                                                                           | 3.2                                                                                  | _                                | ns             |  |

| 108    | Read/Write data strobe assertion to HTA valid <sup>2</sup> 1.1 V core                                                        | _                                                                                    | 7.4                              | ns             |  |

|        | • 1.2 V core                                                                                                                 | _                                                                                    | 6.7                              | ns             |  |

| 109    | Read/Write data strobe deassertion to output HTA high impedance.  (DCR[HTAAD] = 0, HTA at end of access released at logic 0) | _                                                                                    | 6.5                              | ns             |  |

| 110    | Read/Write data strobe deassertion to output HTA deassertion.  (DCR[HTAAD] = 1, HTA at end of access released at logic 1)    | _                                                                                    | 6.5                              | ns             |  |

| 111    | Read/Write data strobe deassertion to output HTA high impedance.  (DCR[HTAAD] = 1, HTA at end of access released at logic 1  | _                                                                                    |                                  |                |  |

|        | DCR[HTADT] = 01                                                                                                              |                                                                                      | 5 + T <sub>REFCLK</sub>          | ns             |  |

|        | DCR[HTADT] = 10     DCR[HTADT] = 11                                                                                          |                                                                                      | 5 + (1.5 × T <sub>REFCLK</sub> ) | ns             |  |

| 112    | DCR[HTADT] = 11  Read/Write data strobe assertion width                                                                      | 1.8 + T <sub>REFCLK</sub>                                                            | 5 + (2.5 × T <sub>REFCLK</sub> ) | ns<br>ns       |  |

|        |                                                                                                                              |                                                                                      | _                                |                |  |

| 201    | Host data input set-up time before write data strobe deassertion                                                             | 1.0                                                                                  | _                                | ns             |  |

| 202    | Host data input hold time after write data strobe deassertion  1.1 V core                                                    | 1.7                                                                                  |                                  | ns             |  |

|        | • 1.2 V core                                                                                                                 | 1.7                                                                                  | _                                | ns             |  |

| Notes: | <u> </u>                                                                                                                     |                                                                                      |                                  |                |  |

Figure 15 shows DSI asynchronous write signals timing.

Notes:

- 1. Used for single-strobe mode access.

- 2. Used for dual-strobe mode access.

- 3. HTA released at logic 0 (DCR[HTAAD] = 0) at end of access; used with pull-down implementation.

- 4. HTA released at logic 1 (DCR[HTAAD] = 1) at end of access; used with pull-up implementation.

Figure 15. Asynchronous Single- and Dual-Strobe Modes Write Timing Diagram

Figure 16 shows DSI asynchronous broadcast write signals timing.

Notes:

- 1. Used for single-strobe mode access.

- 2. Used for dual-strobe mode access.

Figure 16. Asynchronous Broadcast Write Timing Diagram

MSC8122 Quad Digital Signal Processor Data Sheet, Rev. 16

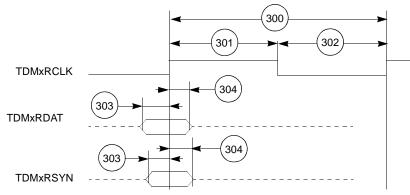

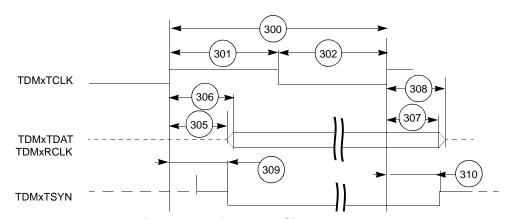

# 2.5.7 TDM Timing

**Table 21. TDM Timing**

| No. | Characteristic                                                          | Expression                | 1.1 V | Core | 1.2 V | I.2 V Core | Units  |

|-----|-------------------------------------------------------------------------|---------------------------|-------|------|-------|------------|--------|

| NO. | Characteristic                                                          | Expression                | Min   | Max  | Min   | Max        | Uiills |

| 300 | TDMxRCLK/TDMxTCLK                                                       | TC <sup>1</sup>           | 16    | _    | 16    | _          | ns     |

| 301 | TDMxRCLK/TDMxTCLK high pulse width                                      | $(0.5 \pm 0.1) \times TC$ | 7     | _    | 7     | _          | ns     |

| 302 | TDMxRCLK/TDMxTCLK low pulse width                                       | $(0.5\pm0.1)\times TC$    | 7     | _    | 7     | _          | ns     |

| 303 | TDM receive all input set-up time                                       |                           | 1.3   | _    | 1.3   | _          | ns     |

| 304 | TDM receive all input hold time                                         |                           | 1.0   | _    | 1.0   | _          | ns     |

| 305 | TDMxTCLK high to TDMxTDAT/TDMxRCLK output active <sup>2,3</sup>         |                           | 2.8   | _    | 2.8   | _          | ns     |

| 306 | TDMxTCLK high to TDMxTDAT/TDMxRCLK output                               |                           | _     | 10.0 | _     | 8.8        | ns     |

| 307 | All output hold time <sup>4</sup>                                       |                           | 2.5   | _    | 2.5   | _          | ns     |

| 308 | TDMxTCLK high to TDmXTDAT/TDMxRCLK output high impedance <sup>2,3</sup> |                           | _     | 10.7 | _     | 10.5       | ns     |

| 309 | TDMxTCLK high to TDMXTSYN output valid <sup>2</sup>                     |                           | _     | 9.7  | _     | 8.5        | ns     |

| 310 | TDMxTSYN output hold time <sup>4</sup>                                  |                           | 2.5   |      | 2.5   |            | ns     |

Notes:

- 1. Values are based on a a maximum frequency of 62.5 MHz. The TDM interface supports any frequency below 62.5 MHz. Devices operating at 300 MHz are limited to a maximum TDMxRCLK/TDMxTCLK frequency of 50 MHz.

- 2. Values are based on 20 pF capacitive load.

- 3. When configured as an output, TDMxRCLK acts as a second data link. See the MSC8122 Reference Manual for details.

- 4. Values are based on 10 pF capacitive load.

Figure 18. TDM Inputs Signals

Figure 19. TDM Output Signals

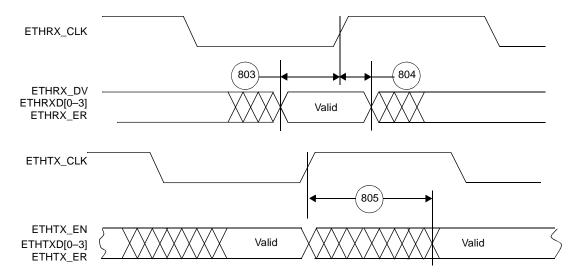

# 2.5.10.2 MII Mode Timing

**Table 25. MII Mode Signal Timing**

| No. | Characteristics                                                      |     | Max  | Unit |

|-----|----------------------------------------------------------------------|-----|------|------|

| 803 | ETHRX_DV, ETHRXD[0-3], ETHRX_ER to ETHRX_CLK rising edge set-up time | 3.5 | _    | ns   |

| 804 | ETHRX_CLK rising edge to ETHRX_DV, ETHRXD[0–3], ETHRX_ER hold time   | 3.5 | _    | ns   |

| 805 | ETHTX_CLK to ETHTX_EN, ETHTXD[0-3], ETHTX_ER output delay            |     |      |      |

|     | • 1.1 V core                                                         | 1   | 14.6 | ns   |

|     | 1.2 V core                                                           | 1   | 12.6 | ns   |

Figure 24. MII Mode Signal Timing

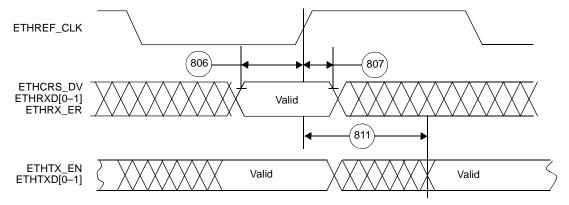

### 2.5.10.3 RMII Mode

**Table 26. RMII Mode Signal Timing**

| No. | Characteristics                                                                 | 1.1 V Core     |      | 1.2 V Core |    | Unit |

|-----|---------------------------------------------------------------------------------|----------------|------|------------|----|------|

|     | Cital acteristics                                                               | Min Max Min Ma |      | Max        |    |      |

| 806 | ETHTX_EN,ETHRXD[0-1], ETHCRS_DV, ETHRX_ER to ETHREF_CLK rising edge set-up time | 1.6            |      | 2          |    | ns   |

| 807 | ETHREF_CLK rising edge to ETHRXD[0–1], ETHCRS_DV, ETHRX_ER hold time            | 1.6            | _    | 1.6        | _  | ns   |

| 811 | ETHREF_CLK rising edge to ETHTXD[0-1], ETHTX_EN output delay.                   | 3              | 12.5 | 3          | 11 | ns   |

Figure 25. RMII Mode Signal Timing

MSC8122 Quad Digital Signal Processor Data Sheet, Rev. 16

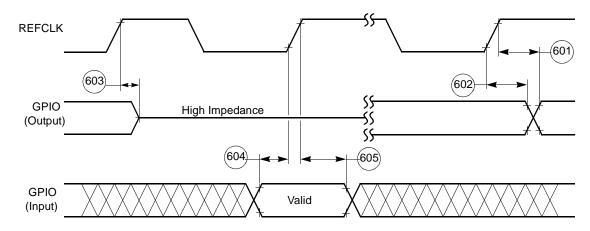

Figure 27. GPIO Timing

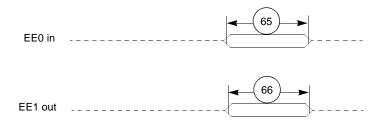

# 2.5.12 EE Signals

Table 29. EE Pin Timing

| Number | Characteristics | Type Min                               |                     |

|--------|-----------------|----------------------------------------|---------------------|

| 65     | EE0 (input)     | out) Asynchronous 4 core clock periods |                     |

| 66     | EE1 (output)    | Synchronous to Core clock              | 1 core clock period |

Notes: 1. The core clock is the SC140 core clock. The ratio between the core clock and CLKOUT is configured during power-on-reset.

2. Refer to **Table 1-4** on page 1-6 for details on EE pin functionality.

Figure 28 shows the signal behavior of the EE pins.

Figure 28. EE Pin Timing

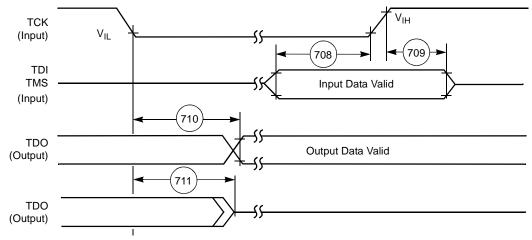

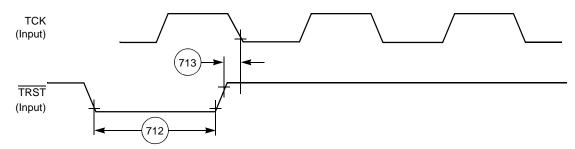

# 2.5.13 JTAG Signals

**Table 30. JTAG Timing**

| No. | Characteristics                                                     |         | All frequencies |     |

|-----|---------------------------------------------------------------------|---------|-----------------|-----|

|     |                                                                     | Min Max |                 |     |

| 700 | TCK frequency of operation (1/(T <sub>C</sub> × 4); maximum 25 MHz) | 0.0     | 25              | MHz |

| 701 | TCK cycle time                                                      | 40.0    | _               | ns  |

| 702 | TCK clock pulse width measured at V <sub>M</sub> = 1.6 V            |         |                 |     |

|     | High                                                                | 20.0    | _               | ns  |

|     | • Low                                                               | 16.0    | _               | ns  |

| 703 | TCK rise and fall times                                             | 0.0     | 3.0             | ns  |

Figure 31. Test Access Port Timing Diagram

Figure 32. TRST Timing Diagram

# 3 Hardware Design Considerations

The following sections discuss areas to consider when the MSC8122 device is designed into a system.

### 3.1 Start-up Sequencing Recommendations

Use the following guidelines for start-up and power-down sequences:

- Assert PORESET and TRST before applying power and keep the signals driven low until the power reaches the required minimum power levels. This can be implemented via weak pull-down resistors.

- CLKIN can be held low or allowed to toggle during the beginning of the power-up sequence. However, CLKIN must start toggling before the deassertion of PORESET and after both power supplies have reached nominal voltage levels.

- If possible, bring up V<sub>DD</sub>/V<sub>CCSYN</sub> and V<sub>DDH</sub> together. If it is not possible, raise V<sub>DD</sub>/V<sub>CCSYN</sub> first and then bring up V<sub>DDH</sub>. V<sub>DDH</sub> should not exceed V<sub>DD</sub>/V<sub>CCSYN</sub> until V<sub>DD</sub>/V<sub>CCSYN</sub> reaches its nominal voltage level. Similarly, bring both voltage levels down together. If that is not possible reverse the power-up sequence, with V<sub>DDH</sub> going down first and then V<sub>DD</sub>/V<sub>CCSYN</sub>.

**Note:** This recommended power sequencing for the MSC8122 is different from the MSC8102. See **Section 2.5.2** for start-up timing specifications.

External voltage applied to any input line must not exceed the I/O supply  $V_{DDH}$  by more than 0.8 V at any time, including during power-up. Some designs require pull-up voltages applied to selected input lines during power-up for configuration purposes. This is an acceptable exception to the rule. However, each such input can draw up to 80 mA per input pin per device in the system during start-up.

During the power-up sequence, if  $V_{DD}$  rises before  $V_{DDH}$  (see **Figure 6**), current can pass from the  $V_{DD}$  supply through the device ESD protection circuits to the  $V_{DDH}$  supply. The ESD protection diode can allow this to occur when  $V_{DD}$  exceeds  $V_{DDH}$  by more than 0.8 V. Design the power supply to prevent or minimize this effect using one of the following optional methods:

#### ware Design Considerations

- Never allow V<sub>DD</sub> to exceed V<sub>DDH</sub> + 0.8V.

- Design the  $V_{DDH}$  supply to prevent reverse current flow by adding a minimum  $10~\Omega$  resistor to GND to limit the current. Such a design yields an initial  $V_{DDH}$  level of  $V_{DD}-0.8~V$  before it is enabled.

After power-up, V<sub>DDH</sub> must not exceed V<sub>DD</sub>/V<sub>CCSYN</sub> by more than 2.6 V.

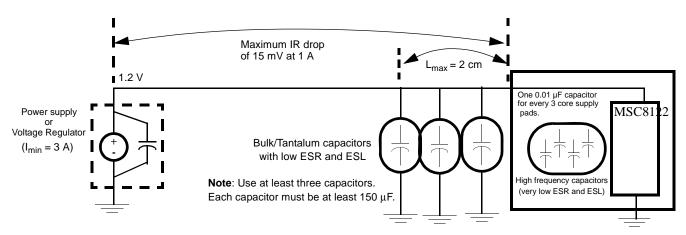

## 3.2 Power Supply Design Considerations

When used as a drop-in replacement in MSC8102 applications or when implementing a new design, use the guidelines described in *Migrating Designs from the MSC8102 to the MSC8122* (AN2716) and the *MSC8122 Design Checklist* (AN3374 for optimal system performance. *MSC8122 and MSC8126 Power Circuit Design Recommendations and Examples* (AN2937) provides detailed design information. See **Section 2.5.2** for start-up timing specifications.

**Figure 33** shows the recommended power decoupling circuit for the core power supply. The voltage regulator and the decoupling capacitors should supply the required device current without any drop in voltage on the device pins. The voltage on the package pins should not drop below the minimum specified voltage level even for a very short spikes. This can be achieved by using the following guidelines:

- For the core supply, use a voltage regulator rated at 1.2 V with nominal rating of at least 3 A. This rating does not reflect actual average current draw, but is recommended because it resists changes imposed by transient spikes and has better voltage recovery time than supplies with lower current ratings.

- Decouple the supply using low-ESR capacitors mounted as close as possible to the socket. **Figure 33** shows three capacitors in parallel to reduce the resistance. Three capacitors is a recommended minimum number. If possible, mount at least one of the capacitors directly below the MSC8122 device.

Figure 33. Core Power Supply Decoupling

Each  $V_{CC}$  and  $V_{DD}$  pin on the MSC8122 device should have a low-impedance path to the board power supply. Similarly, each GND pin should have a low-impedance path to the ground plane. The power supply pins drive distinct groups of logic on the chip. The  $V_{CC}$  power supply should have at least four 0.1  $\mu$ F by-pass capacitors to ground located as closely as possible to the four sides of the package. The capacitor leads and associated printed circuit traces connecting to chip  $V_{CC}$ ,  $V_{DD}$ , and GND should be kept to less than half an inch per capacitor lead. A four-layer board is recommended, employing two inner layers as  $V_{CC}$  and GND planes.

All output pins on the MSC8122 have fast rise and fall times. PCB trace interconnection length should be minimized to minimize undershoot and reflections caused by these fast output switching times. This recommendation particularly applies to the address and data buses. Maximum PCB trace lengths of six inches are recommended. For the DSI control signals in synchronous mode, ensure that the layout supports the DSI AC timing requirements and minimizes any signal crosstalk. Capacitance calculations should consider all device loads as well as parasitic capacitances due to the PCB traces. Attention to proper PCB layout and bypassing becomes especially critical in systems with higher capacitive loads because these loads create higher transient currents in the V<sub>CC</sub>, V<sub>DD</sub>, and GND circuits. Pull up all unused inputs or signals that will be inputs during reset.

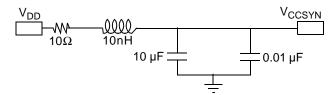

Special care should be taken to minimize the noise levels on the PLL supply pins. There is one pair of PLL supply pins:  $V_{CCSYN}$ -GND<sub>SYN</sub>. To ensure internal clock stability, filter the power to the  $V_{CCSYN}$  input with a circuit similar to the one in

41

Figure 34. For optimal noise filtering, place the circuit as close as possible to  $V_{CCSYN}$ . The 0.01-μF capacitor should be closest to  $V_{CCSYN}$ , followed by the 10-μF capacitor, the 10-nH inductor, and finally the 10-Ω resistor to  $V_{DD}$ . These traces should be kept short and direct. Provide an extremely low impedance path to the ground plane for  $GND_{SYN}$ . Bypass  $GND_{SYN}$  to  $V_{CCSYN}$  by a 0.01-μF capacitor located as close as possible to the chip package. For best results, place this capacitor on the backside of the PCB aligned with the depopulated void on the MSC8122 located in the square defined by positions, L11, L12, L13, M11, M12, M13, N11, N12, and N13.

Figure 34. V<sub>CCSYN</sub> Bypass

# 3.3 Connectivity Guidelines

Unused output pins can be disconnected, and unused input pins should be connected to the non-active value, via resistors to  $V_{DDH}$  or GND, except for the following:

- If the DSI is unused (DDR[DSIDIS] is set), HCS and HBCS must pulled up and all the rest of the DSI signals can be disconnected.

- When the DSI uses synchronous mode, HTA must be pulled up. In asynchronous mode, HTA should be pulled either up or down, depending on design requirements.

- HDST can be disconnected if the DSI is in big-endian mode, or if the DSI is in little-endian mode and the DCR[DSRFA] bit is set.

- When the DSI is in 64-bit data bus mode and DCR[BEM] is cleared, pull up HWBS[1-3]/HDBS[1-3]/HWBE[1-3]/HDBE[1-3]/HDBE[1-3] and HWBS[4-7]/HDBS[4-7]/HDBE[4-7]/HDBE[4-7]/PSDDQM[4-7]/PBS[4-7].

- When the DSI is in 32-bit data bus mode and DCR[BEM] is cleared, HWBS[1-3]/HDBS[1-3]/HDBE[1-3]/HDBE[1-3] must be pulled up.

- When the DSI is in asynchronous mode, HBRST and HCLKIN should either be disconnected or pulled up.

- When the DSI uses sliding window address mode (DCR[SLDWA] = 1), the external HA[11–13] signals must be connected (tied) to the correct voltage levels so that the host can perform the first access to the DCR. After reset, the DSI expects full address mode (DCR[SLDWA] = 0). The DCR address in the DSI memory map is 0x1BE000, which requires the following connections:

- HA11 must be pulled high (1)

- HA12 must be pulled high (1)

- HA13 must be pulled low (0)

- The following signals must be pulled up: HRESET, SRESET, ARTRY, TA, TEA, PSDVAL, and AACK.

- In single-master mode (BCR[EBM] = 0) with internal arbitration (PPC ACR[EARB] = 0):

- $\overline{BG}$ ,  $\overline{DBG}$ , and  $\overline{TS}$  can be left unconnected.

- EXT\_BG[2-3], EXT\_DBG[2-3], and GBL can be left unconnected if they are multiplexed to the system bus functionality. For any other functionality, connect the signal lines based on the multiplexed functionality.

- BR must be pulled up.

- EXT\_BR[2–3] must be pulled up if multiplexed to the system bus functionality.

- If there is an external bus master (BCR[EBM] = 1):

- $\overline{BR}$ ,  $\overline{BG}$ ,  $\overline{DBG}$ , and  $\overline{TS}$  must be pulled up.

- EXT\_BR[2-3], EXT\_BG[2-3], and EXT\_DBG[2-3] must be pulled up if multiplexed to the system bus functionality.

- In single-master mode,  $\overline{ABB}$  and  $\overline{DBB}$  can be selected as  $\overline{IRQ}$  inputs and be connected to the non-active value. In other modes, they must be pulled up.