# E·XFL

#### NXP USA Inc. - MSC8122TMP6400 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Details                 |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Obsolete                                                               |

| Туре                    | SC140 Core                                                             |

| Interface               | DSI, Ethernet, RS-232                                                  |

| Clock Rate              | 400MHz                                                                 |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 1.436MB                                                                |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.20V                                                                  |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                     |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 431-BFBGA, FCBGA                                                       |

| Supplier Device Package | 431-FCPBGA (20x20)                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8122tmp6400 |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Pin A  | ssignments4                         |

|---|--------|-------------------------------------|

|   | 1.1    | FC-PBGA Ball Layout Diagrams4       |

|   | 1.2    | Signal List By Ball Location7       |

| 2 | Electi | rical Characteristics               |

|   | 2.1    | Maximum Ratings                     |

|   | 2.2    | Recommended Operating Conditions    |

|   | 2.3    | Thermal Characteristics14           |

|   | 2.4    | DC Electrical Characteristics       |

|   | 2.5    | AC Timings                          |

| 3 | Hard   | ware Design Considerations          |

|   | 3.1    | Start-up Sequencing Recommendations |

|   | 3.2    | Power Supply Design Considerations  |

|   | 3.3    | Connectivity Guidelines41           |

|   | 3.4    | External SDRAM Selection            |

|   | 3.5    | Thermal Considerations43            |

| 4 | Order  | ring Information43                  |

| 5 | Packa  | age Information                     |

| 6 | Produ  | act Documentation                   |

| 7 | Revis  | ion History                         |

|   |        |                                     |

### List of Figures

| Figure 1. | MSC8122 Block Diagram                                                            |

|-----------|----------------------------------------------------------------------------------|

| Figure 2. | StarCore SC140 DSP Extended Core Block Diagram 3                                 |

| Figure 3. | MSC8122 Package, Top View 5                                                      |

| Figure 4. | MSC8122 Package, Bottom View 6                                                   |

| Figure 5. | Overshoot/Undershoot Voltage for $V_{\text{IH}}$ and $V_{\text{IL}}, \ldots, 16$ |

| Figure 6. | Start-Up Sequence: $V_{DD}$ and $V_{DDH}$ Raised Together 17                     |

| Figure 7. | Start-Up Sequence: V <sub>DD</sub> Raised Before V <sub>DDH</sub> with CLKIN     |

|           | Started with V <sub>DDH</sub> 17                                                 |

| Figure 8. | Power-Up Sequence for $V_{DDH}$ and $V_{DD}/V_{CCSYN}$ 18                        |

| Figure 9. | Timing Diagram for a Reset Configuration Write 21                                |

| Figure 10.Internal Tick Spacing for Memory Controller Signals 22 |

|------------------------------------------------------------------|

| Figure 11.SIU Timing Diagram                                     |

| Figure 12.CLKOUT and CLKIN Signals                               |

| Figure 13.DMA Signals                                            |

| Figure 14.Asynchronous Single- and Dual-Strobe Modes Read        |

| Timing Diagram                                                   |

| Figure 15.Asynchronous Single- and Dual-Strobe Modes Write       |

| Timing Diagram                                                   |

| Figure 16.Asynchronous Broadcast Write Timing Diagram            |

| Figure 17.DSI Synchronous Mode Signals Timing Diagram 31         |

| Figure 18.TDM Inputs Signals                                     |

| Figure 19.TDM Output Signals                                     |

| Figure 20.UART Input Timing                                      |

| Figure 21.UART Output Timing                                     |

| Figure 22.Timer Timing                                           |

| Figure 23.MDIO Timing Relationship to MDC                        |

| Figure 24.MII Mode Signal Timing                                 |

| Figure 25.RMII Mode Signal Timing                                |

| Figure 26.SMII Mode Signal Timing                                |

| Figure 27.GPIO Timing                                            |

| Figure 28.EE Pin Timing                                          |

| Figure 29.Test Clock Input Timing Diagram                        |

| Figure 30.Boundary Scan (JTAG) Timing Diagram                    |

| Figure 31.Test Access Port Timing Diagram                        |

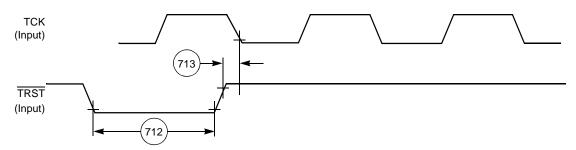

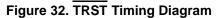

| Figure 32.TRST Timing Diagram                                    |

| Figure 33.Core Power Supply Decoupling                           |

| Figure 34.V <sub>CCSYN</sub> Bypass                              |

| Figure 35.MSC8122 Mechanical Information, 431-pin FC-PBGA        |

| Package                                                          |

ssignments

# 1 Pin Assignments

This section includes diagrams of the MSC8122 package ball grid array layouts and pinout allocation tables.

# 1.1 FC-PBGA Ball Layout Diagrams

Top and bottom views of the FC-PBGA package are shown in Figure 3 and Figure 4 with their ball location index numbers.

MSC8122 Quad Digital Signal Processor Data Sheet, Rev. 16

| Des. | Signal Name           | Des. | Signal Name      |

|------|-----------------------|------|------------------|

| H21  | V <sub>DDH</sub>      | K15  | V <sub>DD</sub>  |

| H22  | A31                   | K16  | TT2/CS5          |

| J2   | HA18                  | K17  | ALE              |

| J3   | HA26                  | K18  | CS2              |

| J4   | V <sub>DD</sub>       | K19  | GND              |

| J5   | HA13                  | K20  | A26              |

| J6   | GND                   | K21  | A29              |

| J7   | PSDAMUX/PGPL5         | K22  | A28              |

| J8   | BADDR27               | L2   | HA12             |

| J9   | V <sub>DD</sub>       | L3   | HA14             |

| J10  | CLKIN                 | L4   | HA11             |

| J11  | BM2/TC2/BNKSEL2       | L5   | V <sub>DDH</sub> |

| J12  | DBG                   | L6   | V <sub>DDH</sub> |

| J13  | V <sub>DD</sub>       | L7   | BADDR28          |

| J14  | GND                   | L8   | IRQ5/BADDR29     |

| J15  | V <sub>DD</sub>       | L9   | GND              |

| J16  | TT3/CS6               | L10  | GND              |

| J17  | PSDA10/PGPL0          | L14  | GND              |

| J18  | BCTL1/CS5             | L15  | V <sub>DDH</sub> |

| J19  | GPIO23/TDM0TDAT/IRQ13 | L16  | GND              |

| J20  | GND                   | L17  | GND              |

| J21  | GPIO25/TDM0RCLK/IRQ15 | L18  | CS3              |

| J22  | A30                   | L19  | V <sub>DDH</sub> |

| K2   | HA15                  | L20  | A27              |

| K3   | HA21                  | L21  | A25              |

| K4   | HA16                  | L22  | A22              |

| K5   | PWE3/PSDDQM3/PBS3     | M2   | HD28             |

| K6   | PWE1/PSDDQM1/PBS1     | M3   | HD31             |

| K7   | POE/PSDRAS/PGPL2      | M4   | V <sub>DDH</sub> |

| K8   | IRQ2/BADDR30          | M5   | GND              |

| K9   | Reserved              | M6   | GND              |

| K10  | GND                   | M7   | GND              |

| K11  | GND                   | M8   | V <sub>DD</sub>  |

| K12  | GND                   | M9   | V <sub>DDH</sub> |

| K13  | GND                   | M10  | GND              |

| K14  | CLKOUT                | M14  | GND              |

### Table 1. MSC8122 Signal Listing by Ball Designator (continued)

Signal Name Signal Name Des. Des. M15 P12 V<sub>DDH</sub> V<sub>CCSYN</sub> M16 HBRST P13 GND M17 V<sub>DDH</sub> P14 GND TA M18 P15 V<sub>DDH</sub> BR GND M19 P16 TEA M20 V<sub>DDH</sub> P17 PSDVAL P18 M21 A24 DP0/DREQ1/EXT\_BR2 M22 A21 P19 N2 HD26 P20 V<sub>DDH</sub> GND HD30 P21 N3 N4 HD29 P22 A19 N5 HD24 R2 HD18 PWE2/PSDDQM2/PBS2 N6 R3 V<sub>DDH</sub> N7 VDDH R4 GND HWBS0/HDBS0/HWBE0/HDBE0 R5 HD22 N8 HBCS HWBS6/HDBS6/HWBE6/HDBE6/PWE6/PSDDQM6/PBS6 R6 N9 GND HWBS4/HDBS4/HWBE4/HDBE4/PWE4/PSDDQM4/PBS4 N10 R7 GND N14 R8 TSZ1 HRDS/HRW/HRDE N15 R9 TSZ3 BG IRQ1/GBL N16 R10 HCS N17 R11 V<sub>DD</sub> N18 CS0 R12  $V_{DD}$ PSDWE/PGPL1 N19 R13 V<sub>DD</sub> N20 GPIO26/TDM0RDAT R14 TT0/HA7 IRQ7/DP7/DREQ4 N21 A23 R15 IRQ6/DP6/DREQ3 N22 A20 R16 IRQ3/DP3/DREQ2/EXT\_BR3 P2 HD20 R17 TS P3 HD27 R18 IRQ2/DP2/DACK2/EXT\_DBG2 P4 HD25 R19 Ρ5 HD23 R20 A17 HWBS3/HDBS3/HWBE3/HDBE3 P6 R21 A18 HWBS2/HDBS2/HWBE2/HDBE2 R22 A16 P7 HWBS1/HDBS1/HWBE1/HDBE1 T2 HD17 P8 Ρ9 HCLKIN HD21 T3 P10 GND Τ4 HD1/DSISYNC P11 **GND**<sub>SYN</sub> T5 HD0/SWTE

#### Table 1. MSC8122 Signal Listing by Ball Designator (continued)

Signal Name Signal Name Des. Des. W15 AA9  $V_{DDH}$ V<sub>DDH</sub> W16 HD33/D33/reserved AA10 HD54/D54/ETHTX\_EN W17 VDDH AA11 HD52/D52 W18 HD32/D32/reserved AA12 V<sub>DDH</sub> GND W19 GND AA13 W20 GND AA14 VDDH W21 A7 AA15 HD46/D46/ETHTXT0 W22 A6 AA16 GND HD42/D42/ETHRXD2/reserved Y2 HD7 AA17 HD15 AA18 Y3 HD38/D38/reserved Y4 AA19 HD35/D35/reserved V<sub>DDH</sub> Y5 HD9 AA20 A0 Y6  $\mathsf{V}_\mathsf{DD}$ AA21 A2 Y7 HD60/D60/ETHCOL/reserved AA22 A3 HD58/D58/ETHMDC GND Y8 AB2 Y9 GND AB3 HD13 Y10 AB4 HD11 V<sub>DDH</sub> HD51/D51 Y11 AB5 HD8 Y12 GND AB6 HD62/D62 HD61/D61 Y13 AB7 VDDH HD43/D43/ETHRXD3/reserved Y14 AB8 HD57/D57/ETHRX\_ER Y15 GND AB9 HD56/D56/ETHRX\_DV/ETHCRS\_DV Y16  $V_{\text{DDH}}$ AB10 HD55/D55/ETHTX\_ER/reserved Y17 GND AB11 HD53/D53 Y18 HD37/D37/reserved AB12 HD50/D50 Y19 HD34/D34/reserved AB13 HD49/D49/ETHTXD3/reserved Y20 AB14 HD48/D48/ETHTXD2/reserved V<sub>DDH</sub> Y21 A4 AB15 HD47/D47/ETHTXD1 Y22 A5 AB16 HD45/D45 AA2 AB17 HD44/D44  $V_{DD}$ AA3 HD14 AB18 HD41/D41/ETHRXD1 AA4 HD12 AB19 HD39/D39/reserved AA5 HD10 AB20 HD36/D36/reserved AA6 HD63/D63 AB21 A1 HD59/D59/ETHMDIO AB22 AA7  $V_{DD}$ AA8 GND

#### Table 1. MSC8122 Signal Listing by Ball Designator (continued)

rical Characteristics

### 2.2 Recommended Operating Conditions

Table 3 lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Rating                                                                                              | Symbol                                | Value                                        | Unit        |

|-----------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------|-------------|

| Core and PLL supply voltage:<br>• Standard<br>— 400 MHz<br>— 500 MHz<br>• Reduced (300 and 400 MHz) | V <sub>DD</sub><br>V <sub>CCSYN</sub> | 1.14 to 1.26<br>1.16 to 1.24<br>1.07 to 1.13 | V<br>V<br>V |

| I/O supply voltage                                                                                  | V <sub>DDH</sub>                      | 3.135 to 3.465                               | V           |

| Input voltage                                                                                       | V <sub>IN</sub>                       | –0.2 to V <sub>DDH</sub> +0.2                | V           |

| Operating temperature range:<br>• Standard<br>• Extended                                            | T <sub>J</sub><br>TJ                  | 0 to 90<br>–40 to 105                        | ℃<br>℃      |

Table 3. Recommended Operating Conditions

# 2.3 Thermal Characteristics

Table 4 describes thermal characteristics of the MSC8122 for the FC-PBGA packages.

|                                                       |                                                                                                                                                                                                                                                                                                                                                               |                                                                                          | FC-<br>20 ×                                                      | Unit                                                  |            |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------|------------|

| Characteristic                                        |                                                                                                                                                                                                                                                                                                                                                               | Symbol                                                                                   | Natural<br>Convection                                            | 200 ft/min<br>(1 m/s) airflow                         | Unit       |

| Junction-to-a                                         | imbient <sup>1, 2</sup>                                                                                                                                                                                                                                                                                                                                       | R <sub>eJA</sub>                                                                         | 26                                                               | 21                                                    | °C/W       |

| Junction-to-ambient, four-layer board <sup>1, 3</sup> |                                                                                                                                                                                                                                                                                                                                                               | R <sub>θJA</sub>                                                                         | 19                                                               | 15                                                    | °C/W       |

| Junction-to-b                                         | ooard (bottom) <sup>4</sup>                                                                                                                                                                                                                                                                                                                                   | R <sub>θJB</sub>                                                                         | 9                                                                |                                                       | °C/W       |

| Junction-to-case <sup>5</sup>                         |                                                                                                                                                                                                                                                                                                                                                               | R <sub>θJC</sub>                                                                         | 0.9                                                              |                                                       | °C/W       |

| Junction-to-package-top <sup>6</sup>                  |                                                                                                                                                                                                                                                                                                                                                               | Ψ <sub>JT</sub>                                                                          | 1                                                                |                                                       | °C/W       |

| Notes: 1.<br>2.<br>3.<br>4.<br>5.                     | Junction temperature is a function of die size<br>temperature, ambient temperature, air flow, p<br>resistance.<br>Per SEMI G38-87 and JEDEC JESD51-2 wit<br>Per JEDEC JESD51-6 with the board horizon<br>Thermal resistance between the die and the<br>the top surface of the board near the packag<br>Thermal resistance between the die and the<br>1012.1). | bower dissipation of o<br>h the single layer boo<br>htal.<br>printed circuit board<br>e. | other components on th<br>ard horizontal.<br>per JEDEC JESD 51-8 | e board, and board therm<br>. Board temperature is me | easured on |

Thermal characterization parameter indicating the temperature difference between package top and the junction temperature

Table 4. Thermal Characteristics for the MSC8122

Section 3.5, *Thermal Considerations* provides a detailed explanation of these characteristics.

6.

per JEDEC JESD51-2.

**Electrical Characteristics**

#### **DC Electrical Characteristics** 2.4

This section describes the DC electrical characteristics for the MSC8122. The measurements in **Table 5** assume the following system conditions:

- ٠  $T_A = 25 \ ^\circ C$

- $V_{DD} =$ ٠

- 300/400 MHz 1.1 V nominal = 1.07–1.13 V<sub>DC</sub>

- 400 MHz 1.2 V nominal = 1.14–1.26 V<sub>DC</sub>

- 500 MHz 1.2 V nominal = 1.16–1.24 V<sub>DC</sub>

- $V_{DDH} = 3.3 \text{ V} \pm 5\% \text{ V}_{DC}$ ٠

- $GND = 0 V_{DC}$

Note: The leakage current is measured for nominal  $V_{DDH}$  and  $V_{DD}$ .

| Characteristic                                                            | Symbol                               | Min  | Typical                              | Max   | Unit     |

|---------------------------------------------------------------------------|--------------------------------------|------|--------------------------------------|-------|----------|

| Input high voltage <sup>1</sup> , all inputs except CLKIN                 | V <sub>IH</sub>                      | 2.0  | _                                    | 3.465 | V        |

| Input low voltage <sup>1</sup>                                            | V <sub>IL</sub>                      | GND  | 0                                    | 0.8   | V        |

| CLKIN input high voltage                                                  | V <sub>IHC</sub>                     | 2.4  | 3.0                                  | 3.465 | V        |

| CLKIN input low voltage                                                   | V <sub>ILC</sub>                     | GND  | 0                                    | 0.8   | V        |

| Input leakage current, V <sub>IN</sub> = V <sub>DDH</sub>                 | I <sub>IN</sub>                      | -1.0 | 0.09                                 | 1     | μA       |

| Tri-state (high impedance off state) leakage current, $V_{IN} = V_{DDH}$  | I <sub>OZ</sub>                      | -1.0 | 0.09                                 | 1     | μA       |

| Signal low input current, $V_{IL} = 0.8 V^2$                              | ۱ <sub>L</sub>                       | -1.0 | 0.09                                 | 1     | μA       |

| Signal high input current, $V_{IH} = 2.0 V^2$                             | I <sub>H</sub>                       | -1.0 | 0.09                                 | 1     | μA       |

| Output high voltage, I <sub>OH</sub> = -2 mA,<br>except open drain pins   | V <sub>OH</sub>                      | 2.0  | 3.0                                  | —     | V        |

| Output low voltage, I <sub>OL</sub> = 3.2 mA                              | V <sub>OL</sub>                      | —    | 0                                    | 0.4   | V        |

| V <sub>CCSYN</sub> PLL supply current                                     | IVCCSYN                              | _    | 2                                    | 4     | mA       |

| Internal supply current: <ul> <li>Wait mode</li> <li>Stop mode</li> </ul> | I <sub>DDW</sub><br>I <sub>DDS</sub> |      | 375 <sup>3</sup><br>290 <sup>3</sup> |       | mA<br>mA |

| Typical power 400 MHz at 1.2 V <sup>4</sup>                               | Р                                    | _    | 1.15                                 |       | W        |

e 5 for undershoot and overshoot voltages. igur

2. Not tested. Guaranteed by design.

Measured for 1.2 V core at 25°C junction temperature. 3.

The typical power values were measured using an EFR code with the device running at a junction temperature of 25°C. No 4. peripherals were enabled and the ICache was not enabled. The source code was optimized to use all the ALUs and AGUs and all four cores. It was created using CodeWarrior<sup>®</sup> 2.5. These values are provided as examples only. Power consumption is application dependent and varies widely. To assure proper board design with regard to thermal dissipation and maintaining proper operating temperatures, evaluate power consumption for your application and use the design guidelines in Chapter 4 of this document and in MSC8102, MSC8122, and MSC8126 Thermal Management Design Guidelines (AN2601).

### 2.5.4.3 Reset Timing Tables

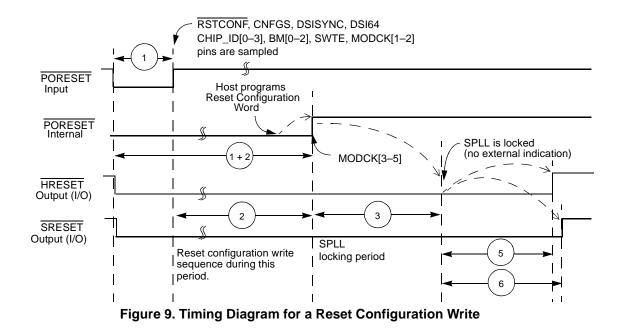

Table 12 and Figure 9 describe the reset timing for a reset configuration write through the direct slave interface (DSI) or through the system bus.

| No.   | Characteristics                                                                                                                                                                                                                                             | Expression                                                   | Min                     | Max                   | Unit                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------|-----------------------|----------------------|

| 1     | Required external PORESET duration minimum<br>• CLKIN = 20 MHz<br>• CLKIN = 100 MHz (300 MHz core)<br>• CLKIN = 133 MHz (400 MHz core)<br>• CLKIN = 166 MHz (500 MHz core)                                                                                  | 16/CLKIN                                                     | 800<br>160<br>120<br>96 |                       | ns<br>ns<br>ns<br>ns |

| 2     | Delay from deassertion of external PORESET to deassertion of internal<br>PORESET<br>• CLKIN = 20 MHz to 166 MHz                                                                                                                                             | 1024/CLKIN                                                   | 6.17                    | 51.2                  | μs                   |

| 3     | Delay from de-assertion of internal PORESET to SPLL lock <ul> <li>CLKIN = 20 MHz (RDF = 1)</li> <li>CLKIN = 100 MHz (RDF = 1) (300 MHz core)</li> <li>CLKIN = 133 MHz (RDF = 2) (400 MHz core)</li> <li>CLKIN = 166 MHz (RDF = 2) (500 MHz core)</li> </ul> | 6400/(CLKIN/RDF)<br>(PLL reference<br>clock-division factor) | 320<br>64<br>96<br>77   | 320<br>64<br>96<br>77 | hs<br>hs<br>hs       |

| 5     | Delay from SPLL to HRESET deassertion <ul> <li>REFCLK = 40 MHz to 166 MHz</li> </ul>                                                                                                                                                                        | 512/REFCLK                                                   | 3.08                    | 12.8                  | μs                   |

| 6     | Delay from SPLL lock to SRESET deassertion <ul> <li>REFCLK = 40 MHz to 166 MHz</li> </ul>                                                                                                                                                                   | 515/REFCLK                                                   | 3.10                    | 12.88                 | μs                   |

| 7     | Setup time from assertion of RSTCONF, CNFGS, DSISYNC, DSI64,<br>CHIP_ID[0–3], BM[0–2], SWTE, and MODCK[1–2] before deassertion of<br>PORESET                                                                                                                |                                                              | 3                       | _                     | ns                   |

| 8     | Hold time from deassertion of PORESET to deassertion of RSTCONF,<br>CNFGS, DSISYNC, DSI64, CHIP_ID[0–3], BM[0–2], SWTE, and<br>MODCK[1–2]                                                                                                                   |                                                              | 5                       | —                     | ns                   |

| Note: | Timings are not tested, but are guaranteed by design.                                                                                                                                                                                                       |                                                              | •                       | •                     | •                    |

Table 12. Timing for a Reset Configuration Write through the DSI or System Bus

MSC8122 Quad Digital Signal Processor Data Sheet, Rev. 16

#### rical Characteristics

#### System Bus Access Timing 2.5.5

#### **Core Data Transfers** 2.5.5.1

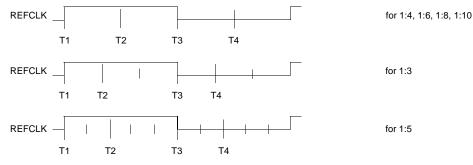

Generally, all MSC8122 bus and system output signals are driven from the rising edge of the reference clock (REFCLK). The REFCLK is the CLKIN signal. Memory controller signals, however, trigger on four points within a REFCLK cycle. Each cycle is divided by four internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge of REFCLK (and T3 at the falling edge), but the spacing of T2 and T4 depends on the PLL clock ratio selected, as Table 13 shows.

|                     | Tick Spacing (T1 Occurs at the Rising Edge of RE |            |             |  |  |  |

|---------------------|--------------------------------------------------|------------|-------------|--|--|--|

| BCLK/SC140 clock    | T2                                               | Т3         | T4          |  |  |  |

| 1:4, 1:6, 1:8, 1:10 | 1/4 REFCLK                                       | 1/2 REFCLK | 3/4 REFCLK  |  |  |  |

| 1:3                 | 1/6 REFCLK                                       | 1/2 REFCLK | 4/6 REFCLK  |  |  |  |

| 1:5                 | 2/10 REFCLK                                      | 1/2 REFCLK | 7/10 REFCLK |  |  |  |

#### Table 13. Tick Spacing for Memory Controller Signals

Figure 10 is a graphical representation of Table 13.

Figure 10. Internal Tick Spacing for Memory Controller Signals

The UPM machine and GPCM machine outputs change on the internal tick selected by the memory controller configuration. The AC timing specifications are relative to the internal tick. SDRAM machine outputs change only on the REFCLK rising edge.

|                 |                                                                                                                                                                                                | \                            | /alue for                    | Bus Spe                      | ed in MHz                 |          |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|---------------------------|----------|

|                 |                                                                                                                                                                                                | R                            | ef = CLK                     | IN                           | Ref = CLKOUT              |          |

| No.             | Characteristic                                                                                                                                                                                 | 1.1 V                        | 1.2 V                        | 1.2 V                        | 1.2 V                     | Units    |

|                 |                                                                                                                                                                                                | 100/<br>133                  | 133                          | 166                          | 133                       |          |

| 10              | Hold time for all signals after the 50% level of the REFCLK rising edge                                                                                                                        | 0.5                          | 0.5                          | 0.5                          | 0.5                       | ns       |

| 11a             | ARTRY/ABB set-up time before the 50% level of the REFCLK rising edge                                                                                                                           | 3.1                          | 3.0                          | 3.0                          | 3.0                       | ns       |

| 11b             | DBG/DBB/BG/BR/TC set-up time before the 50% level of the REFCLK rising edge                                                                                                                    | 3.6                          | 3.3                          | 3.3                          | 3.3                       | ns       |

| 11c             | AACK set-up time before the 50% level of the REFCLK rising edge                                                                                                                                | 3.0                          | 2.9                          | 2.9                          | 2.9                       | ns       |

| 11d             | TA/TEA/PSDVAL set-up time before the 50% level of the REFCLK rising edge                                                                                                                       |                              |                              |                              |                           |          |

|                 | <ul><li>Data-pipeline mode</li><li>Non-pipeline mode</li></ul>                                                                                                                                 | 3.5<br>4.4                   | 3.4<br>4.0                   | 3.4<br>4.0                   | 3.4<br>4.0                | ns<br>ns |

| 12              | Data bus set-up time before REFCLK rising edge in Normal mode <ul> <li>Data-pipeline mode</li> <li>Non-pipeline mode</li> </ul>                                                                | 1.9<br>4.2                   | 1.8<br>4.0                   | 1.7<br>4.0                   | 1.8<br>4.0                | ns<br>ns |

| 13 <sup>1</sup> | Data bus set-up time before the 50% level of the REFCLK rising edge<br>in ECC and PARITY modes<br>• Data-pipeline mode<br>• Non-pipeline mode                                                  | 2.0<br>8.2                   | 2.0<br>7.3                   | 2.0<br>7.3                   | 2.0<br>7.3                | ns<br>ns |

| 14 <sup>1</sup> | DP set-up time before the 50% level of the REFCLK rising edge <ul> <li>Data-pipeline mode</li> <li>Non-pipeline mode</li> </ul>                                                                | 2.0<br>7.9                   | 2.0<br>6.1                   | 2.0<br>6.1                   | 2.0<br>6.1                | ns<br>ns |

| 15a             | <ul> <li>TS and Address bus set-up time before the 50% level of the REFCLK rising edge</li> <li>Extra cycle mode (SIUBCR[EXDD] = 0)</li> <li>No extra cycle mode (SIUBCR[EXDD] = 1)</li> </ul> | 4.2<br>5.5                   | 3.8<br>5.0                   | 3.8<br>5.0                   | 3.8<br>5.0                | ns<br>ns |

| 15b             | Address attributes: TT/TBST/TSZ/GBL set-up time before the 50%<br>level of the REFCLK rising edge<br>• Extra cycle mode (SIUBCR[EXDD] = 0)<br>• No extra cycle mode (SIUBCR[EXDD] = 1)         | 3.7<br>4.8                   | 3.5<br>4.4                   | 3.5<br>4.4                   | 3.5<br>4.4                | ns<br>ns |

| 16              | PUPMWAIT signal set-up time before the 50% level of the REFCLK rising edge                                                                                                                     | 3.7                          | 3.7                          | 3.7                          | 3.7                       | ns       |

| 17              | IRQx setup time before the 50% level; of the REFCLK rising edge <sup>3</sup>                                                                                                                   | 4.0                          | 4.0                          | 4.0                          | 4.0                       | ns       |

| 18              | IRQx minimum pulse width <sup>3</sup>                                                                                                                                                          | 6.0 +<br>T <sub>REFCLK</sub> | 6.0 +<br>T <sub>REFCLK</sub> | 6.0 +<br>T <sub>REFCLK</sub> | 6.0 + T <sub>REFCLK</sub> | ns       |

| Notes:          | <ol> <li>Timings specifications 13 and 14 in non-pipeline mode are more r</li> <li>Values are measured from the 50% TTL transition level relative to</li> <li>Guaranteed by design.</li> </ol> | restrictive                  | than MSC                     | 8102 timin                   | gs.                       |          |

### Table 14. AC Timing for SIU Inputs

|                 |                                                                                                                                                                                   |             | alue for   | Bus Spe    | ed in MHz <sup>3</sup> |          |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|------------|------------------------|----------|

|                 | Characteristic                                                                                                                                                                    | Ref = CLKIN |            |            | Ref = CLKOUT           |          |

| No.             |                                                                                                                                                                                   | 1.1 V       | 1.2 V      | 1.2 V      | 1.2 V                  | Units    |

|                 |                                                                                                                                                                                   | 100/<br>133 | 133        | 166        | 100/133                |          |

| 30 <sup>2</sup> | Minimum delay from the 50% level of the REFCLK for all signals                                                                                                                    | 0.9         | 0.8        | 0.8        | 1.0                    | ns       |

| 31              | PSDVAL/TEA/TA max delay from the 50% level of the REFCLK rising edge                                                                                                              | 6.0         | 4.9        | 4.9        | 5.8                    | ns       |

| 32a             | <ul> <li>Address bus max delay from the 50% level of the REFCLK rising edge</li> <li>Multi-master mode (SIUBCR[EBM] = 1)</li> <li>Single-master mode (SIUBCR[EBM] = 0)</li> </ul> | 6.4<br>5.3  | 5.5<br>4.2 | 5.5<br>3.9 | 6.4<br>5.1             | ns<br>ns |

| 32b             | Address attributes: TT[0–1]/TBST/TSZ/GBL max delay from the 50% level of the REFCLK rising edge                                                                                   | 6.4         | 5.1        | 5.1        | 6.0                    | ns       |

| 32c             | Address attributes: TT[2–4]/TC max delay from the 50% level of the REFCLK rising edge                                                                                             | 6.9         | 5.7        | 5.7        | 6.6                    | ns       |

| 32d             | BADDR max delay from the 50% level of the REFCLK rising edge                                                                                                                      | 5.2         | 4.2        | 4.2        | 5.1                    | ns       |

| 33a             | <ul><li>Data bus max delay from the 50% level of the REFCLK rising edge</li><li>Data-pipeline mode</li><li>Non-pipeline mode</li></ul>                                            | 4.8<br>7.1  | 3.9<br>6.1 | 3.7<br>6.1 | 4.8<br>7.0             | ns<br>ns |

| 33b             | <ul><li>DP max delay from the 50% level of the REFCLK rising edge</li><li>Data-pipeline mode</li><li>Non-pipeline mode</li></ul>                                                  | 6.0<br>7.5  | 5.3<br>6.5 | 5.3<br>6.5 | 6.2<br>7.4             | ns<br>ns |

| 34              | Memory controller signals/ALE/CS[0–4] max delay from the 50% level of the REFCLK rising edge                                                                                      | 5.1         | 4.2        | 3.9        | 5.1                    | ns       |

| 35a             | DBG/BG/BR/DBB max delay from the 50% level of the REFCLK rising edge                                                                                                              | 6.0         | 4.7        | 4.7        | 5.6                    | ns       |

| 35b             | AACK/ABB/TS/CS[5–7] max delay from the 50% level of the REFCLK rising edge                                                                                                        | 5.5         | 4.5        | 4.5        | 5.4                    | ns       |

Decreasing the load results in a timing decrease at the rate of 0.3 ns per 5 pF decrease in load. Increasing the load results in

• In 60x-compatible mode connected to another MSC8122 device, the frequency is determined by adding the input and output longest timing values, which results in the total delay for 20 pF output capacitance. You must also account for other

• To achieve maximum performance on the bus in single-master mode, disable the DBB signal by writing a 1 to the

influences that can affect timing, such as on-board clock skews, on-board noise delays, and so on.

In single-master mode, the frequency depends on the timing of the devices connected to the MSC8122.

SIUMCR[BDD] bit. See the SIU chapter in the MSC8122 Reference Manual for details.

a timing increase at the rate of 0.15 ns per 5 pF increase in load.

The maximum bus frequency depends on the mode:

#### Table 15. AC Timing for SIU Outputs

3.

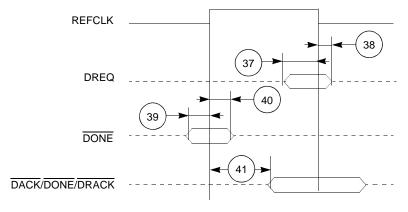

### 2.5.5.3 DMA Data Transfers

Table 17 describes the DMA signal timing.

| No. | Characteristic                                                      | Ref = | CLKIN | Ref = C<br>(1.2 V | Units |    |

|-----|---------------------------------------------------------------------|-------|-------|-------------------|-------|----|

|     |                                                                     | Min   | Max   | Min               | Max   |    |

| 37  | DREQ set-up time before the 50% level of the falling edge of REFCLK | 5.0   | —     | 5.0               | —     | ns |

| 38  | DREQ hold time after the 50% level of the falling edge of REFCLK    | 0.5   | _     | 0.5               | —     | ns |

| 39  | DONE set-up time before the 50% level of the rising edge of REFCLK  | 5.0   | _     | 5.0               | —     | ns |

| 40  | DONE hold time after the 50% level of the rising edge of REFCLK     | 0.5   | _     | 0.5               | —     | ns |

| 41  | DACK/DRACK/DONE delay after the 50% level of the REFCLK rising edge | 0.5   | 7.5   | 0.5               | 8.4   | ns |

#### Table 17. DMA Signals

The DREQ signal is synchronized with REFCLK. To achieve fast response, a synchronized peripheral should assert DREQ according to the timings in **Table 17**. Figure 13 shows synchronous peripheral interaction.

Figure 13. DMA Signals

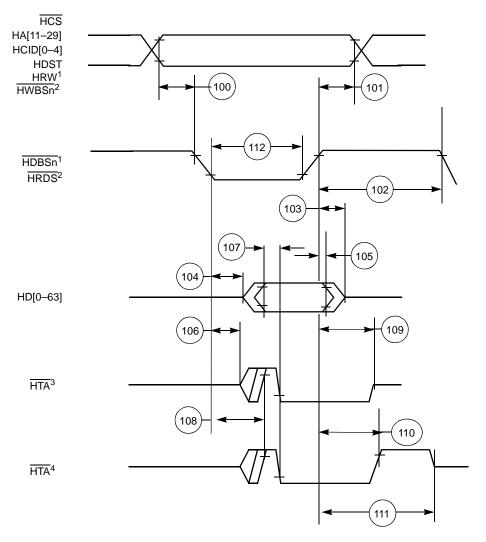

### 2.5.6 DSI Timing

The timings in the following sections are based on a 20 pF capacitive load.

### 2.5.6.1 DSI Asynchronous Mode

| Table 1 | 8. | DSI | Asv         | vnchi    | ronous | Mode | Timing |

|---------|----|-----|-------------|----------|--------|------|--------|

|         | υ. | 201 | <b>A</b> 3) | y 110111 | Unous  | mouc | 1 mmg  |

| No.    | Characteristics                                                                                                                                                                                          | Min                                                            | Max                                     | Unit     |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------|----------|--|--|

| 100    | Attributes <sup>1</sup> set-up time before strobe (HWBS[n]) assertion                                                                                                                                    | 1.5                                                            | —                                       | ns       |  |  |

| 101    | Attributes <sup>1</sup> hold time after data strobe deassertion                                                                                                                                          | 1.3                                                            | —                                       | ns       |  |  |

| 102    | Read/Write data strobe deassertion width:<br>• DCR[HTAAD] = 1                                                                                                                                            |                                                                |                                         |          |  |  |

|        | — Consecutive access to the same DSI     — Different device with DCR[HTADT] = 01                                                                                                                         | 1.8 + T <sub>REFCLK</sub><br>5 + T <sub>REFCLK</sub>           |                                         | ns<br>ns |  |  |

|        | <ul> <li>Different device with DCR[HTADT] = 10</li> <li>Different device with DCR[HTADT] = 11</li> </ul>                                                                                                 | $5 + (1.5 \times T_{REFCLK})$<br>$5 + (2.5 \times T_{REFCLK})$ |                                         | ns<br>ns |  |  |

|        | <ul> <li>DCR[HTAAD] = 0</li> </ul>                                                                                                                                                                       | $1.8 + T_{REFCLK}$                                             |                                         | ns       |  |  |

| 103    | Read data strobe deassertion to output data high impedance                                                                                                                                               | —                                                              | 8.5                                     | ns       |  |  |

| 104    | Read data strobe assertion to output data active from high impedance                                                                                                                                     | 2.0                                                            | _                                       | ns       |  |  |

| 105    | Output data hold time after read data strobe deassertion                                                                                                                                                 | 2.2                                                            | _                                       | ns       |  |  |

| 106    | Read/Write data strobe assertion to HTA active from high impedance                                                                                                                                       | 2.2                                                            | _                                       | ns       |  |  |

| 107    | Output data valid to HTA assertion                                                                                                                                                                       | 3.2                                                            | —                                       | ns       |  |  |

| 108    | Read/Write data strobe assertion to HTA valid <sup>2</sup> <ul> <li>1.1 V core</li> </ul>                                                                                                                | _                                                              | 7.4                                     | ns       |  |  |

|        | • 1.2 V core                                                                                                                                                                                             | _                                                              | 6.7                                     | ns       |  |  |

| 109    | Read/Write data strobe deassertion to output $\overline{HTA}$ high impedance.<br>(DCR[HTAAD] = 0, $\overline{HTA}$ at end of access released at logic 0)                                                 | -                                                              | 6.5                                     | ns       |  |  |

| 110    | Read/Write data strobe deassertion to output HTA deassertion.<br>(DCR[HTAAD] = 1, HTA at end of access released at logic 1)                                                                              | -                                                              | 6.5                                     | ns       |  |  |

| 111    | Read/Write data strobe deassertion to output HTA high impedance.<br>(DCR[HTAAD] = 1, HTA at end of access released at logic 1                                                                            | -                                                              |                                         |          |  |  |

|        | • DCR[HTADT] = 01                                                                                                                                                                                        |                                                                | 5 + T <sub>REFCLK</sub>                 | ns       |  |  |

|        | DCR[HTADT] = 10                                                                                                                                                                                          |                                                                | $5 + (1.5 \times T_{REFCLK})$           | ns       |  |  |

|        | DCR[HTADT] = 11                                                                                                                                                                                          |                                                                | 5 + (2.5 $\times$ T <sub>REFCLK</sub> ) | ns       |  |  |

| 112    | Read/Write data strobe assertion width                                                                                                                                                                   | 1.8 + T <sub>REFCLK</sub>                                      | _                                       | ns       |  |  |

| 201    | Host data input set-up time before write data strobe deassertion                                                                                                                                         | 1.0                                                            | —                                       | ns       |  |  |

| 202    | Host data input hold time after write data strobe deassertion                                                                                                                                            | 4 7                                                            |                                         |          |  |  |

|        | 1.1 V core     1.2 V core                                                                                                                                                                                | 1.7<br>1.5                                                     |                                         | ns<br>ns |  |  |

| Notes: | 1. Attributes refers to the following signals: HCS, HA[11–29], HCID[0–                                                                                                                                   | _                                                              | and UW/BSn                              | 113      |  |  |

| Notes. | <ol> <li>This specification is tested in dual-strobe mode. Timing in single-strobe mode is guaranteed by design.</li> <li>All values listed in this table are tested or guaranteed by design.</li> </ol> |                                                                |                                         |          |  |  |

Figure 14 shows DSI asynchronous read signals timing.

#### Notes: 1. Used for single-strobe mode access.

- **2.** Used for dual-strobe mode access.

- **3.** HTA released at logic 0 (DCR[HTAAD] = 0) at end of access; used with pull-down implementation.

- 4. HTA released at logic 1 (DCR[HTAAD] = 1) at end of access; used with pull-up implementation.

Figure 14. Asynchronous Single- and Dual-Strobe Modes Read Timing Diagram

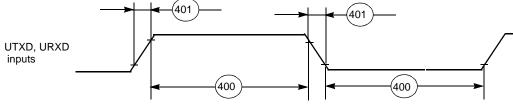

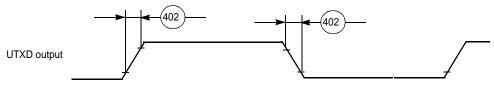

# 2.5.8 UART Timing

| No. | Characteristics                        | Expression               | Min   | Max | Unit |

|-----|----------------------------------------|--------------------------|-------|-----|------|

| 400 | URXD and UTXD inputs high/low duration | 16 × T <sub>REFCLK</sub> | 160.0 | —   | ns   |

| 401 | URXD and UTXD inputs rise/fall time    |                          |       | 10  | ns   |

| 402 | UTXD output rise/fall time             |                          |       | 10  | ns   |

Figure 20. UART Input Timing

Figure 21. UART Output Timing

MSC8122 Quad Digital Signal Processor Data Sheet, Rev. 16

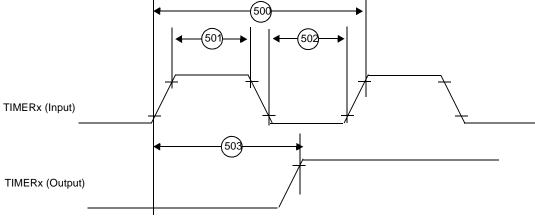

# 2.5.9 Timer Timing

| No. | Characteristics                                                                                            | Ref =      | Unit       |          |

|-----|------------------------------------------------------------------------------------------------------------|------------|------------|----------|

| NO. |                                                                                                            | Min        | Max        | Unit     |

| 500 | TIMERx frequency                                                                                           | 10.0       | _          | ns       |

| 501 | TIMERx Input high period                                                                                   | 4.0        |            | ns       |

| 502 | TIMERx Output low period                                                                                   | 4.0        |            | ns       |

| 503 | <ul> <li>TIMERx Propagations delay from its clock input</li> <li>1.1 V core</li> <li>1.2 V core</li> </ul> | 3.1<br>2.8 | 9.5<br>8.1 | ns<br>ns |

Figure 22. Timer Timing

### 2.5.10 Ethernet Timing

### 2.5.10.1 Management Interface Timing

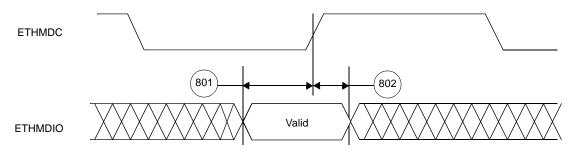

#### Table 24. Ethernet Controller Management Interface Timing

| No. | Characteristics                           | Min | Max | Unit |

|-----|-------------------------------------------|-----|-----|------|

| 801 | ETHMDIO to ETHMDC rising edge set-up time | 10  | _   | ns   |

| 802 | ETHMDC rising edge to ETHMDIO hold time   | 10  |     | ns   |

Figure 23. MDIO Timing Relationship to MDC

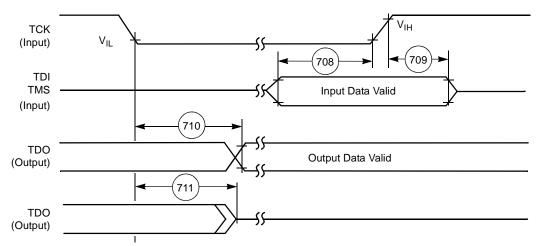

Figure 31. Test Access Port Timing Diagram

# 3 Hardware Design Considerations

The following sections discuss areas to consider when the MSC8122 device is designed into a system.

# 3.1 Start-up Sequencing Recommendations

Use the following guidelines for start-up and power-down sequences:

- Assert **PORESET** and **TRST** before applying power and keep the signals driven low until the power reaches the required minimum power levels. This can be implemented via weak pull-down resistors.

- CLKIN can be held low or allowed to toggle during the beginning of the power-up sequence. However, CLKIN must start toggling before the deassertion of PORESET and after both power supplies have reached nominal voltage levels.

- If possible, bring up V<sub>DD</sub>/V<sub>CCSYN</sub> and V<sub>DDH</sub> together. If it is not possible, raise V<sub>DD</sub>/V<sub>CCSYN</sub> first and then bring up V<sub>DDH</sub>. V<sub>DDH</sub> should not exceed V<sub>DD</sub>/V<sub>CCSYN</sub> until V<sub>DD</sub>/V<sub>CCSYN</sub> reaches its nominal voltage level. Similarly, bring both voltage levels down together. If that is not possible reverse the power-up sequence, with V<sub>DDH</sub> going down first and then V<sub>DD</sub>/V<sub>CCSYN</sub>.

- **Note:** This recommended power sequencing for the MSC8122 is different from the MSC8102. See Section 2.5.2 for start-up timing specifications.

External voltage applied to any input line must not exceed the I/O supply  $V_{DDH}$  by more than 0.8 V at any time, including during power-up. Some designs require pull-up voltages applied to selected input lines during power-up for configuration purposes. This is an acceptable exception to the rule. However, each such input can draw up to 80 mA per input pin per device in the system during start-up.

During the power-up sequence, if  $V_{DD}$  rises before  $V_{DDH}$  (see **Figure 6**), current can pass from the  $V_{DD}$  supply through the device ESD protection circuits to the  $V_{DDH}$  supply. The ESD protection diode can allow this to occur when  $V_{DD}$  exceeds  $V_{DDH}$  by more than 0.8 V. Design the power supply to prevent or minimize this effect using one of the following optional methods:

MSC8122 Quad Digital Signal Processor Data Sheet, Rev. 16

#### ware Design Considerations

- **Note:** The MSC8122 does not support DLL-enabled mode. For the following two clock schemes, ensure that the DLL is disabled (that is, the DLLDIS bit in the Hard Reset Configuration Word is set).

- If no system synchronization is required (for example, the design does not use SDRAM), you can use any of the available clock modes.

- In the CLKIN synchronization mode, use the following connections:

- Connect the oscillator output through a buffer to CLKIN.

- Connect the CLKIN buffer output to the slave device (for example, SDRAM) making sure that the delay path between the clock buffer to the MSC8122 and the SDRAM is equal (that is, has a skew less than 100 ps).

Valid clock modes in this scheme area 0.7, 15, 10, 21, 22, 28, 20, 20, and 21.

- Valid clock modes in this scheme are: 0, 7, 15, 19, 21, 23, 28, 29, 30, and 31.

- In CLKOUT synchronization mode (for 1.2 V devices), CLKOUT is the main clock to SDRAM. Use the following connections:

- Connect the oscillator output through a buffer to CLKIN.

- Connect CLKOUT through a zero-delay buffer to the slave device (for example, SDRAM) using the following guidelines:

- The maximum delay between the slave and CLKOUT must not exceed 0.7 ns.

- The maximum load on CLKOUT must not exceed 10 pF.

- Use a zero-delay buffer with a jitter less than 0.3 ns.

- All clock modes are valid in this clock scheme.

Note: See the Clock chapter in the *MSC8122 Reference Manual* for details.

- If the 60x-compatible system bus is not used and SIUMCR[PBSE] is set, PPBS can be disconnected. Otherwise, it should be pulled up.

- The following signals: SWTE, DSISYNC, DSI64, MODCK[1–2], CNFGS, CHIPID[0–3], RSTCONF and BM[0–2] are

used to configure the MSC8122 and are sampled on the deassertion of the PORESET signal. Therefore, they should

be tied to GND or V<sub>DDH</sub> or through a pull-down or a pull-up resistor until the deassertion of the PORESET signal.

- When they are used, INT\_OUT (if SIUMCR[INTODC] is cleared), NMI\_OUT, and IRQxx (if not full drive) signals must be pulled up.

- When the Ethernet controller is enabled and the SMII mode is selected, GPIO10 and GPIO14 must not be connected externally to any signal line.

- **Note:** For details on configuration, see the *MSC8122 User's Guide* and *MSC8122 Reference Manual*. For additional information, refer to the *MSC8122 Design Checklist* (AN2787).

# 3.4 External SDRAM Selection

The external bus speed implemented in a system determines the speed of the SDRAM used on that bus. However, because of differences in timing characteristics among various SDRAM manufacturers, you may have use a faster speed rated SDRAM to assure efficient data transfer across the bus. For example, for 166 MHz operation, you may have to use 183 or 200 MHz SDRAM. Always perform a detailed timing analysis using the MSC8122 bus timing values and the manufacturer specifications for the SDRAM to ensure correct operation within your system design. The output delay listed in SDRAM specifications is usually given for a load of 30 pF. Scale the number to your specific board load using the typical scaling number provided by the SDRAM manufacturer.

### 3.5 Thermal Considerations

An estimation of the chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

$$T_J = T_A + (R_{\bigcup JA} \times P_D)$$

Eqn. 1

where

$$\begin{split} T_A &= \text{ambient temperature near the package (°C)} \\ R_{\Theta JA} &= \text{junction-to-ambient thermal resistance (°C/W)} \\ P_D &= P_{INT} + P_{I/O} = \text{power dissipation in the package (W)} \\ P_{INT} &= I_{DD} \times V_{DD} = \text{internal power dissipation (W)} \\ P_{I/O} &= \text{power dissipated from device on output pins (W)} \end{split}$$

The power dissipation values for the MSC8122 are listed in **Table 2-3**. The ambient temperature for the device is the air temperature in the immediate vicinity that would cool the device. The junction-to-ambient thermal resistances are JEDEC standard values that provide a quick and easy estimation of thermal performance. There are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. The value that more closely approximates a specific application depends on the power dissipated by other components on the printed circuit board (PCB). The value obtained using a single layer board is appropriate for tightly packed PCB configurations. The value obtained using a board with internal planes is more appropriate for boards with low power dissipation (less than 0.02 W/cm<sup>2</sup> with natural convection) and well separated components. Based on an estimation of junction temperature using this technique, determine whether a more detailed thermal analysis is required. Standard thermal management techniques can be used to maintain the device thermal junction temperature below its maximum. If T<sub>J</sub> appears to be too high, either lower the ambient temperature or the power dissipation of the chip. You can verify the junction temperature by measuring the case temperature using a small diameter thermocouple (40 gauge is recommended) or an infrared temperature sensor on a spot on the device case that is painted black. The MSC8122 device case surface is too shiny (low emissivity) to yield an accurate infrared temperature measurement. Use the following equation to determine T<sub>J</sub>:

$$T_J = T_T + (\theta_{JA} \times P_D)$$

Eqn. 2

where

$T_T$  = thermocouple (or infrared) temperature on top of the package (°C)

$\theta_{JA}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

Note: See MSC8102, MSC8122, and MSC8126 Thermal Management Design Guidelines (AN2601/D).

# 4 Ordering Information

Consult a Freescale Semiconductor sales office or authorized distributor to determine product availability and place an order.

|         |                                             | Core<br>Voltage | Operating<br>Temperature | Core               | Order Number    |                 |  |

|---------|---------------------------------------------|-----------------|--------------------------|--------------------|-----------------|-----------------|--|

| Part    | Package Type                                |                 |                          | Frequency<br>(MHz) | Lead-Free       | Lead-Bearing    |  |

| MSC8122 | Flip Chip Plastic Ball Grid Array (FC-PBGA) | 1.1 V           | -40° to 105°C            | 300                | MSC8122TVT4800V | MSC8122TMP4800V |  |

|         |                                             |                 |                          | 400                | MSC8122TVT6400V | MSC8122TMP6400V |  |

|         |                                             | 1.2 V           | –40° to 105°C            | 400                | MSC8122TVT6400  | MSC8122TMP6400  |  |

|         |                                             |                 | 0° to 90°C               | 500                | MSC8122VT8000   | MSC8122MP8000   |  |

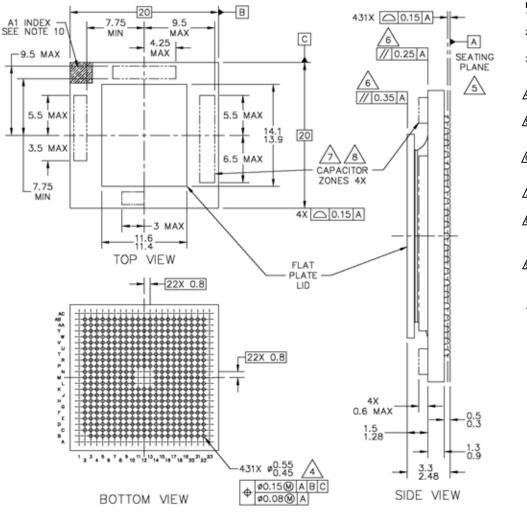

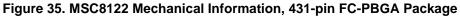

#### **Package Information** 5

- Notes: 1. All dimensions in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M–1994.

- 3. Features are symmetrical about the package center lines unless dimensioned otherwise.

- A Maximum solder ball diameter measured parallel to Datum A.

Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

A Parallelism measurement shall exclude any effect of mark on top surface of package.

Capacitors may not be present on all devices.

Caution must be taken not to short capacitors or exposed metal capacitor pads on package top.

FC CBGA (Ceramic) package code: 5238. FC PBGA (Plastic) package code: 5263.

10.Pin 1 indicator can be in the form of number 1 marking or an "L" shape marking.

#### 6 **Product Documentation**

- MSC8122 Technical Data Sheet (MSC8122). Details the signals, AC/DC characteristics, clock signal characteristics, package and pinout, and electrical design considerations of the MSC8122 device.

- MSC8122 Reference Manual (MSC8122RM). Includes functional descriptions of the extended cores and all the internal subsystems including configuration and programming information.

- Application Notes. Cover various programming topics related to the StarCore DSP core and the MSC8122 device.

- SC140 DSP Core Reference Manual. Covers the SC140 core architecture, control registers, clock registers, program control, and instruction set.