Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | I²C, SCI, SPI                                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 48                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f325ar9t6 |

# Table of Contents

| 10.5.1 Introduction                     |     |

|-----------------------------------------|-----|

| 10.5.2 Main Features                    |     |

| 10.5.3 General Description              |     |

| 10.5.4 Clock Phase and Clock Polarity   |     |

| 10.5.5 Error Flags                      |     |

| 10.5.6 Low Power Modes                  |     |

| 10.5.7 Interrupts                       |     |

|                                         |     |

| 10.5.8 Register Description             |     |

| · ,                                     |     |

| 10.6.1 Introduction                     |     |

| 10.6.2 Main Features                    |     |

| 10.6.3 General Description              |     |

| 10.6.4 Functional Description           |     |

| 10.6.5 Low Power Modes                  |     |

| 10.6.6 Interrupts                       |     |

| 10.6.7 Register Description             |     |

| 10.7 I2C BUS INTERFACE (I2C)            |     |

| 10.7.1 Introduction                     |     |

| 10.7.2 Main Features                    |     |

|                                         |     |

| 10.7.3 General Description              |     |

| 10.7.4 Functional Description           |     |

| 10.7.5 Low Power Modes                  |     |

| 10.7.6 Interrupts                       |     |

| 10.7.7 Register Description             |     |

| 10.8 10-BIT A/D CONVERTER (ADC)         |     |

| 10.8.1 Introduction                     |     |

| 10.8.2 Main Features                    |     |

| 10.8.3 Functional Description           |     |

| 10.8.4 Low Power Modes                  |     |

| 10.8.5 Interrupts                       |     |

| 10.8.6 Register Description             |     |

| 11 INSTRUCTION SET                      |     |

| 11.1 CPU ADDRESSING MODES               |     |

|                                         |     |

| 11.1.1 Inherent                         |     |

| 11.1.2 Immediate                        |     |

| 11.1.3 Direct                           |     |

| 11.1.4 Indexed (No Offset, Short, Long) |     |

| 11.1.5 Indirect (Short, Long)           |     |

| 11.1.6 Indirect Indexed (Short, Long)   |     |

| 11.1.7 Relative mode (Direct, Indirect) |     |

| 11.2 INSTRUCTION GROUPS                 |     |

| 12 ELECTRICAL CHARACTERISTICS           |     |

| 12.1 PARAMETER CONDITIONS               |     |

| 12.1.1 Minimum and Maximum values       |     |

| 12.1.2 Typical values                   |     |

| 12.1.2 Typical values                   |     |

| 12.1.4 Loading capacitor                |     |

| 12.1.4 Loading capacitor                |     |

| IZ I O FILLIDOU VOUADE                  | 14/ |

# Table of Contents —

|    | 12.2 ABSOLUTE MAXIMUM RATINGS                               | 1/12 |

|----|-------------------------------------------------------------|------|

|    |                                                             |      |

|    | 12.2.1 Voltage Characteristics                              |      |

|    | 12.2.3 Thermal Characteristics                              |      |

|    | 12.3 OPERATING CONDITIONS                                   |      |

|    | 12.3.1 General Operating Conditions                         |      |

|    | 12.3.2 Operating Conditions with Low Voltage Detector (LVD) |      |

|    | 12.3.3 Auxiliary Voltage Detector (AVD) Thresholds          |      |

|    | 12.3.4 External Voltage Detector (EVD) Thresholds           |      |

|    | 12.4 SUPPLY CURRENT CHARACTERISTICS                         |      |

|    | 12.4.1 CURRENT CONSUMPTION                                  | 146  |

|    | 12.4.2 Supply and Clock Managers                            | 147  |

|    | 12.4.3 On-Chip Peripherals                                  |      |

|    | 12.5 CLOCK AND TIMING CHARACTERISTICS                       |      |

|    | 12.5.1 General Timings                                      |      |

|    | 12.5.2 External Clock Source                                |      |

|    | 12.5.3 Crystal and Ceramic Resonator Oscillators            |      |

|    | 12.5.4 RC Oscillators                                       |      |

|    | 12.5.5 Clock Security System (CSS)                          |      |

|    | 12.6 MEMORY CHARACTERISTICS                                 |      |

|    | 12.6.1 RAM and Hardware Registers                           |      |

|    | 12.6.2 FLASH Memory                                         |      |

|    | 12.7 EMC CHARACTERISTICS                                    |      |

|    | 12.7.1 Functional EMS (Electro Magnetic Susceptibility)     |      |

|    | 12.7.2 Electro Magnetic Interference (EMI)                  |      |

|    | 12.7.3 Absolute Maximum Ratings (Electrical Sensitivity)    |      |

|    | 12.8 I/O PORT PIN CHARACTERISTICS                           |      |

|    | 12.8.1 General Characteristics                              | 159  |

|    | 12.8.2 Output Driving Current                               | 160  |

|    | 12.9 CONTROL PIN CHARACTERISTICS                            |      |

|    | 12.9.1 Asynchronous RESET Pin                               | 162  |

|    | 12.9.2 ICCSEL/VPP Pin                                       |      |

|    | 12.10TIMER PERIPHERAL CHARACTERISTICS                       | 165  |

|    | 12.10.1 8-Bit PWM-ART Auto-Reload Timer                     |      |

|    | 12.10.2 16-Bit Timer                                        |      |

|    | 12.11COMMUNICATION INTERFACE CHARACTERISTICS                |      |

|    | 12.11.1 SPI - Serial Peripheral Interface                   |      |

|    | 12.11.2 I2C - Inter IC Control Interface                    |      |

|    | 12.1210-BIT ADC CHARACTERISTICS                             |      |

|    | 12.12.1 Analog Power Supply and Reference Pins              |      |

|    | 12.12.2 General PCB Design Guidelines                       |      |

| 12 | 12.12.3 ADC Accuracy                                        |      |

| 13 | 13.1 PACKAGE MECHANICAL DATA                                |      |

|    |                                                             |      |

|    | 13.2 THERMAL CHARACTERISTICS                                | 1/9  |

| Address                                                                                                                    | Block                   | Register<br>Label                                                                                                                                             | Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Reset<br>Status                                                     | Remarks                                                                                                                                                                                           |  |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 002Ch<br>002Dh                                                                                                             | MCC                     | MCC MCCSR Main Clock Control / Status Register Main Clock Controller: Beep Control Register                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |                                                                                                                                                                                                   |  |

| 002Eh<br>to<br>0030h                                                                                                       | Reserved Area (3 Bytes) |                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |                                                                                                                                                                                                   |  |

| 0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h<br>0039h<br>003Ah<br>003Bh<br>003Ch<br>003Dh<br>003Fh | TIMER A                 | TACR2 TACR1 TACSR TAIC1HR TAIC1LR TAOC1HR TAOC1LR TACHR TACHR TACLR | Timer A Control Register 2 Timer A Control Register 1 Timer A Control/Status Register Timer A Input Capture 1 High Register Timer A Input Capture 1 Low Register Timer A Output Compare 1 High Register Timer A Output Compare 1 Low Register Timer A Counter High Register Timer A Counter High Register Timer A Alternate Counter High Register Timer A Alternate Counter Low Register Timer A Input Capture 2 High Register Timer A Input Capture 2 Low Register Timer A Output Compare 2 High Register Timer A Output Compare 2 Low Register | 00h 00h xxxx x0xx b xxh xxh 80h 00h FFh FCh FCh xxh xxh 80h 00h     | R/W R/W Read Only Read Only R/W R/W Read Only         |  |

| 0040h                                                                                                                      |                         |                                                                                                                                                               | Reserved Area (1 Byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |                                                                                                                                                                                                   |  |

| 0041h<br>0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch<br>004Dh<br>004Fh | TIMER B                 | TBCR2 TBCR1 TBCSR TBIC1HR TBIC1LR TBOC1HR TBOC1LR TBCHR TBCHR TBCHR TBCLR TBACHR TBACHR TBACLR TBIC2HR TBIC2LR TBIC2HR TBIC2LR TBOC2HR TBOC2LR                | Timer B Control Register 2 Timer B Control Register 1 Timer B Control/Status Register Timer B Input Capture 1 High Register Timer B Input Compare 1 Low Register Timer B Output Compare 1 Low Register Timer B Output Compare 1 Low Register Timer B Counter High Register Timer B Counter Low Register Timer B Alternate Counter High Register Timer B Alternate Counter Low Register Timer B Input Capture 2 High Register Timer B Input Capture 2 Low Register Timer B Output Compare 2 High Register Timer B Output Compare 2 Low Register   | 00h 00h xxxx x0xx b xxh xxh 80h 00h FFh FCh FFh FCh xxh xxh 80h 00h | R/W R/W Read Only Read Only R/W R/W Read Only RAW R/W |  |

| 0050h<br>0051h<br>0052h<br>0053h<br>0054h<br>0055h<br>0056h<br>0057h                                                       | SCI                     | SCISR<br>SCIDR<br>SCIBRR<br>SCICR1<br>SCICR2<br>SCIERPR<br>SCIETPR                                                                                            | SCI Status Register SCI Data Register SCI Baud Rate Register SCI Control Register 1 SCI Control Register 2 SCI Extended Receive Prescaler Register Reserved area SCI Extended Transmit Prescaler Register                                                                                                                                                                                                                                                                                                                                        | C0h<br>xxh<br>00h<br>x000 0000b<br>00h<br>00h                       | Read Only<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W                                                                                                                                                      |  |

47/

## **5 CENTRAL PROCESSING UNIT**

### 5.1 INTRODUCTION

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

### **5.2 MAIN FEATURES**

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- Low power HALT and WAIT modes

- Priority maskable hardware interrupts

- Non-maskable software/hardware interrupts

### **5.3 CPU REGISTERS**

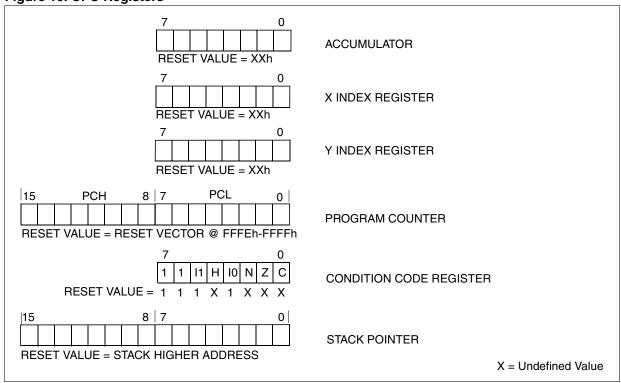

The six CPU registers shown in Figure 1 are not present in the memory mapping and are accessed by specific instructions.

### Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

# Index Registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

# **Program Counter (PC)**

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

Figure 10. CPU Registers

577

# 6 SUPPLY, RESET AND CLOCK MANAGEMENT

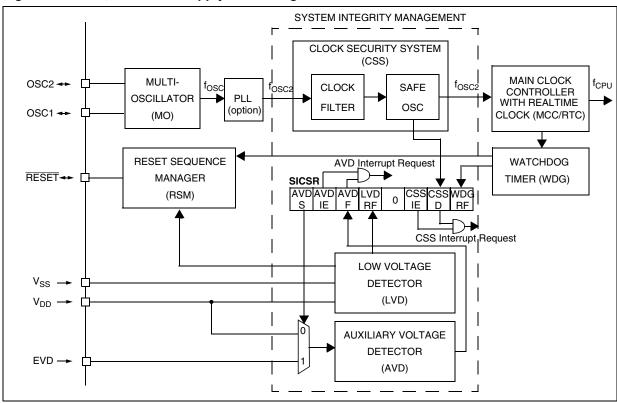

The device includes a range of utility features for securing the application in critical situations (for example in case of a power brown-out), and reducing the number of external components. An overview is shown in Figure 13.

For more details, refer to dedicated parametric section.

### Main features

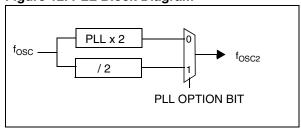

- Optional PLL for multiplying the frequency by 2 (not to be used with internal RC oscillator)

- Reset Sequence Manager (RSM)

- Multi-Oscillator Clock Management (MO)

- 5 Crystal/Ceramic resonator oscillators

- 1 Internal RC oscillator

- System Integrity Management (SI)

- Main supply Low voltage detection (LVD)

- Auxiliary Voltage detector (AVD) with interrupt capability for monitoring the main supply

- Clock Security System (CSS) with Clock Filter and Backup Safe Oscillator (enabled by option byte)

### **6.1 PHASE LOCKED LOOP**

If the clock frequency input to the PLL is in the range 2 to 4 MHz, the PLL can be used to multiply the frequency by two to obtain an  $f_{OSC2}$  of 4 to 8 MHz. The PLL is enabled by option byte. If the PLL is disabled, then  $f_{OSC2} = f_{OSC}/2$ .

**Caution:** The PLL is not recommended for applications where timing accuracy is required. See "PLL Characteristics" on page 154.

Figure 12. PLL Block Diagram

Figure 13. Clock, Reset and Supply Block Diagram

# **RESET SEQUENCE MANAGER** (Cont'd)

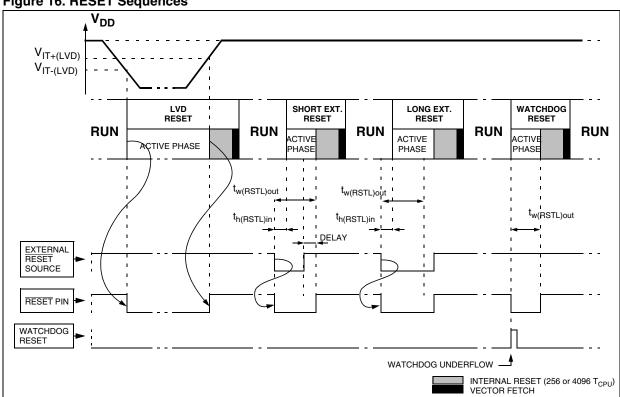

The RESET pin is an asynchronous signal which plays a major role in EMS performance. In a noisy environment, it is recommended to follow the guidelines mentioned in the electrical characteristics section.

If the external  $\overline{\text{RESET}}$  pulse is shorter than  $t_{w(RSTL)out}$  (see short ext. Reset in Figure 16), the signal on the  $\overline{\text{RESET}}$  pin may be stretched. Otherwise the delay will not be applied (see long ext. Reset in Figure 16). Starting from the external RESET pulse recognition, the device  $\overline{\text{RESET}}$  pin acts as an output that is pulled low during at least  $t_{w(RSTL)out}$ .

### 6.3.3 External Power-On RESET

If the LVD is disabled by option byte, to start up the microcontroller correctly, the user must ensure by means of an external reset circuit that the reset signal is held low until  $V_{DD}$  is over the minimum level specified for the selected  $f_{OSC}$  frequency. (see "OPERATING CONDITIONS" on page 144)

A proper reset signal for a slow rising  $V_{DD}$  supply can generally be provided by an external RC network connected to the  $\overline{\text{RESET}}$  pin.

# 6.3.4 Internal Low Voltage Detector (LVD) RESET

Two different RESET sequences caused by the internal LVD circuitry can be distinguished:

- Power-On RESET

- Voltage Drop RESET

The device  $\overline{\text{RESET}}$  pin acts as an output that is pulled low when  $V_{DD} < V_{IT+}$  (rising edge) or  $V_{DD} < V_{IT-}$  (falling edge) as shown in Figure 16.

The LVD filters spikes on  $V_{DD}$  larger than  $t_{g(VDD)}$  to avoid parasitic resets.

### 6.3.5 Internal Watchdog RESET

The RESET sequence generated by a internal Watchdog counter overflow is shown in Figure 16.

Starting from the Watchdog counter underflow, the device  $\overline{RESET}$  pin acts as an output that is pulled low during at least  $t_{w(RSTL)out}$ .

Figure 16. RESET Sequences

57

# MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

# 10.2.5 Low Power Modes

| Mode            | Description                                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT            | No effect on MCC/RTC peripheral.  MCC/RTC interrupt cause the device to exit from WAIT mode.                                                   |

| ACTIVE-<br>HALT | No effect on MCC/RTC counter (OIE bit is set), the registers are frozen.  MCC/RTC interrupt cause the device to exit from ACTIVE-HALT mode.    |

| HALT            | MCC/RTC counter and registers are frozen. MCC/RTC operation resumes when the MCU is woken up by an interrupt with "exit from HALT" capability. |

# 10.2.6 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event          | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------|---------------|--------------------------|----------------------|----------------------|

| Time base overflow event | OIF           | OIE                      | Yes                  | No <sup>1)</sup>     |

### Note:

The MCC/RTC interrupt wakes up the MCU from ACTIVE-HALT mode, not from HALT mode.

# 10.2.7 Register Description MCC CONTROL/STATUS REGISTER (MCCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| ,   |     |     |     |     |     |     | U   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| мсо | CP1 | CP0 | SMS | TB1 | ТВ0 | OIE | OIF |

Bit 7 = MCO Main clock out selection

This bit enables the MCO alternate function on the PF0 I/O port. It is set and cleared by software.

- 0: MCO alternate function disabled (I/O pin free for general-purpose I/O)

- 1: MCO alternate function enabled (f<sub>CPU</sub> on I/O port)

Note: To reduce power consumption, the MCO function is not active in ACTIVE-HALT mode.

Bit 6:5 = CP[1:0] CPU clock prescaler

These bits select the CPU clock prescaler which is applied in the different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software

| f <sub>CPU</sub> in SLOW mode | CP1 | CP0 |

|-------------------------------|-----|-----|

| f <sub>OSC2</sub> / 2         | 0   | 0   |

| f <sub>OSC2</sub> / 4         | 0   | 1   |

| f <sub>OSC2</sub> / 8         | 1   | 0   |

| f <sub>OSC2</sub> / 16        | 1   | 1   |

Bit 4 = **SMS** Slow mode select

This bit is set and cleared by software.

0: Normal mode. f<sub>CPU</sub> = f<sub>OSC2</sub> 1: Slow mode. f<sub>CPU</sub> is given by CP1, CP0 See Section 8.2 SLOW MODE and Section 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) for more de-

# Bit 3:2 = TB[1:0] Time base control

These bits select the programmable divider time base. They are set and cleared by software.

| Counter   | Time                    | TB1                     | ТВ0 |     |

|-----------|-------------------------|-------------------------|-----|-----|

| Prescaler | f <sub>OSC2</sub> =4MHz | f <sub>OSC2</sub> =8MHz | 161 | 150 |

| 16000     | 4ms                     | 2ms                     | 0   | 0   |

| 32000     | 8ms                     | 4ms                     | 0   | 1   |

| 80000     | 20ms                    | 10ms                    | 1   | 0   |

| 200000    | 50ms                    | 25ms                    | 1   | 1   |

A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real time clock.

Bit 1 = **OIE** Oscillator interrupt enable

This bit set and cleared by software.

- 0: Oscillator interrupt disabled

- 1: Oscillator interrupt enabled

This interrupt can be used to exit from ACTIVE-HALT mode.

When this bit is set, calling the ST7 software HALT instruction enters the ACTIVE-HALT power saving mode

# 10.3 PWM AUTO-RELOAD TIMER (ART)

### 10.3.1 Introduction

The Pulse Width Modulated Auto-Reload Timer on-chip peripheral consists of an 8-bit auto reload counter with compare/capture capabilities and of a 7-bit prescaler clock source.

These resources allow five possible operating modes:

- Generation of up to 4 independent PWM signals

- Output compare and Time base interrupt

- Up to two input capture functions

- External event detector

- Up to two external interrupt sources

The three first modes can be used together with a single counter frequency.

The timer can be used to wake up the MCU from WAIT and HALT modes.

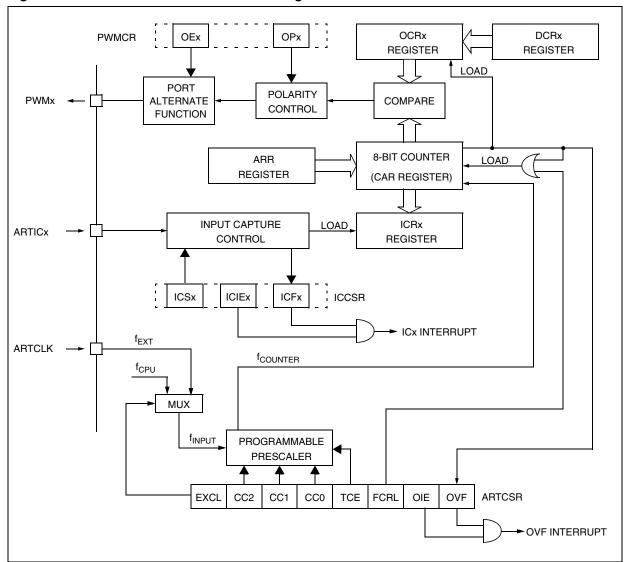

Figure 39. PWM Auto-Reload Timer Block Diagram

# 16-BIT TIMER (Cont'd)

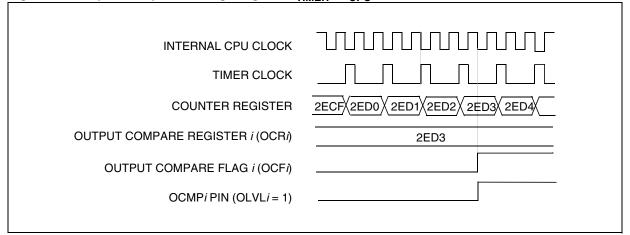

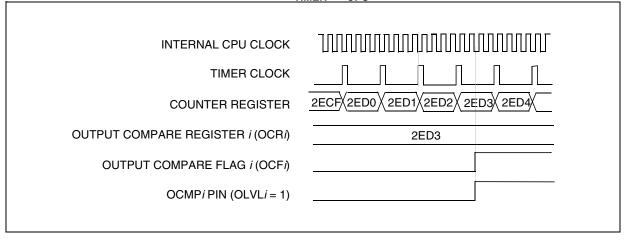

Figure 53. Output Compare Timing Diagram, f<sub>TIMER</sub> = f<sub>CPU</sub>/4

81/197

## 16-BIT TIMER (Cont'd)

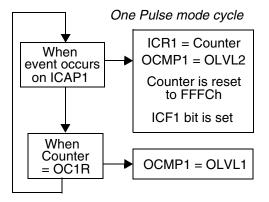

### 10.4.3.5 One Pulse Mode

One Pulse mode enables the generation of a pulse when an external event occurs. This mode is selected via the OPM bit in the CR2 register.

The One Pulse mode uses the Input Capture1 function and the Output Compare1 function.

#### Procedure:

To use One Pulse mode:

- Load the OC1R register with the value corresponding to the length of the pulse (see the formula in the opposite column).

- 2. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after the pulse.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin during the pulse.

- Select the edge of the active transition on the ICAP1 pin with the IEDG1 bit (the ICAP1 pin must be configured as floating input).

- 3. Select the following in the CR2 register:

- Set the OC1E bit, the OCMP1 pin is then dedicated to the Output Compare 1 function.

- Set the OPM bit.

- Select the timer clock CC[1:0] (see Table 1).

Then, on a valid event on the ICAP1 pin, the counter is initialized to FFFCh and OLVL2 bit is loaded on the OCMP1 pin, the ICF1 bit is set and the value FFFDh is loaded in the IC1R register.

Because the ICF1 bit is set when an active edge occurs, an interrupt can be generated if the ICIE bit is set.

Clearing the Input Capture interrupt request (that is, clearing the ICF*i* bit) is done in two steps:

- 1. Reading the SR register while the ICF*i* bit is set.

- 2. An access (read or write) to the ICiLR register.

The OC1R register value required for a specific timing application can be calculated using the following formula:

OC*i*R Value =

$$\frac{t \cdot f_{CPU}}{PRESC} - 5$$

Where:

= Pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on the CC[1:0] bits, see Table 1)

If the timer clock is an external clock the formula is:

$$OCiR = t * f_{EXT} - 5$$

Where:

t = Pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

When the value of the counter is equal to the value of the contents of the OC1R register, the OLVL1 bit is output on the OCMP1 pin, (See Figure 10).

### Notes:

- 1. The OCF1 bit cannot be set by hardware in One Pulse mode but the OCF2 bit can generate an Output Compare interrupt.

- 2. When the Pulse Width Modulation (PWM) and One Pulse mode (OPM) bits are both set, the PWM mode is the only active one.

- 3. If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

- 4. The ICAP1 pin can not be used to perform input capture. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each time a valid edge occurs on the ICAP1 pin and ICF1 can also generates interrupt if ICIE is set.

- 5. When One Pulse mode is used OC1R is dedicated to this mode. Nevertheless OC2R and OCF2 can be used to indicate a period of time has been elapsed but cannot generate an output waveform because the level OLVL2 is dedicated to the One Pulse mode.

# 16-BIT TIMER (Cont'd)

# **CONTROL REGISTER 2 (CR2)**

Read/Write

Reset Value: 0000 0000 (00h)

7 0

| OC1F | OC2F | OPM | PWM | CC1   | CC0 | IFDG2 | <b>EXEDG</b> |

|------|------|-----|-----|-------|-----|-------|--------------|

|      | 00   | •   |     | • • • |     | 0     | _, ( 0.      |

### Bit 7 = **OC1E** Output Compare 1 Pin Enable.

This bit is used only to output the signal from the timer on the OCMP1 pin (OLV1 in Output Compare mode, both OLV1 and OLV2 in PWM and one-pulse mode). Whatever the value of the OC1E bit, the Output Compare 1 function of the timer remains active.

- 0: OCMP1 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP1 pin alternate function enabled.

# Bit 6 = **OC2E** Output Compare 2 Pin Enable.

This bit is used only to output the signal from the timer on the OCMP2 pin (OLV2 in Output Compare mode). Whatever the value of the OC2E bit, the Output Compare 2 function of the timer remains active.

- 0: OCMP2 pin alternate function disabled (I/O pin free for general-purpose I/O).

- 1: OCMP2 pin alternate function enabled.

## Bit 5 = **OPM** One Pulse Mode.

- 0: One Pulse mode is not active.

- 1: One Pulse mode is active, the ICAP1 pin can be used to trigger one pulse on the OCMP1 pin; the active transition is given by the IEDG1 bit. The length of the generated pulse depends on the contents of the OC1R register.

Bit 4 = **PWM** Pulse Width Modulation.

- 0: PWM mode is not active.

- 1: PWM mode is active, the OCMP1 pin outputs a programmable cyclic signal; the length of the pulse depends on the value of OC1R register; the period depends on the value of OC2R register.

### Bit 3, 2 = **CC[1:0]** *Clock Control.*

The timer clock mode depends on these bits:

**Table 18. Clock Control Bits**

| Timer Clock                      | CC1 | CC0 |

|----------------------------------|-----|-----|

| f <sub>CPU</sub> / 4             | 0   | 0   |

| f <sub>CPU</sub> / 2             | U   | 1   |

| f <sub>CPU</sub> / 8             | 1   | 0   |

| External Clock (where available) |     | 1   |

**Note**: If the external clock pin is not available, programming the external clock configuration stops the counter.

# Bit 1 = **IEDG2** Input Edge 2.

This bit determines which type of level transition on the ICAP2 pin will trigger the capture.

- 0: A falling edge triggers the capture.

- 1: A rising edge triggers the capture.

### Bit 0 = **EXEDG** External Clock Edge.

This bit determines which type of level transition on the external clock pin EXTCLK will trigger the counter register.

- 0: A falling edge triggers the counter register.

- 1: A rising edge triggers the counter register.

# SERIAL PERIPHERAL INTERFACE (Cont'd)

Table 21. SPI Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------|-------------------|------|------|------|------|------|------|------|------|

| 0021h             | SPIDR             | MSB  |      |      |      |      |      |      | LSB  |

| 002111            | Reset Value       | Х    | Х    | Х    | Х    | Х    | Х    | Х    | x    |

| 0022h             | SPICR             | SPIE | SPE  | SPR2 | MSTR | CPOL | CPHA | SPR1 | SPR0 |

| 002211            | Reset Value       | 0    | 0    | 0    | 0    | Х    | Х    | Х    | Х    |

| 0023h             | SPICSR            | SPIF | WCOL | OVR  | MODF |      | SOD  | SSM  | SSI  |

| 002311            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

# 10.7 I<sup>2</sup>C BUS INTERFACE (I2C)

### 10.7.1 Introduction

The I<sup>2</sup>C Bus Interface serves as an interface between the microcontroller and the serial I<sup>2</sup>C bus. It provides both multimaster and slave functions, and controls all I<sup>2</sup>C bus-specific sequencing, protocol, arbitration and timing. It supports fast I<sup>2</sup>C mode (400kHz).

## 10.7.2 Main Features

- Parallel-bus/I<sup>2</sup>C protocol converter

- Multi-master capability

- 7-bit/10-bit Addressing

- SMBus V1.1 Compliant

- Transmitter/Receiver flag

- End-of-byte transmission flag

- Transfer problem detection

### I<sup>2</sup>C Master Features:

- Clock generation

- I<sup>2</sup>C bus busy flag

- Arbitration Lost Flag

- End of byte transmission flag

- Transmitter/Receiver Flag

- Start bit detection flag

- Start and Stop generation

## I<sup>2</sup>C Slave Features:

- Stop bit detection

- I<sup>2</sup>C bus busy flag

- Detection of misplaced start or stop condition

- Programmable I<sup>2</sup>C Address detection

- Transfer problem detection

- End-of-byte transmission flag

- Transmitter/Receiver flag

## 10.7.3 General Description

In addition to receiving and transmitting data, this interface converts it from serial to parallel format

and vice versa, using either an interrupt or polled handshake. The interrupts are enabled or disabled by software. The interface is connected to the I<sup>2</sup>C bus by a data pin (SDAI) and by a clock pin (SCLI). It can be connected both with a standard I<sup>2</sup>C bus and a Fast I<sup>2</sup>C bus. This selection is made by software.

# **Mode Selection**

The interface can operate in the four following modes:

- Slave transmitter/receiver

- Master transmitter/receiver

By default, it operates in slave mode.

The interface automatically switches from slave to master after it generates a START condition and from master to slave in case of arbitration loss or a STOP generation, allowing then Multi-Master capability.

### **Communication Flow**

In Master mode, it initiates a data transfer and generates the clock signal. A serial data transfer always begins with a start condition and ends with a stop condition. Both start and stop conditions are generated in master mode by software.

In Slave mode, the interface is capable of recognising its own address (7 or 10-bit), and the General Call address. The General Call address detection may be enabled or disabled by software.

Data and addresses are transferred as 8-bit bytes, MSB first. The first byte(s) following the start condition contain the address (one in 7-bit mode, two in 10-bit mode). The address is always transmitted in Master mode.

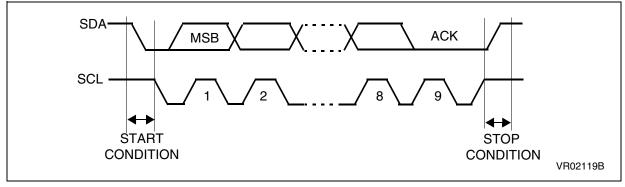

A 9th clock pulse follows the 8 clock cycles of a byte transfer, during which the receiver must send an acknowledge bit to the transmitter. Refer to Figure 67.

Figure 67. I<sup>2</sup>C BUS Protocol

47/

# I<sup>2</sup>C BUS INTERFACE (Cont'd) 10.7.7 Register Description

# I<sup>2</sup>C CONTROL REGISTER (CR)

Read / Write

Reset Value: 0000 0000 (00h)

| 0 0 | PE | ENGC | START | ACK | STOP | ITE |

|-----|----|------|-------|-----|------|-----|

Bit 7:6 = Reserved. Forced to 0 by hardware.

### Bit 5 = PE Peripheral enable.

This bit is set and cleared by software.

- 0: Peripheral disabled

- 1: Master/Slave capability

#### Notes

- When PE=0, all the bits of the CR register and the SR register except the Stop bit are reset. All outputs are released while PE=0

- When PE=1, the corresponding I/O pins are selected by hardware as alternate functions.

- To enable the I<sup>2</sup>C interface, write the CR register

TWICE with PE=1 as the first write only activates the interface (only PE is set).

### Bit 4 = **ENGC** Enable General Call.

This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE=0). The 00h General Call address is acknowledged (01h ignored).

- 0: General Call disabled

- 1: General Call enabled

**Note:** In accordance with the I2C standard, when GCAL addressing is enabled, an I2C slave can only receive data. It will not transmit data to the master.

Bit 3 = **START** Generation of a Start condition. This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE=0) or when the Start condition is sent (with interrupt generation if ITE=1).

- In master mode:

- 0: No start generation

- 1: Repeated start generation

- In slave mode:

- 0: No start generation

- 1: Start generation when the bus is free

### Bit 2 = **ACK** Acknowledge enable.

This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE=0).

- 0: No acknowledge returned

- 1: Acknowledge returned after an address byte or a data byte is received

### Bit 1 = **STOP** Generation of a Stop condition.

This bit is set and cleared by software. It is also cleared by hardware in master mode. Note: This bit is not cleared when the interface is disabled (PE=0).

- In master mode:

- 0: No stop generation

- 1: Stop generation after the current byte transfer or after the current Start condition is sent. The STOP bit is cleared by hardware when the Stop condition is sent.

- In slave mode:

- 0: No stop generation

- 1: Release the SCL and SDA lines after the current byte transfer (BTF=1). In this mode the STOP bit has to be cleared by software.

# Bit 0 = **ITE** Interrupt enable.

This bit is set and cleared by software and cleared by hardware when the interface is disabled (PE=0).

- 0: Interrupts disabled

- 1: Interrupts enabled

Refer to Figure 70 for the relationship between the events and the interrupt.

SCL is held low when the ADD10, SB, BTF or ADSL flags or an EV6 event (See Figure 69) is detected

## **INSTRUCTION SET OVERVIEW** (Cont'd)

### 11.1.1 Inherent

All Inherent instructions consist of a single byte. The opcode fully specifies all the required information for the CPU to process the operation.

| Inherent Instruction       | Function                            |

|----------------------------|-------------------------------------|

| NOP                        | No operation                        |

| TRAP                       | S/W Interrupt                       |

| WFI                        | Wait For Interrupt (Low Power Mode) |

| HALT                       | Halt Oscillator (Lowest Power Mode) |

| RET                        | Sub-routine Return                  |

| IRET                       | Interrupt Sub-routine Return        |

| SIM                        | Set Interrupt Mask (level 3)        |

| RIM                        | Reset Interrupt Mask (level 0)      |

| SCF                        | Set Carry Flag                      |

| RCF                        | Reset Carry Flag                    |

| RSP                        | Reset Stack Pointer                 |

| LD                         | Load                                |

| CLR                        | Clear                               |

| PUSH/POP                   | Push/Pop to/from the stack          |

| INC/DEC                    | Increment/Decrement                 |

| TNZ                        | Test Negative or Zero               |

| CPL, NEG                   | 1 or 2 Complement                   |

| MUL                        | Byte Multiplication                 |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations         |

| SWAP                       | Swap Nibbles                        |

# 11.1.2 Immediate

Immediate instructions have 2 bytes, the first byte contains the opcode, the second byte contains the operand value.

| Immediate Instruction | Function              |

|-----------------------|-----------------------|

| LD                    | Load                  |

| СР                    | Compare               |

| BCP                   | Bit Compare           |

| AND, OR, XOR          | Logical Operations    |

| ADC, ADD, SUB, SBC    | Arithmetic Operations |

### 11.1.3 Direct

In Direct instructions, the operands are referenced by their memory address.

The direct addressing mode consists of two submodes:

### Direct (short)

The address is a byte, thus requires only one byte after the opcode, but only allows 00 - FF addressing space.

# Direct (long)

The address is a word, thus allowing 64 Kbyte addressing space, but requires 2 bytes after the opcode.

## 11.1.4 Indexed (No Offset, Short, Long)

In this mode, the operand is referenced by its memory address, which is defined by the unsigned addition of an index register (X or Y) with an offset.

The indirect addressing mode consists of three submodes:

### Indexed (No Offset)

There is no offset, (no extra byte after the opcode), and allows 00 - FF addressing space.

### Indexed (Short)

The offset is a byte, thus requires only one byte after the opcode and allows 00 - 1FE addressing space.

### Indexed (long)

The offset is a word, thus allowing 64 Kbyte addressing space and requires 2 bytes after the opcode.

### 11.1.5 Indirect (Short, Long)

The required data byte to do the operation is found by its memory address, located in memory (pointer)

The pointer address follows the opcode. The indirect addressing mode consists of two submodes:

### Indirect (short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - FF addressing space, and requires 1 byte after the opcode.

### Indirect (long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# **OPERATING CONDITIONS** (Cont'd)

# 12.3.2 Operating Conditions with Low Voltage Detector (LVD)

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                | Conditions                                   | Min                | Тур  | Max                 | Unit |

|-----------------------|----------------------------------------------------------|----------------------------------------------|--------------------|------|---------------------|------|

|                       | Reset release threshold                                  | VD level = High in option byte               | 4.0 <sup>1)</sup>  | 4.2  | 4.5                 |      |

| $V_{IT+(LVD)}$        | (V <sub>DD</sub> rise)                                   | VD level = Med. in option byte $^{2}$        | 3.55 <sup>1)</sup> | 3.75 | 4.0 <sup>1)</sup>   |      |

|                       | (VDD nee)                                                | VD level = Low in option byte <sup>2)</sup>  | 2.95 <sup>1)</sup> | 3.15 | 3.35 <sup>1)</sup>  | V    |

|                       | Reset generation threshold (V <sub>DD</sub> fall)        | VD level = High in option byte               | 3.8                | 4.0  | 4.25 <sup>1)</sup>  | V    |

| $V_{IT-(LVD)}$        |                                                          | VD level = Med. in option byte <sup>2)</sup> | 3.35 <sup>1)</sup> | 3.55 | 3.75 <sup>1))</sup> |      |

|                       |                                                          | VD level = Low in option byte <sup>2)</sup>  | 2.8 <sup>1)</sup>  | 3.0  | 3.15 <sup>1)</sup>  |      |

| V <sub>hys(LVD)</sub> | LVD voltage threshold hysteresis                         | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub> |                    | 200  |                     | mV   |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time <sup>3)</sup>                  | LVD enabled                                  | 6μs/V              |      | 100ms/V             |      |

| t <sub>g(VDD)</sub>   | $V_{DD}$ glitches filtered (not detected) by LVD $^{3)}$ |                                              |                    |      | 40                  | ns   |

### Notes:

- 1. Data based on characterization results, tested in production for ROM devices only.

- 2. If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed.

- 3. Data based on characterization results, not tested in production.

# 12.3.3 Auxiliary Voltage Detector (AVD) Thresholds

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                    | Conditions                                   | Min                | Тур  | Max                | Unit |

|-----------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|------|--------------------|------|

|                       | 1 O AVDE flog toggle throughold                              | VD level = High in option byte               | 4.4 <sup>1)</sup>  | 4.6  | 4.9 <sup>1)</sup>  |      |

| $V_{IT+(AVD)}$        | 1 ⇒0 AVDF flag toggle threshold (V <sub>DD</sub> rise)       | VD level = Med. in option byte               | 3.95 <sup>1)</sup> | 4.15 | 4.4 <sup>1)</sup>  |      |

| , ,                   | (VDD lise)                                                   | VD level = Low in option byte                | 3.4 <sup>1)</sup>  | 3.6  | 3.8 <sup>1)</sup>  | V    |

|                       | 0 ⇒1 AVDF flag toggle threshold                              | VD level = High in option byte               | 4.2 <sup>1)</sup>  | 4.4  | 4.65 <sup>1)</sup> | , v  |

| V <sub>IT-(AVD)</sub> | 0 ⇒1 AVDF liag toggle tilleshold<br>  (V <sub>DD</sub> fall) | VD level = Med. in option byte               | 3.75 <sup>1)</sup> | 4.0  | 4.2 <sup>1)</sup>  |      |

| ,                     | (VDD Idii)                                                   | VD level = Low in option byte                | 3.2 <sup>1)</sup>  | 3.4  | 3.6 <sup>1)</sup>  |      |

| V <sub>hys(AVD)</sub> | AVD voltage threshold hysteresis                             | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub> |                    | 200  |                    | mV   |

| ΔV <sub>IT-</sub>     | Voltage drop between AVD flag set and LVD reset activated    | V <sub>IT-(AVD)</sub> -V <sub>IT-(LVD)</sub> |                    | 450  |                    | mV   |

<sup>1.</sup> Data based on characterization results, tested in production for ROM devices only.

# 12.3.4 External Voltage Detector (EVD) Thresholds

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                                 | Conditions                                   | Min  | Тур  | Max  | Unit |

|-----------------------|---------------------------------------------------------------------------|----------------------------------------------|------|------|------|------|

| V <sub>IT+(EVD)</sub> | 1 ⇒0 AVDF flag toggle threshold (V <sub>DD</sub> rise) <sup>1)</sup>      |                                              | 1.15 | 1.26 | 1.35 | V    |

| V <sub>IT-(EVD)</sub> | $0 \Rightarrow 1$ AVDF flag toggle threshold $(V_{DD} \text{ fall})^{1)}$ |                                              | 1.1  | 1.2  | 1.3  | V    |

| V <sub>hys(EVD)</sub> | EVD voltage threshold hysteresis                                          | V <sub>IT+(EVD)</sub> -V <sub>IT-(EVD)</sub> |      | 200  |      | mV   |

1. Data based on characterization results, not tested in production.

# 12.6 MEMORY CHARACTERISTICS

## 12.6.1 RAM and Hardware Registers

| Symbol   | Parameter              | Conditions           | Min | Тур | Max | Unit |

|----------|------------------------|----------------------|-----|-----|-----|------|

| $V_{RM}$ | Data retention mode 1) | HALT mode (or RESET) | 1.6 |     |     | V    |

# 12.6.2 FLASH Memory

| DUAL VOL                                | TAGE HDFLASH MEMORY                         |                                    |                   |     |                   |         |  |

|-----------------------------------------|---------------------------------------------|------------------------------------|-------------------|-----|-------------------|---------|--|

| Symbol                                  | Parameter                                   | Conditions                         | Min <sup>2)</sup> | Тур | Max <sup>2)</sup> | Unit    |  |

| f                                       | Operating frequency                         | Read mode                          | 0                 |     | 8                 | MHz     |  |

| $f_{CPU}$                               |                                             | Write / Erase mode                 | 1                 |     | 8                 | IVIITIZ |  |

| V <sub>PP</sub>                         | Programming voltage 3)                      | $4.5V \le V_{DD} \le 5.5V$         | 11.4              |     | 12.6              | V       |  |

|                                         |                                             | RUN mode (f <sub>CPU</sub> = 4MHz) |                   |     | 3                 | A       |  |

| $I_{DD}$                                | Supply current <sup>4)</sup>                | Write / Erase                      |                   | 0   |                   | mA      |  |

|                                         |                                             | Power down mode / HALT             |                   | 1   | 10                |         |  |

| 1                                       | V <sub>PP</sub> current <sup>4)</sup>       | Read (V <sub>PP</sub> =12V)        |                   |     | 200               | μA      |  |

| I <sub>PP</sub>                         |                                             | Write / Erase                      |                   |     | 30                | mA      |  |

| t <sub>VPP</sub>                        | Internal V <sub>PP</sub> stabilization time |                                    |                   | 10  |                   | μs      |  |

|                                         |                                             | T <sub>A</sub> =85°C               | 40                |     |                   |         |  |

| $t_{RET}$                               | Data retention                              | T <sub>A</sub> =105°C              | 15                |     |                   | years   |  |

|                                         |                                             | T <sub>A</sub> =125°C              | 7                 |     |                   |         |  |

| NI                                      | Write erace evoles                          | T <sub>A</sub> = 55°C              | 1000              |     |                   | cycles  |  |

| $N_{RW}$                                | Write erase cycles                          | T <sub>A</sub> = 85°C              | 100               |     |                   | cycles  |  |

| T <sub>PROG</sub><br>T <sub>ERASE</sub> | Programming or erasing temperature range    |                                    | -40               | 25  | 85                | °C      |  |

# Notes:

- 1. Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Not tested in production.

- 2. Data based on characterization results, not tested in production.

- 3. V<sub>PP</sub> must be applied only during the programming or erasing operation and not permanently for reliability reasons.

- 4. Data based on simulation results, not tested in production.

Warning: Do not connect 12V to  $V_{PP}$  before  $V_{DD}$  is powered on, as this may damage the device.

# I/O PORT PIN CHARACTERISTICS (Cont'd)

# 12.8.2 Output Driving Current

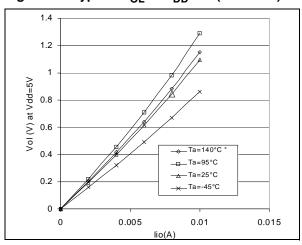

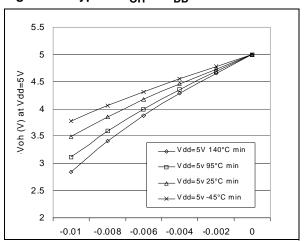

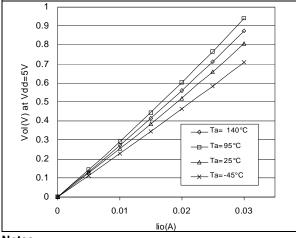

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol                        | Parameter                                                                                                        | Conditions      |                                                 | Min                  | Max        | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------|----------------------|------------|------|

|                               | Output low level voltage for a standard I/O pin                                                                  |                 | I <sub>IO</sub> =+5mA                           |                      | 1.2        |      |

| ) 1)                          | when 8 pins are sunk at same time (see Figure 81)                                                                |                 | I <sub>IO</sub> =+2mA                           |                      | 0.5        |      |

| V <sub>OL</sub> 1)            | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time (see Figure 82 and Figure 84) | 7=c             | $I_{IO}$ =+20mA, $T_A$ ≤85°C $T_A$ ≥85°C        |                      | 1.3<br>1.5 | V    |

|                               |                                                                                                                  | V <sub>DD</sub> | I <sub>IO</sub> =+8mA                           |                      | 0.6        |      |

| V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time                                    |                 | $I_{IO}$ =-5mA, $T_A \le 85$ °C $T_A \ge 85$ °C |                      |            |      |

|                               | (see Figure 83 and Figure 86)                                                                                    |                 | I <sub>IO</sub> =-2mA                           | V <sub>DD</sub> -0.7 |            |      |

Figure 81. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (standard)

Figure 83. Typical V<sub>OH</sub> at V<sub>DD</sub>=5V

Figure 82. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (high-sink)

### Notes

- 1. The  $I_{\text{IO}}$  current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of  $I_{\text{IO}}$  (I/O ports and control pins) must not exceed  $I_{\text{VSS}}$ .

- 2. The  $I_{IO}$  current sourced must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VDD}$ . True open drain I/O pins do not have  $V_{OH}$ .

160/197

# 10-BIT ADC CHARACTERISTICS (Cont'd)

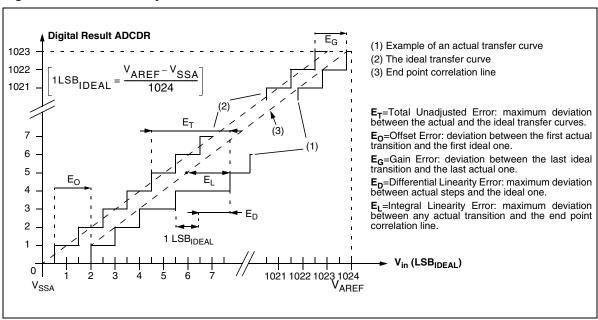

# 12.12.3 ADC Accuracy

Conditions: V<sub>DD</sub>=5V 1)

| Symbol            | Parameter                       | Conditions                                | Тур | Max <sup>2)</sup> | Unit |

|-------------------|---------------------------------|-------------------------------------------|-----|-------------------|------|

| IE <sub>T</sub> I | Total unadjusted error 1)       |                                           | 3   | 4                 |      |

| IE <sub>O</sub> I | Offset error 1)                 |                                           | 2   | 3                 |      |

| IE <sub>G</sub> I | Gain Error 1)                   |                                           | 0.5 | 3                 | LSB  |

| IE <sub>D</sub> I | Differential linearity error 1) | CPU in run mode @ f <sub>ADC</sub> 2 MHz. | 1   | 2                 |      |

| IE <sub>L</sub> I | Integral linearity error 1)     | CPU in run mode @ f <sub>ADC</sub> 2 MHz. | 1   | 2                 |      |

#### Notes:

1. ADC Accuracy vs. Negative Injection Current: Injecting negative current may reduce the accuracy of the conversion being performed on another analog input.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 12.8 does not affect the ADC accuracy.

2. Data based on characterization results, monitored in production to guarantee 99.73% within  $\pm$  max value from -40°C to 125°C ( $\pm$  3 $\sigma$  distribution limits).

Figure 98. ADC Accuracy Characteristics

# **13.2 THERMAL CHARACTERISTICS**

| Symbol Ratings    |                                                  | Value | Unit |

|-------------------|--------------------------------------------------|-------|------|

|                   | Package thermal resistance (junction to ambient) |       |      |

|                   | LQFP64 10x10                                     | 50    |      |

|                   | LQFP48 7x7                                       | 80    |      |

| $R_{thJA}$        | LQFP44 10x10                                     | 52    | °C/W |

|                   | SDIP42                                           | 55    |      |

|                   | LQFP32 7x7                                       | 70    |      |

|                   | SDIP32                                           | 50    |      |

| $P_{D}$           | Power dissipation 1)                             | 500   | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>2)</sup>       | 150   | °C   |

### Notes:

- 1. The maximum chip-junction temperature is based on technology characteristics.

- 2. The maximum power dissipation is obtained from the formula PD = (TJ -TA) / RthJA.

The power dissipation of an application can be defined by the user with the formula: PD=PINT+PPORT where PINT is the chip internal power (IDDxVDD) and PPORT is the port power dissipation depending on the ports used in the application.