Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 16KB (16K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f325j4tce |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | F       | Pin n   | 0      |        |                                 |      | Le             | evel            |   |                     | Р   | ort   |                 |                 | Main                                         |                                                                                                                                                                                                                         |                             |         |  |  |

|--------|---------|---------|--------|--------|---------------------------------|------|----------------|-----------------|---|---------------------|-----|-------|-----------------|-----------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------|--|--|

| P64    | 48C     | 48S     | P44    | 42     | Pin Name                        | Type | ut             | out             |   | Input               |     |       | Out             | Output func     |                                              | function<br>(after Alternate f                                                                                                                                                                                          |                             |         |  |  |

| LQFP64 | LQFP48C | LQFP48S | LQFP44 | SDIP42 |                                 |      | Input          | Input<br>Output |   | float<br>wpu<br>int |     | ana   | OD              | РР              | reset)                                       |                                                                                                                                                                                                                         |                             |         |  |  |

| 42     | 32      | 32      | 30     | 23     | PC7/SS/AIN15                    | I/O  | CT             |                 | x | х                   |     | х     | x               | x               | Port C7                                      | SPI Slave<br>Select (ac-<br>tive low)                                                                                                                                                                                   | ADC Ana-<br>log<br>Input 15 |         |  |  |

| 43     | _4)     | -       | -      | -      | PA0                             | I/O  | $C_T$          |                 | Х | X ei0               |     | X ei0 |                 | X ei0           |                                              | Х                                                                                                                                                                                                                       | Х                           | Port A0 |  |  |

| 44     | _4)     | -       | -      | -      | PA1                             | I/O  | $C_T$          |                 | Χ | e                   | i0  |       | Х               | Х               | Port A1                                      |                                                                                                                                                                                                                         |                             |         |  |  |

| 45     | 33      | -       | -      | -      | PA2                             | I/O  | $C_T$          |                 | Х | e                   | i0  |       | Х               | Х               | Port A2                                      |                                                                                                                                                                                                                         |                             |         |  |  |

| 46     | 34      | 34      | 31     | 24     | PA3 (HS)                        | I/O  | $C_T$          | HS              | Х |                     | ei0 |       | Х               | Х               | Port A3                                      |                                                                                                                                                                                                                         |                             |         |  |  |

| 47     | 35      | 35      | 32     | 25     | V <sub>DD_1</sub> <sup>6)</sup> | S    |                |                 |   |                     |     |       |                 |                 | Digital M                                    | ain Supply Vo                                                                                                                                                                                                           | oltage                      |         |  |  |

| 48     | 36      | 36      | 33     | 26     | V <sub>SS_1</sub> <sup>6)</sup> | S    |                |                 |   |                     |     |       |                 |                 | Digital G                                    | round Voltage                                                                                                                                                                                                           | )                           |         |  |  |

| 49     | 37      | 37      | 34     | 27     | PA4 (HS)                        | I/O  | $C_T$          | HS              | Χ | Х                   |     |       | Х               | Х               | Port A4                                      |                                                                                                                                                                                                                         |                             |         |  |  |

| 50     | 38      | 38      | 35     | 28     | PA5 (HS)                        | I/O  | $C_{T}$        | HS              | Х | Х                   |     |       | Х               | Х               | Port A5                                      |                                                                                                                                                                                                                         |                             |         |  |  |

| 51     | 39      | 39      | 36     | 29     | PA6 (HS)/SDAI                   | I/O  | $C_{T}$        | HS              | Х |                     |     |       | Т               |                 | Port A6                                      | I <sup>2</sup> C Data 1)                                                                                                                                                                                                |                             |         |  |  |

| 52     | 40      | 40      | 37     | 30     | PA7 (HS)/SCLI                   | I/O  | $C_T$          | HS              | Х |                     |     |       | Т               |                 | Port A7                                      | I <sup>2</sup> C Clock 1)                                                                                                                                                                                               |                             |         |  |  |

| 53     | 41      | 41      | 38     | 31     | V <sub>PP</sub> / ICCSEL        | I    |                |                 |   |                     |     |       |                 |                 | ming mo<br>program<br>See Sect<br>tails. Hig | Must be tied low. In flash program-<br>ming mode, this pin acts as the<br>programming voltage input V <sub>PP</sub> .<br>See Section 12.9.2 for more de-<br>tails. High voltage must not be ap-<br>plied to ROM devices |                             |         |  |  |

| 54     | 42      | 42      | 39     | 32     | RESET                           | I/O  | CT             |                 |   |                     |     |       |                 |                 | Top prior<br>rupt.                           | ity non maska                                                                                                                                                                                                           | able inter-                 |         |  |  |

| 55     | -       | -       | -      | -      | EVD                             |      |                |                 |   |                     |     |       |                 |                 | External                                     | voltage detec                                                                                                                                                                                                           | tor                         |         |  |  |

| 56     | -       | -       | -      | -      | TLI                             | I    | C <sub>T</sub> |                 |   |                     | Х   |       |                 |                 | Top leve                                     | interrupt inpu                                                                                                                                                                                                          | ut pin                      |         |  |  |

| 57     | 43      | 43      | 40     | 33     | V <sub>SS_2</sub> <sup>6)</sup> | S    |                |                 |   |                     |     |       |                 |                 | Digital G                                    | round Voltage                                                                                                                                                                                                           | )                           |         |  |  |

| 58     | 44      | 44      | 41     | 34     | OSC2 <sup>3)</sup>              | I/O  |                |                 |   |                     |     |       |                 |                 | Resonate<br>put                              | or oscillator in                                                                                                                                                                                                        | verter out-                 |         |  |  |

| 59     | 45      | 45      | 42     | 35     | OSC1 <sup>3)</sup>              | I    |                |                 |   |                     |     |       |                 |                 |                                              | External clock input or Resonator oscillator inverter input                                                                                                                                                             |                             |         |  |  |

| 60     | 46      | 46      | 43     | 36     | V <sub>DD_2</sub> <sup>6)</sup> | S    |                |                 |   |                     |     |       |                 |                 | Digital M                                    | ain Supply Vo                                                                                                                                                                                                           | oltage                      |         |  |  |

| 61     | 47      | 47      | 44     | 37     | PE0/TDO                         | I/O  | $C_T$          |                 | Х | Х                   |     |       | Х               | Х               | Port E0                                      | SCI Transm                                                                                                                                                                                                              | it Data Out                 |         |  |  |

| 62     | 48      | 48      | 1      | 38     | PE1/RDI                         | I/O  | $C_T$          |                 | Х | Х                   |     |       | Х               | Х               | Port E1                                      | SCI Receive                                                                                                                                                                                                             | e Data In                   |         |  |  |

| 63     | 1       | -       | -      | -      | PE2                             | I/O  | $C_{T}$        |                 | Х | Х                   |     |       | X <sup>4)</sup> | X <sup>4)</sup> | Port E2                                      |                                                                                                                                                                                                                         |                             |         |  |  |

| 64     | -4)     | -       | -      | -      | PE3                             | I/O  | $C_T$          |                 | Х | Х                   |     |       | Х               | Х               | Port E3                                      |                                                                                                                                                                                                                         |                             |         |  |  |

57

# FLASH PROGRAM MEMORY (Cont'd)

### 4.5 ICP (In-Circuit Programming)

To perform ICP the microcontroller must be switched to ICC (In-Circuit Communication) mode by an external controller or programming tool.

Depending on the ICP code downloaded in RAM, Flash memory programming can be fully customized (number of bytes to program, program locations, or selection serial communication interface for downloading).

When using an STMicroelectronics or third-party programming tool that supports ICP and the specific microcontroller device, the user needs only to implement the ICP hardware interface on the application board (see Figure 8). For more details on the pin locations, refer to the device pinout description.

### 4.6 IAP (In-Application Programming)

**ل ح**ک

This mode uses a BootLoader program previously stored in Sector 0 by the user (in ICP mode or by plugging the device in a programming tool).

This mode is fully controlled by user software. This allows it to be adapted to the user application, (user-defined strategy for entering programming mode, choice of communications protocol used to fetch the data to be stored, etc.). For example, it is possible to download code from the SPI, SCI, USB or CAN interface and program it in the Flash. IAP mode can be used to program any of the Flash sectors except Sector 0, which is write/erase protected to allow recovery in case errors occur during the programming operation.

## 4.7 Related Documentation

For details on Flash programming and ICC protocol, refer to the ST7 Flash Programming Reference Manual and to the ST7 ICC Protocol Reference Manual.

# 4.7.1 Register Description FLASH CONTROL/STATUS REGISTER (FCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

This register is reserved for use by Programming Tool software. It controls the Flash programming and erasing operations.

### Figure 9. Flash Control/Status Register Address and Reset Value

| Address<br>(Hex.) | Register<br>Label   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------|---------------------|---|---|---|---|---|---|---|---|

| 0029h             | FCSR<br>Reset Value | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

23/197

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

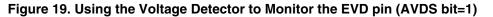

# 6.4.2.2 Monitoring a Voltage on the EVD pin

This mode is selected by setting the AVDS bit in the SICSR register.

The AVD circuitry can generate an interrupt when the AVDIE bit of the SICSR register is set. This interrupt is generated on the rising and falling edges

57

of the comparator output. This means it is generated when either one of these two events occur:

- $V_{EVD}$  rises up to  $V_{IT+(EVD)}$   $V_{EVD}$  falls down to  $V_{IT-(EVD)}$

- The EVD function is illustrated in Figure 19.

For more details, refer to the Electrical Characteristics section.

# WATCHDOG TIMER (Cont'd)

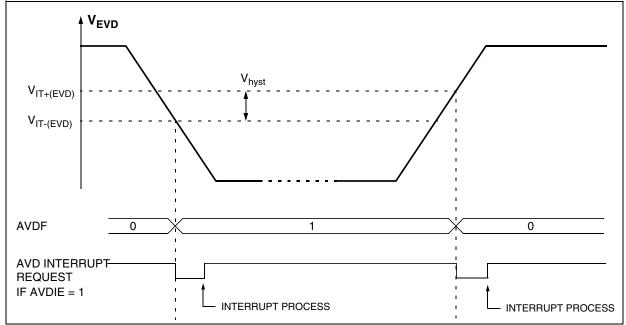

## 10.1.4 How to Program the Watchdog Timeout

Figure 2 shows the linear relationship between the 6-bit value to be loaded in the Watchdog Counter (CNT) and the resulting timeout duration in milliseconds. This can be used for a quick calculation without taking the timing variations into account. If

Figure 36. Approximate Timeout Duration

more precision is needed, use the formulae in Figure 3.

**Caution:** When writing to the WDGCR register, always write 1 in the T6 bit to avoid generating an immediate reset.

57

# MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

### 10.2.5 Low Power Modes

| Mode            | Description                                                                                                                                             |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT            | No effect on MCC/RTC peripheral.<br>MCC/RTC interrupt cause the device to exit<br>from WAIT mode.                                                       |

| ACTIVE-<br>HALT | No effect on MCC/RTC counter (OIE bit is<br>set), the registers are frozen.<br>MCC/RTC interrupt cause the device to exit<br>from ACTIVE-HALT mode.     |

| HALT            | MCC/RTC counter and registers are frozen.<br>MCC/RTC operation resumes when the<br>MCU is woken up by an interrupt with "exit<br>from HALT" capability. |

## 10.2.6 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event          | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------|---------------|--------------------------|----------------------|----------------------|

| Time base overflow event | OIF           | OIE                      | Yes                  | No <sup>1)</sup>     |

### Note:

The MCC/RTC interrupt wakes up the MCU from ACTIVE-HALT mode, not from HALT mode.

# 10.2.7 Register Description MCC CONTROL/STATUS REGISTER (MCCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| мсо | CP1 | CP0 | SMS | TB1 | TB0 | OIE | OIF |  |

Bit 7 = **MCO** *Main clock out selection*

This bit enables the MCO alternate function on the PF0 I/O port. It is set and cleared by software.

0: MCO alternate function disabled (I/O pin free for general-purpose I/O)

1: MCO alternate function enabled (f<sub>CPU</sub> on I/O port)

**Note**: To reduce power consumption, the MCO function is not active in ACTIVE-HALT mode.

### Bit 6:5 = CP[1:0] CPU clock prescaler

These bits select the CPU clock prescaler which is applied in the different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software

| f <sub>CPU</sub> in SLOW mode | CP1 | CP0 |

|-------------------------------|-----|-----|

| f <sub>OSC2</sub> / 2         | 0   | 0   |

| f <sub>OSC2</sub> / 4         | 0   | 1   |

| f <sub>OSC2</sub> / 8         | 1   | 0   |

| f <sub>OSC2</sub> / 16        | 1   | 1   |

## Bit 4 = **SMS** *Slow mode select*

This bit is set and cleared by software.

0: Normal mode. f<sub>CPU</sub> = f<sub>OSC2</sub>

1: Slow mode. f<sub>CPU</sub> is given by CP1, CP0 See Section 8.2 SLOW MODE and Section 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) for more details.

# Bit 3:2 = TB[1:0] Time base control

These bits select the programmable divider time base. They are set and cleared by software.

| Counter   | Time                    | Base                    | TB1 | тво |  |

|-----------|-------------------------|-------------------------|-----|-----|--|

| Prescaler | f <sub>OSC2</sub> =4MHz | f <sub>OSC2</sub> =8MHz | 101 | 150 |  |

| 16000     | 4ms                     | 2ms                     | 0   | 0   |  |

| 32000     | 8ms                     | 4ms                     | 0   | 1   |  |

| 80000     | 20ms                    | 10ms                    | 1   | 0   |  |

| 200000    | 50ms                    | 25ms                    | 1   | 1   |  |

A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real time clock.

Bit 1 = **OIE** Oscillator interrupt enable

This bit set and cleared by software.

0: Oscillator interrupt disabled

1: Oscillator interrupt enabled

This interrupt can be used to exit from ACTIVE-HALT mode.

When this bit is set, calling the ST7 software HALT instruction enters the ACTIVE-HALT power saving mode.

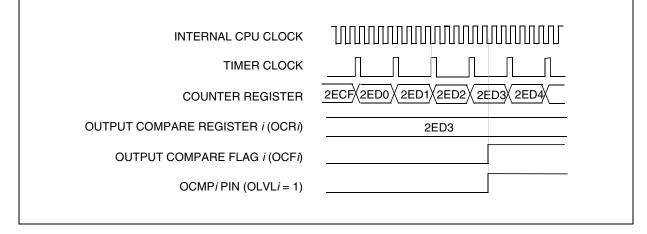

### 16-BIT TIMER (Cont'd)

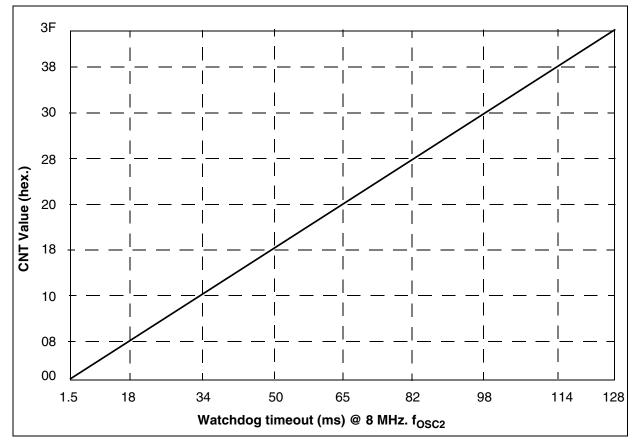

### 10.4.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are two output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OC*i*E bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

### Procedure:

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 1).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OC*i*R register and CR register:

OCF*i* bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \text{ OC} i \text{R} = \frac{\Delta t * f_{\text{CPU}}}{\text{PRESC}}$$

Where:

$\Delta t$  = Output compare period (in seconds)

$f_{CPU} = CPU \operatorname{clock} \operatorname{frequency} (\operatorname{in} \operatorname{hertz})$

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 1)

If the timer clock is an external clock, the formula is:

$$\Delta OC R = \Delta t * f_{EXT}$$

Where:

$\Delta t$  = Output compare period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (that is, clearing the OCF*i* bit) is done by:

1. Reading the SR register while the OCF*i* bit is set.

2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCFi bit from being set between the time it is read and the write to the OCiR register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

57

# 16-BIT TIMER (Cont'd)

<u>ل</u>حک

### 16-BIT TIMER (Cont'd)

# OUTPUT COMPARE 2 HIGH REGISTER (OC2HR)

#### Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

# OUTPUT COMPARE 2 LOW REGISTER (OC2LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

### **COUNTER HIGH REGISTER (CHR)**

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# **COUNTER LOW REGISTER (CLR)**

#### Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# ALTERNATE COUNTER HIGH REGISTER (ACHR)

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

# ALTERNATE COUNTER LOW REGISTER (ACLR)

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# **INPUT CAPTURE 2 HIGH REGISTER (IC2HR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

# **INPUT CAPTURE 2 LOW REGISTER (IC2LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

### SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 10.5.3.3 Master Mode Operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

Note: The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

To operate the SPI in master mode, perform the following steps in order (if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account):

1. Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 60 shows the four possible configurations. **Note:** The slave must have the same CPOL and CPHA settings as the master.

- Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- Write to the SPICR register:

- Set the MSTR and SPE bits

MSTR and SPE bits remain set only if SS is high).

The transmit sequence begins when software writes a byte in the SPIDR register.

### 10.5.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register.

Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### 10.5.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- 1. Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see **Note:** The slave must have the same CPOL and CPHA settings as the master.

- Manage the SS pin as described in Section 10.5.3.2 and Figure 58. If CPHA=1 SS must be held low continuously. If CPHA=0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- 2. Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

### 10.5.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set.

- A write or a read to the SPIDR register.

Notes: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 10.5.5.2).

# SERIAL PERIPHERAL INTERFACE (Cont'd)

# 10.5.6 Low Power Modes

<u>ل</u>رک

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the MCU is woken up by<br>an interrupt with "exit from HALT mode" ca-<br>pability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the device. |

# 10.5.6.1 Using the SPI to wakeup the MCU from Halt mode

In slave configuration, the SPI is able to wakeup the ST7 device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware. **Note:** When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the ST7 from Halt mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the ST7 enters Halt mode. So if Slave selection is configured as external (see Section 10.5.3.2), make sure the master drives a low level on the SS pin when the slave enters Halt mode.

## 10.5.7 Interrupts

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of Transfer<br>Event | SPIF          |                          | Yes                  | Yes                  |

| Master Mode Fault<br>Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          | Yes                  | No                   |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in

### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

### 10.6.4.7 Parity Control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the frame length defined by the M bit, the possible SCI frame formats are as listed in Table 1.

### Table 22. Frame Formats

| M bit | PCE bit | SCI frame                  |

|-------|---------|----------------------------|

| 0     | 0       | SB   8 bit data   STB      |

| 0     | 1       | SB   7-bit data   PB   STB |

| 1     | 0       | SB   9-bit data   STB      |

| 1     | 1       | SB   8-bit data PB   STB   |

**Legend:** SB = Start Bit, STB = Stop Bit, PB = Parity Bit

FD = Failiy Dil

**Note**: In case of wake up by an address mark, the MSB bit of the data is taken into account and not the parity bit

**Even parity:** the parity bit is calculated to obtain an even number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 0 if even parity is selected (PS bit = 0).

**Odd parity:** the parity bit is calculated to obtain an odd number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 1 if odd parity is selected (PS bit = 1).

**Transmission mode:** If the PCE bit is set then the MSB bit of the data written in the data register is not transmitted but is changed by the parity bit.

**Reception mode:** If the PCE bit is set then the interface checks if the received data byte has an

even number of "1s" if even parity is selected (PS = 0) or an odd number of "1s" if odd parity is selected (PS = 1). If the parity check fails, the PE flag is set in the SCISR register and an interrupt is generated if PIE is set in the SCICR1 register.

### 10.6.4.8 SCI Clock Tolerance

During reception, each bit is sampled 16 times. The majority of the 8th, 9th and 10th samples is considered as the bit value. For a valid bit detection, all the three samples should have the same value otherwise the noise flag (NF) is set. For example: If the 8th, 9th and 10th samples are 0, 1 and 1 respectively, then the bit value is "1", but the Noise Flag bit is set because the three samples values are not the same.

Consequently, the bit length must be long enough so that the 8th, 9th and 10th samples have the desired bit value. This means the clock frequency should not vary more than 6/16 (37.5%) within one bit. The sampling clock is resynchronized at each start bit, so that when receiving 10 bits (one start bit, 1 data byte, 1 stop bit), the clock deviation must not exceed 3.75%.

**Note:** The internal sampling clock of the microcontroller samples the pin value on every falling edge. Therefore, the internal sampling clock and the time the application expects the sampling to take place may be out of sync. For example: If the baud rate is 15.625 Kbaud (bit length is 64µs), then the 8th, 9th and 10th samples are at 28µs, 32µs and 36µs respectively (the first sample starting ideally at 0µs). But if the falling edge of the internal clock occurs just before the pin value changes, the samples would then be out of sync by ~4us. This means the entire bit length must be at least 40µs (36µs for the 10th sample + 4µs for synchronization with the internal sampling clock).

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) 10.6.5 Low Power Modes

| Mode | Description                                                                        |  |

|------|------------------------------------------------------------------------------------|--|

|      | No effect on SCI.                                                                  |  |

| WAIT | SCI interrupts cause the device to exit from Wait mode.                            |  |

|      | SCI registers are frozen.                                                          |  |

| HALT | In Halt mode, the SCI stops transmitting/re-<br>ceiving until Halt mode is exited. |  |

## 10.6.6 Interrupts

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

| Interrupt Event                 | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|---------------------------------|---------------|--------------------------|----------------------|----------------------|

| Transmit Data Register<br>Empty | TDRE          | TIE                      | Yes                  | No                   |

| Transmission Com-<br>plete      | тс            | TCIE                     | Yes                  | No                   |

| Received Data Ready to be Read  | RDRF          | RIE                      | Yes                  | No                   |

| Overrun Error Detect-<br>ed     | OR            |                          | Yes                  | No                   |

| Idle Line Detected              | IDLE          | ILIE                     | Yes                  | No                   |

| Parity Error                    | PE            | PIE                      | Yes                  | No                   |

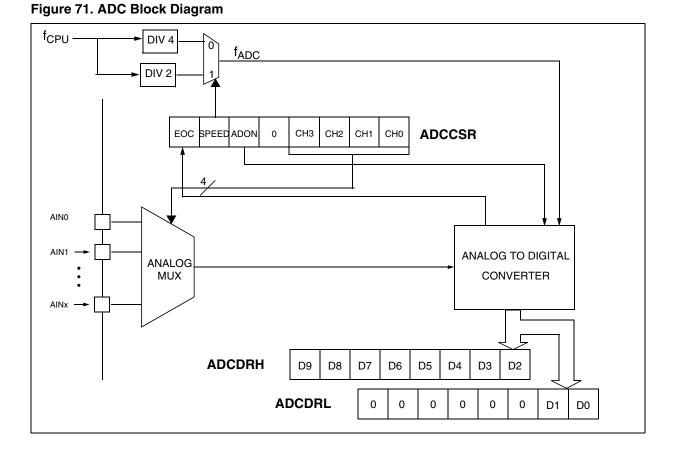

## 10.8 10-BIT A/D CONVERTER (ADC)

### 10.8.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 16 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 16 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled

# through a Control/Status Register.

## 10.8.2 Main Features

- 10-bit conversion

- Up to 16 channels with multiplexed input

- Linear successive approximation

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 71.

# INSTRUCTION SET OVERVIEW (Cont'd)

## 11.1.1 Inherent

All Inherent instructions consist of a single byte. The opcode fully specifies all the required information for the CPU to process the operation.

| Inherent Instruction       | Function                                 |

|----------------------------|------------------------------------------|

| NOP                        | No operation                             |

| TRAP                       | S/W Interrupt                            |

| WFI                        | Wait For Interrupt (Low Pow-<br>er Mode) |

| HALT                       | Halt Oscillator (Lowest Power Mode)      |

| RET                        | Sub-routine Return                       |

| IRET                       | Interrupt Sub-routine Return             |

| SIM                        | Set Interrupt Mask (level 3)             |

| RIM                        | Reset Interrupt Mask (level 0)           |

| SCF                        | Set Carry Flag                           |

| RCF                        | Reset Carry Flag                         |

| RSP                        | Reset Stack Pointer                      |

| LD                         | Load                                     |

| CLR                        | Clear                                    |

| PUSH/POP                   | Push/Pop to/from the stack               |

| INC/DEC                    | Increment/Decrement                      |

| TNZ                        | Test Negative or Zero                    |

| CPL, NEG                   | 1 or 2 Complement                        |

| MUL                        | Byte Multiplication                      |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations              |

| SWAP                       | Swap Nibbles                             |

### 11.1.2 Immediate

Immediate instructions have 2 bytes, the first byte contains the opcode, the second byte contains the operand value.

| Immediate Instruction | Function              |

|-----------------------|-----------------------|

| LD                    | Load                  |

| CP                    | Compare               |

| BCP                   | Bit Compare           |

| AND, OR, XOR          | Logical Operations    |

| ADC, ADD, SUB, SBC    | Arithmetic Operations |

## 11.1.3 Direct

In Direct instructions, the operands are referenced by their memory address.

The direct addressing mode consists of two submodes:

### Direct (short)

The address is a byte, thus requires only one byte after the opcode, but only allows 00 - FF addressing space.

### Direct (long)

The address is a word, thus allowing 64 Kbyte addressing space, but requires 2 bytes after the opcode.

### 11.1.4 Indexed (No Offset, Short, Long)

In this mode, the operand is referenced by its memory address, which is defined by the unsigned addition of an index register (X or Y) with an offset.

The indirect addressing mode consists of three submodes:

### Indexed (No Offset)

There is no offset, (no extra byte after the opcode), and allows 00 - FF addressing space.

### Indexed (Short)

The offset is a byte, thus requires only one byte after the opcode and allows 00 - 1FE addressing space.

### Indexed (long)

The offset is a word, thus allowing 64 Kbyte addressing space and requires 2 bytes after the opcode.

### 11.1.5 Indirect (Short, Long)

The required data byte to do the operation is found by its memory address, located in memory (pointer).

The pointer address follows the opcode. The indirect addressing mode consists of two submodes:

### Indirect (short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - FF addressing space, and requires 1 byte after the opcode.

### Indirect (long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

### 12.5.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                             | Parameter                                                                                                         | Conditions | Min                  | Max                  | Unit |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------|----------------------|----------------------|------|

| f <sub>OSC</sub>                   | Oscillator Frequency <sup>1)</sup>                                                                                |            | 1                    | 16                   | MHz  |

| R <sub>F</sub>                     | Feedback resistor <sup>2)</sup>                                                                                   |            | 20                   | 40                   | kΩ   |

| C <sub>L1</sub><br>C <sub>L2</sub> | Recommended load capacitance versus equivalent serial resistance of the crystal or ceramic resonator $(R_S)^{3)}$ |            | 20<br>20<br>15<br>15 | 60<br>50<br>35<br>35 | pF   |

| Symbol         | Parameter            | Conditions                                                                                                                                                                                                   | Тур                      | Max | Unit |

|----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|

| i <sub>2</sub> | OSC2 driving current | $V_{DD}=5V: \\ f_{OSC}=2MHz, C0 = 6pF, CI1 = CI2 = 68pF \\ f_{OSC}=4MHz, C0 = 6pF, CI1 = CI2 = 68pF \\ f_{OSC}=8MHz, C0 = 6pF, CI1 = CI2 = 40pF \\ f_{OSC}=16MHz, C0 = 7pF, CI1 = CI2 = 20pF \\ \end{cases}$ | 426<br>425<br>456<br>660 |     | μA   |

### Notes:

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

2. Data based on characterisation results, not tested in production.

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

| Supplier | f <sub>osc</sub><br>(MHz) | Typical Ceramic Resonators <sup>2)</sup> |                      |

|----------|---------------------------|------------------------------------------|----------------------|

|          | 2                         | CSTCC2M00G56Z-R0                         |                      |

|          | <del>ر</del> ل            | 4                                        | SMD CSTCR4M00G53Z-R0 |

| ŋ        |                           | Lead CSTLS4M00G53Z-R0                    |                      |

| urat     | Murata<br>8               |                                          | SMD CSTCE8M00G52Z-R0 |

| Ē        |                           | Lead CSTLS4M0052Z-R0                     |                      |

|          | 16                        | SMD CSTCE16M0V51Z-R0                     |                      |

|          | 10                        | Lead CSTLS16M0X51Z-R0                    |                      |

### Notes:

1. Resonator characteristics given by the ceramic resonator manufacturer.

2. SMD = [-R0: Plastic tape package (∅ =180mm), -B0: Bulk] LEAD = [-A0: Flat pack package (Radial taping Ho= 18mm), -B0: Bulk]

For more information on these resonators, please consult www.murata.com

## **13.2 THERMAL CHARACTERISTICS**

| Symbol            | Ratings                                          | Value | Unit |

|-------------------|--------------------------------------------------|-------|------|

|                   | Package thermal resistance (junction to ambient) |       |      |

|                   | LQFP64 10x10                                     | 50    |      |

|                   | LQFP48 7x7                                       | 80    |      |

| R <sub>thJA</sub> | LQFP44 10x10                                     | 52    | °C/W |

|                   | SDIP42                                           | 55    |      |

|                   | LQFP32 7x7                                       | 70    |      |

|                   | SDIP32                                           | 50    |      |

| PD                | Power dissipation <sup>1)</sup>                  | 500   | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>2)</sup>       | 150   | °C   |

### Notes:

1. The maximum chip-junction temperature is based on technology characteristics.

2. The maximum power dissipation is obtained from the formula PD = (TJ - TA) / RthJA.

The power dissipation of an application can be defined by the user with the formula: PD=PINT+PPORT where PINT is the chip internal power (IDDxVDD) and PPORT is the port power dissipation depending on the ports used in the application.

# 14.4 ST7 APPLICATION NOTES

# Table 32. ST7 Application Notes

| IDENTIFICATION | DESCRIPTION                                                                                 |

|----------------|---------------------------------------------------------------------------------------------|

| APPLICATION EX | AMPLES                                                                                      |

| AN1658         | SERIAL NUMBERING IMPLEMENTATION                                                             |

| AN1720         | MANAGING THE READ-OUT PROTECTION IN FLASH MICROCONTROLLERS                                  |

| AN1755         | A HIGH RESOLUTION/PRECISION THERMOMETER USING ST7 AND NE555                                 |

| AN1756         | CHOOSING A DALI IMPLEMENTATION STRATEGY WITH ST7DALI                                        |

| AN1812         | A HIGH PRECISION, LOW COST, SINGLE SUPPLY ADC FOR POSITIVE AND NEGATIVE IN-<br>PUT VOLTAGES |

| EXAMPLE DRIVE  | RS                                                                                          |

| AN 969         | SCI COMMUNICATION BETWEEN ST7 AND PC                                                        |

| AN 970         | SPI COMMUNICATION BETWEEN ST7 AND EEPROM                                                    |

| AN 971         | I <sup>2</sup> C COMMUNICATION BETWEEN ST7 AND M24CXX EEPROM                                |

| AN 972         | ST7 SOFTWARE SPI MASTER COMMUNICATION                                                       |

| AN 973         | SCI SOFTWARE COMMUNICATION WITH A PC USING ST72251 16-BIT TIMER                             |

| AN 974         | REAL TIME CLOCK WITH ST7 TIMER OUTPUT COMPARE                                               |

| AN 976         | DRIVING A BUZZER THROUGH ST7 TIMER PWM FUNCTION                                             |

| AN 979         | DRIVING AN ANALOG KEYBOARD WITH THE ST7 ADC                                                 |

| AN 980         | ST7 KEYPAD DECODING TECHNIQUES, IMPLEMENTING WAKE-UP ON KEYSTROKE                           |

| AN1017         | USING THE ST7 UNIVERSAL SERIAL BUS MICROCONTROLLER                                          |

| AN1041         | USING ST7 PWM SIGNAL TO GENERATE ANALOG OUTPUT (SINUSOÏD)                                   |

| AN1042         | ST7 ROUTINE FOR I <sup>2</sup> C SLAVE MODE MANAGEMENT                                      |

| AN1044         | MULTIPLE INTERRUPT SOURCES MANAGEMENT FOR ST7 MCUS                                          |

| AN1045         | ST7 S/W IMPLEMENTATION OF I <sup>2</sup> C BUS MASTER                                       |

| AN1046         | UART EMULATION SOFTWARE                                                                     |

| AN1047         | MANAGING RECEPTION ERRORS WITH THE ST7 SCI PERIPHERALS                                      |

| AN1048         | ST7 SOFTWARE LCD DRIVER                                                                     |

| AN1078         | PWM DUTY CYCLE SWITCH IMPLEMENTING TRUE 0% & 100% DUTY CYCLE                                |

| AN1082         | DESCRIPTION OF THE ST72141 MOTOR CONTROL PERIPHERALS REGISTERS                              |

| AN1083         | ST72141 BLDC MOTOR CONTROL SOFTWARE AND FLOWCHART EXAMPLE                                   |

| AN1105         | ST7 PCAN PERIPHERAL DRIVER                                                                  |

| AN1129         | PWM MANAGEMENT FOR BLDC MOTOR DRIVES USING THE ST72141                                      |

| AN1130         | AN INTRODUCTION TO SENSORLESS BRUSHLESS DC MOTOR DRIVE APPLICATIONS WITH THE ST72141        |

| AN1148         | USING THE ST7263 FOR DESIGNING A USB MOUSE                                                  |

| AN1149         | HANDLING SUSPEND MODE ON A USB MOUSE                                                        |

| AN1180         | USING THE ST7263 KIT TO IMPLEMENT A USB GAME PAD                                            |

| AN1276         | BLDC MOTOR START ROUTINE FOR THE ST72141 MICROCONTROLLER                                    |

| AN1321         | USING THE ST72141 MOTOR CONTROL MCU IN SENSOR MODE                                          |

| AN1325         | USING THE ST7 USB LOW-SPEED FIRMWARE V4.X                                                   |

| AN1445         | EMULATED 16-BIT SLAVE SPI                                                                   |

| AN1475         | DEVELOPING AN ST7265X MASS STORAGE APPLICATION                                              |

| AN1504         | STARTING A PWM SIGNAL DIRECTLY AT HIGH LEVEL USING THE ST7 16-BIT TIMER                     |

| AN1602         | 16-BIT TIMING OPERATIONS USING ST7262 OR ST7263B ST7 USB MCUS                               |

| AN1633         | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION IN ST7 NON-USB APPLICATIONS                    |

| AN1712         | GENERATING A HIGH RESOLUTION SINEWAVE USING ST7 PWMART                                      |

| AN1713         | SMBUS SLAVE DRIVER FOR ST7 I2C PERIPHERALS                                                  |

| AN1753         | SOFTWARE UART USING 12-BIT ART                                                              |

# Table 32. ST7 Application Notes

| IDENTIFICATION      | DESCRIPTION                                                                          |  |  |

|---------------------|--------------------------------------------------------------------------------------|--|--|

| AN1071              | HALF DUPLEX USB-TO-SERIAL BRIDGE USING THE ST72611 USB MICROCONTROLLER               |  |  |

| AN1106              | TRANSLATING ASSEMBLY CODE FROM HC05 TO ST7                                           |  |  |

| AN1179              | PROGRAMMING ST7 FLASH MICROCONTROLLERS IN REMOTE ISP MODE (IN-SITU PRO-<br>GRAMMING) |  |  |

| AN1446              | USING THE ST72521 EMULATOR TO DEBUG AN ST72324 TARGET APPLICATION                    |  |  |

| AN1477              | EMULATED DATA EEPROM WITH XFLASH MEMORY                                              |  |  |

| AN1527              | DEVELOPING A USB SMARTCARD READER WITH ST7SCR                                        |  |  |

| AN1575              | ON-BOARD PROGRAMMING METHODS FOR XFLASH AND HDFLASH ST7 MCUS                         |  |  |

| AN1576              | IN-APPLICATION PROGRAMMING (IAP) DRIVERS FOR ST7 HDFLASH OR XFLASH MCUS              |  |  |

| AN1577              | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION FOR ST7 USB APPLICATIONS                |  |  |

| AN1601              | SOFTWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |  |  |

| AN1603              | USING THE ST7 USB DEVICE FIRMWARE UPGRADE DEVELOPMENT KIT (DFU-DK)                   |  |  |

| AN1635              | ST7 CUSTOMER ROM CODE RELEASE INFORMATION                                            |  |  |

| AN1754              | DATA LOGGING PROGRAM FOR TESTING ST7 APPLICATIONS VIA ICC                            |  |  |

| AN1796              | FIELD UPDATES FOR FLASH BASED ST7 APPLICATIONS USING A PC COMM PORT                  |  |  |

| AN1900              | HARDWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |  |  |

| AN1904              | ST7MC THREE-PHASE AC INDUCTION MOTOR CONTROL SOFTWARE LIBRARY                        |  |  |

| AN1905              | ST7MC THREE-PHASE BLDC MOTOR CONTROL SOFTWARE LIBRARY                                |  |  |

| SYSTEM OPTIMIZATION |                                                                                      |  |  |

| AN1711              | SOFTWARE TECHNIQUES FOR COMPENSATING ST7 ADC ERRORS                                  |  |  |

| AN1827              | IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09                                 |  |  |

| AN2009              | PWM MANAGEMENT FOR 3-PHASE BLDC MOTOR DRIVES USING THE ST7FMC                        |  |  |

| AN2030              | BACK EMF DETECTION DURING PWM ON TIME BY ST7MC                                       |  |  |

# **16 REVISION HISTORY**

# Table 33. Revision History

| Date        | Revision | Description of Changes                                                                                                                        |  |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 26-Sep-2005 | 1        | Initial release                                                                                                                               |  |  |

| 04-Dec-2006 |          | Modified LQFP48 pinout, added S device ordering information                                                                                   |  |  |

|             |          | Modified Note 4 on page 16 for unbonded pins in 48 pin C devices                                                                              |  |  |

|             | 2        | Added caution about reset vector in unprogrammed Flash devices in Section 6.3.                                                                |  |  |

|             |          | Removed EMC protective circuitry in Figure 88 on page 163 (device works correctly without these components)                                   |  |  |

|             |          | Modified SS min. setup time and added note 4 to section 12.11.1 on page 166                                                                   |  |  |

|             |          | Modifed description PKG1 bit in "FLASH OPTION BYTES" on page 181                                                                              |  |  |

|             |          | Added "TIMD set simultaneously with OC interrupt" on page 194                                                                                 |  |  |

|             | 3        | In Table 2 added note 5 for I/O Port E2 (PE2) output mode "pull-up always activated" and added note 6 on connection of power and ground pins. |  |  |

| 04 4        |          | Deleted the sentence in Section 4.3.1 'Readout protection is not supported if LVD is enabled                                                  |  |  |

| 04-Apr-2007 |          | Added Package dimensions for LQFP64 14 x14 in Figure 122                                                                                      |  |  |

|             |          | Specified EMI data for LQFP64 in Section 12.7.2                                                                                               |  |  |

|             |          | Added 'Pull-up always active on PE2' in Section 15.1.8                                                                                        |  |  |

|             |          | Title of the document changed                                                                                                                 |  |  |

|             |          | Modified Table 1 on page 1<br>Modified "Starting the Conversion" on page 133                                                                  |  |  |

|             |          | Modified t <sub>RET</sub> and N <sub>RW</sub> values in "FLASH Memory" on page 155                                                            |  |  |

|             | 4        | Modified "Absolute Maximum Ratings (Electrical Sensitivity)" on page 158                                                                      |  |  |

| 07.0.4.0000 |          | Values in inches rounded to 4 decimal digits (instead of 3) in "PACKAGE MECHANICAL DA-                                                        |  |  |

| 07-Oct-2008 |          | TA" on page 174<br>Removed reference to "Application with a Crystal or Ceramic Resonator for ROM (LQFP64                                      |  |  |

|             |          | or any 48/60K ROM)" on page 151                                                                                                               |  |  |

|             |          | Modified "PACKAGE CHARACTERISTICS" on page 174 (Section 13.3)                                                                                 |  |  |

|             |          | Modified "TIMD set simultaneously with OC interrupt" on page 194                                                                              |  |  |

|             |          | Modified Section 14.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUS-<br>TOMER CODE on page 183 (Figure 106 and option lists)                |  |  |

|             |          | TOWER CODE OF Page Too (Figure Too and option lists)                                                                                          |  |  |