Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 32                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                            |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f325j6b6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents —

|        | CRIPTION                                        |    |

|--------|-------------------------------------------------|----|

|        | DESCRIPTION                                     |    |

|        | STER & MEMORY MAP                               |    |

|        | SH PROGRAM MEMORY                               |    |

|        | INTRODUCTION                                    |    |

|        | MAIN FEATURES                                   |    |

| 4.3    | STRUCTURE                                       |    |

|        | 4.3.1 Read-out Protection                       |    |

|        | ICC INTERFACE                                   |    |

|        | ICP (IN-CIRCUIT PROGRAMMING)                    |    |

|        | IAP (IN-APPLICATION PROGRAMMING)                |    |

| 4.7    | RELATED DOCUMENTATION                           |    |

|        | 4.7.1 Register Description                      |    |

|        | TRAL PROCESSING UNIT                            |    |

|        | INTRODUCTION                                    |    |

|        | MAIN FEATURES                                   |    |

|        | CPU REGISTERS                                   |    |

|        | PLY, RESET AND CLOCK MANAGEMENT                 |    |

|        | PHASE LOCKED LOOP                               |    |

|        | MULTI-OSCILLATOR (MO)                           |    |

| 6.3    | RESET SEQUENCE MANAGER (RSM)                    | 29 |

|        | 6.3.1 Introduction                              |    |

|        | 6.3.2 Asynchronous External RESET pin           |    |

|        | 6.3.3 External Power-On RESET                   |    |

|        | 6.3.4 Internal Low Voltage Detector (LVD) RESET |    |

| 6.4    | SYSTEM INTEGRITY MANAGEMENT (SI)                |    |

| 0.4    | 6.4.1 Low Voltage Detector (LVD)                |    |

|        | 6.4.2 Auxiliary Voltage Detector (AVD)          |    |

|        | 6.4.3 Clock Security System (CSS)               |    |

|        | 6.4.4 Low Power Modes                           |    |

|        | 6.4.5 Register Description                      |    |

| 7 INTE | RRUPTS                                          | 36 |

| 7.1    | INTRODUCTION                                    | 36 |

| 7.2    | MASKING AND PROCESSING FLOW                     | 36 |

| 7.3    | INTERRUPTS AND LOW POWER MODES                  | 38 |

| 7.4    | CONCURRENT & NESTED MANAGEMENT                  | 38 |

| 7.5    | INTERRUPT REGISTER DESCRIPTION                  | 39 |

|        | EXTERNAL INTERRUPTS                             |    |

| -      | 7.6.1 I/O Port Interrupt Sensitivity            |    |

| 7.7    | EXTERNAL INTERRUPT CONTROL REGISTER (EICR)      |    |

|        | ER SAVING MODES                                 |    |

|        | INTRODUCTION                                    |    |

| 8.2    | SLOW MODE                                       | 45 |

# Table of Contents ——

| 8.3   | WAIT               | MODE                                                       | . 46 |

|-------|--------------------|------------------------------------------------------------|------|

| 8.4   | ACTIV              | E-HALT AND HALT MODES                                      | . 47 |

|       | 8.4.1              | ACTIVE-HALT MODE                                           |      |

| - ··- |                    | HALT MODE                                                  |      |

|       |                    |                                                            |      |

|       |                    | DUCTION                                                    |      |

| 9.2   | FUNC               | FIONAL DESCRIPTION                                         | . 50 |

|       | 9.2.1              | Input Modes                                                | . 50 |

|       | 9.2.2              | Output Modes                                               |      |

|       | 9.2.3              | Alternate Functions                                        |      |

|       |                    | RT IMPLEMENTATION                                          |      |

|       |                    | POWER MODES                                                |      |

| 9.5   | INTER              | RUPTS                                                      | . 53 |

|       | 9.5.1              | I/O Port Implementation                                    | . 54 |

|       |                    | ERIPHERALS                                                 |      |

| 10.   | 1 WATC             | HDOG TIMER (WDG)                                           | . 56 |

|       | 10.1.1             | Introduction                                               | . 56 |

|       | 10.1.2             | Main Features                                              | . 56 |

|       |                    | Functional Description                                     |      |

|       |                    | How to Program the Watchdog Timeout                        |      |

|       |                    | Low Power Modes                                            |      |

|       |                    | Hardware Watchdog Option                                   |      |

|       |                    | Using Halt Mode with the WDG (WDGHALT option)              |      |

|       |                    | Interrupts                                                 |      |

| 10    |                    | Register Description                                       |      |

| 10.   |                    | CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) |      |

|       |                    | Programmable CPU Clock Prescaler                           |      |

|       | 10.2.2             | Clock-out Capability                                       | . 61 |

|       |                    | Real Time Clock Timer (RTC)                                |      |

|       |                    | Beeper                                                     |      |

|       |                    | Low Power Modes                                            |      |

|       |                    | Register Description                                       |      |

| 10    |                    | AUTO-RELOAD TIMER (ART)                                    |      |

| 10.   |                    | Introduction                                               |      |

|       |                    | Functional Description                                     |      |

|       |                    | Register Description                                       |      |

| 10    | 16.5.5<br>4 16-BIT | e ·                                                        |      |

| 10.   | 10.4.1             | Introduction                                               |      |

|       |                    | Main Features                                              | _    |

|       |                    | Functional Description                                     |      |

|       |                    | Low Power Modes                                            |      |

|       |                    | Interrupts                                                 |      |

|       |                    | Summary of Timer Modes                                     |      |

|       |                    | Register Description                                       |      |

| 10.   |                    | L PERIPHERAL INTERFACE (SPI)                               |      |

# Table of Contents —

| 13.3 SOLDE              | RING INFORMATION                                     | 180 |

|-------------------------|------------------------------------------------------|-----|

| 14 ST72325 DI           | EVICE CONFIGURATION AND ORDERING INFORMATION         | 181 |

| 14.1 FLASH              | OPTION BYTES                                         | 181 |

| 14.2 DEVIC              | E ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE | 183 |

| 14.3 DEVEL              | OPMENT TOOLS                                         | 187 |

| 14.3.1                  | Starter kits                                         | 187 |

|                         | Development and debugging tools                      |     |

| 14.3.3                  | Programming tools                                    | 187 |

|                         | Socket and Emulator Adapter Information              |     |

| 14.4 ST7 AF             | PLICATION NOTES                                      | 189 |

| 15 KNOWN LII            | MITATIONS                                            | 192 |

| 15.1 ALL DE             | EVICES                                               | 192 |

| 15.1.1                  | Unexpected Reset Fetch                               | 192 |

| 15.1.2                  | External interrupt missed                            | 192 |

|                         | Clearing active interrupts outside interrupt routine |     |

|                         | SCI Wrong Break duration                             |     |

|                         | 16-bit Timer PWM Mode                                |     |

|                         | TIMD set simultaneously with OC interrupt            |     |

| 15.1.7                  | 120 Waltimactor                                      |     |

|                         | Pull-up always active on PE2                         |     |

| 15.1.9<br>16 REVISION I | ADC accuracy 16/32K Flash devices                    | 195 |

|                         |                                                      |     |

#### **SYSTEM INTEGRITY MANAGEMENT** (Cont'd)

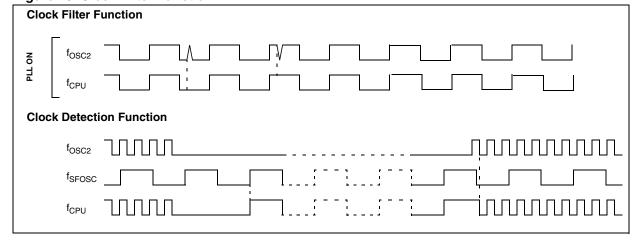

#### 6.4.3 Clock Security System (CSS)

The Clock Security System (CSS) protects the ST7 against breakdowns, spikes and overfrequencies occurring on the main clock source ( $f_{OSC}$ ). It is based on a clock filter and a clock detection control with an internal safe oscillator ( $f_{SFOSC}$ ).

#### 6.4.3.1 Clock Filter Control

The PLL has an integrated glitch filtering capability making it possible to protect the internal clock from overfrequencies created by individual spikes. This feature is available only when the PLL is enabled. If glitches occur on  $f_{OSC}$  (for example, due to loose connection or noise), the CSS filters these automatically, so the internal CPU frequency ( $f_{CPU}$ ) continues deliver a glitch-free signal (see Figure 20).

#### 6.4.3.2 Clock detection Control

If the clock signal disappears (due to a broken or disconnected resonator...), the safe oscillator delivers a low frequency clock signal (f<sub>SFOSC</sub>) which allows the ST7 to perform some rescue operations.

Automatically, the ST7 clock source switches back from the safe oscillator ( $f_{SFOSC}$ ) if the main clock source ( $f_{OSC}$ ) recovers.

When the internal clock ( $f_{CPU}$ ) is driven by the safe oscillator ( $f_{SFOSC}$ ), the application software is notified by hardware setting the CSSD bit in the SIC-SR register. An interrupt can be generated if the

CSSIE bit has been previously set.

These two bits are described in the SICSR register description.

#### 6.4.4 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SI. CSS and AVD interrupts cause the device to exit from Wait mode.                                                                                                                                                                                                                        |

| HALT | The SICSR register is frozen. The CSS (including the safe oscillator) is disabled until HALT mode is exited. The previous CSS configuration resumes when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET. |

#### 6.4.4.1 Interrupts

The CSS or AVD interrupt events generate an interrupt if the corresponding Enable Control Bit (CSSIE or AVDIE) is set and the interrupt mask in the CC register is reset (RIM instruction).

| Interrupt Event                                                  | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|------------------------------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| CSS event detection<br>(safe oscillator activated as main clock) | CSSD          | CSSIE                    | Yes                  | No                   |

| AVD event                                                        | AVDF          | AVDIE                    | Yes                  | No                   |

Figure 20. Clock Filter Function

34/197

#### **SYSTEM INTEGRITY MANAGEMENT (Cont'd)**

#### 6.4.5 Register Description

#### SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

Read/Write

Reset Value: 000x 000x (00h)

7 0

| AVD | AVD | AVD | LVD | 0 | CSS | CSS | WDG |

|-----|-----|-----|-----|---|-----|-----|-----|

| S   | ΙE  | F   | RF  | U | ΙE  | D   | RF  |

#### Bit 7 = **AVDS** Voltage Detection selection

This bit is set and cleared by software. Voltage Detection is available only if the LVD is enabled by option byte.

0: Voltage detection on  $\underline{V}_{D\underline{D}}$  supply

1: Voltage detection on EVD pin

Bit 6 = **AVDIE** Voltage Detector interrupt enable

This bit is set and cleared by software. It enables

an interrupt to be generated when the AVDF flag

changes (toggles). The pending interrupt information is automatically cleared when software enters

the AVD interrupt routine.

0: AVD interrupt disabled

1: AVD interrupt enabled

#### Bit 5 = **AVDF** Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to Figure 18 and to Section 6.4.2.1 for additional details.

0:  $V_{DD}$  or  $V_{EVD}$  over  $V_{IT+(AVD)}$  threshold 1:  $V_{DD}$  or  $V_{EVD}$  under  $V_{IT-(AVD)}$  threshold

### Bit 4 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag description for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

Bit 3 = Reserved, must be kept cleared.

Bit 2 = **CSSIE** Clock security syst interrupt enable This bit enables the interrupt when a disturbance is detected by the Clock Security System (CSSD bit set). It is set and cleared by software.

0: Clock security system interrupt disabled

1: Clock security system interrupt enabled

When the CSS is disabled by OPTION BYTE, the CSSIE bit has no effect.

#### Bit 1 = CSSD Clock security system detection

This bit indicates that the safe oscillator of the Clock Security System block has been selected by hardware due to a disturbance on the main clock signal (f<sub>OSC</sub>). It is set by hardware and cleared by reading the SICSR register when the original oscillator recovers.

0: Safe oscillator is not active

1: Safe oscillator has been activated

When the CSS is disabled by OPTION BYTE, the CSSD bit value is forced to 0.

# Bit 0 = WDGRF Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| RESET Sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

#### **Application notes**

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

**CAUTION:** When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

# INTERRUPTS (Cont'd)

Figure 25. External Interrupt Control bits

**57**

# I/O PORTS (Cont'd)

# 9.5.1 I/O Port Implementation

The I/O port register configurations are summarised as follows.

#### **Standard Ports**

# PA5:4, PC7:0, PD7:0, PE7:3, PE1:0, PF7:3,

| MODE              | DDR | OR |

|-------------------|-----|----|

| floating input    | 0   | 0  |

| pull-up input     | 0   | 1  |

| open drain output | 1   | 0  |

| push-pull output  | 1   | 1  |

# **Interrupt Ports**

# PA2:0, PB6:5, PB4, PB2:0, PF1:0 (with pull-up)

| MODE                    | DDR | OR |

|-------------------------|-----|----|

| floating input          | 0   | 0  |

| pull-up interrupt input | 0   | 1  |

| open drain output       | 1   | 0  |

| push-pull output        | 1   | 1  |

| MODE                     | DDR | OR |

|--------------------------|-----|----|

| floating input           | 0   | 0  |

| floating interrupt input | 0   | 1  |

| open drain output        | 1   | 0  |

| push-pull output         | 1   | 1  |

# **True Open Drain Ports PA7:6**

| MODE                         | DDR |

|------------------------------|-----|

| floating input               | 0   |

| open drain (high sink ports) | 1   |

# **Pull-Up Input Port PE2**

| MODE               | DDR | OR |

|--------------------|-----|----|

| pull-up input      | 0   | Х  |

| open drain output* | 1   | 0  |

| push-pull output*  | 1   | 1  |

**Table 13. Port Configuration**

| Dowl   | Din nama             | <u> </u>           | nput               | Output      |            |  |

|--------|----------------------|--------------------|--------------------|-------------|------------|--|

| Port   | Pin name             | OR = 0             | OR = 1             | OR = 0      | OR = 1     |  |

|        | PA7:6                | floating           |                    | true ope    | en-drain   |  |

| Port A | PA5:4                | floating           | pull-up            | open drain  | push-pull  |  |

| Port A | PA3                  | floating           | floating interrupt | open drain  | push-pull  |  |

|        | PA2:0                | floating           | pull-up interrupt  | open drain  | push-pull  |  |

|        | PB7, PB3             | floating           | floating interrupt | open drain  | push-pull  |  |

| Port B | PB6:5, PB4,<br>PB2:0 | floating           | pull-up interrupt  | open drain  | push-pull  |  |

| Port C | PC7:0                | floating           | pull-up            | open drain  | push-pull  |  |

| Port D | PD7:0                | floating           | pull-up            | open drain  | push-pull  |  |

| Port E | PE7:3, PE1:0         | floating pull-up   |                    | open drain  | push-pull  |  |

| POILE  | PE2                  | pull-up input only |                    | open drain* | push-pull* |  |

|        | PF7:3                | floating           | pull-up            | open drain  | push-pull  |  |

| Port F | PF2                  | floating           | floating interrupt | open drain  | push-pull  |  |

|        | PF1:0                | floating           | pull-up interrupt  | open drain  | push-pull  |  |

<sup>\*</sup>Pull-up always activated on PE2.

47/

#### **16-BIT TIMER** (Cont'd)

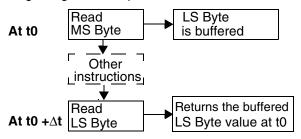

**16-bit read sequence:** (from either the Counter Register or the Alternate Counter Register).

Beginning of the sequence

Sequence completed

The user must read the MS Byte first, then the LS Byte value is buffered automatically.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MS Byte several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LS Byte of the count value at the time of the read.

Whatever the timer mode used (input capture, output compare, One Pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h then:

- The TOF bit of the SR register is set.

- A timer interrupt is generated if:

- TOIE bit of the CR1 register is set and

- I bit of the CC register is cleared.

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true.

Clearing the overflow interrupt request is done in two steps:

- 1. Reading the SR register while the TOF bit is set.

- 2. An access (read or write) to the CLR register.

**Notes:** The TOF bit is not cleared by accesses to ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by WAIT mode.

In HALT mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a Reset).

#### 10.4.3.2 External Clock

The external clock (where available) is selected if CC0 = 1 and CC1 = 1 in the CR2 register.

The status of the EXEDG bit in the CR2 register determines the type of level transition on the external clock pin EXTCLK that will trigger the free running counter.

The counter is synchronized with the falling edge of the internal CPU clock.

A minimum of four falling edges of the CPU clock must occur between two consecutive active edges of the external clock; thus the external clock frequency must be less than a quarter of the CPU clock frequency.

# SERIAL PERIPHERAL INTERFACE (Cont'd)

Table 21. SPI Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------|-------------------|------|------|------|------|------|------|------|------|

| 0021h             | SPIDR             | MSB  |      |      |      |      |      |      | LSB  |

|                   | Reset Value       | Х    | Х    | Х    | Х    | Х    | Х    | Х    | x    |

| 0022h             | SPICR             | SPIE | SPE  | SPR2 | MSTR | CPOL | CPHA | SPR1 | SPR0 |

|                   | Reset Value       | 0    | 0    | 0    | 0    | Х    | Х    | Х    | Х    |

| 0023h             | SPICSR            | SPIF | WCOL | OVR  | MODF |      | SOD  | SSM  | SSI  |

|                   | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

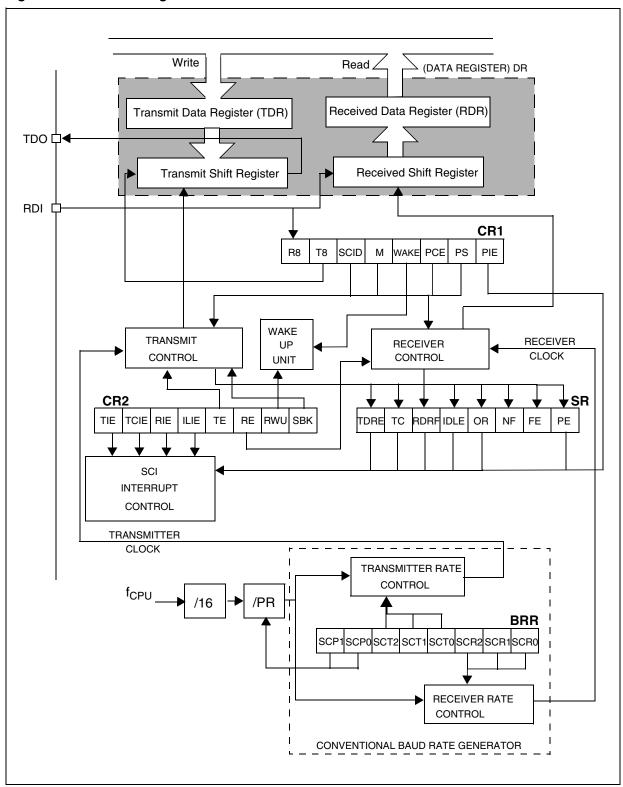

Figure 63. SCI Block Diagram

# **SERIAL COMMUNICATIONS INTERFACE** (Cont'd) **10.6.4 Functional Description**

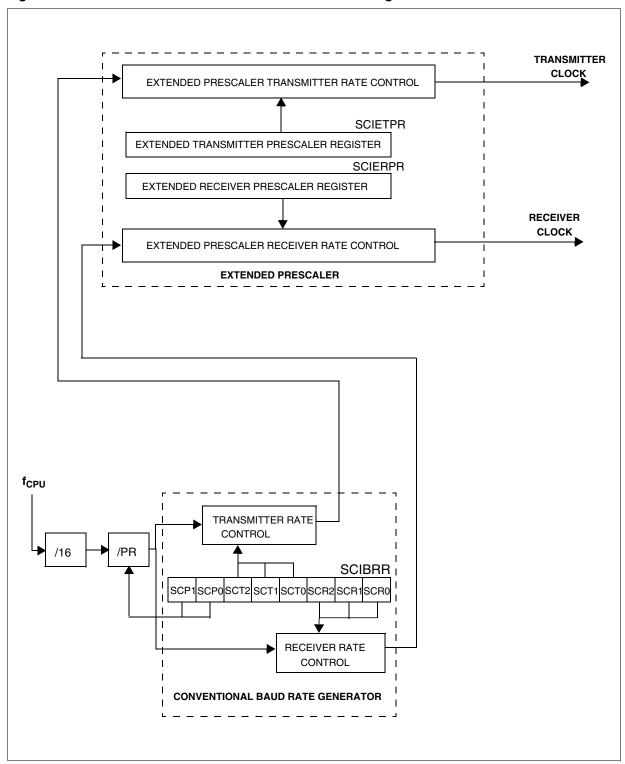

The block diagram of the Serial Control Interface, is shown in Figure 1. It contains six dedicated registers:

- Two control registers (SCICR1 & SCICR2)

- A status register (SCISR)

- A baud rate register (SCIBRR)

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

Refer to the register descriptions in Section 0.1.7 for the definitions of each bit.

#### 10.6.4.1 Serial Data Format

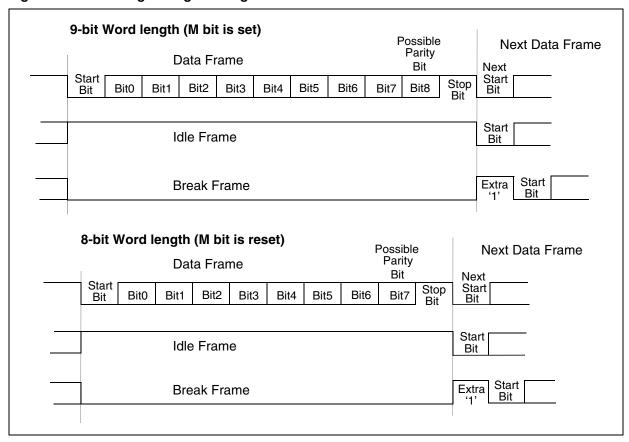

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 1.).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of "1"s followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving "0"s for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra "1" bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

Figure 64. Word Length Programming

#### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.6.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 1.).

#### **Procedure**

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to assign the TDO pin to the alternate function and to send a idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set.

When a frame transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

- An access to the SCISR register

- 2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 2.).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### Idle Characters

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

Figure 65. SCI Baud Rate and Extended Prescaler Block Diagram

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

#### **Master Transmitter**

Following the address transmission and after SR1 register has been read, the master sends bytes from the DR register to the SDA line via the internal shift register.

The master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 69 Transfer sequencing EV8).

When the acknowledge bit is received, the interface sets:

EVF and BTF bits with an interrupt if the ITE bit is set

To close the communication: after writing the last byte to the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

#### **Error Cases**

BERR: Detection of a Stop or a Start condition during a byte transfer. In this case, the EVF and BERR bits are set by hardware with an interrupt if ITE is set.

Note that BERR will not be set if an error is detected during the first or second pulse of each 9-bit transaction:

Single Master Mode

If a Start or Stop is issued during the first or second pulse of a 9-bit transaction, the BERR flag will not be set and transfer will continue however the BUSY flag will be reset. To work around this, slave devices should issue a NACK when they receive a misplaced Start or Stop. The reception of a NACK or BUSY by the master in the middle

of communication gives the possibility to reinitiate transmission.

Multimaster Mode

Normally the BERR bit would be set whenever unauthorized transmission takes place while transfer is already in progress. However, an issue will arise if an external master generates an unauthorized Start or Stop while the I<sup>2</sup>C master is on the first or second pulse of a 9-bit transaction. It is possible to work around this by polling the BUSY bit during I<sup>2</sup>C master mode transmission. The resetting of the BUSY bit can then be handled in a similar manner as the BERR flag being set.

AF: Detection of a non-acknowledge bit. In this case, the EVF and AF bits are set by hardware with an interrupt if the ITE bit is set. To resume, set the Start or Stop bit.

The AF bit is cleared by reading the I2CSR2 register. However, if read before the completion of the transmission, the AF flag will be set again, thus possibly generating a new interrupt. Software must ensure either that the SCL line is back at 0 before reading the SR2 register, or be able to correctly handle a second interrupt during the 9th pulse of a transmitted byte.

ARLO: Detection of an arbitration lost condition. In this case the ARLO bit is set by hardware (with an interrupt if the ITE bit is set and the interface goes automatically back to slave mode (the M/SL bit is cleared).

**Note**: In all these cases, the SCL line is not held low; however, the SDA line can remain low due to possible «0» bits transmitted last. It is then necessary to release both lines by software.

# INSTRUCTION SET OVERVIEW (Cont'd)

| Mnemo | Description                 | Function/Example    | Dst    | Src | l1 | Н |    |

|-------|-----------------------------|---------------------|--------|-----|----|---|----|

| ADC   | Add with Carry              | A = A + M + C       | Α      | М   |    | Н |    |

| ADD   | Addition                    | A = A + M           | Α      | М   |    | Н |    |

| AND   | Logical And                 | A = A . M           | Α      | М   |    |   |    |

| ВСР   | Bit compare A, Memory       | tst (A . M)         | Α      | М   |    |   |    |

| BRES  | Bit Reset                   | bres Byte, #3       | М      |     |    |   |    |

| BSET  | Bit Set                     | bset Byte, #3       | М      |     |    |   |    |

| BTJF  | Jump if bit is false (0)    | btjf Byte, #3, Jmp1 | М      |     |    |   |    |

| BTJT  | Jump if bit is true (1)     | btjt Byte, #3, Jmp1 | М      |     |    |   |    |

| CALL  | Call subroutine             |                     |        |     |    |   |    |

| CALLR | Call subroutine relative    |                     |        |     |    |   |    |

| CLR   | Clear                       |                     | reg, M |     |    |   |    |

| СР    | Arithmetic Compare          | tst(Reg - M)        | reg    | М   |    |   |    |

| CPL   | One Complement              | A = FFH-A           | reg, M |     |    |   |    |

| DEC   | Decrement                   | dec Y               | reg, M |     |    |   |    |

| HALT  | Halt                        |                     |        |     | 1  |   | (  |

| IRET  | Interrupt routine return    | Pop CC, A, X, PC    |        |     | 11 | Н | 10 |

| INC   | Increment                   | inc X               | reg, M |     |    |   |    |

| JP    | Absolute Jump               | jp [TBL.w]          |        |     |    |   |    |

| JRA   | Jump relative always        |                     |        |     |    |   |    |

| JRT   | Jump relative               |                     |        |     |    |   |    |

| JRF   | Never jump                  | jrf *               |        |     |    |   |    |

| JRIH  | Jump if ext. INT pin = 1    | (ext. INT pin high) |        |     |    |   |    |

| JRIL  | Jump if ext. INT pin = 0    | (ext. INT pin low)  |        |     |    |   |    |

| JRH   | Jump if H = 1               | H = 1 ?             |        |     |    |   |    |

| JRNH  | Jump if H = 0               | H = 0 ?             |        |     |    |   |    |

| JRM   | Jump if I1:0 = 11           | I1:0 = 11 ?         |        |     |    |   |    |

| JRNM  | Jump if I1:0 <> 11          | l1:0 <> 11 ?        |        |     |    |   |    |

| JRMI  | Jump if N = 1 (minus)       | N = 1 ?             |        |     |    |   |    |

| JRPL  | Jump if N = 0 (plus)        | N = 0 ?             |        |     |    |   |    |

| JREQ  | Jump if Z = 1 (equal)       | Z = 1 ?             |        |     |    |   |    |

| JRNE  | Jump if $Z = 0$ (not equal) | Z = 0 ?             |        |     |    |   |    |

| JRC   | Jump if C = 1               | C = 1 ?             |        |     |    |   |    |

| JRNC  | Jump if C = 0               | C = 0 ?             |        |     |    |   |    |

| JRULT | Jump if C = 1               | Unsigned <          |        |     |    |   |    |

| JRUGE | Jump if C = 0               | Jmp if unsigned >=  |        |     |    |   |    |

| JRUGT | Jump if $(C + Z = 0)$       | Unsigned >          |        |     |    |   |    |

Z

Ζ

Ζ

Ζ

Z

Z

Ζ

Z

Z

Z

С

С

С

C

С

1

С

140/197

## **CONTROL PIN CHARACTERISTICS** (Cont'd)

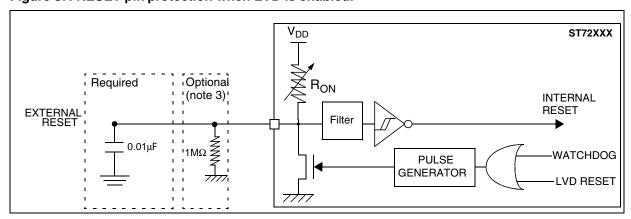

Figure 87. RESET pin protection when LVD is enabled. (1)2)3)4)

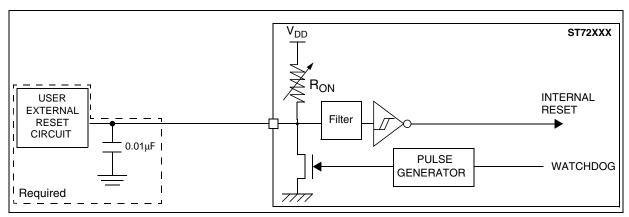

Figure 88. RESET pin protection when LVD is disabled.<sup>1)</sup>

#### Note 1:

- The reset network protects the device against parasitic resets.

- The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the

device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

- Whatever the reset source is (internal or external), the user must ensure that the level on the RESET pin can go below the V<sub>IL</sub> max. level specified in section 12.9.1 on page 162. Otherwise the reset will not be taken into account internally.

- Because the reset circuit is designed to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin is less than the absolute maximum value specified for I<sub>INJ(RESET)</sub> in section 12.2.2 on page 143.

Note 2: When the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

**Note 3:** In case a capacitive power supply is used, it is recommended to connect a  $1M\Omega$  pull-down resistor to the  $\overline{\text{RESET}}$  pin to discharge any residual voltage induced by the capacitive effect of the power supply (this will add  $5\mu\text{A}$  to the power consumption of the MCU).

Note 4: Tips when using the LVD:

- 1. Check that all recommendations related to reset circuit have been applied (see notes above).

- 2. Check that the power supply is properly decoupled (100nF + 10µF close to the MCU). Refer to AN1709 and AN2017. If this cannot be done, it is recommended to put a 100nF +  $1M\Omega$  pull-down on the RESET pin.

- 3. The capacitors connected on the RESET pin and also the power supply are key to avoid any start-up marginality.

In most cases, steps 1 and 2 above are sufficient for a robust solution. Otherwise: replace 10nF pull-down on the RESET pin with a 5μF to 20μF capacitor.

## 12.10 TIMER PERIPHERAL CHARACTERISTICS

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output...).

## 12.10.1 8-Bit PWM-ART Auto-Reload Timer

| Symbol                | Parameter                    | Conditions                      | Min | Тур | Max                 | Unit             |

|-----------------------|------------------------------|---------------------------------|-----|-----|---------------------|------------------|

| t                     | PWM resolution time          |                                 | 1   |     |                     | t <sub>CPU</sub> |

| T <sub>res(PWM)</sub> | www.resolution.time          | f <sub>CPU</sub> =8MHz          | 125 |     |                     | ns               |

| f <sub>EXT</sub>      | ART external clock frequency |                                 | 0   |     | f <sub>CPU</sub> /2 | MHz              |

| f <sub>PWM</sub>      | PWM repetition rate          |                                 | 0   |     | f <sub>CPU</sub> /2 | IVII IZ          |

| Res <sub>PWM</sub>    | PWM resolution               |                                 |     |     | 8                   | bit              |

| V <sub>OS</sub>       | PWM/DAC output step voltage  | V <sub>DD</sub> =5V, Res=8-bits |     | 20  |                     | mV               |

#### 12.10.2 16-Bit Timer

| Symbol                 | Parameter                      | Conditions             | Min | Тур | Max                 | Unit             |

|------------------------|--------------------------------|------------------------|-----|-----|---------------------|------------------|

| t <sub>w(ICAP)in</sub> | Input capture pulse time       |                        | 1   |     |                     | t <sub>CPU</sub> |

| t <sub>res(PWM)</sub>  | PWM resolution time            |                        | 2   |     |                     | t <sub>CPU</sub> |

|                        |                                | f <sub>CPU</sub> =8MHz | 250 |     |                     | ns               |

| f <sub>EXT</sub>       | Timer external clock frequency |                        | 0   |     | f <sub>CPU</sub> /4 | MHz              |

| f <sub>PWM</sub>       | PWM repetition rate            |                        | 0   |     | f <sub>CPU</sub> /4 | MHz              |

| Res <sub>PWM</sub>     | PWM resolution                 |                        |     |     | 16                  | bit              |

## **COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)**

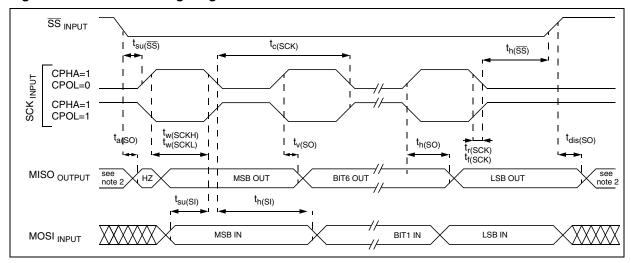

Figure 91. SPI Slave Timing Diagram with CPHA=11)

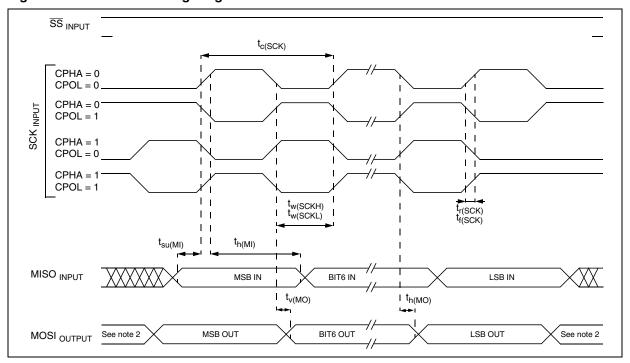

Figure 92. SPI Master Timing Diagram 1)

#### Notes:

- 1. Measurement points are done at CMOS levels:  $0.3 \mathrm{xV}_{\mathrm{DD}}$  and  $0.7 \mathrm{xV}_{\mathrm{DD}}$ .

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

# ST72325 DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

| .020 52 1102 00111                         | ST72325 ROM M                 | IICROCONTROLLER OPTION LIST                  |  |  |  |

|--------------------------------------------|-------------------------------|----------------------------------------------|--|--|--|

| Customer:                                  |                               | t update: October 2008)                      |  |  |  |

| Address:                                   |                               |                                              |  |  |  |

| Contact                                    |                               |                                              |  |  |  |

| Contact:<br>Phone No:                      |                               |                                              |  |  |  |

|                                            |                               |                                              |  |  |  |

| The ROM code name i                        | is assigned by STMicro        | oelectronics.                                |  |  |  |

|                                            |                               | x extension cannot be processed.             |  |  |  |

| Device Type/Memory S                       | Size/Package (check c         | only one option):                            |  |  |  |

| ROM device:                                | - 32K                         | -  <br>_   16K                               |  |  |  |

| LQFP32 7x7:                                | []                            | I [] I                                       |  |  |  |

| SDIP32:                                    | i []                          |                                              |  |  |  |

| LQFP48 7x7:                                | [j                            | ı [j                                         |  |  |  |

| LQFP44 10x10:                              | [j                            |                                              |  |  |  |

| SDIP42:                                    | [j                            | ı [j l                                       |  |  |  |

| Die form:                                  | - 32K                         | <br>  16K                                    |  |  |  |

|                                            |                               | _                                            |  |  |  |

|                                            | []                            | I [] I                                       |  |  |  |

| Conditioning (check or                     | nly one option):              |                                              |  |  |  |

|                                            |                               | Die Product (dice tested at 25°C only)       |  |  |  |

|                                            |                               | ·                                            |  |  |  |

| [] Tape & Reel                             | [] Iray                       | []Tape & Reel                                |  |  |  |

|                                            |                               | [] Inked wafer                               |  |  |  |

|                                            |                               | l [] Sawn wafer on sticky foil               |  |  |  |

| Temp. Range (do not d                      |                               |                                              |  |  |  |

| Temp. Range                                | <del></del>                   |                                              |  |  |  |

| []-40°C to +85°C                           |                               |                                              |  |  |  |

| []-40°C to +125°C                          |                               |                                              |  |  |  |

| []                                         |                               |                                              |  |  |  |

| Special Marking:                           | [] No                         | [] Yes " " (10 char. max)                    |  |  |  |

| Authorized characters                      |                               |                                              |  |  |  |

| Authorized characters                      | are letters, digits, .,       | , / and spaces only.                         |  |  |  |

| Clock Source Selection                     | n: [] Resonato                | or: [] 1 to 2 MHz                            |  |  |  |

|                                            | -                             | [] 2 to 4 MHz                                |  |  |  |

|                                            |                               | [] 4 to 8 MHz                                |  |  |  |

|                                            | <b></b>                       | [] 8 to 16 MHz                               |  |  |  |

|                                            | [] Internal F                 |                                              |  |  |  |

| D                                          | [] External                   |                                              |  |  |  |

| PLL:                                       | [] Disabled                   | [] Enabled                                   |  |  |  |

| CSS:                                       | [] Disabled                   | []Enabled                                    |  |  |  |

| [] Endured                                 |                               |                                              |  |  |  |

| VD Reset: [] Disabl                        |                               |                                              |  |  |  |

| Reset Delay:                               | [] 256 Cycle                  | les [] 4096 Cycles                           |  |  |  |

| Watchdog Šelection:<br>Watchdog Reset on H | []Soπware<br>lalt: []Reset    | Activation [] Hardware Activation            |  |  |  |

| Readout Protection:                        | iait. [] neset<br>[] Disabled |                                              |  |  |  |

|                                            |                               |                                              |  |  |  |

| Date                                       |                               | Signature                                    |  |  |  |

| المام والمام والمرام والمرام والمرام       | tuonolon efilele eel          | . link from .                                |  |  |  |

| ase download the lates                     | t version of this option      | list from:<br>iicrocontrollers > Option list |  |  |  |

| ,.,, w w w.st.com, mca >                   | downloads > 017 m             | norocontrollers > Option list                |  |  |  |

**Table 32. ST7 Application Notes**

| IDENTIFICATION | DESCRIPTION                                                                 |

|----------------|-----------------------------------------------------------------------------|

| AN1947         | ST7MC PMAC SINE WAVE MOTOR CONTROL SOFTWARE LIBRARY                         |

| GENERAL PURPO  | SE                                                                          |

| AN1476         | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                   |

| AN1526         | ST7FLITE0 QUICK REFERENCE NOTE                                              |

| AN1709         | EMC DESIGN FOR ST MICROCONTROLLERS                                          |

| AN1752         | ST72324 QUICK REFERENCE NOTE                                                |

| PRODUCT EVALU  | ATION                                                                       |

| AN 910         | PERFORMANCE BENCHMARKING                                                    |

| AN 990         | ST7 BENEFITS VS INDUSTRY STANDARD                                           |

| AN1077         | OVERVIEW OF ENHANCED CAN CONTROLLERS FOR ST7 AND ST9 MCUS                   |

| AN1086         | U435 CAN-DO SOLUTIONS FOR CAR MULTIPLEXING                                  |

| AN1103         | IMPROVED B-EMF DETECTION FOR LOW SPEED, LOW VOLTAGE WITH ST72141            |

| AN1150         | BENCHMARK ST72 VS PC16                                                      |

| AN1151         | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                           |

| AN1278         | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                  |

| PRODUCT MIGRA  | TION                                                                        |

| AN1131         | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324          |

| AN1322         | MIGRATING AN APPLICATION FROM ST7263 REV.B TO ST7263B                       |

| AN1365         | GUIDELINES FOR MIGRATING ST72C254 APPLICATIONS TO ST72F264                  |

| AN1604         | HOW TO USE ST7MDT1-TRAIN WITH ST72F264                                      |

| AN2200         | GUIDELINES FOR MIGRATING ST7LITE1X APPLICATIONS TO ST7FLITE1XB              |

| PRODUCT OPTIMI |                                                                             |

| AN 982         | USING ST7 WITH CERAMIC RESONATOR                                            |

| AN1014         | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                   |

| AN1015         | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE           |

| AN1040         | MONITORING THE VBUS SIGNAL FOR USB SELF-POWERED DEVICES                     |

| AN1070         | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                       |

| AN1181         | ELECTROSTATIC DISCHARGE SENSITIVE MEASUREMENT                               |

| AN1324         | CALIBRATING THE RC OSCILLATOR OF THE ST7FLITE0 MCU USING THE MAINS          |

| AN1502         | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                |

| AN1529         | EXTENDING THE CURRENT & VOLTAGE CAPABILITY ON THE ST7265 VDDF SUPPLY        |

| AN1530         | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLATOR |

| AN1605         | USING AN ACTIVE RC TO WAKEUP THE ST7LITE0 FROM POWER SAVING MODE            |

| AN1636         | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                          |

| AN1828         | PIR (PASSIVE INFRARED) DETECTOR USING THE ST7FLITE05/09/SUPERLITE           |

| AN1946         | SENSORLESS BLDC MOTOR CONTROL AND BEMF SAMPLING METHODS WITH ST7MC          |

| AN1953         | PFC FOR ST7MC STARTER KIT                                                   |

| AN1971         | ST7LITE0 MICROCONTROLLED BALLAST                                            |

| PROGRAMMING A  | AND TOOLS                                                                   |

| AN 978         | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                          |

| AN 983         | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                           |

| AN 985         | EXECUTING CODE IN ST7 RAM                                                   |

| AN 986         | USING THE INDIRECT ADDRESSING MODE WITH ST7                                 |

| AN 987         | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                      |

| AN 988         | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                       |

| AN1039         | ST7 MATH UTILITY ROUTINES                                                   |

|                |                                                                             |