#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Through Hole                                                         |

| Package / Case             | 32-SDIP (0.400", 10.16mm)                                            |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f325k6b6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4 FLASH PROGRAM MEMORY

#### 4.1 Introduction

The ST7 dual voltage High Density Flash

(HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a Byte-by-Byte basis using an external V<sub>PP</sub> supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (In-Circuit Programming) or IAP (In-Application Programming).

The array matrix organisation allows each sector to be erased and reprogrammed without affecting other sectors.

#### 4.2 Main Features

- Three Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased.

- ICP (In-Circuit Programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (In-Application Programming) In this mode, all sectors except Sector 0, can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (In-Circuit Testing) for downloading and executing user application test patterns in RAM

- Read-out protection

- Register Access Security System (RASS) to prevent accidental programming or erasing

#### 4.3 Structure

<u>ل</u>رک

The Flash memory is organised in sectors and can be used for both code and data storage.

Depending on the overall Flash memory size in the microcontroller device, there are up to three user sectors (see Table 5). Each of these sectors can be erased independently to avoid unnecessary erasing of the whole Flash memory when only a partial erasing is required.

The first two sectors have a fixed size of 4 Kbytes (see Figure 7). They are mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

#### Table 5. Sectors available in Flash devices

| Flash Size (bytes) | Available Sectors |

|--------------------|-------------------|

| 4K                 | Sector 0          |

| 8K                 | Sectors 0,1       |

| > 8K               | Sectors 0,1, 2    |

#### 4.3.1 Read-out Protection

Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

In flash devices, this protection is removed by reprogramming the option. In this case, the entire program memory is first automatically erased and the device can be reprogrammed.

Read-out protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP\_R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the Option List.

#### <u>60ł</u> FLASH MEMORY SIZE 1000h 3EEEh SECTOR 2 16 Kbytes 2 Kbytes 8 Kbytes 24 Kbytes 40 Kbvtes 52 Kbytes DFFFh 4 Kbytes SECTOR 1 EFFF 4 Kbytes SECTOR 0 FFFF

Figure 7. Memory Map and Sector Address

## CENTRAL PROCESSING UNIT (Cont'd)

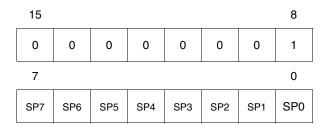

## Stack Pointer (SP)

#### Read/Write

Reset Value: 01 FFh

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 2).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

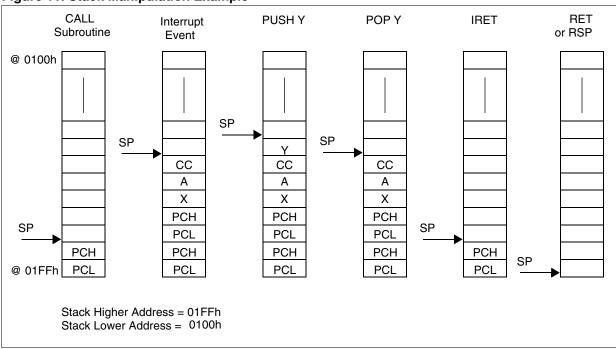

#### Figure 11. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 2.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

**47/**

## SYSTEM INTEGRITY MANAGEMENT (Cont'd)

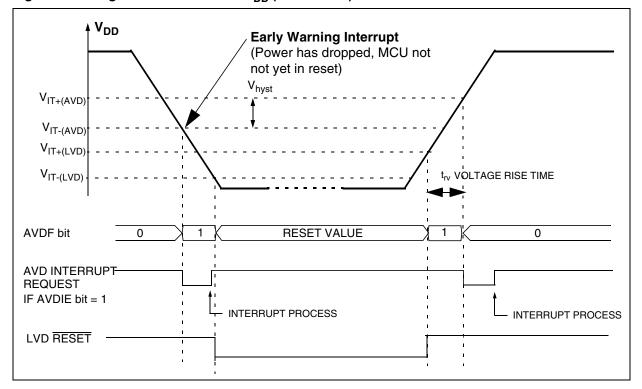

## 6.4.2 Auxiliary Voltage Detector (AVD)

The Voltage Detector function (AVD) is based on an analog comparison between a V<sub>IT-(AVD)</sub> and V<sub>IT+(AVD)</sub> reference value and the V<sub>DD</sub> main supply or the external EVD pin voltage level (V<sub>EVD</sub>). The V<sub>IT</sub> reference value for falling voltage is lower than the V<sub>IT+</sub> reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real time status bit (AVDF) in the SICSR register. This bit is read only.

**Caution**: The AVD function is active only if the LVD is enabled through the option byte.

## 6.4.2.1 Monitoring the V<sub>DD</sub> Main Supply

This mode is selected by clearing the AVDS bit in the SICSR register.

The AVD voltage threshold value is relative to the selected LVD threshold configured by option byte (see section 14.1 on page 181).

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the V<sub>IT+(AVD)</sub> or V<sub>IT-(AVD)</sub> threshold (AVDF bit toggles).

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut down safely before the LVD resets the microcontroller. See Figure 18.

The interrupt on the rising edge is used to inform the application that the  $V_{DD}$  warning state is over.

If the voltage rise time  $t_{rv}$  is less than 256 or 4096 CPU cycles (depending on the reset delay selected by option byte), no AVD interrupt will be generated when  $V_{\rm IT+(AVD)}$  is reached.

If  $t_{rv}$  is greater than 256 or 4096 cycles then:

- If the AVD interrupt is enabled before the  $V_{IT+(AVD)}$  threshold is reached, then 2 AVD interrupts will be received: the first when the AVDIE bit is set, and the second when the threshold is reached.

- If the AVD interrupt is enabled after the V<sub>IT+(AVD)</sub> threshold is reached then only one AVD interrupt will occur.

**67/**

Figure 18. Using the AVD to Monitor V<sub>DD</sub> (AVDS bit=0)

## SYSTEM INTEGRITY MANAGEMENT (Cont'd)

## 6.4.5 Register Description

## SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

#### Read/Write

Reset Value: 000x 000x (00h)

| 7   |    |     |    |   |     |   | 0   |

|-----|----|-----|----|---|-----|---|-----|

| AVD |    | AVD |    | 0 | CSS |   | WDG |

| 5   | IE | Г   | RF |   |     | D | RF  |

#### Bit 7 = **AVDS** Voltage Detection selection

This bit is set and cleared by software. Voltage Detection is available only if the LVD is enabled by option byte.

0: Voltage detection on V<sub>DD</sub> supply

1: Voltage detection on EVD pin

## Bit 6 = **AVDIE** Voltage Detector interrupt enable

This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag changes (toggles). The pending interrupt information is automatically cleared when software enters the AVD interrupt routine. 0: AVD interrupt disabled

1: AVD interrupt enabled

#### Bit 5 = **AVDF** Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to Figure 18 and to Section 6.4.2.1 for additional details.

0:  $V_{DD}$  or  $V_{EVD}$  over  $V_{IT+(AVD)}$  threshold 1:  $V_{DD}$  or  $V_{EVD}$  under  $V_{IT-(AVD)}$  threshold

#### Bit 4 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag description for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

Bit 3 = Reserved, must be kept cleared.

Bit 2 = **CSSIE** Clock security syst interrupt enable This bit enables the interrupt when a disturbance

is detected by the Clock Security System (CSSD bit set). It is set and cleared by software. 0: Clock security system interrupt disabled 1: Clock security system interrupt enabled When the CSS is disabled by OPTION BYTE, the CSSIE bit has no effect.

#### Bit 1 = CSSD Clock security system detection

This bit indicates that the safe oscillator of the Clock Security System block has been selected by hardware due to a disturbance on the main clock signal (f<sub>OSC</sub>). It is set by hardware and cleared by reading the SICSR register when the original oscillator recovers.

0: Safe oscillator is not active

1: Safe oscillator has been activated

When the CSS is disabled by OPTION BYTE, the CSSD bit value is forced to 0.

## Bit 0 = WDGRF Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| <b>RESET Sources</b> | LVDRF | WDGRF |

|----------------------|-------|-------|

| External RESET pin   | 0     | 0     |

| Watchdog             | 0     | 1     |

| LVD                  | 1     | Х     |

## **Application notes**

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

CAUTION: When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

<u>/</u>ک

## INTERRUPTS (Cont'd)

## 7.5 INTERRUPT REGISTER DESCRIPTION

# CPU CC REGISTER INTERRUPT BITS

## Read/Write

**67/**

Reset Value: 111x 1010 (xAh)

| 7 |   |    |   |    |   |   | 0 |

|---|---|----|---|----|---|---|---|

| 1 | 1 | 11 | Н | 10 | N | Z | С |

#### Bit 5, 3 = 11, 10 Software Interrupt Priority

These two bits indicate the current interrupt software priority.

| Interrupt Software Priority    | Level | 1 | 10 |

|--------------------------------|-------|---|----|

| Level 0 (main)                 | Low   | 1 | 0  |

| Level 1                        |       | 0 | 1  |

| Level 2                        | •     | 0 | 0  |

| Level 3 (= interrupt disable*) | High  | 1 | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (ISPRx).

They can be also set/cleared by software with the RIM, SIM, HALT, WFI, IRET and PUSH/POP instructions (see "Interrupt Dedicated Instruction Set" table).

\*Note: TRAP and RESET events can interrupt a level 3 program.

# INTERRUPT SOFTWARE PRIORITY REGISTERS (ISPRX)

Read/Write (bit 7:4 of **ISPR3** are read only) Reset Value: 1111 1111 (FFh)

|       | 7     |       |       |       |       |       |       | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| ISPR0 | l1_3  | 10_3  | l1_2  | 10_2  | 11_1  | I0_1  | l1_0  | 10_0  |

| ISPR1 | 11_7  | 10_7  | l1_6  | 10_6  | l1_5  | 10_5  | 11_4  | 10_4  |

| ISPR2 | 11_11 | 10_11 | 11_10 | 10_10 | l1_9  | 10_9  | l1_8  | 10_8  |

| ISPR3 | 1     | 1     | 1     | 1     | 11_13 | 10_13 | 11_12 | 10_12 |

These four registers contain the interrupt software priority of each interrupt vector.

Each interrupt vector (except RESET and TRAP) has corresponding bits in these registers where its own software priority is stored. This correspondance is shown in the following table.

| Vector address | ISPRx bits           |

|----------------|----------------------|

| FFFBh-FFFAh    | I1_0 and I0_0 bits*  |

| FFF9h-FFF8h    | I1_1 and I0_1 bits   |

|                |                      |

| FFE1h-FFE0h    | I1_13 and I0_13 bits |

Each I1\_x and I0\_x bit value in the ISPRx registers has the same meaning as the I1 and I0 bits in the CC register.

Level 0 can not be written (l1\_x=1, l0\_x=0). In this case, the previously stored value is kept. (example: previous=CFh, write=64h, result=44h)

The TLI, RESET, and TRAP vectors have no software priorities. When one is serviced, the I1 and I0 bits of the CC register are both set.

\*Note: Bits in the ISPRx registers which correspond to the TLI can be read and written but they are not significant in the interrupt process management.

**Caution**: If the  $I1_x$  and  $I0_x$  bits are modified while the interrupt x is executed the following behaviour has to be considered: If the interrupt x is still pending (new interrupt or flag not cleared) and the new software priority is higher than the previous one, the interrupt x is re-entered. Otherwise, the software priority stays unchanged up to the next interrupt request (after the IRET of the interrupt x).

## POWER SAVING MODES (Cont'd)

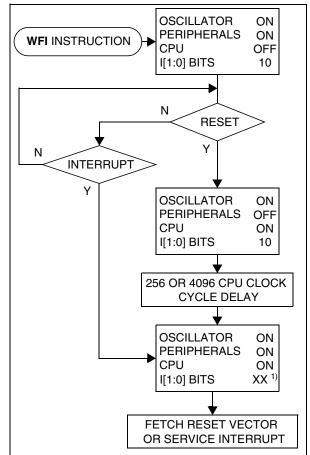

#### 8.3 WAIT MODE

WAIT mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the 'WFI' instruction.

All peripherals remain active. During WAIT mode, the I[1:0] bits of the CC register are forced to '10', to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in WAIT mode until an interrupt or RESET occurs, whereupon the Program Counter branches to the starting address of the interrupt or Reset service routine.

The MCU will remain in WAIT mode until a Reset or an Interrupt occurs, causing it to wake up.

Refer to Figure 28.

#### Note:

1. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

## Figure 28. WAIT Mode Flow-chart

# **10 ON-CHIP PERIPHERALS**

## **10.1 WATCHDOG TIMER (WDG)**

#### 10.1.1 Introduction

The Watchdog timer is used to detect the occurrence of a software fault, usually generated by external interference or by unforeseen logical conditions, which causes the application program to abandon its normal sequence. The Watchdog circuit generates an MCU reset on expiry of a programmed time period, unless the program refreshes the counter's contents before the T6 bit becomes cleared.

#### 10.1.2 Main Features

- Programmable free-running downcounter

- Programmable reset

- Reset (if watchdog activated) when the T6 bit reaches zero

- Optional reset on HALT instruction (configurable by option byte)

- Hardware Watchdog selectable by option byte

## **10.1.3 Functional Description**

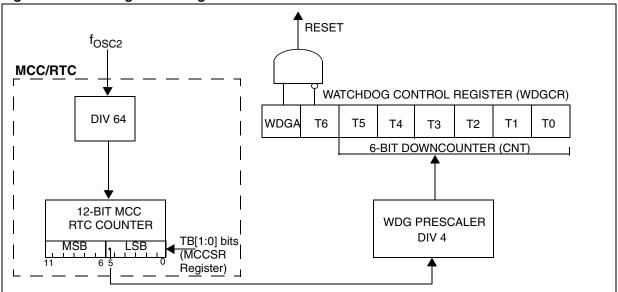

The counter value stored in the Watchdog Control register (WDGCR bits T[6:0]), is decremented every 16384  $f_{OSC2}$  cycles (approx.), and the length of the timeout period can be programmed by the user in 64 increments.

If the watchdog is activated (the WDGA bit is set) and when the 7-bit timer (bits T[6:0]) rolls over from 40h to 3Fh (T6 becomes cleared), it initiates a reset cycle pulling the reset pin low for typically  $30\mu s$ .

The application program must write in the WDGCR register at regular intervals during normal operation to prevent an MCU reset. This down-counter is free-running: it counts down even if the watchdog is disabled. The value to be stored in the WDGCR register must be between FFh and C0h:

- The WDGA bit is set (watchdog enabled)

- The T6 bit is set to prevent generating an immediate reset

- The T[5:0] bits contain the number of increments which represents the time delay before the watchdog produces a reset (see Figure 2. Approximate Timeout Duration). The timing varies between a minimum and a maximum value due to the unknown status of the prescaler when writing to the WDGCR register (see Figure 3).

Following a reset, the watchdog is disabled. Once activated it cannot be disabled, except by a reset.

The T6 bit can be used to generate a software reset (the WDGA bit is set and the T6 bit is cleared).

If the watchdog is activated, the HALT instruction will generate a Reset.

**47/**

#### Figure 35. Watchdog Block Diagram

## **ON-CHIP PERIPHERALS** (Cont'd)

# INPUT CAPTURE CONTROL / STATUS REGISTER (ARTICCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |     |     |      |      |     | 0   |

|---|---|-----|-----|------|------|-----|-----|

| 0 | 0 | CS2 | CS1 | CIE2 | CIE1 | CF2 | CF1 |

Bit 7:6 = Reserved, always read as 0.

#### Bit 5:4 = CS[2:1] Capture Sensitivity

These bits are set and cleared by software. They determine the trigger event polarity on the corresponding input capture channel.

0: Falling edge triggers capture on channel x.

1: Rising edge triggers capture on channel x.

Bit 3:2 = **CIE[2:1]** Capture Interrupt Enable These bits are set and cleared by software. They enable or disable the Input capture channel interrupts independently.

0: Input capture channel x interrupt disabled.

1: Input capture channel x interrupt enabled.

#### Bit 1:0 = CF[2:1] Capture Flag

These bits are set by hardware and cleared by software reading the corresponding ARTICRx register. Each CFx bit indicates that an input capture x has occurred.

0: No input capture on channel x.

1: An input capture has occurred on channel x.

## **INPUT CAPTURE REGISTERS (ARTICRx)**

Read only

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IC7 | IC6 | IC5 | IC4 | IC3 | IC2 | IC1 | IC0 |

## Bit 7:0 = IC[7:0] Input Capture Data

These read only bits are set and cleared by hardware. An ARTICRx register contains the 8-bit auto-reload counter value transferred by the input capture channel x event.

57

## 16-BIT TIMER (Cont'd)

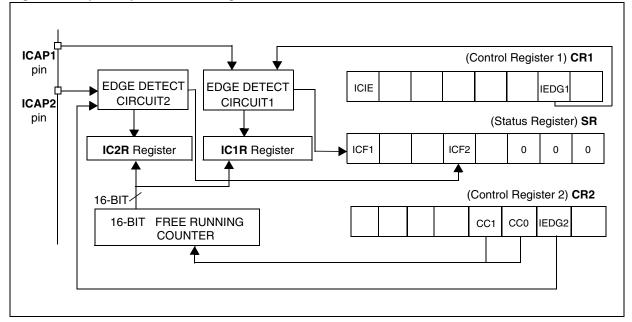

## Figure 49. Input Capture Block Diagram

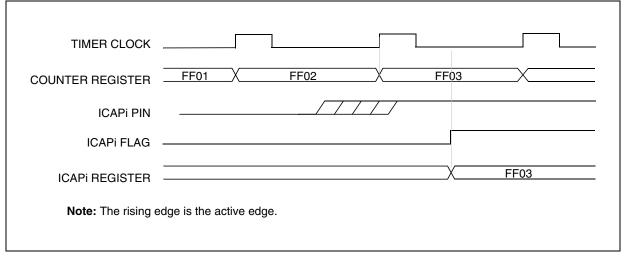

## Figure 50. Input Capture Timing Diagram

لركم ا

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.6.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 1.).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to assign the TDO pin to the alternate function and to send a idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set. When a frame transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

1. An access to the SCISR register

2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 2.).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### **Idle Characters**

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

# I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C STATUS REGISTER 1 (SR1)

#### Read Only

Reset Value: 0000 0000 (00h)

| 7   |       |     |      |     |      |      | 0  |

|-----|-------|-----|------|-----|------|------|----|

| EVF | ADD10 | TRA | BUSY | BTF | ADSL | M/SL | SB |

## Bit 7 = **EVF** Event flag.

This bit is set by hardware as soon as an event occurs. It is cleared by software reading SR2 register in case of error event or as described in Figure 69. It is also cleared by hardware when the interface is disabled (PE=0).

- 0: No event

- 1: One of the following events has occurred:

- BTF=1 (Byte received or transmitted)

- ADSL=1 (Address matched in Slave mode while ACK=1)

- SB=1 (Start condition generated in Master mode)

- AF=1 (No acknowledge received after byte transmission)

- STOPF=1 (Stop condition detected in Slave mode)

- ARLO=1 (Arbitration lost in Master mode)

- BERR=1 (Bus error, misplaced Start or Stop condition detected)

- ADD10=1 (Master has sent header byte)

- Address byte successfully transmitted in Master mode.

#### Bit 6 = **ADD10** 10-bit addressing in Master mode.

This bit is set by hardware when the master has sent the first byte in 10-bit address mode. It is cleared by software reading SR2 register followed by a write in the DR register of the second address byte. It is also cleared by hardware when the peripheral is disabled (PE=0).

0: No ADD10 event occurred.

1: Master has sent first address byte (header)

#### Bit 5 = TRA Transmitter/Receiver.

When BTF is set, TRA=1 if a data byte has been transmitted. It is cleared automatically when BTF is cleared. It is also cleared by hardware after detection of Stop condition (STOPF=1), loss of bus arbitration (ARLO=1) or when the interface is disabled (PE=0).

0: Data byte received (if BTF=1)

## 1: Data byte transmitted

## Bit 4 = **BUSY** Bus busy.

This bit is set by hardware on detection of a Start condition and cleared by hardware on detection of a Stop condition. It indicates a communication in progress on the bus. The BUSY flag of the I2CSR1 register is cleared if a Bus Error occurs. 0: No communication on the bus

1: Communication ongoing on the bus

Note:

The BUSY flag is NOT updated when the interface is disabled (PE=0). This can have consequences when operating in Multimaster mode; i.e. a second active I<sup>2</sup>C master commencing a transfer with an unset BUSY bit can cause a conflict resulting in lost data. A software workaround consists of checking that the I<sup>2</sup>C is not busy before enabling the I<sup>2</sup>C Multimaster cell.

## Bit 3 = **BTF** Byte transfer finished.

This bit is set by hardware as soon as a byte is correctly received or transmitted with interrupt generation if ITE=1. It is cleared by software reading SR1 register followed by a read or write of DR register. It is also cleared by hardware when the interface is disabled (PE=0).

- Following a byte transmission, this bit is set after reception of the acknowledge clock pulse. In case an address byte is sent, this bit is set only after the EV6 event (See Figure 69). BTF is cleared by reading SR1 register followed by writing the next byte in DR register.

- Following a byte reception, this bit is set after transmission of the acknowledge clock pulse if ACK=1. BTF is cleared by reading SR1 register followed by reading the byte from DR register.

The SCL line is held low while BTF=1.

- 0: Byte transfer not done

- 1: Byte transfer succeeded

Bit 2 = **ADSL** Address matched (Slave mode). This bit is set by hardware as soon as the received slave address matched with the OAR register content or a general call is recognized. An interrupt is generated if ITE=1. It is cleared by software reading SR1 register or by hardware when the interface is disabled (PE=0).

The SCL line is held low while ADSL=1.

- 0: Address mismatched or not received

- 1: Received address matched

## I<sup>2</sup>C BUS INTERFACE (Cont'd)

#### Bit 1 = **M/SL** *Master/Slave*.

This bit is set by hardware as soon as the interface is in Master mode (writing START=1). It is cleared by hardware after detecting a Stop condition on the bus or a loss of arbitration (ARLO=1). It is also cleared when the interface is disabled (PE=0). 0: Slave mode

1: Master mode

#### Bit 0 = SB Start bit (Master mode).

This bit is set by hardware as soon as the Start condition is generated (following a write START=1). An interrupt is generated if ITE=1. It is cleared by software reading SR1 register followed by writing the address byte in DR register. It is also cleared by hardware when the interface is disabled (PE=0).

0: No Start condition

1: Start condition generated

## I<sup>2</sup>C STATUS REGISTER 2 (SR2)

Read Only

Reset Value: 0000 0000 (00h)

| 7 |   |   |    |       |      |      | 0    |

|---|---|---|----|-------|------|------|------|

| 0 | 0 | 0 | AF | STOPF | ARLO | BERR | GCAL |

Bit 7:5 = Reserved. Forced to 0 by hardware.

#### Bit 4 = **AF** Acknowledge failure.

This bit is set by hardware when no acknowledge is returned. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

The SCL line is not held low while AF=1 but by other flags (SB or BTF) that are set at the same time.

0: No acknowledge failure

1: Acknowledge failure

Note:

– When an AF event occurs, the SCL line is not held low; however, the SDA line can remain low if the last bits transmitted are all 0. It is then necessary to release both lines by software.

Bit 3 =**STOPF** *Stop detection (Slave mode).* This bit is set by hardware when a Stop condition is detected on the bus after an acknowledge (if ACK=1). An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0). The SCL line is not held low while STOPF=1.

- 0: No Stop condition detected

- 1: Stop condition detected

## Bit 2 = ARLO Arbitration lost.

This bit is set by hardware when the interface loses the arbitration of the bus to another master. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

After an ARLO event the interface switches back automatically to Slave mode (M/SL=0).

The SCL line is not held low while ARLO=1.

0: No arbitration lost detected

1: Arbitration lost detected

Note:

In a Multimaster environment, when the interface is configured in Master Receive mode it does not perform arbitration during the reception of the Acknowledge Bit. Mishandling of the ARLO bit from the I2CSR2 register may occur when a second master simultaneously requests the same data from the same slave and the I<sup>2</sup>C master does not acknowledge the data. The ARLO bit is then left at 0 instead of being set.

## Bit 1 = **BERR** Bus error.

This bit is set by hardware when the interface detects a misplaced Start or Stop condition. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

The SCL line is not held low while BERR=1.

0: No misplaced Start or Stop condition

1: Misplaced Start or Stop condition

Note:

If a Bus Error occurs, a Stop or a repeated Start condition should be generated by the Master to re-synchronize communication, get the transmission acknowledged and the bus released for further communication

Bit 0 = GCAL General Call (Slave mode).

This bit is set by hardware when a general call address is detected on the bus while ENGC=1. It is cleared by hardware detecting a Stop condition (STOPF=1) or when the interface is disabled (PE=0).

- 0: No general call address detected on bus

- 1: general call address detected on bus

## INSTRUCTION SET OVERVIEW (Cont'd)

## **11.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | СР   | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

## Using a prebyte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

| PC-2 | End of previous instruction |

|------|-----------------------------|

|------|-----------------------------|

| PC-1 | Prebyte |

|------|---------|

|------|---------|

PC Opcode

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

**/**

## **12.2.3 Thermal Characteristics**

| Symbol           | Ratings                                                                 | Value       | Unit |  |

|------------------|-------------------------------------------------------------------------|-------------|------|--|

| T <sub>STG</sub> | Storage temperature range                                               | -65 to +150 | °C   |  |

| Т <sub>Ј</sub>   | Maximum junction temperature (see Section 13.2 THERMAL CHARACTERISTICS) |             |      |  |

## **12.3 OPERATING CONDITIONS**

## **12.3.1 General Operating Conditions**

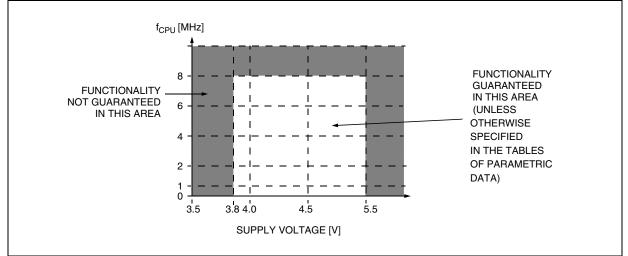

| Symbol                                  | Parameter                                            | Conditions                      | Min | Max | Unit |

|-----------------------------------------|------------------------------------------------------|---------------------------------|-----|-----|------|

| f <sub>CPU</sub>                        | Internal clock frequency                             |                                 | 0   | 8   | MHz  |

| V <sub>DD</sub>                         | Standard voltage range (except Flash<br>Write/Erase) |                                 | 3.8 | 5.5 | v    |

| Operating Voltage for Flash Write/Erase |                                                      | V <sub>PP</sub> = 11.4 to 12.6V | 4.5 | 5.5 |      |

|                                         |                                                      | 1 Suffix Version                | 0   | 70  |      |

|                                         |                                                      | 5 Suffix Version                | -10 | 85  |      |

| T <sub>A</sub>                          | Ambient temperature range                            | 6Suffix Versions                | -40 | 85  | °C   |

|                                         |                                                      | 7 Suffix Versions               | -40 | 105 |      |

|                                         |                                                      | 3 Suffix Version                | -40 | 125 |      |

## Figure 74. f<sub>CPU</sub> Max Versus $V_{\text{DD}}$

**Note:** Some temperature ranges are only available with a specific package and memory size. Refer to Ordering Information.

## **12.5 CLOCK AND TIMING CHARACTERISTICS**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

## 12.5.1 General Timings

| Symbol                                            | Parameter                               | Conditions | Min | <b>Typ</b> <sup>1)</sup> | Max              | Unit             |

|---------------------------------------------------|-----------------------------------------|------------|-----|--------------------------|------------------|------------------|

| t <sub>c(INST)</sub> Instruction cycle time       |                                         | 2          | 3   | 12                       | t <sub>CPU</sub> |                  |

|                                                   | f <sub>CPU</sub> =8MHz                  | 250        | 375 | 1500                     | ns               |                  |

| +                                                 | t Interrupt reaction time <sup>2)</sup> |            | 10  |                          | 22               | t <sub>CPU</sub> |

| $t_{v(IT)}$ $t_{v(IT)} = \Delta t_{c(INST)} + 10$ | f <sub>CPU</sub> =8MHz                  | 1.25       |     | 2.75                     | μs               |                  |

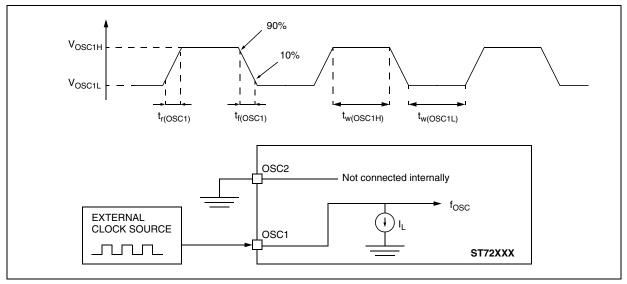

## 12.5.2 External Clock Source

| Symbol                                         | Parameter                            | Conditions                       | Min                             | Тур | Max                             | Unit |

|------------------------------------------------|--------------------------------------|----------------------------------|---------------------------------|-----|---------------------------------|------|

| V <sub>OSC1H</sub>                             | OSC1 input pin high level voltage    |                                  | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     | V <sub>DD</sub>                 | V    |

| V <sub>OSC1L</sub>                             | OSC1 input pin low level voltage     |                                  | V <sub>SS</sub>                 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | v    |

| t <sub>w(OSC1H)</sub><br>t <sub>w(OSC1L)</sub> | OSC1 high or low time <sup>3)</sup>  | see Figure 75                    | 5                               |     |                                 | ns   |

| t <sub>r(OSC1)</sub><br>t <sub>f(OSC1)</sub>   | OSC1 rise or fall time <sup>3)</sup> |                                  |                                 |     | 15                              | 113  |

| ١L                                             | OSC1 Input leakage current           | $V_{SS} \leq V_{IN} \leq V_{DD}$ |                                 |     | ±1                              | μA   |

## Figure 75. Typical Application with an External Clock Source

#### Notes:

1. Data based on typical application software.

2. Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{c(INST)}$  is the number of  $t_{CPU}$  cycles needed to finish the current instruction execution.

3. Data based on design simulation and/or technology characteristics, not tested in production.

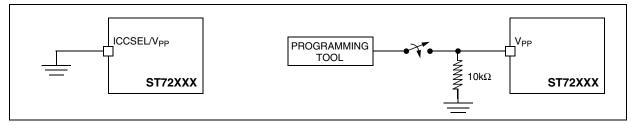

## CONTROL PIN CHARACTERISTICS (Cont'd) 12.9.2 ICCSEL/V<sub>PP</sub> Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol | Parameter             | Conditions                               | Min | Max <sup>1</sup> | Unit |

|--------|-----------------------|------------------------------------------|-----|------------------|------|

| ١L     | Input leakage current | current V <sub>IN</sub> =V <sub>SS</sub> |     | ±1               | μA   |

Figure 89. Two typical Applications with ICCSEL/V\_{PP} Pin  $^{\rm 2)}$

Notes:

1. Data based on design simulation and/or technology characteristics, not tested in production.

2. When ICC mode is not required by the application ICCSEL/V<sub>PP</sub> pin must be tied to  $V_{SS}$ .

## ST72325 DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

## 14.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE

Customer code is made up of the ROM/FAS-TROM contents and the list of the selected options (if any). The ROM/FASTROM contents are to be sent on diskette, or by electronic means, with the S19 hexadecimal file generated by the development tool. All unused bytes must be set to FFh.

The selected options are communicated to STMicroelectronics using the correctly completed OPTION LIST appended.

Refer to application note AN1635 for information on the counter listing returned by ST after code has been transferred. The STMicroelectronics Sales Organization will be pleased to provide detailed information on contractual points.

**Caution:** The Readout Protection binary value is inverted between ROM and FLASH products. The option byte checksum will differ between ROM and FLASH.

## DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

|                                            | ST72P325 FASTROM                                | MICROCONTROLL                              |                                         |            |

|--------------------------------------------|-------------------------------------------------|--------------------------------------------|-----------------------------------------|------------|

| Customer:                                  | · · · · · · · · · · · · · · · · · · ·           | ·<br>· · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·   |            |

|                                            | • • • • • • • • • • • • • • • • • • • •         | • • • • • • • • • • • • • • • • • • • •    | • • • • • • • • • • • • • • • • • • • • |            |

| Contact:                                   |                                                 |                                            |                                         |            |

| Reference/ROM Code                         |                                                 |                                            |                                         |            |

| ROM code name                              | is assigned by STMicro<br>ent in .S19 formatHex | electronics.<br>extension cannot be        | processed.                              |            |

|                                            | Size/Package (check or                          |                                            |                                         |            |

| FASTROM DEVICE:                            | <br> 60K                                        | 48K                                        | <br> 32K                                | <br> 16K   |

| LQFP32 7x7:                                | 1                                               |                                            | []                                      | []         |

| SDIP32:                                    |                                                 |                                            | []                                      |            |

| LQFP48 7x7 (S):<br>LQFP44 10x10:           | · []                                            | []                                         | []<br>  []                              |            |

| SDIP42:                                    | I I I                                           |                                            | ı (j                                    | I [] I     |

| LQFP64 10x10:<br>LQFP64 14x14:             |                                                 |                                            |                                         |            |

|                                            | []  <br>                                        |                                            |                                         | -          |

| DIE FORM:                                  | 60K                                             | 48K                                        | 32K                                     | 32K        |

|                                            | []                                              | []                                         | []                                      | []         |

| Conditioning (check o                      | nly one option):                                |                                            |                                         |            |

| Pac                                        | kaged Product                                   | Die Pro                                    | duct (dice tested at 2                  | 5°C only)  |

| [] Tape & Reel                             | [] Tray                                         | []Tape                                     |                                         |            |

|                                            |                                                 | []Inked                                    | l wafer<br>1 wafer on sticky foil       |            |

| Temp Bange (do not                         | check for die product).                         |                                            | water off sticky for                    |            |

| Temp. Rang                                 |                                                 |                                            |                                         |            |

|                                            |                                                 |                                            |                                         |            |

| [ ] 0°C to +70°C<br>[ ] -10°C to +85°C     |                                                 |                                            |                                         |            |

| [] -40°C to +85°C                          |                                                 |                                            |                                         |            |

| [] -40°C to +105°C                         |                                                 |                                            |                                         |            |

| []-40°C to +125°C                          |                                                 |                                            | " (10 )                                 |            |

| Special Marking:<br>Authorized characters  | [] No<br>are letters, digits, '.', '-',         |                                            | " (10 o                                 | char. max) |

|                                            |                                                 |                                            |                                         |            |

| Clock Source Selection                     | on: [] Resonator                                | : [] 1 to 2 MH<br>[] 2 to 4 MH             |                                         |            |

|                                            |                                                 | [] 4 to 8 MH                               |                                         |            |

|                                            |                                                 | [] 8 to 16 M                               |                                         |            |

|                                            | [ ] Internal R<br>[ ] External C                |                                            |                                         |            |

| PLL:                                       | [] Disabled                                     | [] Enabled                                 |                                         |            |

| CSS:                                       | [] Disabled                                     | [] Enabled                                 |                                         |            |

|                                            |                                                 |                                            |                                         |            |

| LVD Reset: [] Disab<br>Reset Delay:        | led [] High thres<br>[] 256 Cycle               |                                            | shold [] Low thres<br>les               | noid       |

| Watchdog Selection:                        | Software A                                      | Activation                                 | [] Hardware Activa                      | tion       |

| Watchdog Reset on H<br>Readout Protection: | Halt: [] Reset<br>[] Disabled                   |                                            | [] No Reset<br>[] Enabled               |            |

|                                            |                                                 |                                            |                                         |            |

|                                            |                                                 |                                            |                                         |            |

## Table 32. ST7 Application Notes

| IDENTIFICATION | DESCRIPTION                                                                      |

|----------------|----------------------------------------------------------------------------------|

| AN1947         | ST7MC PMAC SINE WAVE MOTOR CONTROL SOFTWARE LIBRARY                              |

| GENERAL PURPO  |                                                                                  |

| AN1476         | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                        |

| AN1526         | ST7FLITE0 QUICK REFERENCE NOTE                                                   |

| AN1709         | EMC DESIGN FOR ST MICROCONTROLLERS                                               |

| AN1752         | ST72324 QUICK REFERENCE NOTE                                                     |

| PRODUCT EVALU  | ATION                                                                            |

| AN 910         | PERFORMANCE BENCHMARKING                                                         |

| AN 990         | ST7 BENEFITS VS INDUSTRY STANDARD                                                |

| AN1077         | OVERVIEW OF ENHANCED CAN CONTROLLERS FOR ST7 AND ST9 MCUS                        |

| AN1086         | U435 CAN-DO SOLUTIONS FOR CAR MULTIPLEXING                                       |

| AN1103         | IMPROVED B-EMF DETECTION FOR LOW SPEED, LOW VOLTAGE WITH ST72141                 |

| AN1150         | BENCHMARK ST72 VS PC16                                                           |

| AN1151         | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                                |

| AN1278         | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                       |

| PRODUCT MIGRA  | TION                                                                             |

| AN1131         | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324               |

| AN1322         | MIGRATING AN APPLICATION FROM ST7263 REV.B TO ST7263B                            |

| AN1365         | GUIDELINES FOR MIGRATING ST72C254 APPLICATIONS TO ST72F264                       |

| AN1604         | HOW TO USE ST7MDT1-TRAIN WITH ST72F264                                           |

| AN2200         | GUIDELINES FOR MIGRATING ST7LITE1X APPLICATIONS TO ST7FLITE1XB                   |

| PRODUCT OPTIMI | ZATION                                                                           |

| AN 982         | USING ST7 WITH CERAMIC RESONATOR                                                 |

| AN1014         | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                        |

| AN1015         | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE                |

| AN1040         | MONITORING THE VBUS SIGNAL FOR USB SELF-POWERED DEVICES                          |

| AN1070         | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                            |

| AN1181         | ELECTROSTATIC DISCHARGE SENSITIVE MEASUREMENT                                    |

| AN1324         | CALIBRATING THE RC OSCILLATOR OF THE ST7FLITE0 MCU USING THE MAINS               |

| AN1502         | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                     |

| AN1529         | EXTENDING THE CURRENT & VOLTAGE CAPABILITY ON THE ST7265 VDDF SUPPLY             |

| AN1530         | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLA-<br>TOR |

| AN1605         | USING AN ACTIVE RC TO WAKEUP THE ST7LITE0 FROM POWER SAVING MODE                 |

| AN1636         | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                               |

| AN1828         | PIR (PASSIVE INFRARED) DETECTOR USING THE ST7FLITE05/09/SUPERLITE                |

| AN1946         | SENSORLESS BLDC MOTOR CONTROL AND BEMF SAMPLING METHODS WITH ST7MC               |

| AN1953         | PFC FOR ST7MC STARTER KIT                                                        |

| AN1971         | ST7LITE0 MICROCONTROLLED BALLAST                                                 |

| PROGRAMMING A  | IND TOOLS                                                                        |

| AN 978         | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                               |

| AN 983         | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                                |

| AN 985         | EXECUTING CODE IN ST7 RAM                                                        |

| AN 986         | USING THE INDIRECT ADDRESSING MODE WITH ST7                                      |

| AN 987         | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                           |

| AN 988         | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                            |

| AN1039         | ST7 MATH UTILITY ROUTINES                                                        |

# **16 REVISION HISTORY**

## Table 33. Revision History

| Date        | Revision | Description of Changes                                                                                                                        |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 26-Sep-2005 | 1        | Initial release                                                                                                                               |

|             |          | Modified LQFP48 pinout, added S device ordering information                                                                                   |

|             |          | Modified Note 4 on page 16 for unbonded pins in 48 pin C devices                                                                              |

|             |          | Added caution about reset vector in unprogrammed Flash devices in Section 6.3.                                                                |

| 04-Dec-2006 | 2        | Removed EMC protective circuitry in Figure 88 on page 163 (device works correctly without these components)                                   |

|             |          | Modified SS min. setup time and added note 4 to section 12.11.1 on page 166                                                                   |

|             |          | Modifed description PKG1 bit in "FLASH OPTION BYTES" on page 181                                                                              |

|             |          | Added "TIMD set simultaneously with OC interrupt" on page 194                                                                                 |

|             |          | In Table 2 added note 5 for I/O Port E2 (PE2) output mode "pull-up always activated" and added note 6 on connection of power and ground pins. |

| 04 4        |          | Deleted the sentence in Section 4.3.1 'Readout protection is not supported if LVD is enabled                                                  |

| 04-Apr-2007 | 3        | Added Package dimensions for LQFP64 14 x14 in Figure 122                                                                                      |

|             |          | Specified EMI data for LQFP64 in Section 12.7.2                                                                                               |

|             |          | Added 'Pull-up always active on PE2' in Section 15.1.8                                                                                        |

|             |          | Title of the document changed                                                                                                                 |

|             |          | Modified Table 1 on page 1<br>Modified "Starting the Conversion" on page 133                                                                  |

|             |          | Modified t <sub>RET</sub> and N <sub>RW</sub> values in "FLASH Memory" on page 155                                                            |

|             |          | Modified "Absolute Maximum Ratings (Electrical Sensitivity)" on page 158                                                                      |

| 07.0.4.0000 |          | Values in inches rounded to 4 decimal digits (instead of 3) in "PACKAGE MECHANICAL DA-                                                        |

| 07-Oct-2008 | 4        | TA" on page 174<br>Removed reference to "Application with a Crystal or Ceramic Resonator for ROM (LQFP64                                      |

|             |          | or any 48/60K ROM)" on page 151                                                                                                               |

|             |          | Modified "PACKAGE CHARACTERISTICS" on page 174 (Section 13.3)                                                                                 |

|             |          | Modified "TIMD set simultaneously with OC interrupt" on page 194                                                                              |

|             |          | Modified Section 14.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUS-<br>TOMER CODE on page 183 (Figure 106 and option lists)                |

|             |          | TOWER CODE OF Page Too (Figure Too and option lists)                                                                                          |