#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                  |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 6x10b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f325k6t3 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1 DESCRIPTION**

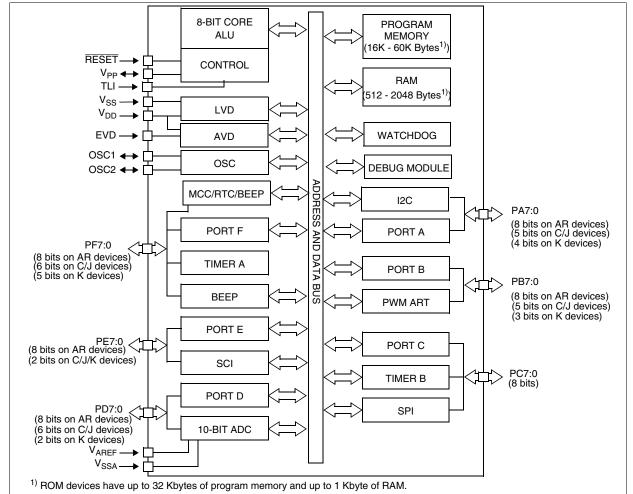

The ST72F325 Flash and ST72325 ROM devices are members of the ST7 microcontroller family designed for mid-range applications.

They are derivatives of the ST72321 and ST72324 devices, with enhanced characteristics and robust Clock Security System.

All devices are based on a common industrystandard 8-bit core, featuring an enhanced instruction set and are available with Flash or ROM program memory. The ST7 family architecture offers both power and flexibility to software developers, enabling the design of highly efficient and compact application code.

The on-chip peripherals include an A/D converter, a PWM Autoreload timer, 2 general purpose timers, I<sup>2</sup>C bus, SPI interface and an SCI interface.

For power economy, microcontroller can switch dynamically into WAIT, SLOW, ACTIVE-HALT or

HALT mode when the application is in idle or stand-by state.

Typical applications are consumer, home, office and industrial products.

The devices feature an on-chip Debug Module (DM) to support in-circuit debugging (ICD). For a description of the DM registers, refer to the ST7 ICC Protocol Reference Manual.

### Main Differences with ST72321:

- LQFP48 and LQFP32 packages

- Clock Security System

- Internal RC, Readout protection, LVD and PLL without limitations

- Negative current injection not allowed on I/O port PB0 (instead of PC6).

- External interrupts have Exit from Active Halt mode capability.

## Figure 1. Device Block Diagram

<u>/</u>ک

| Pin    | n n°  |                                 |      | Le             | evel   |       |     | Ρ   | ort |     |      | Main                               |                                                                                                                                                                                               |                        |  |

|--------|-------|---------------------------------|------|----------------|--------|-------|-----|-----|-----|-----|------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| 32     | 32    | Pin Name                        | Type | Ħ              | out    |       | Inp | out |     | Out | tput | function<br>(after                 | Alternate                                                                                                                                                                                     | function               |  |

| LQFP32 | DIP32 |                                 | -    | Input          | Output | float | ndw | int | ana | OD  | РР   | reset)                             |                                                                                                                                                                                               |                        |  |

| 1      | 4     | V <sub>AREF</sub> <sup>6)</sup> | Ι    |                |        |       |     |     |     |     |      | Analog F                           | eference Voltage for ADC                                                                                                                                                                      |                        |  |

| 2      | 5     | V <sub>SSA</sub> <sup>6)</sup>  | S    |                |        |       |     |     |     |     |      | Analog G                           | Ground Voltage                                                                                                                                                                                |                        |  |

| 3      | 6     | PF0/MCO/AIN8                    | I/O  | CT             |        | x     | е   | i1  | х   | х   | х    | Port F0                            | Main clock out<br>(f <sub>OSC</sub> /2)                                                                                                                                                       | ADC Analog<br>Input 8  |  |

| 4      | 7     | PF1 (HS)/BEEP                   | I/O  | $C_T$          | HS     | Х     | е   | i1  |     | Х   | Х    | Port F1                            | Beep signal outp                                                                                                                                                                              | ut                     |  |

| 5      | 8     | PF4/OCMP1_A/<br>AIN10           | I/O  | CT             |        | x     | х   |     | х   | х   | х    | Port F4                            | Timer A Output<br>Compare 1                                                                                                                                                                   | ADC Analog<br>Input 10 |  |

| 6      | 9     | PF6 (HS)/ICAP1_A                | I/O  | $C_T$          | HS     | Х     | Х   |     |     | Х   | Х    | Port F6                            | Timer A Input Ca                                                                                                                                                                              | pture 1                |  |

| 7      | 10    | PF7 (HS)/<br>EXTCLK_A           | I/O  | CT             | HS     | x     | х   |     |     | х   | х    | Port F7                            | Timer A External                                                                                                                                                                              | Clock Source           |  |

| 8      | 11    | PC0/OCMP2_B/<br>AIN12           | I/O  | CT             |        | х     | Х   |     | х   | х   | х    | Port C0                            | Timer B Output<br>Compare 2                                                                                                                                                                   | ADC Analog<br>Input 12 |  |

| 9      | 12    | PC1/OCMP1_B/<br>AIN13           | I/O  | CT             |        | х     | Х   |     | х   | х   | х    | Port C1                            | Timer B Output<br>Compare 1                                                                                                                                                                   | ADC Analog<br>Input 13 |  |

| 10     | 13    | PC2 (HS)/ICAP2_B                | I/O  | $C_T$          | HS     | Х     | Х   |     |     | Х   | Х    | Port C2                            | Timer B Input Capture 2                                                                                                                                                                       |                        |  |

| 11     | 14    | PC3 (HS)/ICAP1_B                | I/O  | $C_T$          | HS     | Х     | Х   |     |     | Х   | Х    | Port C3                            | Timer B Input Capture 1                                                                                                                                                                       |                        |  |

| 12     | 15    | PC4/MISO/ICCDA-<br>TA           | I/O  | C <sub>T</sub> |        | x     | х   |     |     | х   | х    | Port C4                            | SPI Master In /<br>Slave Out Data                                                                                                                                                             |                        |  |

| 13     | 16    | PC5/MOSI/AIN14                  | I/O  | CT             |        | x     | Х   |     | х   | х   | х    | Port C5                            | SPI Master Out /<br>Slave In Data                                                                                                                                                             | ADC Analog<br>Input 14 |  |

| 14     | 17    | PC6/SCK/ICCCLK                  | I/O  | CT             |        | x     | х   |     |     | х   | х    | Port C6                            | SPI Serial Clock                                                                                                                                                                              | ICC Clock<br>Output    |  |

| 15     | 18    | PC7/SS/AIN15                    | I/O  | CT             |        | x     | х   |     | х   | х   | х    | Port C7                            | SPI Slave Select<br>(active low)                                                                                                                                                              | ADC Analog<br>Input 15 |  |

| 16     | 19    | PA3 (HS)                        | I/O  | $C_T$          | HS     | Х     |     | ei0 |     | Х   | Х    | Port A3                            |                                                                                                                                                                                               |                        |  |

| 17     | 20    | PA4 (HS)                        | I/O  | $C_T$          | HS     | Х     | Х   |     |     | Х   | Х    | Port A4                            | -                                                                                                                                                                                             |                        |  |

| 18     | 21    | PA6 (HS)/SDAI                   | I/O  | $C_T$          | HS     | Х     |     |     |     | Т   |      | Port A6                            | I <sup>2</sup> C Data <sup>1)</sup>                                                                                                                                                           |                        |  |

| 19     | 22    | PA7 (HS)/SCLI                   | I/O  | $C_T$          | HS     | Х     |     |     |     | Т   |      | Port A7                            | I <sup>2</sup> C Clock <sup>1)</sup>                                                                                                                                                          |                        |  |

| 20     | 23    | V <sub>PP</sub> / ICCSEL        | I    |                |        |       |     |     |     |     |      | mode, th<br>voltage in<br>more det | st be tied low. In flash programming<br>de, this pin acts as the programming<br>tage input $V_{PP}$ . See Section 12.9.2 for<br>re details. High voltage must not be ap-<br>ed to ROM devices |                        |  |

| 21     | 24    | RESET                           | I/O  | $C_T$          |        |       |     |     |     |     |      | Top prior                          | priority non maskable interrupt.                                                                                                                                                              |                        |  |

| 22     | 25    | V <sub>SS_2</sub> <sup>6)</sup> | S    |                |        |       |     |     |     |     |      | -                                  | al Ground Voltage                                                                                                                                                                             |                        |  |

| 23     | 26    | OSC2 <sup>3)</sup>              | I/O  |                |        |       |     |     |     |     |      |                                    | sonator oscillator inverter output                                                                                                                                                            |                        |  |

| 24     | 27    | OSC1 <sup>3)</sup>              | Ι    |                |        |       |     |     |     |     |      |                                    | External clock input or Resonator oscillator nverter input                                                                                                                                    |                        |  |

| 25     | 28    | V <sub>DD_2</sub> <sup>6)</sup> | S    |                |        |       |     |     |     |     |      | Digital M                          | ain Supply Voltage                                                                                                                                                                            | )                      |  |

| 26     | 29    | PE0/TDO                         | I/O  | $C_T$          |        | Х     | Х   |     |     | Х   | Х    | Port E0                            | SCI Transmit Dat                                                                                                                                                                              | ta Out                 |  |

| 27     | 30    | PE1/RDI                         | I/O  | $C_T$          |        | Х     | Х   |     |     | Х   | Х    | Port E1                            | SCI Receive Data                                                                                                                                                                              | a In                   |  |

## Table 3. LQFP32/DIP32 Device Pin Description

### CENTRAL PROCESSING UNIT (Cont'd)

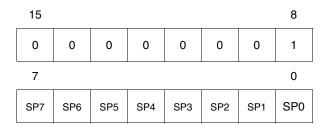

### Stack Pointer (SP)

#### Read/Write

Reset Value: 01 FFh

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 2).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

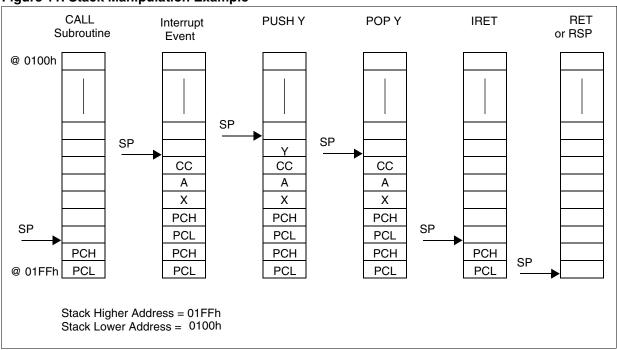

#### Figure 11. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 2.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

**47/**

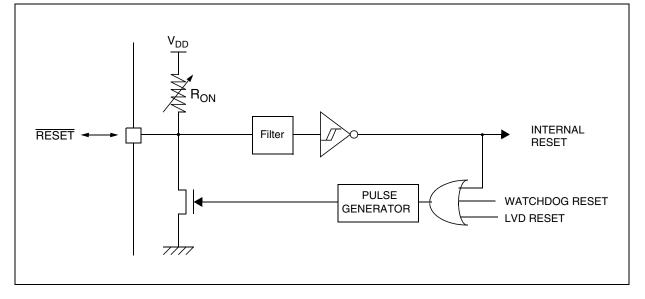

#### 6.3 RESET SEQUENCE MANAGER (RSM)

#### 6.3.1 Introduction

The reset sequence manager includes three RE-SET sources as shown in Figure 15:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

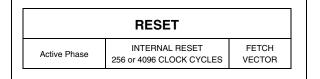

The basic RESET sequence consists of 3 phases as shown in Figure 14:

- Active Phase depending on the RESET source

- 256 or 4096 CPU clock cycle delay (selected by option byte)

- RESET vector fetch

The 256 or 4096 CPU clock cycle delay allows the oscillator to stabilise and ensures that recovery has taken place from the Reset state. The shorter or longer clock cycle delay should be selected by option byte to correspond to the stabilization time of the external oscillator used in the application (see section 14.1 on page 181).

The RESET vector fetch phase duration is 2 clock cycles.

#### Figure 14. RESET Sequence Phases

**Caution:** When the ST7 is unprogrammed or fully erased, the Flash is blank and the RESET vector is not programmed.

For this reason, it is recommended to keep the RESET pin in low state until programming mode is entered, in order to avoid unwanted behavior.

#### 6.3.2 Asynchronous External RESET pin

The RESET pin is both an input and an open-drain output with integrated  $R_{ON}$  weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the device. See "CONTROL PIN CHARACTERISTICS" on page 162 for more details.

A RESET signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see Figure 16). This detection is asynchronous and therefore the MCU can enter reset state even in HALT mode.

#### Figure 15. Reset Block Diagram

**67/**

### SYSTEM INTEGRITY MANAGEMENT (Cont'd)

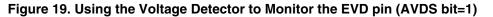

## 6.4.2.2 Monitoring a Voltage on the EVD pin

This mode is selected by setting the AVDS bit in the SICSR register.

The AVD circuitry can generate an interrupt when the AVDIE bit of the SICSR register is set. This interrupt is generated on the rising and falling edges

57

of the comparator output. This means it is generated when either one of these two events occur:

- $V_{EVD}$  rises up to  $V_{IT+(EVD)}$   $V_{EVD}$  falls down to  $V_{IT-(EVD)}$

- The EVD function is illustrated in Figure 19.

For more details, refer to the Electrical Characteristics section.

### SYSTEM INTEGRITY MANAGEMENT (Cont'd)

### 6.4.5 Register Description

### SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

#### Read/Write

Reset Value: 000x 000x (00h)

| 7   |    |     |    |   |     |   | 0   |

|-----|----|-----|----|---|-----|---|-----|

| AVD |    | AVD |    | 0 | CSS |   | WDG |

| 5   | IE | Г   | RF |   |     | D | RF  |

#### Bit 7 = **AVDS** Voltage Detection selection

This bit is set and cleared by software. Voltage Detection is available only if the LVD is enabled by option byte.

0: Voltage detection on V<sub>DD</sub> supply

1: Voltage detection on EVD pin

### Bit 6 = **AVDIE** Voltage Detector interrupt enable

This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag changes (toggles). The pending interrupt information is automatically cleared when software enters the AVD interrupt routine. 0: AVD interrupt disabled

1: AVD interrupt enabled

#### Bit 5 = **AVDF** Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to Figure 18 and to Section 6.4.2.1 for additional details.

0:  $V_{DD}$  or  $V_{EVD}$  over  $V_{IT+(AVD)}$  threshold 1:  $V_{DD}$  or  $V_{EVD}$  under  $V_{IT-(AVD)}$  threshold

#### Bit 4 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag description for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

Bit 3 = Reserved, must be kept cleared.

Bit 2 = **CSSIE** *Clock security syst interrupt enable* This bit enables the interrupt when a disturbance is detected by the Clock Security System (CSSD bit set). It is set and cleared by software.0: Clock security system interrupt disabled1: Clock security system interrupt enabledWhen the CSS is disabled by OPTION BYTE, the CSSIE bit has no effect.

#### Bit 1 = **CSSD** Clock security system detection

This bit indicates that the safe oscillator of the Clock Security System block has been selected by hardware due to a disturbance on the main clock signal ( $f_{OSC}$ ). It is set by hardware and cleared by reading the SICSR register when the original oscillator recovers.

0: Safe oscillator is not active

1: Safe oscillator has been activated

When the CSS is disabled by OPTION BYTE, the CSSD bit value is forced to 0.

### Bit 0 = WDGRF Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| <b>RESET Sources</b> | LVDRF | WDGRF |

|----------------------|-------|-------|

| External RESET pin   | 0     | 0     |

| Watchdog             | 0     | 1     |

| LVD                  | 1     | Х     |

### **Application notes**

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

**CAUTION:** When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

57

## **INTERRUPTS** (Cont'd)

| Instruction | New Description                 | Function/Example      | 11 | Н | 10 | Ν | Z | С |

|-------------|---------------------------------|-----------------------|----|---|----|---|---|---|

| HALT        | Entering Halt mode              |                       | 1  |   | 0  |   |   |   |

| IRET        | Interrupt routine return        | Pop CC, A, X, PC      | 11 | Н | 10 | Ν | Z | С |

| JRM         | Jump if I1:0=11 (level 3)       | 11:0=11 ?             |    |   |    |   |   |   |

| JRNM        | Jump if I1:0<>11                | 11:0<>11 ?            |    |   |    |   |   |   |

| POP CC      | Pop CC from the Stack           | Mem => CC             | 11 | Н | 10 | Ν | Z | С |

| RIM         | Enable interrupt (level 0 set)  | Load 10 in I1:0 of CC | 1  |   | 0  |   |   |   |

| SIM         | Disable interrupt (level 3 set) | Load 11 in I1:0 of CC | 1  |   | 1  |   |   |   |

| TRAP        | Software trap                   | Software NMI          | 1  |   | 1  |   |   |   |

| WFI         | Wait for interrupt              |                       | 1  |   | 0  |   |   |   |

## Table 8. Dedicated Interrupt Instruction Set

Note: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current software priority up to the next IRET instruction or one of the previously mentioned instructions.

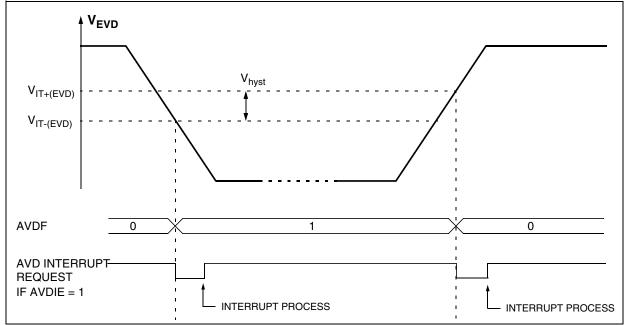

### I/O PORTS (Cont'd)

### Figure 33. I/O Port General Block Diagram

#### Table 11. I/O Port Mode Options

| Configuration Mode |                                 | Pull-Up | P-Buffer | Diodes             |                    |  |

|--------------------|---------------------------------|---------|----------|--------------------|--------------------|--|

|                    | Configuration Mode              |         | F-Duilei | to V <sub>DD</sub> | to V <sub>SS</sub> |  |

| Input              | Floating with/without Interrupt | Off     | Off      |                    |                    |  |

| input              | Pull-up with/without Interrupt  | On      |          | On                 | On                 |  |

|                    | Push-pull                       | Off     | On       |                    |                    |  |

| Output             | Open Drain (logic level)        |         | Off      | 1                  |                    |  |

|                    | True Open Drain                 | NI      | NI       | NI (see note)      |                    |  |

Legend: NI - not implemented

Off - implemented not activated On - implemented and activated **Note**: The diode to  $V_{DD}$  is not implemented in the true open drain pads. A local protection between the pad and  $V_{SS}$  is implemented to protect the device against positive stress.

57

### I/O PORTS (Cont'd)

## Table 14. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label        | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|--------------------------|-----|---|---|---|---|---|---|-----|

|                   | t Value<br>ort registers | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000h             | PADR                     |     |   |   |   |   |   |   |     |

| 0001h             | PADDR                    | MSB |   |   |   |   |   |   | LSB |

| 0002h             | PAOR                     |     |   |   |   |   |   |   |     |

| 0003h             | PBDR                     |     |   |   |   |   |   |   |     |

| 0004h             | PBDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0005h             | PBOR                     |     |   |   |   |   |   |   |     |

| 0006h             | PCDR                     |     |   |   |   |   |   |   |     |

| 0007h             | PCDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0008h             | PCOR                     |     |   |   |   |   |   |   |     |

| 0009h             | PDDR                     |     |   |   |   |   |   |   |     |

| 000Ah             | PDDDR                    | MSB |   |   |   |   |   |   | LSB |

| 000Bh             | PDOR                     |     |   |   |   |   |   |   |     |

| 000Ch             | PEDR                     |     |   |   |   |   |   |   |     |

| 000Dh             | PEDDR                    | MSB |   |   |   |   |   |   | LSB |

| 000Eh             | PEOR                     |     |   |   |   |   |   |   |     |

| 000Fh             | PFDR                     |     |   |   |   |   |   |   |     |

| 0010h             | PFDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0011h             | PFOR                     |     |   |   |   |   |   |   |     |

## **Related Documentation**

57

AN 970: SPI Communication between ST7 and EEPROM

AN1045: S/W implementation of I2C bus master AN1048: Software LCD driver

55/197

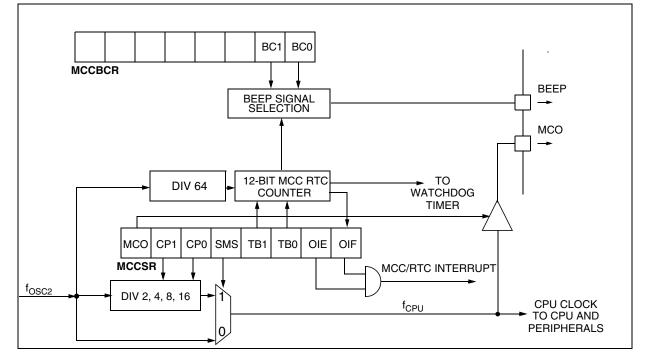

### 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC)

The Main Clock Controller consists of three different functions:

- a programmable CPU clock prescaler

- a clock-out signal to supply external devices

- a real time clock timer with interrupt capability

Each function can be used independently and simultaneously.

### 10.2.1 Programmable CPU Clock Prescaler

The programmable CPU clock prescaler supplies the clock for the ST7 CPU and its internal peripherals. It manages SLOW power saving mode (See Section 8.2 SLOW MODE for more details).

The prescaler selects the  $f_{CPU}$  main clock frequency and is controlled by three bits in the MCCSR register: CP[1:0] and SMS.

#### 10.2.2 Clock-out Capability

**لركم**

The clock-out capability is an alternate function of an I/O port pin that outputs a  $f_{CPU}$  clock to drive

external devices. It is controlled by the MCO bit in the MCCSR register.

**CAUTION**: When selected, the clock out pin suspends the clock during ACTIVE-HALT mode.

### 10.2.3 Real Time Clock Timer (RTC)

The counter of the real time clock timer allows an interrupt to be generated based on an accurate real time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by four bits of the MCC-SR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters ACTIVE-HALT mode when the HALT instruction is executed. See Section 8.4 AC-TIVE-HALT AND HALT MODES for more details.

#### 10.2.4 Beeper

The beep function is controlled by the MCCBCR register. It can output three selectable frequencies on the BEEP pin (I/O port alternate function).

#### Figure 38. Main Clock Controller (MCC/RTC) Block Diagram

### **ON-CHIP PERIPHERALS** (Cont'd)

#### **10.3.2 Functional Description**

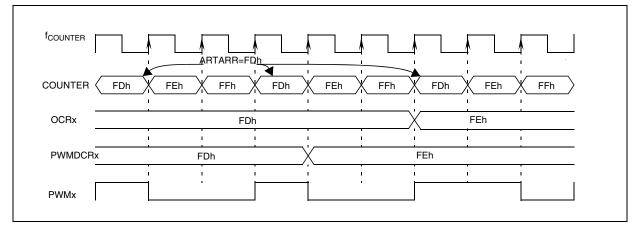

#### Counter

The free running 8-bit counter is fed by the output of the prescaler, and is incremented on every rising edge of the clock signal.

It is possible to read or write the contents of the counter on the fly by reading or writing the Counter Access register (ARTCAR).

When a counter overflow occurs, the counter is automatically reloaded with the contents of the ARTARR register (the prescaler is not affected).

#### **Counter clock and prescaler**

The counter clock frequency is given by:

$$f_{COUNTER} = f_{INPUT} / 2^{CC[2:0]}$$

The timer counter's input clock ( $f_{INPUT}$ ) feeds the 7-bit programmable prescaler, which selects one of the 8 available taps of the prescaler, as defined by CC[2:0] bits in the Control/Status Register (ARTCSR). Thus the division factor of the prescaler can be set to 2<sup>n</sup> (where n = 0, 1,..7).

This  $f_{INPUT}$  frequency source is selected through the EXCL bit of the ARTCSR register and can be either the  $f_{CPU}$  or an external input frequency  $f_{FXT}$ .

The clock input to the counter is enabled by the TCE (Timer Counter Enable) bit in the ARTCSR register. When TCE is reset, the counter is stopped and the prescaler and counter contents are frozen. When TCE is set, the counter runs at the rate of the selected clock source.

#### **Counter and Prescaler Initialization**

After RESET, the counter and the prescaler are cleared and  $f_{INPUT} = f_{CPU}$ .

The counter can be initialized by:

- Writing to the ARTARR register and then setting the FCRL (Force Counter Re-Load) and the TCE (Timer Counter Enable) bits in the ARTCSR register.

- Writing to the ARTCAR counter access register,

In both cases the 7-bit prescaler is also cleared, whereupon counting will start from a known value.

Direct access to the prescaler is not possible.

#### Output compare control

The timer compare function is based on four different comparisons with the counter (one for each PWMx output). Each comparison is made between the counter value and an output compare register (OCRx) value. This OCRx register can not be accessed directly, it is loaded from the duty cycle register (PWMDCRx) at each overflow of the counter.

This double buffering method avoids glitch generation when changing the duty cycle on the fly.

Figure 40. Output compare control

<u>لرک</u>

#### 10.4 16-BIT TIMER

#### 10.4.1 Introduction

The timer consists of a 16-bit free-running counter driven by a programmable prescaler.

It may be used for a variety of purposes, including pulse length measurement of up to two input signals (*input capture*) or generation of up to two output waveforms (*output compare* and *PWM*).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the CPU clock prescaler.

Some ST7 devices have two on-chip 16-bit timers. They are completely independent, and do not share any resources. They are synchronized after a MCU reset as long as the timer clock frequencies are not modified.

This description covers one or two 16-bit timers. In ST7 devices with two timers, register names are prefixed with TA (Timer A) or TB (Timer B).

#### 10.4.2 Main Features

- Programmable prescaler: f<sub>CPU</sub> divided by 2, 4 or 8

- Overflow status flag and maskable interrupt

- External clock input (must be at least four times slower than the CPU clock speed) with the choice of active edge

- 1 or 2 Output Compare functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated programmable signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- 1 or 2 Input Capture functions each with:

- 2 dedicated 16-bit registers

- 2 dedicated active edge selection signals

- 2 dedicated status flags

- 1 dedicated maskable interrupt

- Pulse width modulation mode (PWM)

- One Pulse mode

- Reduced Power Mode

- 5 alternate functions on I/O ports (ICAP1, ICAP2, OCMP1, OCMP2, EXTCLK)\*

The Block Diagram is shown in Figure 1.

\***Note:** Some timer pins may not be available (not bonded) in some ST7 devices. Refer to the device pin out description.

When reading an input signal on a non-bonded pin, the value will always be '1'.

#### 10.4.3 Functional Description

#### 10.4.3.1 Counter

The main block of the Programmable Timer is a 16-bit free running upcounter and its associated 16-bit registers. The 16-bit registers are made up of two 8-bit registers called high and low.

Counter Register (CR):

- Counter High Register (CHR) is the most significant byte (MS Byte).

- Counter Low Register (CLR) is the least significant byte (LS Byte).

Alternate Counter Register (ACR)

- Alternate Counter High Register (ACHR) is the most significant byte (MS Byte).

- Alternate Counter Low Register (ACLR) is the least significant byte (LS Byte).

These two read-only 16-bit registers contain the same value but with the difference that reading the ACLR register does not clear the TOF bit (Timer overflow flag), located in the Status register, (SR), (see note at the end of paragraph titled 16-bit read sequence).

Writing in the CLR register or ACLR register resets the free running counter to the FFFCh value. Both counters have a reset value of FFFCh (this is the only value which is reloaded in the 16-bit timer). The reset value of both counters is also FFFCh in One Pulse mode and PWM mode.

The timer clock depends on the clock control bits of the CR2 register, as illustrated in Table 1. The value in the counter register repeats every 131072, 262144 or 524288 CPU clock cycles depending on the CC[1:0] bits.

The timer frequency can be  $f_{CPU}/2$ ,  $f_{CPU}/4$ ,  $f_{CPU}/8$  or an external frequency.

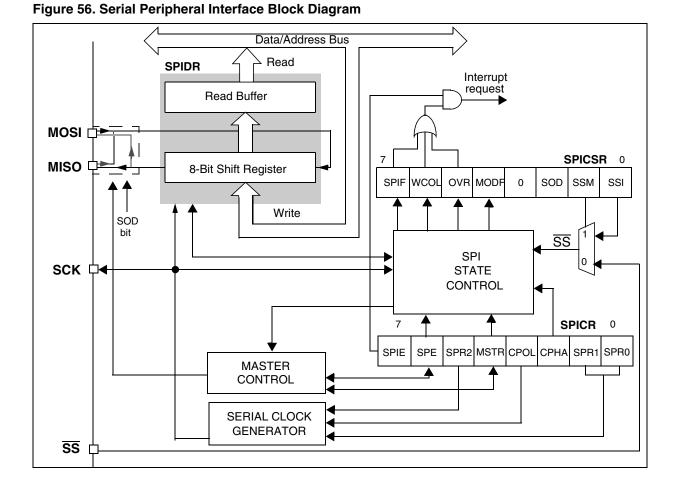

### **10.5 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 10.5.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves however the SPI interface can not be a master in a multi-master system.

### 10.5.2 Main Features

- Full duplex synchronous transfers (on 3 lines)

- Simplex synchronous transfers (on 2 lines)

- Master or slave operation

- Six master mode frequencies (f<sub>CPU</sub>/4 max.)

- f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

**Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

### **10.5.3 General Description**

Figure 56 shows the serial peripheral interface (SPI) block diagram. There are 3 registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through 4 pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

**47/**

## I<sup>2</sup>C INTERFACE (Cont'd) How to release the SDA / SCL lines

Set and subsequently clear the STOP bit while BTF is set. The SDA/SCL lines are released after the transfer of the current byte.

### **SMBus Compatibility**

ST7 I<sup>2</sup>C is compatible with SMBus V1.1 protocol. It supports all SMBus adressing modes, SMBus bus protocols and CRC-8 packet error checking. Refer to AN1713: SMBus Slave Driver For ST7 I<sup>2</sup>C Peripheral.

### 10.7.4.2 Master Mode

To switch from default Slave mode to Master mode a Start condition generation is needed.

#### Start condition

Setting the START bit while the BUSY bit is cleared causes the interface to switch to Master mode (M/SL bit set) and generates a Start condition.

Once the Start condition is sent:

The EVF and SB bits are set by hardware with an interrupt if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register with the Slave address, **holding the SCL line low** (see Figure 69 Transfer sequencing EV5).

#### Slave address transmission

Then the slave address is sent to the SDA line via the internal shift register.

In 7-bit addressing mode, one address byte is sent.

In 10-bit addressing mode, sending the first byte including the header sequence causes the following event:

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 69 Transfer sequencing EV9). Then the second address byte is sent by the interface.

After completion of this transfer (and acknowledge from the slave if the ACK bit is set):

- The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the CR register (for example set PE bit), **holding the SCL line low** (see Figure 69 Transfer sequencing EV6).

Next the master must enter Receiver or Transmitter mode.

**Note:** In 10-bit addressing mode, to switch the master to Receiver mode, software must generate a repeated Start condition and resend the header sequence with the least significant bit set (11110xx1).

### **Master Receiver**

Following the address transmission and after SR1 and CR registers have been accessed, the master receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see Figure 69 Transfer sequencing EV7).

To close the communication: before reading the last byte from the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

**Note:** In order to generate the non-acknowledge pulse after the last received data byte, the ACK bit must be cleared just before reading the second last data byte.

## 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### **10.8.6 Register Description**

### **CONTROL/STATUS REGISTER (ADCCSR)**

Read/Write (Except bit 7 read only)

Reset Value: 0000 0000 (00h)

| 7   |       |      |   |     |     |     | 0   |

|-----|-------|------|---|-----|-----|-----|-----|

| EOC | SPEED | ADON | 0 | СНЗ | CH2 | CH1 | CH0 |

Bit 7 = **EOC** End of Conversion This bit is set by hardware. It is cleared by hardware when software reads the ADCDRH register or writes to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 = **SPEED** ADC clock selection This bit is set and cleared by software. 0:  $f_{ADC} = f_{CPU}/4$

1:  $f_{ADC} = f_{CPU}/2$

Bit 5 = **ADON** *A/D Converter on* This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = **Reserved.** Must be kept cleared.

## Bit 3:0 = CH[3:0] Channel Selection

These bits are set and cleared by software. They select the analog input to convert.

| Channel Pin* | CH3 | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | 1   | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

\*The number of channels is device dependent. Refer to the device pinout description.

#### **DATA REGISTER (ADCDRH)**

Read Only

Reset Value: 0000 0000 (00h)

7

0

D9

D8

D7

D6

D5

D4

D3

D2

Bit 7:0 = D[9:2] MSB of Converted Analog Value

#### **DATA REGISTER (ADCDRL)**

Read Only Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bit 7:2 = Reserved. Forced by hardware to 0.

Bit 1:0 = **D**[1:0] LSB of Converted Analog Value

# 10-BIT A/D CONVERTER (Cont'd)

## Table 26. ADC Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label     | 7        | 6          | 5         | 4       | 3        | 2        | 1        | 0        |

|-------------------|-----------------------|----------|------------|-----------|---------|----------|----------|----------|----------|

| 0070h             | ADCCSR<br>Reset Value | EOC<br>0 | SPEED<br>0 | ADON<br>0 | 0       | CH3<br>0 | CH2<br>0 | CH1<br>0 | CH0<br>0 |

| 0071h             | ADCDRH<br>Reset Value | D9<br>0  | D8<br>0    | D7<br>0   | D6<br>0 | D5<br>0  | D4<br>0  | D3<br>0  | D2<br>0  |

| 0072h             | ADCDRL<br>Reset Value | 0        | 0          | 0         | 0       | 0        | 0        | D1<br>0  | D0<br>0  |

### **12.2.3 Thermal Characteristics**

| Symbol           | Ratings                                                                 | Value       | Unit |  |  |  |  |

|------------------|-------------------------------------------------------------------------|-------------|------|--|--|--|--|

| T <sub>STG</sub> | Storage temperature range                                               | -65 to +150 | °C   |  |  |  |  |

| TJ               | Maximum junction temperature (see Section 13.2 THERMAL CHARACTERISTICS) |             |      |  |  |  |  |

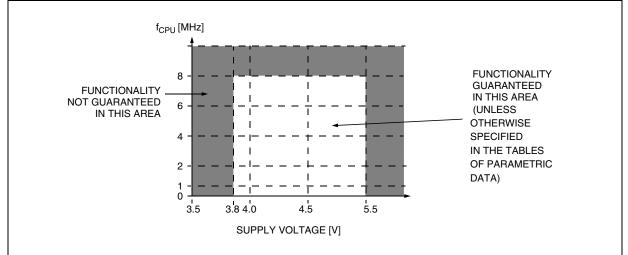

### **12.3 OPERATING CONDITIONS**

### **12.3.1 General Operating Conditions**

| Symbol           | Parameter                                            | Conditions                      | Min | Max | Unit |  |

|------------------|------------------------------------------------------|---------------------------------|-----|-----|------|--|

| f <sub>CPU</sub> | Internal clock frequency                             |                                 | 0   | 8   | MHz  |  |

| V <sub>DD</sub>  | Standard voltage range (except Flash<br>Write/Erase) |                                 | 3.8 | 5.5 | V    |  |

|                  | Operating Voltage for Flash Write/Erase              | V <sub>PP</sub> = 11.4 to 12.6V | 4.5 | 5.5 |      |  |

| T <sub>A</sub>   | Ambient temperature range                            | 1 Suffix Version                | 0   | 70  |      |  |

|                  |                                                      | 5 Suffix Version                | -10 | 85  | °C   |  |

|                  |                                                      | 6Suffix Versions                | -40 | 85  |      |  |

|                  |                                                      | 7 Suffix Versions               | -40 | 105 |      |  |

|                  |                                                      | 3 Suffix Version                | -40 | 125 |      |  |

## Figure 74. f<sub>CPU</sub> Max Versus $V_{\text{DD}}$

**Note:** Some temperature ranges are only available with a specific package and memory size. Refer to Ordering Information.

## CONTROL PIN CHARACTERISTICS (Cont'd) 12.9.2 ICCSEL/V<sub>PP</sub> Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol | Parameter             | Conditions                       | Min | Max <sup>1</sup> | Unit |

|--------|-----------------------|----------------------------------|-----|------------------|------|

| ١L     | Input leakage current | V <sub>IN</sub> =V <sub>SS</sub> |     | ±1               | μA   |

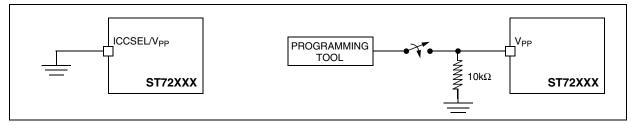

Figure 89. Two typical Applications with ICCSEL/V\_{PP} Pin  $^{\rm 2)}$

Notes:

1. Data based on design simulation and/or technology characteristics, not tested in production.

2. When ICC mode is not required by the application ICCSEL/V<sub>PP</sub> pin must be tied to  $V_{SS}$ .

## DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

|                                            | ST72P325 FASTROM                                | MICROCONTROLL                           |                                         |            |  |  |

|--------------------------------------------|-------------------------------------------------|-----------------------------------------|-----------------------------------------|------------|--|--|

| Customer:                                  |                                                 |                                         |                                         |            |  |  |

|                                            | • • • • • • • • • • • • • • • • • • • •         | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • |            |  |  |

| Contact:                                   |                                                 |                                         |                                         |            |  |  |

| Reference/ROM Code                         |                                                 |                                         |                                         |            |  |  |

| ROM code name                              | is assigned by STMicro<br>ent in .S19 formatHex | electronics.<br>extension cannot be     | processed.                              |            |  |  |

|                                            | Size/Package (check or                          |                                         |                                         |            |  |  |

| FASTROM DEVICE:                            | <br> 60K                                        | 48K                                     | <br> 32K                                | <br> 16K   |  |  |

| LQFP32 7x7:                                | 1                                               |                                         | []                                      | []         |  |  |

| SDIP32:                                    |                                                 |                                         | []                                      |            |  |  |

| LQFP48 7x7 (S):<br>LQFP44 10x10:           | · []                                            | []                                      | []<br>  []                              |            |  |  |

| SDIP42:                                    | I I I                                           |                                         | ı (j                                    | I [] I     |  |  |

| LQFP64 10x10:<br>LQFP64 14x14:             |                                                 |                                         |                                         |            |  |  |

|                                            | []  <br>                                        |                                         |                                         | -          |  |  |

| DIE FORM:                                  | 60K                                             | 48K                                     | 32K                                     | 32K        |  |  |

|                                            | []                                              | []                                      | []                                      | []         |  |  |

| Conditioning (check o                      | nly one option):                                |                                         |                                         |            |  |  |

| Pac                                        | kaged Product                                   | Die Pro                                 | duct (dice tested at 2                  | 5°C only)  |  |  |

| [] Tape & Reel                             | [] Tray                                         | []Tape                                  |                                         |            |  |  |

|                                            |                                                 | []Inked                                 | l wafer<br>1 wafer on sticky foil       |            |  |  |

| Temp Bange (do not                         | check for die product).                         |                                         | water off sticky for                    |            |  |  |

| Temp. Rang                                 |                                                 |                                         |                                         |            |  |  |

|                                            |                                                 |                                         |                                         |            |  |  |

| [ ] 0°C to +70°C<br>[ ] -10°C to +85°C     |                                                 |                                         |                                         |            |  |  |

| [] -40°C to +85°C                          |                                                 |                                         |                                         |            |  |  |

| [] -40°C to +105°C                         |                                                 |                                         |                                         |            |  |  |

| []-40°C to +125°C                          |                                                 |                                         | " (10 )                                 |            |  |  |

| Special Marking:<br>Authorized characters  | [] No<br>are letters, digits, '.', '-',         |                                         | " (10 o                                 | char. max) |  |  |

|                                            |                                                 |                                         |                                         |            |  |  |

| Clock Source Selection                     | on: [] Resonator                                | : [] 1 to 2 MH<br>[] 2 to 4 MH          |                                         |            |  |  |

|                                            |                                                 | [] 4 to 8 MH                            |                                         |            |  |  |

|                                            |                                                 | [] 8 to 16 M                            |                                         |            |  |  |

|                                            | [ ] Internal R<br>[ ] External C                |                                         |                                         |            |  |  |

| PLL:                                       | [] Disabled                                     | [] Enabled                              |                                         |            |  |  |

| CSS:                                       | [] Disabled                                     | [] Enabled                              |                                         |            |  |  |

|                                            |                                                 |                                         |                                         | bald       |  |  |

| LVD Reset: [] Disab<br>Reset Delay:        | [ ] 256 Cycle                                   | s [] 4096 Cvc                           | shold []Low thres<br>les                | noid       |  |  |

| Watchdog Selection:                        | Software A                                      | Activation                              | [] Hardware Activa                      | tion       |  |  |

| Watchdog Reset on H<br>Readout Protection: | Halt: [] Reset<br>[] Disabled                   |                                         | [] No Reset<br>[] Enabled               |            |  |  |

|                                            |                                                 |                                         |                                         |            |  |  |

|                                            |                                                 |                                         |                                         |            |  |  |

## Table 32. ST7 Application Notes

| IDENTIFICATION      | DESCRIPTION                                                                          |  |  |

|---------------------|--------------------------------------------------------------------------------------|--|--|

| AN1071              | HALF DUPLEX USB-TO-SERIAL BRIDGE USING THE ST72611 USB MICROCONTROLLER               |  |  |

| AN1106              | TRANSLATING ASSEMBLY CODE FROM HC05 TO ST7                                           |  |  |

| AN1179              | PROGRAMMING ST7 FLASH MICROCONTROLLERS IN REMOTE ISP MODE (IN-SITU PRO-<br>GRAMMING) |  |  |

| AN1446              | USING THE ST72521 EMULATOR TO DEBUG AN ST72324 TARGET APPLICATION                    |  |  |

| AN1477              | EMULATED DATA EEPROM WITH XFLASH MEMORY                                              |  |  |

| AN1527              | DEVELOPING A USB SMARTCARD READER WITH ST7SCR                                        |  |  |

| AN1575              | ON-BOARD PROGRAMMING METHODS FOR XFLASH AND HDFLASH ST7 MCUS                         |  |  |

| AN1576              | IN-APPLICATION PROGRAMMING (IAP) DRIVERS FOR ST7 HDFLASH OR XFLASH MCUS              |  |  |

| AN1577              | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION FOR ST7 USB APPLICATIONS                |  |  |

| AN1601              | SOFTWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |  |  |

| AN1603              | USING THE ST7 USB DEVICE FIRMWARE UPGRADE DEVELOPMENT KIT (DFU-DK)                   |  |  |

| AN1635              | ST7 CUSTOMER ROM CODE RELEASE INFORMATION                                            |  |  |

| AN1754              | DATA LOGGING PROGRAM FOR TESTING ST7 APPLICATIONS VIA ICC                            |  |  |

| AN1796              | FIELD UPDATES FOR FLASH BASED ST7 APPLICATIONS USING A PC COMM PORT                  |  |  |

| AN1900              | HARDWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |  |  |

| AN1904              | ST7MC THREE-PHASE AC INDUCTION MOTOR CONTROL SOFTWARE LIBRARY                        |  |  |

| AN1905              | ST7MC THREE-PHASE BLDC MOTOR CONTROL SOFTWARE LIBRARY                                |  |  |

| SYSTEM OPTIMIZATION |                                                                                      |  |  |

| AN1711              | SOFTWARE TECHNIQUES FOR COMPENSATING ST7 ADC ERRORS                                  |  |  |

| AN1827              | IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09                                 |  |  |

| AN2009              | PWM MANAGEMENT FOR 3-PHASE BLDC MOTOR DRIVES USING THE ST7FMC                        |  |  |

| AN2030              | BACK EMF DETECTION DURING PWM ON TIME BY ST7MC                                       |  |  |