Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                  |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 36                                                                   |

| Program Memory Size        | 16KB (16K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 512 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 48-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f325s4t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

\_\_\_\_\_

| 1 DES  | CRIPTION                                                                                           | 7  |

|--------|----------------------------------------------------------------------------------------------------|----|

|        | DESCRIPTION                                                                                        |    |

| 3 REG  | SISTER & MEMORY MAP                                                                                | 17 |

| 4 FLA  | SH PROGRAM MEMORY                                                                                  | 21 |

| 4.1    |                                                                                                    | 21 |

| 4.2    | MAIN FEATURES                                                                                      | 21 |

| 4.3    | STRUCTURE                                                                                          | 21 |

|        | 4.3.1 Read-out Protection                                                                          | 21 |

| 4.4    |                                                                                                    | 22 |

| 4.5    | ICP (IN-CIRCUIT PROGRAMMING)                                                                       | 23 |

| 4.6    | IAP (IN-APPLICATION PROGRAMMING)                                                                   | 23 |

| 4.7    | RELATED DOCUMENTATION                                                                              | 23 |

|        | 4.7.1 Register Description                                                                         | 23 |

| 5 CEN  |                                                                                                    |    |

| 5.1    |                                                                                                    | 24 |

| 5.2    | MAIN FEATURES                                                                                      | 24 |

| 5.3    | CPU REGISTERS                                                                                      | 24 |

| 6 SUP  | PLY, RESET AND CLOCK MANAGEMENT                                                                    | 27 |

|        | PHASE LOCKED LOOP                                                                                  |    |

|        | MULTI-OSCILLATOR (MO)                                                                              |    |

|        | RESET SEQUENCE MANAGER (RSM)                                                                       |    |

|        | 6.3.1 Introduction                                                                                 |    |

|        | 6.3.2 Asynchronous External RESET pin                                                              |    |

|        | 6.3.3 External Power-On RESET                                                                      |    |

|        | 6.3.4 Internal Low Voltage Detector (LVD) RESET                                                    | 30 |

|        | 6.3.5 Internal Watchdog RESET                                                                      | 30 |

| 6.4    | SYSTEM INTEGRITY MANAGEMENT (SI)                                                                   |    |

|        | 6.4.1 Low Voltage Detector (LVD)                                                                   |    |

|        | <ul><li>6.4.2 Auxiliary Voltage Detector (AVD)</li><li>6.4.3 Clock Security System (CSS)</li></ul> |    |

|        | 6.4.4 Low Power Modes                                                                              |    |

|        | 6.4.5 Register Description                                                                         |    |

| 7 INTE |                                                                                                    |    |

| 7.1    |                                                                                                    | 36 |

| 7.2    | MASKING AND PROCESSING FLOW                                                                        | 36 |

| 7.3    | INTERRUPTS AND LOW POWER MODES                                                                     | 38 |

|        | CONCURRENT & NESTED MANAGEMENT                                                                     |    |

| 7.5    | INTERRUPT REGISTER DESCRIPTION                                                                     | 39 |

|        | EXTERNAL INTERRUPTS                                                                                |    |

| 110    | 7.6.1 I/O Port Interrupt Sensitivity                                                               |    |

| 7.7    | EXTERNAL INTERRUPT CONTROL REGISTER (EICR)                                                         | 43 |

|        | VER SAVING MODES                                                                                   |    |

|        |                                                                                                    |    |

|        | SLOW MODE                                                                                          |    |

57

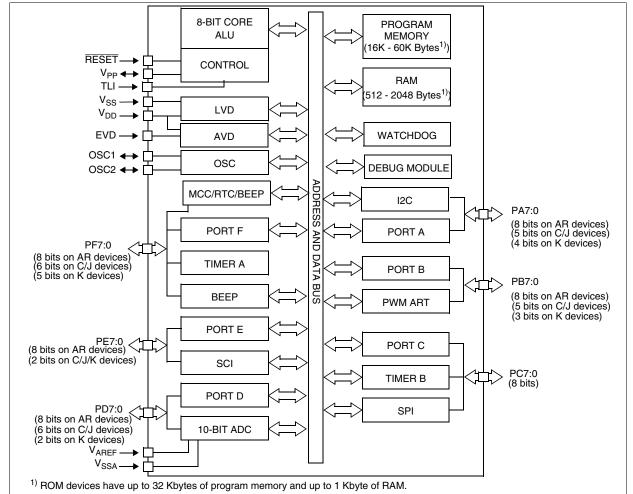

# **1 DESCRIPTION**

The ST72F325 Flash and ST72325 ROM devices are members of the ST7 microcontroller family designed for mid-range applications.

They are derivatives of the ST72321 and ST72324 devices, with enhanced characteristics and robust Clock Security System.

All devices are based on a common industrystandard 8-bit core, featuring an enhanced instruction set and are available with Flash or ROM program memory. The ST7 family architecture offers both power and flexibility to software developers, enabling the design of highly efficient and compact application code.

The on-chip peripherals include an A/D converter, a PWM Autoreload timer, 2 general purpose timers, I<sup>2</sup>C bus, SPI interface and an SCI interface.

For power economy, microcontroller can switch dynamically into WAIT, SLOW, ACTIVE-HALT or

HALT mode when the application is in idle or stand-by state.

Typical applications are consumer, home, office and industrial products.

The devices feature an on-chip Debug Module (DM) to support in-circuit debugging (ICD). For a description of the DM registers, refer to the ST7 ICC Protocol Reference Manual.

# Main Differences with ST72321:

- LQFP48 and LQFP32 packages

- Clock Security System

- Internal RC, Readout protection, LVD and PLL without limitations

- Negative current injection not allowed on I/O port PB0 (instead of PC6).

- External interrupts have Exit from Active Halt mode capability.

# Figure 1. Device Block Diagram

<u>/</u>ک

<u>ل</u>حک

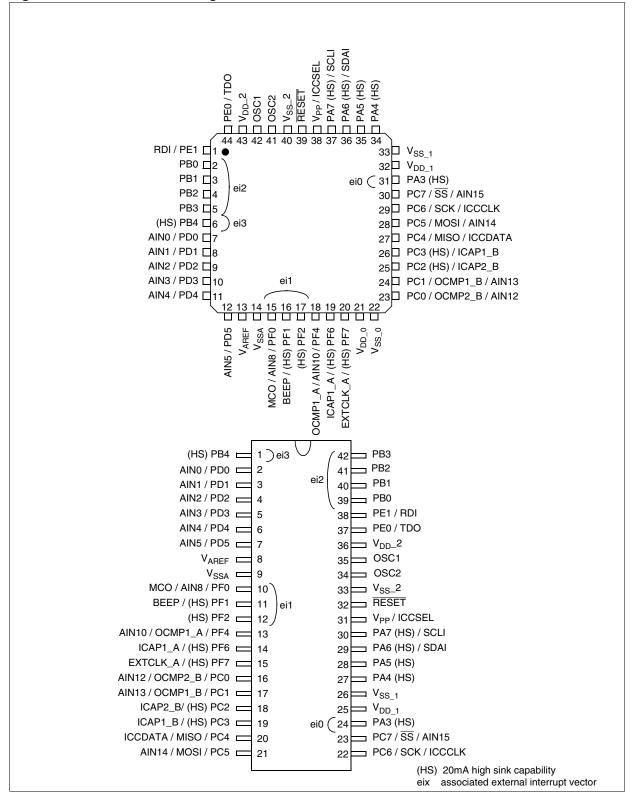

|        | F       | Pin n   | 0      |        |                                 |          | Le             | evel   |       |     | Р   | ort |                 |                 | Main                                          |                                                                                                         |                                                 |  |

|--------|---------|---------|--------|--------|---------------------------------|----------|----------------|--------|-------|-----|-----|-----|-----------------|-----------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|

| P64    | 48C     | 48S     | P44    | o42    | Pin Name                        | Type     | ut             | out    |       | Inp | out |     | Out             | tput            | function<br>(after                            | Alternate                                                                                               | function                                        |  |

| LQFP64 | LQFP48C | LQFP48S | LQFP44 | SDIP42 |                                 | <b> </b> | Input          | Output | float | wpu | int | ana | OD              | РР              | reset)                                        |                                                                                                         |                                                 |  |

| 42     | 32      | 32      | 30     | 23     | PC7/SS/AIN15                    | I/O      | CT             |        | x     | х   |     | х   | x               | x               | Port C7                                       | SPI Slave<br>Select (ac-<br>tive low)                                                                   | ADC Ana-<br>log<br>Input 15                     |  |

| 43     | _4)     | -       | -      | -      | PA0                             | I/O      | $C_T$          |        | Х     | e   | i0  |     | Х               | Х               | Port A0                                       |                                                                                                         |                                                 |  |

| 44     | _4)     | -       | -      | -      | PA1                             | I/O      | $C_T$          |        | Χ     | e   | i0  |     | Х               | Х               | Port A1                                       |                                                                                                         |                                                 |  |

| 45     | 33      | -       | -      | -      | PA2                             | I/O      | $C_T$          |        | Х     | e   | i0  |     | Х               | Х               | Port A2                                       |                                                                                                         |                                                 |  |

| 46     | 34      | 34      | 31     | 24     | PA3 (HS)                        | I/O      | $C_T$          | HS     | Х     |     | ei0 |     | Х               | Х               | Port A3                                       |                                                                                                         |                                                 |  |

| 47     | 35      | 35      | 32     | 25     | V <sub>DD_1</sub> <sup>6)</sup> | S        |                |        |       |     |     |     |                 |                 | Digital M                                     | ain Supply Vo                                                                                           | oltage                                          |  |

| 48     | 36      | 36      | 33     | 26     | V <sub>SS_1</sub> <sup>6)</sup> | S        |                |        |       |     |     |     |                 |                 | Digital G                                     | round Voltage                                                                                           | )                                               |  |

| 49     | 37      | 37      | 34     | 27     | PA4 (HS)                        | I/O      | $C_T$          | HS     | Χ     | Х   |     |     | Х               | Х               | Port A4                                       | Port A4                                                                                                 |                                                 |  |

| 50     | 38      | 38      | 35     | 28     | PA5 (HS)                        | I/O      | $C_{T}$        | HS     | Х     | Х   |     |     | Х               | Х               | Port A5                                       |                                                                                                         |                                                 |  |

| 51     | 39      | 39      | 36     | 29     | PA6 (HS)/SDAI                   | I/O      | $C_{T}$        | HS     | Χ     |     |     |     | Т               |                 | Port A6 I <sup>2</sup> C Data <sup>1)</sup>   |                                                                                                         |                                                 |  |

| 52     | 40      | 40      | 37     | 30     | PA7 (HS)/SCLI                   | I/O      | $C_T$          | HS     | Х     |     |     |     | Т               |                 | Port A7 I <sup>2</sup> C Clock <sup>1)</sup>  |                                                                                                         |                                                 |  |

| 53     | 41      | 41      | 38     | 31     | V <sub>PP</sub> / ICCSEL        | I        |                |        |       |     |     |     |                 |                 | ming mo<br>programi<br>See Sect<br>tails. Hig | ied low. In flas<br>de, this pin ac<br>ming voltage i<br>ion 12.9.2 for<br>h voltage mus<br>ROM devices | ts as the<br>nput V <sub>PP</sub> .<br>more de- |  |

| 54     | 42      | 42      | 39     | 32     | RESET                           | I/O      | CT             |        |       |     |     |     |                 |                 | Top prior<br>rupt.                            | ity non maska                                                                                           | able inter-                                     |  |

| 55     | -       | -       | -      | -      | EVD                             |          |                |        |       |     |     |     |                 |                 | External                                      | voltage detec                                                                                           | tor                                             |  |

| 56     | -       | -       | -      | -      | TLI                             | Ι        | C <sub>T</sub> |        |       |     | Х   |     |                 |                 | Top leve                                      | interrupt inpu                                                                                          | ut pin                                          |  |

| 57     | 43      | 43      | 40     | 33     | V <sub>SS_2</sub> <sup>6)</sup> | S        |                |        |       |     |     |     |                 |                 | Digital G                                     | round Voltage                                                                                           | )                                               |  |

| 58     | 44      | 44      | 41     | 34     | OSC2 <sup>3)</sup>              | I/O      |                |        |       |     |     |     |                 |                 | Resonate<br>put                               | or oscillator in                                                                                        | verter out-                                     |  |

| 59     | 45      | 45      | 42     | 35     | OSC1 <sup>3)</sup>              | I        |                |        |       |     |     |     |                 |                 |                                               | External clock input or Resonator oscillator inverter input                                             |                                                 |  |

| 60     | 46      | 46      | 43     | 36     | V <sub>DD_2</sub> <sup>6)</sup> | S        |                |        |       |     |     |     |                 |                 | Digital M                                     | ain Supply Vo                                                                                           | oltage                                          |  |

| 61     | 47      | 47      | 44     | 37     | PE0/TDO                         | I/O      | $C_T$          |        | Х     | Х   |     |     | Х               | Х               | Port E0                                       | SCI Transm                                                                                              | it Data Out                                     |  |

| 62     | 48      | 48      | 1      | 38     | PE1/RDI                         | I/O      | $C_T$          |        | Х     | Х   |     |     | Х               | Х               | Port E1                                       | SCI Receive                                                                                             | e Data In                                       |  |

| 63     | 1       | -       | -      | -      | PE2                             | I/O      | $C_{T}$        |        | Х     | Х   |     |     | X <sup>4)</sup> | X <sup>4)</sup> | Port E2                                       |                                                                                                         |                                                 |  |

| 64     | -4)     | -       | -      | -      | PE3                             | I/O      | $C_T$          |        | Х     | Х   |     |     | Х               | Х               | Port E3                                       |                                                                                                         |                                                 |  |

57

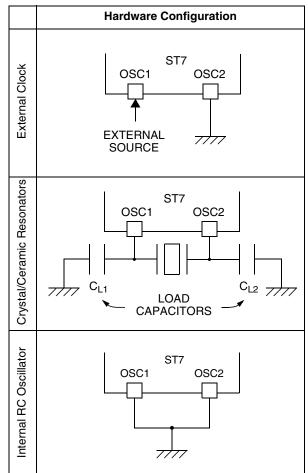

# 6.2 MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by three different source types coming from the multioscillator block:

- an external source

- 4 crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 6. Refer to the electrical characteristics section for more details.

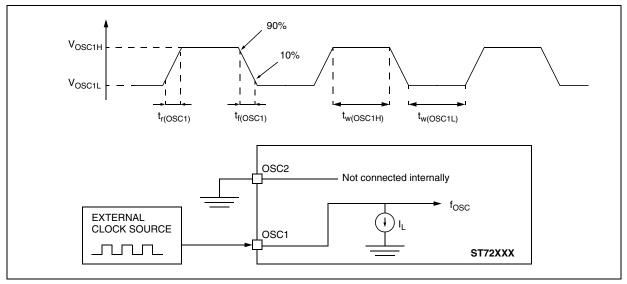

#### **External Clock Source**

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

## **Crystal/Ceramic Oscillators**

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of 4 oscillators with different frequency ranges has to be done by option byte in order to reduce consumption (refer to section 14.1 on page 181 for more details on the frequency ranges). In this mode of the multi-oscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

# Internal RC Oscillator

This oscillator allows a low cost solution for the main clock of the ST7 using only an internal resistor and capacitor. Internal RC oscillator mode has the drawback of a lower frequency accuracy and should not be used in applications that require accurate timing.

In this mode, the two oscillator pins have to be tied to ground.

Table 6. ST7 Clock Sources

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

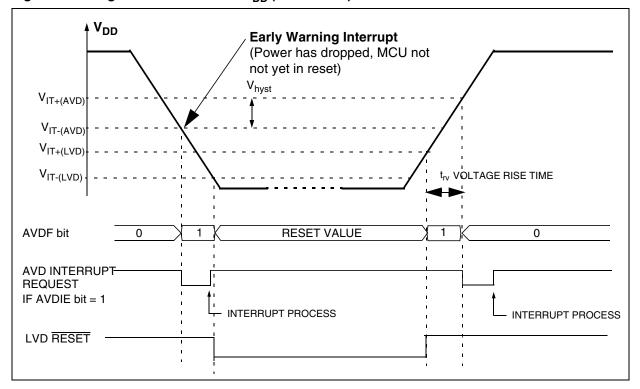

## 6.4.2 Auxiliary Voltage Detector (AVD)

The Voltage Detector function (AVD) is based on an analog comparison between a V<sub>IT-(AVD)</sub> and V<sub>IT+(AVD)</sub> reference value and the V<sub>DD</sub> main supply or the external EVD pin voltage level (V<sub>EVD</sub>). The V<sub>IT</sub> reference value for falling voltage is lower than the V<sub>IT+</sub> reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real time status bit (AVDF) in the SICSR register. This bit is read only.

**Caution**: The AVD function is active only if the LVD is enabled through the option byte.

# 6.4.2.1 Monitoring the V<sub>DD</sub> Main Supply

This mode is selected by clearing the AVDS bit in the SICSR register.

The AVD voltage threshold value is relative to the selected LVD threshold configured by option byte (see section 14.1 on page 181).

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the V<sub>IT+(AVD)</sub> or V<sub>IT-(AVD)</sub> threshold (AVDF bit toggles).

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut down safely before the LVD resets the microcontroller. See Figure 18.

The interrupt on the rising edge is used to inform the application that the  $V_{DD}$  warning state is over.

If the voltage rise time  $t_{rv}$  is less than 256 or 4096 CPU cycles (depending on the reset delay selected by option byte), no AVD interrupt will be generated when  $V_{\rm IT+(AVD)}$  is reached.

If  $t_{rv}$  is greater than 256 or 4096 cycles then:

- If the AVD interrupt is enabled before the  $V_{IT+(AVD)}$  threshold is reached, then 2 AVD interrupts will be received: the first when the AVDIE bit is set, and the second when the threshold is reached.

- If the AVD interrupt is enabled after the V<sub>IT+(AVD)</sub> threshold is reached then only one AVD interrupt will occur.

**67/**

Figure 18. Using the AVD to Monitor V<sub>DD</sub> (AVDS bit=0)

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

# 6.4.5 Register Description

# SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

### Read/Write

Reset Value: 000x 000x (00h)

| 7   |    |     |    |   |     |   | 0   |

|-----|----|-----|----|---|-----|---|-----|

| AVD |    | AVD |    | 0 | CSS |   | WDG |

| 5   | IE | Г   | RF |   |     | D | RF  |

## Bit 7 = **AVDS** Voltage Detection selection

This bit is set and cleared by software. Voltage Detection is available only if the LVD is enabled by option byte.

0: Voltage detection on V<sub>DD</sub> supply

1: Voltage detection on EVD pin

## Bit 6 = **AVDIE** Voltage Detector interrupt enable

This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag changes (toggles). The pending interrupt information is automatically cleared when software enters the AVD interrupt routine. 0: AVD interrupt disabled

1: AVD interrupt enabled

## Bit 5 = **AVDF** Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to Figure 18 and to Section 6.4.2.1 for additional details.

0:  $V_{DD}$  or  $V_{EVD}$  over  $V_{IT+(AVD)}$  threshold 1:  $V_{DD}$  or  $V_{EVD}$  under  $V_{IT-(AVD)}$  threshold

#### Bit 4 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag description for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

Bit 3 = Reserved, must be kept cleared.

Bit 2 = **CSSIE** *Clock security syst interrupt enable* This bit enables the interrupt when a disturbance is detected by the Clock Security System (CSSD bit set). It is set and cleared by software.0: Clock security system interrupt disabled1: Clock security system interrupt enabledWhen the CSS is disabled by OPTION BYTE, the CSSIE bit has no effect.

#### Bit 1 = **CSSD** Clock security system detection

This bit indicates that the safe oscillator of the Clock Security System block has been selected by hardware due to a disturbance on the main clock signal ( $f_{OSC}$ ). It is set by hardware and cleared by reading the SICSR register when the original oscillator recovers.

0: Safe oscillator is not active

1: Safe oscillator has been activated

When the CSS is disabled by OPTION BYTE, the CSSD bit value is forced to 0.

# Bit 0 = WDGRF Watchdog reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| <b>RESET Sources</b> | LVDRF | WDGRF |

|----------------------|-------|-------|

| External RESET pin   | 0     | 0     |

| Watchdog             | 0     | 1     |

| LVD                  | 1     | Х     |

## **Application notes**

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

**CAUTION:** When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

57

# WATCHDOG TIMER (Cont'd)

# 10.1.5 Low Power Modes

| Mode | Description  |             |                                                                                                                                                                                                                                                                                                                                |

|------|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLOW | No effect on | Watchdog.   |                                                                                                                                                                                                                                                                                                                                |

| WAIT | No effect on | Watchdog.   |                                                                                                                                                                                                                                                                                                                                |

|      | OIE bit in   | WDGHALT bit |                                                                                                                                                                                                                                                                                                                                |

|      | MCCSR        | in Option   |                                                                                                                                                                                                                                                                                                                                |

|      | register     | Byte        |                                                                                                                                                                                                                                                                                                                                |

| -    | 0            | 0           | No Watchdog reset is generated. The MCU enters Halt mode. The Watch-<br>dog counter is decremented once and then stops counting and is no longer<br>able to generate a watchdog reset until the MCU receives an external inter-<br>rupt or a reset.                                                                            |

| HALT | 0            |             | If an external interrupt is received, the Watchdog restarts counting after 256 or 4096 CPU clocks. If a reset is generated, the Watchdog is disabled (reset state) unless Hardware Watchdog is selected by option byte. For application recommendations see Section 0.1.7 below.                                               |

|      | 0            | 1           | A reset is generated.                                                                                                                                                                                                                                                                                                          |

|      | 1            | x           | No reset is generated. The MCU enters Active Halt mode. The Watchdog counter is not decremented. It stop counting. When the MCU receives an oscillator interrupt or external interrupt, the Watchdog restarts counting immediately. When the MCU receives a reset the Watchdog restarts counting after 256 or 4096 CPU clocks. |

# 10.1.6 Hardware Watchdog Option

If Hardware Watchdog is selected by option byte, the watchdog is always active and the WDGA bit in the WDGCR is not used. Refer to the Option Byte description.

# 10.1.7 Using Halt Mode with the WDG (WDGHALT option)

The following recommendation applies if Halt mode is used when the watchdog is enabled.

Before executing the HALT instruction, refresh the WDG counter, to avoid an unexpected WDG reset immediately after waking up the microcontroller.

## 10.1.8 Interrupts

None.

# 10.1.9 Register Description CONTROL REGISTER (WDGCR)

## Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | Т3 | T2 | T1 | то |

Bit 7 = **WDGA** Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset. 0: Watchdog disabled 1: Watchdog enabled

**Note:** This bit is not used if the hardware watchdog option is enabled by option byte.

Bit 6:0 = **T[6:0]** 7-bit counter (MSB to LSB). These bits contain the value of the watchdog counter. It is decremented every 16384  $f_{OSC2}$  cycles (approx.). A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared).

57

# ST72325xx

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 002Ah             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | T0 |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

# Table 15. Watchdog Timer Register Map and Reset Values

# **ON-CHIP PERIPHERALS** (Cont'd)

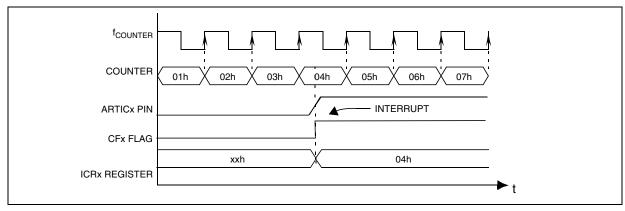

#### Input capture function

This mode allows the measurement of external signal pulse widths through ARTICRx registers.

Each input capture can generate an interrupt independently on a selected input signal transition. This event is flagged by a set of the corresponding CFx bits of the Input Capture Control/Status register (ARTICCSR).

These input capture interrupts are enabled through the CIEx bits of the ARTICCSR register.

The active transition (falling or rising edge) is software programmable through the CSx bits of the ARTICCSR register.

The read only input capture registers (ARTICRx) are used to latch the auto-reload counter value when a transition is detected on the ARTICx pin (CFx bit set in ARTICCSR register). After fetching the interrupt vector, the CFx flags can be read to identify the interrupt source.

**Note**: After a capture detection, data transfer in the ARTICRx register is inhibited until it is read (clearing the CFx bit).

The timer interrupt remains pending while the CFx flag is set when the interrupt is enabled (CIEx bit set). This means, the ARTICRx register has to be read at each capture event to clear the CFx flag.

The timing resolution is given by auto-reload counter cycle time  $(1/f_{COUNTER})$ .

**Note:** During HALT mode, if both input capture and external clock are enabled, the ARTICRx register value is not guaranteed if the input capture pin and the external clock change simultaneously.

## Figure 44. Input Capture Timing Diagram

## External interrupt capability

This mode allows the Input capture capabilities to be used as external interrupt sources. The interrupts are generated on the edge of the ARTICx signal.

The edge sensitivity of the external interrupts is programmable (CSx bit of ARTICCSR register) and they are independently enabled through CIEx bits of the ARTICCSR register. After fetching the interrupt vector, the CFx flags can be read to identify the interrupt source.

During HALT mode, the external interrupts can be used to wake up the micro (if the CIEx bit is set).

# SERIAL PERIPHERAL INTERFACE (Cont'd)

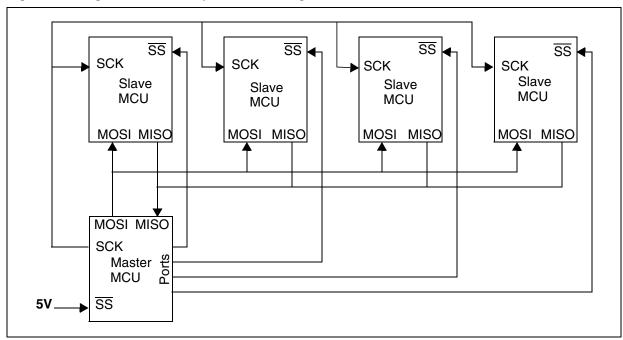

#### 10.5.5.4 Single Master Systems

A typical single master system may be configured, using an MCU as the master and four MCUs as slaves (see Figure 62).

The master device selects the individual slave devices by using four pins of a parallel port to control the four SS pins of the slave devices.

The  $\overline{SS}$  pins are pulled high during reset since the master device ports will be forced to be inputs at that time, thus disabling the slave devices.

**Note:** To prevent a bus conflict on the MISO line the master allows only one active slave device during a transmission.

For more security, the slave device may respond to the master with the received data byte. Then the master will receive the previous byte back from the slave device if all MISO and MOSI pins are connected and the slave has not written to its SPIDR register.

Other transmission security methods can use ports for handshake lines or data bytes with command fields.

#### Figure 62. Single Master / Multiple Slave Configuration

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

# 10.7.7 Register Description

# I<sup>2</sup>C CONTROL REGISTER (CR)

Read / Write Reset Value: 0000 0000 (00h)

| 7 |   |    |      |       |     |      | 0   |

|---|---|----|------|-------|-----|------|-----|

| 0 | 0 | PE | ENGC | START | ACK | STOP | ITE |

Bit 7:6 = Reserved. Forced to 0 by hardware.

## Bit 5 = **PE** Peripheral enable.

This bit is set and cleared by software.

- 0: Peripheral disabled

- 1: Master/Slave capability

Notes:

- When PE=0, all the bits of the CR register and the SR register except the Stop bit are reset. All outputs are released while PE=0

- When PE=1, the corresponding I/O pins are selected by hardware as alternate functions.

- To enable the I<sup>2</sup>C interface, write the CR register TWICE with PE=1 as the first write only activates the interface (only PE is set).

# Bit 4 = **ENGC** Enable General Call.

This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE=0). The 00h General Call address is acknowledged (01h ignored). 0: General Call disabled

1: General Call enabled

**Note:** In accordance with the I2C standard, when GCAL addressing is enabled, an I2C slave can only receive data. It will not transmit data to the master.

Bit 3 = **START** Generation of a Start condition. This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE=0) or when the Start condition is sent (with interrupt generation if ITE=1).

In master mode:

- 0: No start generation

- 1: Repeated start generation

- In slave mode:

- 0: No start generation

- 1: Start generation when the bus is free

Bit 2 = **ACK** Acknowledge enable.

This bit is set and cleared by software. It is also cleared by hardware when the interface is disabled (PE=0).

- 0: No acknowledge returned

- 1: Acknowledge returned after an address byte or a data byte is received

Bit 1 = **STOP** Generation of a Stop condition. This bit is set and cleared by software. It is also cleared by hardware in master mode. Note: This bit is not cleared when the interface is disabled (PE=0).

In master mode:

0: No stop generation

1: Stop generation after the current byte transfer or after the current Start condition is sent. The STOP bit is cleared by hardware when the Stop condition is sent.

– In slave mode:

0: No stop generation

1: Release the SCL and SDA lines after the current byte transfer (BTF=1). In this mode the STOP bit has to be cleared by software.

## Bit 0 = ITE Interrupt enable.

This bit is set and cleared by software and cleared by hardware when the interface is disabled (PE=0).

0: Interrupts disabled

1: Interrupts enabled

Refer to Figure 70 for the relationship between the events and the interrupt.

SCL is held low when the ADD10, SB, BTF or ADSL flags or an EV6 event (See Figure 69) is detected.

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

# 12.4.3 On-Chip Peripherals

Measured on LQFP64 generic board  $T_A = 25^{\circ}C f_{CPU} = 4MHz$ .

| Symbol               | Parameter                                        | Conditions            | Тур | Unit |

|----------------------|--------------------------------------------------|-----------------------|-----|------|

| I <sub>DD(TIM)</sub> | 16-bit Timer supply current <sup>1)</sup>        | V <sub>DD</sub> =5.0V | 50  | μA   |

| I <sub>DD(ART)</sub> | ART PWM supply current <sup>2)</sup>             | V <sub>DD</sub> =5.0V | 75  | μA   |

| I <sub>DD(SPI)</sub> | SPI supply current <sup>3)</sup>                 | V <sub>DD</sub> =5.0V | 400 | μA   |

| I <sub>DD(SCI)</sub> | SCI supply current <sup>4)</sup>                 | V <sub>DD</sub> =5.0V | 400 | μA   |

| I <sub>DD(I2C)</sub> | I2C supply current <sup>5)</sup>                 | V <sub>DD</sub> =5.0V | 175 | μA   |

| I <sub>DD(ADC)</sub> | ADC supply current when converting <sup>6)</sup> | V <sub>DD</sub> =5.0V | 400 | μA   |

Notes:

- 1. Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer counter running at f<sub>CPU</sub>/4) and timer counter stopped (only TIMD bit set). Data valid for one timer.

- Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer stopped) and timer counter enabled (only TCE bit set).

3. Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to 55h). This measurement includes the pad toggling consumption.

4. Data based on a differential I<sub>DD</sub> measurement between SCI low power state (SCID=1) and a permanent SCI data transmit sequence.

5. Data based on a differential I<sub>DD</sub> measurement between reset configuration (I2C disabled) and a permanent I2C master communication at 100kHz (data sent equal to 55h). This measurement include the pad toggling consumption (27kOhm external pull-up on clock and data lines).

6. Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions.

# **12.5 CLOCK AND TIMING CHARACTERISTICS**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

# 12.5.1 General Timings

| Symbol               | Parameter                             | Conditions             | Min  | <b>Typ</b> <sup>1)</sup> | Max  | Unit             |

|----------------------|---------------------------------------|------------------------|------|--------------------------|------|------------------|

| +                    | Instruction quals time                |                        | 2    | 3                        | 12   | t <sub>CPU</sub> |

| <sup>I</sup> c(INST) | Instruction cycle time                | f <sub>CPU</sub> =8MHz | 250  | 375                      | 1500 | ns               |

| +                    | Interrupt reaction time <sup>2)</sup> |                        | 10   |                          | 22   | t <sub>CPU</sub> |

| τ <sub>v(IT)</sub>   | $t_{v(IT)} = \Delta t_{c(INST)} + 10$ | f <sub>CPU</sub> =8MHz | 1.25 |                          | 2.75 | μs               |

# 12.5.2 External Clock Source

| Symbol                                         | Parameter                            | Conditions                       | Min                             | Тур | Max                             | Unit |

|------------------------------------------------|--------------------------------------|----------------------------------|---------------------------------|-----|---------------------------------|------|

| V <sub>OSC1H</sub>                             | OSC1 input pin high level voltage    |                                  | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     | V <sub>DD</sub>                 | V    |

| V <sub>OSC1L</sub>                             | OSC1 input pin low level voltage     |                                  | V <sub>SS</sub>                 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | v    |

| t <sub>w(OSC1H)</sub><br>t <sub>w(OSC1L)</sub> | OSC1 high or low time <sup>3)</sup>  | see Figure 75                    | 5                               |     |                                 | ns   |

| t <sub>r(OSC1)</sub><br>t <sub>f(OSC1)</sub>   | OSC1 rise or fall time <sup>3)</sup> |                                  |                                 |     | 15                              | 113  |

| ١L                                             | OSC1 Input leakage current           | $V_{SS} \leq V_{IN} \leq V_{DD}$ |                                 |     | ±1                              | μA   |

# Figure 75. Typical Application with an External Clock Source

#### Notes:

1. Data based on typical application software.

2. Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{c(INST)}$  is the number of  $t_{CPU}$  cycles needed to finish the current instruction execution.

3. Data based on design simulation and/or technology characteristics, not tested in production.

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

## 12.5.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                             | Parameter                                                                                                         | Conditions                                                                                                                                                                | Min                  | Max                  | Unit |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| f <sub>OSC</sub>                   | Oscillator Frequency <sup>1)</sup>                                                                                |                                                                                                                                                                           | 1                    | 16                   | MHz  |

| R <sub>F</sub>                     | Feedback resistor <sup>2)</sup>                                                                                   |                                                                                                                                                                           | 20                   | 40                   | kΩ   |

| C <sub>L1</sub><br>C <sub>L2</sub> | Recommended load capacitance versus equivalent serial resistance of the crystal or ceramic resonator $(R_S)^{3)}$ | $f_{OSC} = 1 \text{ to } 2 \text{ MHz}$<br>$f_{OSC} = 2 \text{ to } 4 \text{ MHz}$<br>$f_{OSC} = 4 \text{ to } 8 \text{ MHz}$<br>$f_{OSC} = 8 \text{ to } 16 \text{ MHz}$ | 20<br>20<br>15<br>15 | 60<br>50<br>35<br>35 | pF   |

| Symbol         | Parameter            | Conditions                                                                                                                                                                                                   | Тур                      | Max | Unit |

|----------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|

| i <sub>2</sub> | OSC2 driving current | $V_{DD}=5V: \\ f_{OSC}=2MHz, C0 = 6pF, CI1 = CI2 = 68pF \\ f_{OSC}=4MHz, C0 = 6pF, CI1 = CI2 = 68pF \\ f_{OSC}=8MHz, C0 = 6pF, CI1 = CI2 = 40pF \\ f_{OSC}=16MHz, C0 = 7pF, CI1 = CI2 = 20pF \\ \end{cases}$ | 426<br>425<br>456<br>660 |     | μA   |

#### Notes:

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

2. Data based on characterisation results, not tested in production.

# **12.8 I/O PORT PIN CHARACTERISTICS**

## 12.8.1 General Characteristics

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{OSC}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                              | Parameter                                                | Conditions                                        |                        | Min                             | Тур | Max                             | Unit             |

|-------------------------------------|----------------------------------------------------------|---------------------------------------------------|------------------------|---------------------------------|-----|---------------------------------|------------------|

| V <sub>IL</sub>                     | Input low level voltage 1)                               | CMOS ports                                        |                        |                                 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | v                |

| V <sub>IH</sub>                     | Input high level voltage 1)                              |                                                   |                        | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     |                                 |                  |

| V <sub>hys</sub>                    | Schmitt trigger voltage hysteresis 2)                    |                                                   |                        |                                 | 0.7 |                                 |                  |

| I <sub>INJ(PIN)</sub> <sup>3)</sup> | Injected Current on PB0 (Flash de-<br>vices only)        |                                                   |                        | 0                               |     | +4                              |                  |

|                                     | Injected Current on an I/O pin                           | V <sub>DD</sub> =5V                               |                        |                                 |     | ± 4                             | mA               |

| $\Sigma I_{\rm INJ(PIN)}^{3)}$      | Total injected current (sum of all I/O and control pins) |                                                   |                        |                                 |     | ± 25                            |                  |

| ١L                                  | Input leakage current                                    | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub> |                        |                                 |     | ±1                              |                  |

| I <sub>S</sub>                      | Static current consumption                               | Floating inpu                                     | Floating input mode 4) |                                 | 400 |                                 | μA               |

| R <sub>PU</sub>                     | Weak pull-up equivalent resistor 5)                      | V <sub>IN</sub> =V <sub>SS</sub>                  | V <sub>DD</sub> =5V    | 50                              | 120 | 250                             | kΩ               |

| C <sub>IO</sub>                     | I/O pin capacitance                                      | <b>(</b>                                          |                        |                                 | 5   |                                 | pF               |

| t <sub>f(IO)out</sub>               | Output high to low level fall time <sup>1)</sup>         | C <sub>L</sub> =50pF<br>Between 10% and 90%       |                        |                                 | 25  |                                 | ns               |

| t <sub>r(IO)out</sub>               | Output low to high level rise time <sup>1)</sup>         |                                                   |                        |                                 | 25  |                                 | 115              |

| t <sub>w(IT)in</sub>                | External interrupt pulse time 6)                         |                                                   |                        | 1                               |     |                                 | t <sub>CPU</sub> |

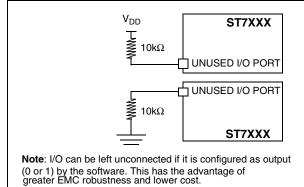

Figure 79. Unused I/Os configured as input

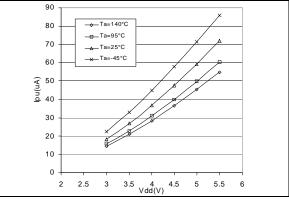

# Figure 80. Typical I<sub>PU</sub> vs. V<sub>DD</sub> with V<sub>IN</sub>=V<sub>SS</sub>

#### Notes:

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

3. When the current limitation is not possible, the V<sub>IN</sub> maximum must be respected, otherwise refer to I<sub>INJ(PIN)</sub> specification. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. Refer to section 12.2.2 on page 143 for more details.

4. Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example and leaving the I/O unconnected on the board or an external pull-up or pull-down resistor (see Figure 79). Static peak current value taken at a fixed  $V_{IN}$  value, based on design simulation and technology characteristics, not tested in production. This value depends on  $V_{DD}$  and temperature values.

5. The  $R_{PU}$  pull-up equivalent resistor is based on a resistive transistor (corresponding  $I_{PU}$  current characteristics described in Figure 80).

6. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

# **12.11 COMMUNICATION INTERFACE CHARACTERISTICS**

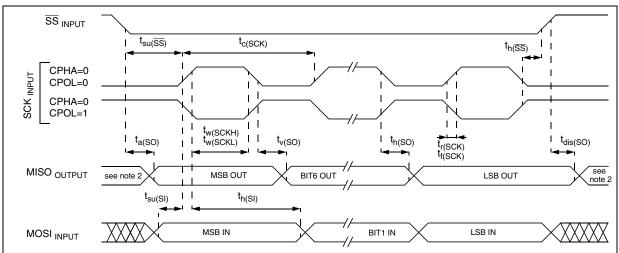

## 12.11.1 SPI - Serial Peripheral Interface

Subject to general operating conditions for  $V_{DD}, f_{CPU},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                    | Conditions                       | Min                             | Max                          | Unit             |

|----------------------------------------------|------------------------------|----------------------------------|---------------------------------|------------------------------|------------------|

| f <sub>SCK</sub>                             | SPI clock frequency          | Master<br>f <sub>CPU</sub> =8MHz | f <sub>CPU</sub> /128<br>0.0625 | f <sub>CPU</sub> /4<br>2     | MHz              |

| 1/t <sub>c(SCK)</sub>                        |                              | Slave<br>f <sub>CPU</sub> =8MHz  | 0                               | foru/2                       |                  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time |                                  | see I/O p                       | see I/O port pin description |                  |

| t <sub>su(SS)</sub>                          | SS setup time <sup>4)</sup>  | Slave                            | t <sub>CPU</sub> + 50           |                              |                  |

| t <sub>h(SS)</sub>                           | SS hold time                 | Slave                            | 120                             |                              |                  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time        | Master<br>Slave                  | 100<br>90                       |                              |                  |

| t <sub>su(MI)</sub><br>t <sub>su(SI)</sub>   | Data input setup time        | Master<br>Slave                  | 100<br>100                      |                              |                  |

| t <sub>h(MI)</sub><br>t <sub>h(SI)</sub>     | Data input hold time         | Master<br>Slave                  | 100<br>100                      |                              | ns               |

| t <sub>a(SO)</sub>                           | Data output access time      | Slave                            | 0                               | 120                          |                  |

| t <sub>dis(SO)</sub>                         | Data output disable time     | Slave                            |                                 | 240                          |                  |

| t <sub>v(SO)</sub>                           | Data output valid time       | Slave (after enable edge)        |                                 | 120                          |                  |

| t <sub>h(SO)</sub>                           | Data output hold time        | Slave (after enable edge)        | 0                               |                              |                  |

| t <sub>v(MO)</sub>                           | Data output valid time       | Master (after enable edge)       |                                 | 120                          | +                |

| t <sub>h(MO)</sub>                           | Data output hold time        |                                  | 0                               |                              | t <sub>CPU</sub> |

# Figure 90. SPI Slave Timing Diagram with CPHA=0<sup>3)</sup>

#### Notes:

1. Data based on design simulation and/or characterisation results, not tested in production.

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

- 3. Measurement points are done at CMOS levels:  $0.3 x V_{\text{DD}}$  and  $0.7 x V_{\text{DD}}.$

- 4. Depends on f<sub>CPU</sub>. For example, if f<sub>CPU</sub> = 8 MHz, then t<sub>CPU</sub> = 1 / f<sub>CPU</sub> = 125 ns and t<sub>su(SS)</sub> = 175 ns.

# ADC CHARACTERISTICS (Cont'd)

# 12.12.1 Analog Power Supply and Reference Pins

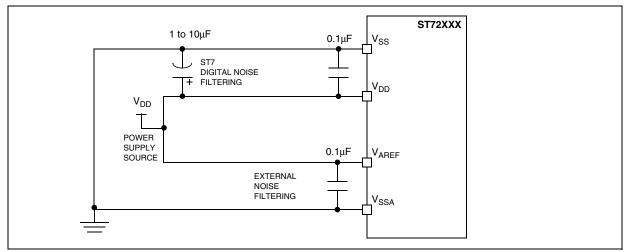

Depending on the MCU pin count, the package may feature separate  $V_{AREF}$  and  $V_{SSA}$  analog power supply pins. These pins supply power to the A/D converter cell and function as the high and low reference voltages for the conversion.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines (see Section 12.12.2 General PCB Design Guidelines).

## 12.12.2 General PCB Design Guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB.

- Filter power to the analog power planes. It is recommended to connect capacitors, with good high frequency characteristics, between the power and ground lines, placing  $0.1\mu$ F and optionally, if needed 10pF capacitors as close as possible to the ST7 power supply pins and a 1 to  $10\mu$ F capacitor close to the power source (see Figure 97).

- The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>AREF</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs on the same I/O port as the A/D input being converted.

**/رک**ا

# Figure 97. Power Supply Filtering

# **13.2 THERMAL CHARACTERISTICS**

| Symbol            | Ratings                                          | Value | Unit |

|-------------------|--------------------------------------------------|-------|------|

|                   | Package thermal resistance (junction to ambient) |       |      |

|                   | LQFP64 10x10                                     | 50    |      |

|                   | LQFP48 7x7                                       | 80    |      |

| R <sub>thJA</sub> | LQFP44 10x10                                     | 52    | °C/W |

|                   | SDIP42                                           | 55    |      |

|                   | LQFP32 7x7                                       | 70    |      |

|                   | SDIP32                                           | 50    |      |

| PD                | Power dissipation <sup>1)</sup>                  | 500   | mW   |

| T <sub>Jmax</sub> | Maximum junction temperature <sup>2)</sup>       | 150   | °C   |

#### Notes:

1. The maximum chip-junction temperature is based on technology characteristics.

2. The maximum power dissipation is obtained from the formula PD = (TJ - TA) / RthJA.

The power dissipation of an application can be defined by the user with the formula: PD=PINT+PPORT where PINT is the chip internal power (IDDxVDD) and PPORT is the port power dissipation depending on the ports used in the application.

# Table 32. ST7 Application Notes

| IDENTIFICATION        | DESCRIPTION                                                                      |  |  |

|-----------------------|----------------------------------------------------------------------------------|--|--|

| AN1947                | ST7MC PMAC SINE WAVE MOTOR CONTROL SOFTWARE LIBRARY                              |  |  |

| GENERAL PURPO         |                                                                                  |  |  |

| AN1476                | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                        |  |  |

| AN1526                | ST7FLITE0 QUICK REFERENCE NOTE                                                   |  |  |

| AN1709                | EMC DESIGN FOR ST MICROCONTROLLERS                                               |  |  |

| AN1752                | ST72324 QUICK REFERENCE NOTE                                                     |  |  |

| PRODUCT EVALU         | ATION                                                                            |  |  |

| AN 910                | PERFORMANCE BENCHMARKING                                                         |  |  |

| AN 990                | ST7 BENEFITS VS INDUSTRY STANDARD                                                |  |  |

| AN1077                | OVERVIEW OF ENHANCED CAN CONTROLLERS FOR ST7 AND ST9 MCUS                        |  |  |

| AN1086                | U435 CAN-DO SOLUTIONS FOR CAR MULTIPLEXING                                       |  |  |

| AN1103                | IMPROVED B-EMF DETECTION FOR LOW SPEED, LOW VOLTAGE WITH ST72141                 |  |  |

| AN1150                | BENCHMARK ST72 VS PC16                                                           |  |  |

| AN1151                | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                                |  |  |

| AN1278                | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                       |  |  |

| PRODUCT MIGRA         | TION                                                                             |  |  |

| AN1131                | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324               |  |  |

| AN1322                | MIGRATING AN APPLICATION FROM ST7263 REV.B TO ST7263B                            |  |  |

| AN1365                | GUIDELINES FOR MIGRATING ST72C254 APPLICATIONS TO ST72F264                       |  |  |

| AN1604                | HOW TO USE ST7MDT1-TRAIN WITH ST72F264                                           |  |  |

| AN2200                | GUIDELINES FOR MIGRATING ST7LITE1X APPLICATIONS TO ST7FLITE1XB                   |  |  |

| PRODUCT OPTIM         | IZATION                                                                          |  |  |

| AN 982                | USING ST7 WITH CERAMIC RESONATOR                                                 |  |  |

| AN1014                | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                        |  |  |

| AN1015                | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE                |  |  |

| AN1040                | MONITORING THE VBUS SIGNAL FOR USB SELF-POWERED DEVICES                          |  |  |

| AN1070                | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                            |  |  |

| AN1181                | ELECTROSTATIC DISCHARGE SENSITIVE MEASUREMENT                                    |  |  |

| AN1324                | CALIBRATING THE RC OSCILLATOR OF THE ST7FLITE0 MCU USING THE MAINS               |  |  |

| AN1502                | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                     |  |  |

| AN1529                | EXTENDING THE CURRENT & VOLTAGE CAPABILITY ON THE ST7265 VDDF SUPPLY             |  |  |

| AN1530                | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLA-<br>TOR |  |  |

| AN1605                | USING AN ACTIVE RC TO WAKEUP THE ST7LITE0 FROM POWER SAVING MODE                 |  |  |

| AN1636                | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                               |  |  |

| AN1828                | PIR (PASSIVE INFRARED) DETECTOR USING THE ST7FLITE05/09/SUPERLITE                |  |  |

| AN1946                | SENSORLESS BLDC MOTOR CONTROL AND BEMF SAMPLING METHODS WITH ST7MC               |  |  |

| AN1953                | PFC FOR ST7MC STARTER KIT                                                        |  |  |

| AN1971                | ST7LITE0 MICROCONTROLLED BALLAST                                                 |  |  |

| PROGRAMMING AND TOOLS |                                                                                  |  |  |

| AN 978                | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                               |  |  |

| AN 983                | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                                |  |  |

| AN 985                | EXECUTING CODE IN ST7 RAM                                                        |  |  |

| AN 986                | USING THE INDIRECT ADDRESSING MODE WITH ST7                                      |  |  |

| AN 987                | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                           |  |  |

| AN 988                | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                            |  |  |

| AN1039                | ST7 MATH UTILITY ROUTINES                                                        |  |  |