#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                     |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40/20MHz                                                                  |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR                                                                       |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 8KB (8K x 8)                                                              |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LQFP                                                                   |

| Supplier Device Package    | 44-VQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at87c52x2-rlrum |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Table 1. Memory Size

|           | ROM (bytes) | EPROM (bytes) | TOTAL RAM (bytes) |

|-----------|-------------|---------------|-------------------|

| TS80C32X2 | 0           | 0             | 256               |

| TS80C52X2 | 8k          | 0             | 256               |

| TS87C52X2 | 0           | 8k            | 256               |

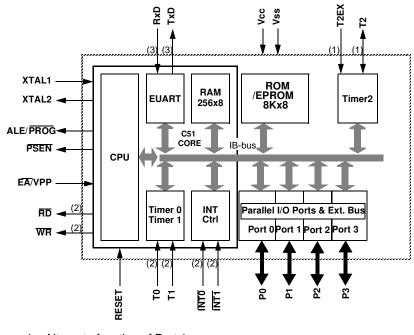

## **Block Diagram**

Notes: 1. Alternate function of Port 1 2. Alternate function of Port 3

## SFR Mapping

The Special Function Registers (SFRs) of the TS80C52X2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- Interrupt system registers: IE, IP, IPH

- Others: AUXR, CKCON

| Table 2. All SFRs with their address and their reset value |

|------------------------------------------------------------|

|------------------------------------------------------------|

|         | Bit<br>Addressable |                    | Non Bit Addressable |                     |                  |                  |                  |                    |     |  |

|---------|--------------------|--------------------|---------------------|---------------------|------------------|------------------|------------------|--------------------|-----|--|

|         | 0/8                | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E              | 7/F                |     |  |

| F8h     |                    |                    |                     |                     |                  |                  |                  |                    | FFh |  |

| F0h     | B<br>0000 0000     |                    |                     |                     |                  |                  |                  |                    | F7h |  |

| E8h     |                    |                    |                     |                     |                  |                  |                  |                    | EFh |  |

| E0h     | ACC<br>0000 0000   |                    |                     |                     |                  |                  |                  |                    | E7h |  |

| D8<br>h |                    |                    |                     |                     |                  |                  |                  |                    | DFh |  |

| D0<br>h | PSW<br>0000 0000   |                    |                     |                     |                  |                  |                  |                    | D7h |  |

| C8<br>h | T2CON<br>0000 0000 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000 | TH2<br>0000 0000 |                  |                    | CFh |  |

| C0<br>h |                    |                    |                     |                     |                  |                  |                  |                    | C7h |  |

| B8h     | IP<br>XX00 0000    | SADEN<br>0000 0000 |                     |                     |                  |                  |                  |                    | BFh |  |

| B0h     | P3<br>1111 1111    |                    |                     |                     |                  |                  |                  | IPH<br>XX00 0000   | B7h |  |

| A8h     | IE<br>0X00 0000    | SADDR<br>0000 0000 |                     |                     |                  |                  |                  |                    | AFh |  |

| A0h     | P2<br>1111 1111    |                    | AUXR1<br>XXXX XXX0  |                     |                  |                  |                  |                    | A7h |  |

| 98h     | SCON<br>0000 0000  | SBUF<br>XXXX XXXX  |                     |                     |                  |                  |                  |                    | 9Fh |  |

| 90h     | P1<br>1111 1111    |                    |                     |                     |                  |                  |                  |                    | 97h |  |

| 88h     | TCON<br>0000 0000  | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000 | TH1<br>0000 0000 | AUXR<br>XXXXXXX0 | CKCON<br>XXXX XXX0 | 8Fh |  |

| 80h     | P0<br>1111 1111    | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                  |                  |                  | PCON<br>00X1 0000  | 87h |  |

|         | 0/8                | 1/9                | 2/A                 | 3/B                 | 4/C              | 5/D              | 6/E              | 7/F                |     |  |

Reserved

| Mnemonic        | I         | Pin Nu           | mber         | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-----------------|-----------|------------------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                 | DIL       | LCC              | VQFP<br>1.4  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| V <sub>SS</sub> | 20        | 22               | 16           | I    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Vss1            |           | 1                | 39           | I    | Optional Ground: Contact the Sales Office for ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| V <sub>CC</sub> | 40        | 44               | 38           | I    | <b>Power Supply:</b> This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P0.0-P0.7       | 39-<br>32 | 43-<br>36        | 37-30        | I/O  | Port 0: Port 0 is an open-drain, bidirectional I/O port. Port 0<br>pins that have 1s written to them float and can be used as<br>high impedance inputs.Port 0 pins must be polarized to Vc<br>or Vss in order to prevent any parasitic current consumptio<br>Port 0 is also the multiplexed low-order address and data b<br>during access to external program and data memory. In thi<br>application, it uses strong internal pull-up when emitting 1s<br>Port 0 also inputs the code bytes during EPROM<br>programming. External pull-ups are required during program<br>verification during which P0 outputs the code bytes.                                                   |  |  |  |

|                 |           |                  |              |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P1.0-P1.7       | 1-8       | 2-9              | 40-44<br>1-3 | I/O  | pull-ups. Port 1 pins that have 1s written to them are pulled<br>high by the internal pull-ups and can be used as inputs. As                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                 |           |                  |              |      | inputs, Port 1 pins that are externally pulled low will source<br>current because of the internal pull-ups. Port 1 also receives<br>the low-order address byte during memory programming an<br>verification.<br>Alternate functions for Port 1 include:                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                 | 1         | 2                | 40           | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 | 2         | 3                | 41           | I    | T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction<br>Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| P2.0-P2.7       | 21-<br>28 | 24-<br>31        | 18-25        | I/O  | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                 |           |                  |              |      | high by the internal pull-ups and can be used as inputs. As<br>inputs, Port 2 pins that are externally pulled low will source<br>current because of the internal pull-ups. Port 2 emits the hig<br>order address byte during fetches from external program<br>memory and during accesses to external data memory that<br>use 16-bit addresses (MOVX atDPTR). In this application, it<br>uses strong internal pull-ups emitting 1s. During accesses to<br>external data memory that use 8-bit addresses (MOVX atRi<br>port 2 emits the contents of the P2 SFR. Some Port 2 pins<br>receive the high order address bits during EPROM<br>programming and verification: P2.0 to P2.4 |  |  |  |

| P3.0-P3.7       | 10-<br>17 | 11,<br>13-<br>19 | 5,<br>7-13   | I/O  | <ul> <li>pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                 |           |                  |              |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                 | 10        | 11               | 5            | 1    | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                 | 11        | 13               | 7            | 0    | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                 | 12        | 14               | 8            | I    | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

6 **TS8xCx2X2**

## TS80C52X2 Enhanced Features

In comparison to the original 80C52, the TS80C52X2 implements some new features, which are:

- The X2 option

- The Dual Data Pointer

- The 4 level interrupt priority system

- The power-off flag

- The ONCE mode

- The ALE disabling

- Some enhanced features are also located in the UART and the Timer 2

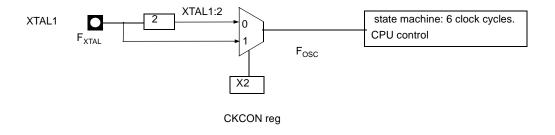

**X2 Feature** The TS80C52X2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power

- Save power consumption while keeping same CPU power (oscillator power saving)

- Save power consumption by dividing dynamically operating frequency by 2 in operating and idle modes

- Increase CPU power by 2 while keeping same crystal frequency

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

Description

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 1. shows the clock generation block diagram. X2 bit is validated on XTAL1÷2 rising edge to avoid glitches when switching from X2 to STD mode. Figure 2 shows the mode switching waveforms.

Figure 1. Clock Generation Diagram

| Timer 2          | The timer 2 in the TS80C52X2 is compatible with the timer 2 in the 80C52.<br>It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2, connected in cascade. It is controlled by T2CON register (See Table 5) and T2MOD register (See Table 6). Timer 2 operation is similar to Timer 0 and Timer 1. C/T2 selects $F_{OSC}/12$ (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to be incremented by the selected input. |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON), as described in the Atmel 8-bit Microcontroller Hardware description.                                                                                                                                                                                                                                                                                              |

|                  | Refer to the Atmel 8-bit Microcontroller Hardware description for the description of Cap-<br>ture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                                                                                                                             |

|                  | In TS80C52X2 Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  | Auto-reload mode with up or down counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Auto-reload Mode | The Auto-reload mode configures timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, timer 2 behaves as in 80C52 (refer to the<br>Atmel 8-bit Microcontroller Hardware description). If DCEN bit is set, timer 2 acts as an<br>Up/down timer/counter as shown in Figure 4. In this mode the T2EX pin controls the<br>direction of count.                                                                                                                                  |

|                  | When T2EX is high, timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                                                                                                 |

|                  | When T2EX is low, timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                                                                                              |

|                  | The EXF2 bit toggles when timer 2 overflows or underflows according to the the direc-<br>tion of the count. EXF2 does not generate any interrupt. This bit can be used to provide<br>17-bit resolution.                                                                                                                                                                                                                                                                                                                      |

### **Power-off Flag**

The power-off flag allows the user to distinguish between a "cold start" reset and a "warm start" reset.

A cold start reset is the one induced by  $V_{CC}$  switch-on. A warm start reset occurs while  $V_{CC}$  is still applied to the device and could be generated for example by an exit from power-down.

The power-off flag (POF) is located in PCON register (See Table 17.). POF is set by hardware when  $V_{CC}$  rises from 0 to its nominal voltage. The POF can be set or cleared by software allowing the user to determine the type of reset.

The POF value is only relevant with a Vcc range from 4.5V to 5.5V. For lower Vcc value, reading POF bit will return indeterminate value.

| 7             | 6               | 5                       | 4                                                                                                                                                                         | 3               | 2             | 1  | 0   |  |  |

|---------------|-----------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|----|-----|--|--|

| SMOD1         | SMOD0           | -                       | POF                                                                                                                                                                       | GF1             | GF0           | PD | IDL |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Descript                | Description                                                                                                                                                               |                 |               |    |     |  |  |

| 7             | SMOD1           |                         | Serial port Mode bit 1<br>Set to select double baud rate in mode 1, 2 or 3.                                                                                               |                 |               |    |     |  |  |

| 6             | SMOD0           | Clear to s              | cerial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register.                                                          |                 |               |    |     |  |  |

| 5             | -               |                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                           |                 |               |    |     |  |  |

| 4             | POF             | Clear to r<br>Set by ha | <b>Power-off Flag</b><br>Clear to recognize next reset type.<br>Set by hardware when V <sub>CC</sub> rises from 0 to its nominal voltage. Can also be<br>set by software. |                 |               |    |     |  |  |

| 3             | GF1             | Cleared b               | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                                              |                 |               |    |     |  |  |

| 2             | GF0             | Cleared b               | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                                              |                 |               |    |     |  |  |

| 1             | PD              | Cleared b               | Power-down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                                            |                 |               |    |     |  |  |

| 0             | IDL             |                         |                                                                                                                                                                           | en interrupt or | reset occurs. |    |     |  |  |

### Table 17. PCON Register

PCON - Power Control Register (87h)

Reset Value = 00X1 0000b Not bit addressable

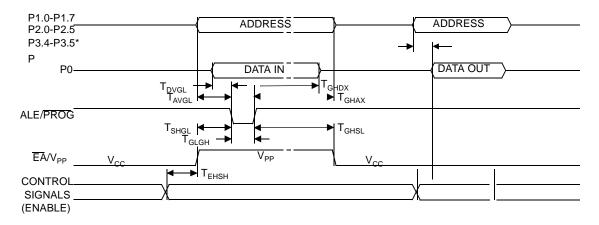

# EPROM Programming and Verification Characteristics

$T_A$  = 21°C to 27°C;  $V_{SS}$  = 0V;  $V_{CC}$  = 5V  $\pm$  10% while programming.  $V_{CC}$  = operating range while verifying.

Table 35. EPROM Programming Parameters

| Symbol              | Parameter                         | Min                  | Max                  | Units |

|---------------------|-----------------------------------|----------------------|----------------------|-------|

| V <sub>PP</sub>     | Programming Supply Voltage        | 12.5                 | 13                   | V     |

| I <sub>PP</sub>     | Programming Supply Current        |                      | 75                   | mA    |

| 1/T <sub>CLCL</sub> | Oscillator Frquency               | 4                    | 6                    | MHz   |

| T <sub>AVGL</sub>   | Address Setup to PROG Low         | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHAX</sub>   | Adress Hold after PROG            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>DVGL</sub>   | Data Setup to PROG Low            | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>GHDX</sub>   | Data Hold after PROG              | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>EHSH</sub>   | (Enable) High to V <sub>PP</sub>  | 48 T <sub>CLCL</sub> |                      |       |

| T <sub>SHGL</sub>   | V <sub>PP</sub> Setup to PROG Low | 10                   |                      | ms    |

| T <sub>GHSL</sub>   | V <sub>PP</sub> Hold after PROG   | 10                   |                      | ms    |

| T <sub>GLGH</sub>   | PROG Width                        | 90                   | 110                  | ms    |

| T <sub>AVQV</sub>   | Address to Valid Data             |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>ELQV</sub>   | ENABLE Low to Data Valid          |                      | 48 T <sub>CLCL</sub> |       |

| T <sub>EHQZ</sub>   | Data Float after ENABLE           | 0                    | 48 T <sub>CLCL</sub> |       |

## EPROM Programming and Verification Waveforms

### Figure 22. EPROM Programming and Verification Waveforms

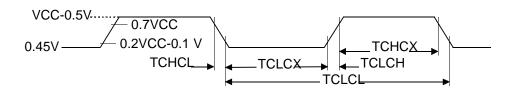

### External Clock Drive Characteristics (XTAL1)

Table 36. AC Parameters

| Symbol                               | Parameter               | Min | Max | Units |

|--------------------------------------|-------------------------|-----|-----|-------|

| T <sub>CLCL</sub>                    | Oscillator Period       | 25  |     | ns    |

| T <sub>CHCX</sub>                    | High Time               | 5   |     | ns    |

| T <sub>CLCX</sub>                    | Low Time                | 5   |     | ns    |

| T <sub>CLCH</sub>                    | Rise Time               |     | 5   | ns    |

| T <sub>CHCL</sub>                    | Fall Time               |     | 5   | ns    |

| T <sub>CHCX</sub> /T <sub>CLCX</sub> | Cyclic ratio in X2 mode | 40  | 60  | %     |

# External Clock Drive Waveforms

Figure 23. External Clock Drive Waveforms

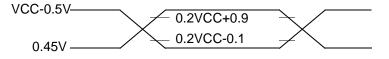

### AC Testing Input/Output Waveforms

Figure 24. AC Testing Input/Output Waveforms

INPUT/OUTPUT

AC inputs during testing are driven at V<sub>CC</sub> - 0.5 for a logic "1" and 0.45V for a logic "0". Timing measurement are made at V<sub>IH</sub> min for a logic "1" and V<sub>IL</sub> max for a logic "0".

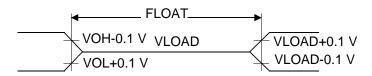

### **Float Waveforms**

Figure 25. Float Waveforms

For timing purposes a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \ge \pm 20$ mA.

### Table 37. Possible Ordering Entries (Continued)

| Part Number <sup>(3)</sup> | Memory Size | Supply Voltage | Temperature<br>Range | Max Frequency         | Package | Packing |  |  |  |  |

|----------------------------|-------------|----------------|----------------------|-----------------------|---------|---------|--|--|--|--|

| AT80C52X2zzz-RLTUM         | 8K ROM      | 5V ±10%        | Industrial & Green   | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |  |  |  |  |

| AT80C52X2zzz-3CSUL         | 8K ROM      | 2.7 to 5.5V    | Industrial & Green   | 30 MHz <sup>(1)</sup> | PDIL40  | Stick   |  |  |  |  |

| AT80C52X2zzz-SLSUL         | 8K ROM      | 2.7 to 5.5V    | Industrial & Green   | 30 MHz <sup>(1)</sup> | PLCC44  | Stick   |  |  |  |  |

| AT80C52X2zzz-RLTUL         | 8K ROM      | 2.7 to 5.5V    | Industrial & Green   | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |  |  |  |  |

| AT80C52X2zzz-3CSUV         | 8K ROM      | 5V ±10%        | Industrial & Green   | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |  |  |  |  |

| AT80C52X2zzz-SLSUV         | 8K ROM      | 5V ±10%        | Industrial & Green   | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |  |  |  |  |

| AT80C52X2zzz-RLTUV         | 8K ROM      | 5V ±10%        | Industrial & Green   | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |  |  |  |  |

| <b>TS87C52X2</b> -MCA      |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-MCB              | •           |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-MCC              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-MCE              |             |                |                      |                       |         |         |  |  |  |  |

| <b>TS87C52X2</b> -LCA      |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-LCB              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-LCC              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-LCE              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-VCA              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-VCB              | •           |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-VCC              | •           |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-VCE              |             |                | 0.5                  | 001 575               |         |         |  |  |  |  |

| TS87C52X2-MIA              |             |                | OB                   | SOLETE                |         |         |  |  |  |  |

| TS87C52X2-MIB              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-MIC              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-MIE              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-LIA              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-LIB              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-LIC              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-LIE              |             |                |                      |                       |         |         |  |  |  |  |

| <b>TS87C52X2</b> -VIA      |             |                |                      |                       |         |         |  |  |  |  |

| <b>TS87C52X2</b> -VIB      |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-VIC              |             |                |                      |                       |         |         |  |  |  |  |

| TS87C52X2-VIE              |             |                |                      |                       |         |         |  |  |  |  |

| AT87C52X2-3CSUM            | 8K OTP      | 5V ±10%        | Industrial & Green   | 40 MHz <sup>(1)</sup> | PDIL40  | Stick   |  |  |  |  |

### Table 37. Possible Ordering Entries (Continued)

| Part Number <sup>(3)</sup> | Memory Size | Supply Voltage | Temperature<br>Range | Max Frequency         | Package | Packing |

|----------------------------|-------------|----------------|----------------------|-----------------------|---------|---------|

| AT87C52X2-SLSUM            | 8K OTP      | 5V ±10%        | Industrial & Green   | 40 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| AT87C52X2-RLTUM            | 8K OTP      | 5V ±10%        | Industrial & Green   | 40 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| AT87C52X2-3CSUL            | 8K OTP      | 2.7 to 5.5V    | Industrial & Green   | 30 MHz <sup>(1)</sup> | PDIL40  | Stick   |

| AT87C52X2-SLSUL            | 8K OTP      | 2.7 to 5.5V    | Industrial & Green   | 30 MHz <sup>(1)</sup> | PLCC44  | Stick   |

| AT87C52X2-RLTUL            | 8K OTP      | 2.7 to 5.5V    | Industrial & Green   | 30 MHz <sup>(1)</sup> | VQFP44  | Tray    |

| AT87C52X2-3CSUV            | 8K OTP      | 5V ±10%        | Industrial & Green   | 60 MHz <sup>(3)</sup> | PDIL40  | Stick   |

| AT87C52X2-SLSUV            | 8K OTP      | 5V ±10%        | Industrial & Green   | 60 MHz <sup>(3)</sup> | PLCC44  | Stick   |

| AT87C52X2-RLTUV            | 8K OTP      | 5V ±10%        | Industrial & Green   | 60 MHz <sup>(3)</sup> | VQFP44  | Tray    |

Notes: 1. 20 MHz in X2 Mode.

2. Tape and Reel available for SL, PQFP and RL packages

3. 30 MHz in X2 Mode.