Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                             |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 48MHz                                                                              |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 48                                                                                 |

| Program Memory Size        | 200KB (200K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                        |

| Data Converters            | A/D 12x12b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-VFQFN Exposed Pad                                                               |

| Supplier Device Package    | PG-VQFN-64-6                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc1402q064x0200aaxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Features

#### **CPU** subsystem

- 32-bit ARM Cortex-M0 CPU Core

- 0.84 DMIPS/MHz (Dhrystone 2.1) at 48 MHz

- Nested Vectored Interrupt Controller

- 64 interrupt nodes

- MATH coprocessor

- 24-bit trigonometric calculation (CORDIC)

- 32-bit divide operation

- 2x4 channels ERU for event interconnections

#### **On-Chip Memories**

- 8 Kbyte ROM

- 16 Kbyte SRAM (with parity)

- up to 200 Kbyte Flash (with ECC)

#### Supply, Reset and Clock

- 1.8 V to 5.5 V supply with power on reset and brownout detector

- On-chip clock monitor

- External crystal oscillator support (32 kHz and 4 to 20 MHz)

- Internal slow and fast oscillators without the need of PLL

#### System Control

- · Window watchdog

- Real time clock module

- Pseudo random number generator

## **Communication Peripherals**

- Four USIC channels, usable as

- UART (up to 12 Mb/s)

- single-SPI (up to 12 Mb/s)

- double-SPI (up to 2 × 12 Mb/s)

- quad-SPI (up to 4 × 12 Mb/s)

- IIC (up to 400 kb/s)

- IIS (up to 12 Mb/s)

- LIN interfaces (20kb/s)

- LEDTS in Human-Machine interface

- up to 24 touch pads

- drive up to 144 LEDs

- MultiCAN+, Full-CAN/Basic-CAN with 2 nodes, 32 message objects (up to 1 MBaud)

## Analog Frontend Peripherals

- A/D Converters (up to 12 analog inputs)

2 sample and hold stages

- fast 12-bit ADC (up to 1.1 MS/s), adjustable gain

- 0 V to 5.5 V input range

- Up to 8 channels out of range comparators

- Up to 4 fast analog comparators

- Temperature Sensor

## **Industrial Control Peripherals**

- 2x4 16-bit 96 MHz CCU4 timers for signal monitoring and PWM

- 2x4 16-bit 96 MHz CCU8 timers for complex PWM, complementary high/low side switches and multi phase control

- 2x POSIF for hall and quadrature encoders, motor positioning

- 9 channel BCCU (brightness and color control) for LED lighting applications

#### Up to 56 Input/Output Ports

- 1.8 V to 5.5 V capable

- up to 8 high current pads (50 mA sink)

#### **On-Chip Debug Support**

- 4 breakpoints, 2 watchpoints

- ARM serial wire debug, single-pin debug interfaces

#### **Programming Support**

- Single-pin bootloader

- Secure bootstrap loader SBSL (optional)

#### Packages

- TSSOP-38 (9.7 × 6.4 mm<sup>2</sup>)

- VQFN-40/48/64 (5×5/7×7/8×8 mm<sup>2</sup>)

- LQFP-64 (12 × 12 mm<sup>2</sup>)

#### Tools

• Free DAVE<sup>™</sup> toolchain with low level drivers and apps

| Derivative        | Value                                                                                   | Marking |

|-------------------|-----------------------------------------------------------------------------------------|---------|

| XMC1403-Q064X0200 | 00014093 07CF00FF 1E071FF7 00B00000<br>00000D00 00001000 00033000 10204083 <sub>H</sub> | AA      |

| XMC1404-Q048X0064 | 00014083 07FF00FF 1E071FF7 30BFF00F<br>00000D00 00001000 00011000 10204083 <sub>H</sub> | AA      |

| XMC1404-Q048X0128 | 00014083 07FF00FF 1E071FF7 30BFF00F<br>00000D00 00001000 00021000 10204083 <sub>H</sub> | AA      |

| XMC1404-Q048X0200 | 00014083 07FF00FF 1E071FF7 30BFF00F<br>00000D00 00001000 00033000 10204083 <sub>H</sub> | AA      |

| XMC1404-Q064X0064 | 00014093 07FF00FF 1E071FF7 30BFF00F<br>00000D00 00001000 00011000 10204083 <sub>H</sub> | AA      |

| XMC1404-Q064X0128 | 00014093 07FF00FF 1E071FF7 30BFF00F<br>00000D00 00001000 00021000 10204083 <sub>H</sub> | AA      |

| XMC1404-Q064X0200 | 00014093 07FF00FF 1E071FF7 30BFF00F<br>00000D00 00001000 00033000 10204083 <sub>H</sub> | AA      |

| XMC1404-F064X0064 | 000140A3 07FF00FF 1E071FF7 30BFF00F<br>00000D00 00001000 00011000 10204083 <sub>H</sub> | AA      |

| XMC1404-F064X0128 | 000140A3 07FF00FF 1E071FF7 30BFF00F<br>00000D00 00001000 00021000 10204083 <sub>H</sub> | AA      |

| XMC1404-F064X0200 | 000140A3 07FF00FF 1E071FF7 30BFF00F<br>00000D00 00001000 00033000 10204083 <sub>H</sub> | AA      |

# Table 3 XMC1400 Chip Identification Number (cont'd)

## **General Device Information**

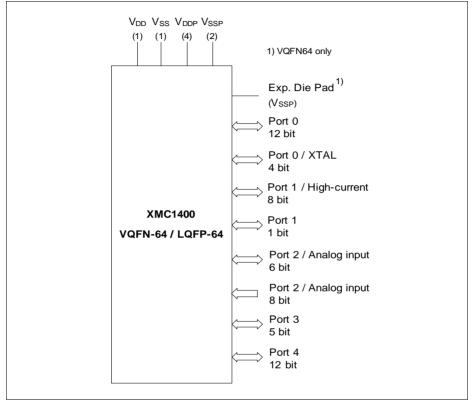

## Figure 5 XMC1400 Logic Symbol for PG-LQFP-64-26 / PG-VQFN-64-6

## **General Device Information**

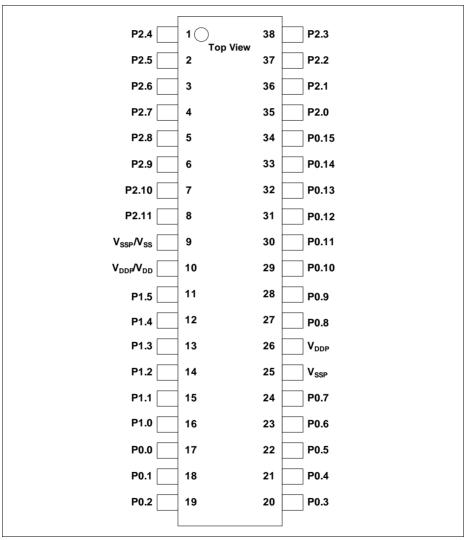

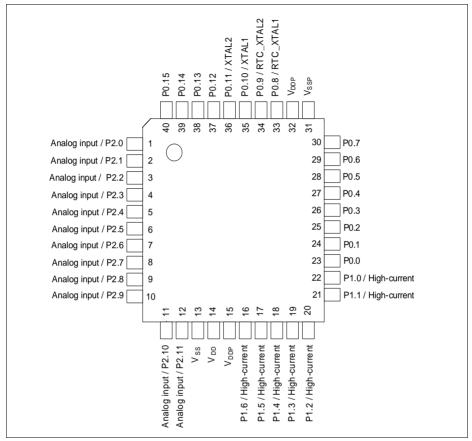

# 2.2 Pin Configuration and Definition

The following figures summarize all pins, showing their locations on the different packages.

Figure 6 XMC1400 PG-TSSOP-38-9 Pin Configuration (top view)

22

## XMC1400 AA-Step XMC1000 Family

## **General Device Information**

Figure 7 XMC1400 PG-VQFN-40-17 Pin Configuration (top view)

Table 9

Port I/O Functions (cont'd)

| ata |  |

|-----|--|

| She |  |

| eet |  |

| Function | ion Outputs |      |      |      | Inputs          |      |      |                 |      |       |                 |                 |       |                 |       |       |       |                        |       |       |       |

|----------|-------------|------|------|------|-----------------|------|------|-----------------|------|-------|-----------------|-----------------|-------|-----------------|-------|-------|-------|------------------------|-------|-------|-------|

|          | ALT1        | ALT2 | ALT3 | ALT4 | ALT5            | ALT6 | ALT7 | ALT8            | ALT9 | Input | Input           | Input           | Input | Input           | Input | Input | Input | Input                  | Input | Input | Input |

| P4.10    |             |      |      |      | CCU80.<br>OUT00 |      |      |                 |      |       |                 | CCU41.I<br>N2BA |       | CCU81.I<br>N3AB |       |       | · ·   | USIC1_<br>CH1.DX<br>5A |       |       |       |

| P4.11    |             |      |      |      | CCU80.<br>OUT01 |      |      | CCU81.<br>OUT33 |      |       | CCU40.I<br>N3AV | CCU41.I<br>N3BA |       |                 |       |       | CH0.D | USIC1_<br>CH1.DX<br>3A |       |       |       |

Infineon

# Table 10 Hardware I/O Controlled Functions

| Function | Outputs | Outputs         | Inputs | Inputs          | Pull Control | Pull Control | Pull Control | Pull Contro |

|----------|---------|-----------------|--------|-----------------|--------------|--------------|--------------|-------------|

|          | HWO0    | HWO1            | HWI0   | HWI1            | HW0_PD       | HW0_PU       | HW1_PD       | HW1_PU      |

| P1.3     |         | USIC0_CH0.DOUT3 |        | USIC0_CH0.HWIN3 | BCCU0.OUT5   | BCCU0.OUT5   |              |             |

| P1.4     |         |                 |        |                 | BCCU0.OUT6   | BCCU0.OUT6   |              |             |

| P1.5     |         |                 |        |                 | BCCU0.OUT7   | BCCU0.OUT7   |              |             |

| P1.6     |         |                 |        |                 | BCCU0.OUT8   | BCCU0.OUT8   |              |             |

| P1.7     |         |                 |        |                 |              |              |              |             |

| P1.8     |         |                 |        |                 |              |              |              |             |

| P2.0     |         |                 |        |                 | BCCU0.OUT1   | BCCU0.OUT1   |              |             |

| P2.1     |         |                 |        |                 | BCCU0.OUT6   | BCCU0.OUT6   |              |             |

| P2.2     |         |                 |        |                 | BCCU0.OUT0   | BCCU0.OUT0   | CCU40.OUT3   | CCU40.OUT3  |

| P2.3     |         |                 |        |                 | ACMP2.OUT    | ACMP2.OUT    |              |             |

| P2.4     |         |                 |        |                 | BCCU0.OUT8   | BCCU0.OUT8   |              |             |

| P2.5     |         |                 |        |                 | ACMP1.OUT    | ACMP1.OUT    |              |             |

| P2.6     |         |                 |        |                 | BCCU0.OUT2   | BCCU0.OUT2   | CCU40.OUT3   | CCU40.OUT3  |

| P2.7     |         |                 |        |                 | BCCU0.OUT8   | BCCU0.OUT8   | CCU40.OUT3   | CCU40.OUT3  |

| P2.8     |         |                 |        |                 | BCCU0.OUT1   | BCCU0.OUT1   | CCU40.OUT2   | CCU40.OUT2  |

| P2.9     |         |                 |        |                 | BCCU0.OUT7   | BCCU0.OUT7   | CCU40.OUT2   | CCU40.OUT2  |

| P2.10    |         |                 |        |                 | BCCU0.OUT4   | BCCU0.OUT4   |              |             |

| P2.11    |         |                 |        |                 | BCCU0.OUT5   | BCCU0.OUT5   |              |             |

| P2.12    |         |                 |        |                 | BCCU0.OUT3   | BCCU0.OUT3   | CCU41.OUT0   | CCU41.OUT0  |

| P2.13    |         |                 |        |                 | BCCU0.OUT4   | BCCU0.OUT4   | CCU41.OUT2   | CCU41.OUT2  |

| P3.0     |         |                 |        |                 |              |              |              |             |

| P3.1     |         | USIC1_CH0.DOUT3 |        | USIC1_CH0.HWIN3 |              |              |              |             |

| P3.2     |         | USIC1_CH0.DOUT2 |        | USIC1_CH0.HWIN2 |              |              |              |             |

| P3.3     |         | USIC1_CH0.DOUT1 |        | USIC1_CH0.HWIN1 |              |              |              |             |

| P3.4     |         | USIC1_CH0.DOUT0 |        | USIC1_CH0.HWIN0 |              |              |              |             |

| P4.0     |         |                 |        |                 |              |              |              |             |

| P4.1     |         |                 |        |                 |              |              |              |             |

| P4.2     |         |                 |        |                 |              |              |              |             |

| P4.3     |         |                 |        |                 |              |              |              |             |

XMC1400 AA-Step XMC1000 Family

Data Sheet

# Table 10 Hardware I/O Controlled Functions

| Function | Outputs              | Outputs | Inputs       | Inputs       | Pull Control                    | Pull Control                    | Pull Control | Pull Control                        |  |

|----------|----------------------|---------|--------------|--------------|---------------------------------|---------------------------------|--------------|-------------------------------------|--|

|          | HWO0                 | HWO1    | HWIO         | HWI1         | HW0_PD                          | HW0_PU                          | HW1_PD       | HW1_PU                              |  |

| P4.4     | LEDTS2.<br>EXTENDED0 |         | LEDTS2.TSIN0 | LEDTS2.TSIN0 | Reserved for LEDTS<br>Scheme A: | Reserved for LEDTS<br>Scheme A: |              | Scheme B:<br>pull-down disabled, an |  |

| P4.5     | LEDTS2.<br>EXTENDED1 |         | LEDTS2.TSIN1 | LEDTS2.TSIN1 | pull-down disabled<br>always    | pull-down enabled<br>always     | vice versa   |                                     |  |

| P4.6     | LEDTS2.<br>EXTENDED2 |         | LEDTS2.TSIN2 | LEDTS2.TSIN2 |                                 |                                 |              |                                     |  |

| P4.7     | LEDTS2.<br>EXTENDED3 |         | LEDTS2.TSIN3 | LEDTS2.TSIN3 |                                 |                                 |              |                                     |  |

| P4.8     | LEDTS2.<br>EXTENDED4 |         | LEDTS2.TSIN4 | LEDTS2.TSIN4 |                                 |                                 |              |                                     |  |

| P4.9     | LEDTS2.<br>EXTENDED5 |         | LEDTS2.TSIN5 | LEDTS2.TSIN5 |                                 |                                 |              |                                     |  |

| P4.10    | LEDTS2.<br>EXTENDED6 |         | LEDTS2.TSIN6 | LEDTS2.TSIN6 |                                 |                                 |              |                                     |  |

| P4.11    | LEDTS2.<br>EXTENDED7 |         | LEDTS2.TSIN7 | LEDTS2.TSIN7 |                                 |                                 |              |                                     |  |

Infineon

# 3.1.2 Absolute Maximum Ratings

Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

| Parameter                                                            | Symb                                   | Symbol |      | Va   | lues                                | Unit | Note /                |

|----------------------------------------------------------------------|----------------------------------------|--------|------|------|-------------------------------------|------|-----------------------|

|                                                                      |                                        |        | Min  | Тур. | Max.                                |      | Test Cond ition       |

| Junction temperature                                                 | $T_{J}$                                | SR     | -40  | -    | 115                                 | °C   | -                     |

| Storage temperature                                                  | $T_{\rm ST}$                           | SR     | -40  | -    | 125                                 | °C   | -                     |

| Voltage on power supply pin with respect to $V_{\rm SSP}$            | $V_{DDP}$                              | SR     | -0.3 | -    | 6                                   | V    | -                     |

| Voltage on digital pins with respect to $V_{\rm SSP}^{1)}$           | $V_{\rm IN}$                           | SR     | -0.5 | -    | $V_{\text{DDP}}$ + 0.5<br>or max. 6 | V    | whichever<br>is lower |

| Voltage on P2 pins with respect to $V_{\rm SSP}^{2)}$                | $V_{\rm INP2}$                         | SR     | -0.3 | -    | V <sub>DDP</sub> + 0.3              | V    | -                     |

| Voltage on analog input pins with respect to $V_{\rm SSP}$           | $V_{\mathrm{AIN}}$ $V_{\mathrm{AREF}}$ | SR     | -0.5 | -    | $V_{\text{DDP}}$ + 0.5<br>or max. 6 | V    | whichever<br>is lower |

| Input current on any pin<br>during overload condition                | I <sub>IN</sub>                        | SR     | -10  | -    | 10                                  | mA   | -                     |

| Absolute maximum sum of all input currents during overload condition | $\Sigma I_{\rm IN}$                    | SR     | -50  | -    | +50                                 | mA   | -                     |

Table 11 Absolute Maximum Rating Parameters

1) Excluding port pins P2.[1,2,6,7,8,9,11].

2) Applicable to port pins P2.[1,2,6,7,8,9,11].

| Parameter                                                   | Symbol                  |      | Values | 5    | Unit | Note /                   |  |

|-------------------------------------------------------------|-------------------------|------|--------|------|------|--------------------------|--|

|                                                             |                         | Min. | Тур.   | Max. |      | Test Condition           |  |

| Input frequency                                             | $f_{\rm OSC}{\rm SR}$   | 4    | -      | 48   | MHz  | Direct Input Mode        |  |

|                                                             |                         | 4    | -      | 20   | MHz  | External Crystal<br>Mode |  |

| Oscillator start-up time <sup>1)2)</sup>                    | t <sub>oscs</sub><br>CC | -    | -      | 10   | ms   |                          |  |

| Input voltage at XTAL1                                      | $V_{\rm IX}$ SR         | -0.3 | -      | 1.5  | V    | External Crystal<br>Mode |  |

|                                                             |                         | -0.3 | -      | 5.5  | V    | Direct Input Mode        |  |

| Input amplitude (peak-<br>to-peak) at XTAL1 <sup>2)3)</sup> | $V_{\rm PPX}{\rm SR}$   | 0.6  | _      | 1.7  | V    | External Crystal<br>Mode |  |

## Table 21 OSC\_XTAL Parameters

1)  $t_{OSCS}$  is defined from the moment the oscillator is enabled wih SCU\_ANAOSCHPCTRL.MODE until the oscillations reach an amplitude at XTAL1 of 0.9 \*  $V_{PPX}$ .

2) The external oscillator circuitry must be optimized by the customer and checked for negative resistance and amplitude as recommended and specified by crystal suppliers.

3) If the shaper unit is enabled and not bypassed.

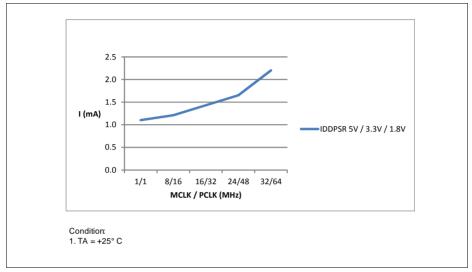

**Figure 18** shows typical graphs for sleep mode current for  $V_{DDP} = 5 \text{ V}$ ,  $V_{DDP} = 3.3 \text{ V}$ ,  $V_{DDP} = 1.8 \text{ V}$  across different clock frequencies.

Figure 18 Sleep mode, peripherals clocks disabled, Flash powered down: Supply current I<sub>DDPSD</sub> over supply voltage V<sub>DDP</sub> for different clock frequencies

**Table 24** provides the active current consumption of some modules operating at 5 V power supply at 25 °C. The typical values shown are used as a reference guide on the current consumption when these modules are enabled.

| Active Current<br>Consumption | Symbol                | Limit<br>Values | Unit | Test Condition                                                    |

|-------------------------------|-----------------------|-----------------|------|-------------------------------------------------------------------|

|                               |                       | Тур.            |      |                                                                   |

| Baseload current              | I <sub>CPUDDC</sub>   | 4.14            | mA   | Modules including Core, SCU, PORT, memories, ANATOP <sup>1)</sup> |

| VADC and SHS                  | I <sub>ADCDDC</sub>   | 3.73            | mA   | Set CGATCLR0.VADC to 1 <sup>2)</sup>                              |

| USICx                         | I <sub>USICODDC</sub> | 1.35            | mA   | Set CGATCLR0.USIC0 to 13)                                         |

| CCU4x                         | I <sub>CCU40DDC</sub> | 0.99            | mA   | Set CGATCLR0.CCU40 to 1 <sup>4)</sup>                             |

| CCU8x                         | I <sub>CCU80DDC</sub> | 1.00            | mA   | Set CGATCLR0.CCU80 to 1 <sup>5)</sup>                             |

| POSIFx                        | I <sub>PIF0DDC</sub>  | 1.05            | mA   | Set CGATCLR0.POSIF0 to 16)                                        |

| LEDTSx                        | ILTSxDDC              | 1.14            | mA   | Set CGATCLR0.LEDTSx to 17)                                        |

| BCCU0                         | I <sub>BCCU0DDC</sub> | 0.29            | mA   | Set CGATCLR0.BCCU0 to 18)                                         |

| MATH                          | I <sub>MATHDDC</sub>  | 0.50            | mA   | Set CGATCLR0.MATH to 19)                                          |

| WDT                           | I <sub>WDTDDC</sub>   | 0.03            | mA   | Set CGATCLR0.WDT to 1 <sup>10)</sup>                              |

| RTC                           | I <sub>RTCDDC</sub>   | 0.01            | mA   | Set CGATCLR0.RTC to 1 <sup>11)</sup>                              |

| MultiCAN                      | I <sub>MCANDDC</sub>  | 1.38            | mA   | Set CGATCLR0.MCAN0 to 1 <sup>12)</sup>                            |

Table 24 Typical Active Current parameter table

1) Baseload current is measured with device running in user mode, MCLK=PCLK=48 MHz, with an endless loop in the flash memory. The clock to the modules stated in CGATSTAT0 are gated.

2) Active current is measured with: module enabled, MCLK=48 MHz, running in auto-scan conversion mode

- Active current is measured with: module enabled, each of the 2 USIC channels sending alternate messages at 57.6 kbaud every 200 ms

- 4) Active current is measured with: module enabled, MCLK=PCLK=48 MHz, 1 CCU4 slice for PWM switching at 20kHz with duty cycle varying at 10%-90%, 1 CCU4 slice in capture mode for reading period and duty cycle

- 5) Active current is measured with: module enabled, MCLK=PCLK=48 MHz, 3 CCU8 slices with PWM frequency at 20kHz and a period match interrupt used to toggle duty cycle between 10% and 90%

- 6) Active current is measured with: module enabled, MCLK=48 MHz, PCLK=96 MHz, hall sensor mode

- Active current is measured with: module enabled, MCLK=48 MHz, 1 LED column, 6 LED/TS lines, Pad Scheme A with large pad hysteresis config, time slice duration = 1.048 ms

- Active current is measured with: module enabled, MCLK=48 MHz, PCLK=96MHz, FCLK=0.8 MHz, Normal mode (BCCU clock = FCLK/4), 4 BCCU Channels with packers enabled and 1 Dimming Engine, change color or dim every 1s

- Active current is measured with: module enabled, MCLK=48 MHz, PCLK=96 MHz, tangent calculation in while loop; CORDIC circular rotation, no keep, autostart; 32-by-32 bit signed DIV, autostart, DVS right shift by 11

66

# 3.3.2 **Power-Up and Supply Threshold Characteristics**

Table 26 provides the characteristics of the supply threshold in XMC1400.

The guard band between the lowest valid operating voltage and the brownout reset threshold provides a margin for noise immunity and hysteresis. The electrical parameters may be violated while  $V_{\text{DDP}}$  is outside its operating range.

The brownout detection triggers a reset within the defined range. The prewarning detection can be used to trigger an early warning and issue corrective and/or fail-safe actions in case of a critical supply voltage drop.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                           | Symbol                                 | V                                                                | /alues |                 | Unit | Note /                                                                      |

|-------------------------------------|----------------------------------------|------------------------------------------------------------------|--------|-----------------|------|-----------------------------------------------------------------------------|

|                                     |                                        | Min.                                                             | Тур.   | Max.            |      | Test Condition                                                              |

| $V_{\rm DDP}$ ramp-up time          | t <sub>RAMPUP</sub> SR                 | $\begin{array}{c} V_{\rm DDP} / \\ S_{\rm VDDPrise} \end{array}$ | -      | 10 <sup>7</sup> | μS   |                                                                             |

| $V_{\rm DDP}$ slew rate             | $S_{\text{VDDPOP}}$ SR                 | 0                                                                | -      | 0.1             | V/µs | Slope during<br>normal operation                                            |

|                                     | $S_{\rm VDDP10}~{ m SR}$               | 0                                                                | -      | 10              | V/µs | Slope during fast<br>transient within +/-<br>10% of V <sub>DDP</sub>        |

|                                     | $S_{\rm VDDPrise}~{ m SR}$             | 0                                                                | -      | 10              | V/µs | Slope during<br>power-on or<br>restart after<br>brownout event              |

|                                     | S <sub>VDDPfall</sub> <sup>1)</sup> SR | 0                                                                | -      | 0.25            | V/µs | Slope during<br>supply falling out<br>of the +/-10%<br>limits <sup>2)</sup> |

| V <sub>DDP</sub> prewarning voltage | V <sub>DDPPW</sub> CC                  | 2.1                                                              | 2.25   | 2.4             | V    | ANAVDEL.VDEL_<br>SELECT = 00 <sub>B</sub>                                   |

|                                     |                                        | 2.85                                                             | 3      | 3.15            | V    | ANAVDEL.VDEL_<br>SELECT = 01 <sub>B</sub>                                   |

|                                     |                                        | 4.2                                                              | 4.4    | 4.6             | V    | ANAVDEL.VDEL_<br>SELECT = 10 <sub>B</sub>                                   |

# Table 26 Power-Up and Supply Threshold Parameters (Operating Conditions apply)

# 3.3.5 SPD Timing Requirements

The optimum SPD decision time between  $0_B$  and  $1_B$  is 0.75 µs. With this value the system has maximum robustness against frequency deviations of the sampling clock on tool and on device side. However it is not always possible to exactly match this value with the given constraints for the sample clock. For instance for a oversampling rate of 4, the sample clock will be 8 MHz and in this case the closest possible effective decision time is 5.5 clock cycles (0.69 µs).

| Sample<br>Freq. | Sampling<br>Factor | •      | Sample<br>Clocks 1 <sub>B</sub> | Effective<br>Decision<br>Time <sup>1)</sup> | Remark                                                                                    |  |  |  |  |  |  |  |

|-----------------|--------------------|--------|---------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 8 MHz           | 4                  | 1 to 5 | 6 to 12                         | 0.69 µs                                     | The other closest option $(0.81 \ \mu s)$ for the effective decision time is less robust. |  |  |  |  |  |  |  |

| Table 30 | Optimum | Number | of Sample | Clocks for SPD |

|----------|---------|--------|-----------|----------------|

|          | opunium | Number | or oumpic |                |

1) Nominal sample frequency period multiplied with  $0.5 + (max. number of 0_B sample clocks)$

For a balanced distribution of the timing robustness of SPD between tool and device, the timing requirements for the tool are:

- Frequency deviation of the sample clock is +/- 5%

- Effective decision time is between 0.69 µs and 0.75 µs (calculated with nominal sample frequency)

# 3.3.6 Peripheral Timings

# 3.3.6.1 Synchronous Serial Interface (USIC SSC) Timing

The following parameters are applicable for a USIC channel operated in SSC mode. *Note: Operating Conditions apply.*

| Parameter                                                               | Symbol              | Va                       | lues |      | Unit | Note /<br>Test Condition |

|-------------------------------------------------------------------------|---------------------|--------------------------|------|------|------|--------------------------|

|                                                                         |                     | Min.                     | Тур. | Max. |      |                          |

| SCLKOUT master clock period                                             | t <sub>CLK</sub> CC | 4/MCLK                   | -    | -    | ns   |                          |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC   | t <sub>CLK</sub> /2 - 28 | -    | -    | ns   |                          |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC   | 0                        | -    | -    | ns   |                          |

| Data output DOUT[3:0] valid time                                        | t <sub>3</sub> CC   | -28                      | -    | 28   | ns   |                          |

| Receive data input<br>DX0/DX[5:3] setup time to<br>SCLKOUT receive edge | t <sub>4</sub> SR   | 75                       | -    | -    | ns   |                          |

| Data input DX0/DX[5:3]<br>hold time from SCLKOUT<br>receive edge        | t <sub>5</sub> SR   | 0                        | -    | -    | ns   |                          |

## Table 31 USIC SSC Master Mode Timing

## Table 32 USIC SSC Slave Mode Timing

| Parameter                                                                   | Symbol                    | Va     | lues |      | Unit | Note /             |

|-----------------------------------------------------------------------------|---------------------------|--------|------|------|------|--------------------|

|                                                                             |                           | Min.   | Тур. | Max. |      | Test Conditio<br>n |

| DX1 slave clock period                                                      | t <sub>CLK</sub> SR       | 4/MCLK | -    | _    | ns   |                    |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup> | <i>t</i> <sub>10</sub> SR | 16     | -    | _    | ns   |                    |

76

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Table 32 | <b>USIC SSC Slave Mode Timin</b> | na |

|----------|----------------------------------|----|

|          |                                  |    |

| Parameter                                                                                 | Symbol                |      | Values |      | Unit | Note /<br>Test Conditio<br>n |

|-------------------------------------------------------------------------------------------|-----------------------|------|--------|------|------|------------------------------|

|                                                                                           |                       | Min. | Тур.   | Max. |      |                              |

| Select input DX2 hold after<br>last clock input DX1 receive<br>edge <sup>1)</sup>         | <sup>t</sup> 11<br>SR | 17   | -      | -    | ns   |                              |

| Receive data input<br>DX0/DX[5:3] setup time to<br>shift clock receive edge <sup>1)</sup> | <sup>t</sup> 12<br>SR | 21   | -      | -    | ns   |                              |

| Data input DX0/DX[5:3] hold<br>time from clock input DX1<br>receive edge <sup>1)</sup>    | <sup>t</sup> 13<br>SR | 15   | -      | -    | ns   |                              |

| Data output DOUT[3:0] valid time                                                          | t <sub>14</sub><br>CC | -    | -      | 71   | ns   |                              |

1) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

# 3.3.6.2 Inter-IC (IIC) Interface Timing

The following parameters are applicable for a USIC channel operated in IIC mode. *Note: Operating Conditions apply.*

| Table 33 | USIC IIC | Standard | Mode | Timing <sup>1)</sup> |

|----------|----------|----------|------|----------------------|

|----------|----------|----------|------|----------------------|

| Parameter                                              | Symbol                   |      | Values | 5    | Unit | Note /<br>Test Condition |

|--------------------------------------------------------|--------------------------|------|--------|------|------|--------------------------|

|                                                        |                          | Min. | Тур.   | Max. |      |                          |

| Fall time of both SDA and SCL                          | t <sub>1</sub><br>CC/SR  | -    | -      | 300  | ns   |                          |

| Rise time of both SDA and SCL                          | t <sub>2</sub><br>CC/SR  | -    | -      | 1000 | ns   |                          |

| Data hold time                                         | t <sub>3</sub><br>CC/SR  | 0    | -      | -    | μs   |                          |

| Data set-up time                                       | t <sub>4</sub><br>CC/SR  | 250  | -      | -    | ns   |                          |

| LOW period of SCL clock                                | t <sub>5</sub><br>CC/SR  | 4.7  | -      | -    | μs   |                          |

| HIGH period of SCL clock                               | t <sub>6</sub><br>CC/SR  | 4.0  | -      | -    | μs   |                          |

| Hold time for (repeated)<br>START condition            | t <sub>7</sub><br>CC/SR  | 4.0  | -      | -    | μs   |                          |

| Set-up time for repeated START condition               | t <sub>8</sub><br>CC/SR  | 4.7  | -      | -    | μs   |                          |

| Set-up time for STOP condition                         | t <sub>9</sub><br>CC/SR  | 4.0  | -      | -    | μs   |                          |

| Bus free time between a<br>STOP and START<br>condition | t <sub>10</sub><br>CC/SR | 4.7  | -      | -    | μs   |                          |

| Capacitive load for each bus line                      | $C_{\sf b}{\sf SR}$      | -    | -      | 400  | pF   |                          |

Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

# Table 34 USIC IIC Fast Mode Timing<sup>1)</sup>

| Parameter                                              | Symbol                   |                            | Values |      | Unit | Note /<br>Test Condition |

|--------------------------------------------------------|--------------------------|----------------------------|--------|------|------|--------------------------|

|                                                        |                          | Min.                       | Тур.   | Max. |      |                          |

| Fall time of both SDA and SCL                          | t <sub>1</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -      | 300  | ns   |                          |

| Rise time of both SDA and SCL                          | t <sub>2</sub><br>CC/SR  | 20 +<br>0.1*C <sub>b</sub> | -      | 300  | ns   |                          |

| Data hold time                                         | t <sub>3</sub><br>CC/SR  | 0                          | -      | -    | μs   |                          |

| Data set-up time                                       | t <sub>4</sub><br>CC/SR  | 100                        | -      | -    | ns   |                          |

| LOW period of SCL clock                                | t <sub>5</sub><br>CC/SR  | 1.3                        | -      | -    | μs   |                          |

| HIGH period of SCL clock                               | t <sub>6</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Hold time for (repeated)<br>START condition            | t <sub>7</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Set-up time for repeated START condition               | t <sub>8</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Set-up time for STOP condition                         | t <sub>9</sub><br>CC/SR  | 0.6                        | -      | -    | μs   |                          |

| Bus free time between a<br>STOP and START<br>condition | t <sub>10</sub><br>CC/SR | 1.3                        | -      | -    | μs   |                          |

| Capacitive load for each bus line                      | $C_{\rm b}{\rm SR}$      | -                          | -      | 400  | pF   |                          |

1) Due to the wired-AND configuration of an IIC bus system, the port drivers of the SCL and SDA signal lines need to operate in open-drain mode. The high level on these lines must be held by an external pull-up device, approximately 10 kOhm for operation at 100 kbit/s, approximately 2 kOhm for operation at 400 kbit/s.

2) C<sub>b</sub> refers to the total capacitance of one bus line in pF.

## Package and Reliability

The difference between junction temperature and ambient temperature is determined by  $\Delta T = (P_{INT} + P_{IOSTAT} + P_{IODYN}) \times R_{\Theta JA}$

The internal power consumption is defined as

$P_{\text{INT}} = V_{\text{DDP}} \times I_{\text{DDP}}$  (switching current and leakage current).

The static external power consumption caused by the output drivers is defined as  $P_{\text{IOSTAT}} = \Sigma((V_{\text{DDP}}-V_{\text{OH}}) \times I_{\text{OH}}) + \Sigma(V_{\text{OI}} \times I_{\text{OI}})$

The dynamic external power consumption caused by the output drivers ( $P_{IODYN}$ ) depends on the capacitive load connected to the respective pins and their switching frequencies.

If the total power dissipation for a given system configuration exceeds the defined limit, countermeasures must be taken to ensure proper system operation:

- Reduce  $V_{\text{DDP}}$ , if possible in the system

- Reduce the system frequency

- Reduce the number of output pins

- Reduce the load on active output drivers

www.infineon.com

Published by Infineon Technologies AG