Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                             |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 48MHz                                                                              |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, I <sup>2</sup> S, LED, POR, PWM, WDT                       |

| Number of I/O              | 48                                                                                 |

| Program Memory Size        | 64KB (64K × 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 16К х 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                        |

| Data Converters            | A/D 12x12b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 64-VFQFN Exposed Pad                                                               |

| Supplier Device Package    | PG-VQFN-64-6                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xmc1404q064x0064aaxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup>, XMC<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

ARM<sup>®</sup>, ARM Powered<sup>®</sup>, Cortex<sup>®</sup>, Thumb<sup>®</sup> and AMBA<sup>®</sup> are registered trademarks of ARM, Limited.

CoreSight<sup>™</sup>, ETM<sup>™</sup>, Embedded Trace Macrocell<sup>™</sup> and Embedded Trace Buffer<sup>™</sup> are trademarks of ARM, Limited.

#### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

#### Features

#### **CPU** subsystem

- 32-bit ARM Cortex-M0 CPU Core

- 0.84 DMIPS/MHz (Dhrystone 2.1) at 48 MHz

- Nested Vectored Interrupt Controller

- 64 interrupt nodes

- MATH coprocessor

- 24-bit trigonometric calculation (CORDIC)

- 32-bit divide operation

- 2x4 channels ERU for event interconnections

#### **On-Chip Memories**

- 8 Kbyte ROM

- 16 Kbyte SRAM (with parity)

- up to 200 Kbyte Flash (with ECC)

#### Supply, Reset and Clock

- 1.8 V to 5.5 V supply with power on reset and brownout detector

- On-chip clock monitor

- External crystal oscillator support (32 kHz and 4 to 20 MHz)

- Internal slow and fast oscillators without the need of PLL

#### System Control

- · Window watchdog

- Real time clock module

- Pseudo random number generator

#### **Communication Peripherals**

- Four USIC channels, usable as

- UART (up to 12 Mb/s)

- single-SPI (up to 12 Mb/s)

- double-SPI (up to 2 × 12 Mb/s)

- quad-SPI (up to 4 × 12 Mb/s)

- IIC (up to 400 kb/s)

- IIS (up to 12 Mb/s)

- LIN interfaces (20kb/s)

- LEDTS in Human-Machine interface

- up to 24 touch pads

- drive up to 144 LEDs

- MultiCAN+, Full-CAN/Basic-CAN with 2 nodes, 32 message objects (up to 1 MBaud)

#### Analog Frontend Peripherals

- A/D Converters (up to 12 analog inputs)

2 sample and hold stages

- fast 12-bit ADC (up to 1.1 MS/s), adjustable gain

- 0 V to 5.5 V input range

- Up to 8 channels out of range comparators

- Up to 4 fast analog comparators

- Temperature Sensor

#### **Industrial Control Peripherals**

- 2x4 16-bit 96 MHz CCU4 timers for signal monitoring and PWM

- 2x4 16-bit 96 MHz CCU8 timers for complex PWM, complementary high/low side switches and multi phase control

- 2x POSIF for hall and quadrature encoders, motor positioning

- 9 channel BCCU (brightness and color control) for LED lighting applications

#### Up to 56 Input/Output Ports

- 1.8 V to 5.5 V capable

- up to 8 high current pads (50 mA sink)

#### **On-Chip Debug Support**

- 4 breakpoints, 2 watchpoints

- ARM serial wire debug, single-pin debug interfaces

#### **Programming Support**

- Single-pin bootloader

- Secure bootstrap loader SBSL (optional)

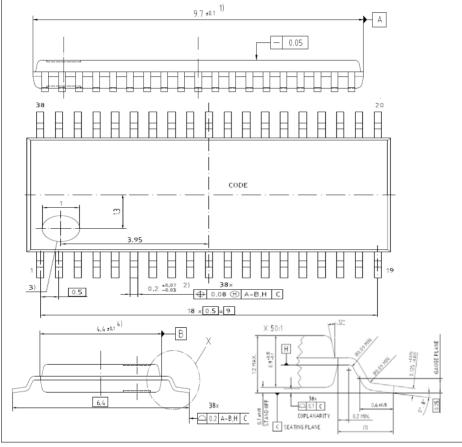

#### Packages

- TSSOP-38 (9.7 × 6.4 mm<sup>2</sup>)

- VQFN-40/48/64 (5×5/7×7/8×8 mm<sup>2</sup>)

- LQFP-64 (12 × 12 mm<sup>2</sup>)

#### Tools

• Free DAVE<sup>™</sup> toolchain with low level drivers and apps

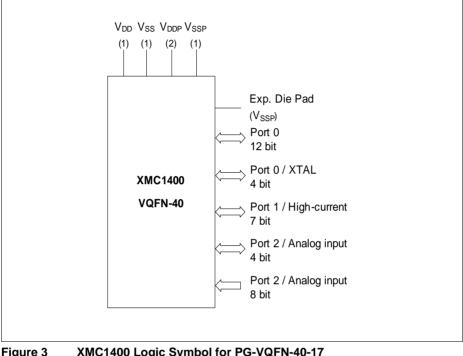

Figure 3 XMC1400 Logic Symbol for PG-VQFN-40-17

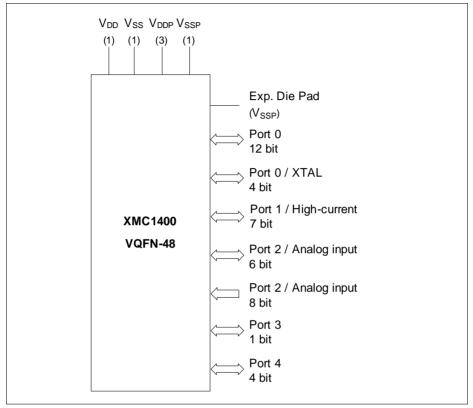

Figure 4 XMC1400 Logic Symbol for PG-VQFN-48-73

## 2.2.1 Package Pin Summary

The following general building block is used to describe each pin:

#### Table 4 Package Pin Mapping Description

| Function | Package A | Package B | <br>Pad Type |

|----------|-----------|-----------|--------------|

| Px.y     | Ν         | Ν         | Pad Class    |

The table is sorted by the "Function" column, starting with the regular Port pins (Px.y), followed by the supply pins.

The following columns, titled with the supported package variants, lists the package pin number to which the respective function is mapped in that package.

The "Pad Type" indicates the employed pad type:

- STD\_INOUT (standard bi-directional pads)

- STD\_INOUT/AN (standard bi-directional pads with analog input)

- STD\_INOUT/clock (standard bi-directional pads with oscillator function)

- High Current (high current bi-directional pads)

- STD\_IN/AN (standard input pads with analog input)

- Power (power supply)

Details about the pad properties are defined in the Electrical Parameter chapter.

| Function               | LQFP<br>64,<br>VQFN<br>64 | VQFN<br>48 | VQFN<br>40 | TSSOP<br>38 | Pad Type               | Notes |

|------------------------|---------------------------|------------|------------|-------------|------------------------|-------|

| P0.0                   | 41                        | 29         | 23         | 17          | STD_INOUT              |       |

| P0.1                   | 42                        | 30         | 24         | 18          | STD_INOUT              |       |

| P0.2                   | 43                        | 31         | 25         | 19          | STD_INOUT              |       |

| P0.3                   | 44                        | 32         | 26         | 20          | STD_INOUT              |       |

| P0.4                   | 45                        | 33         | 27         | 21          | STD_INOUT              |       |

| P0.5                   | 46                        | 34         | 28         | 22          | STD_INOUT              |       |

| P0.6                   | 47                        | 35         | 29         | 23          | STD_INOUT              |       |

| P0.7                   | 48                        | 36         | 30         | 24          | STD_INOUT              |       |

| P0.8/<br>RTC_<br>XTAL1 | 51                        | 39         | 33         | 27          | STD_INOUT<br>/clock_IN |       |

#### Table 5Package Pin Mapping

#### **General Device Information**

| Table 5  | Packa                                  | ge Pin Ma   | apping (c   | ont'd)      |          |                                                                                                                                                                                                                        |

|----------|----------------------------------------|-------------|-------------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function | LQFP<br>64,<br>VQFN<br>64              | VQFN<br>48  | VQFN<br>40  | TSSOP<br>38 | Pad Type | Notes                                                                                                                                                                                                                  |

| VDD      | 24                                     | 18          | 14          | 10          | Power    | Supply VDD, ADC<br>reference voltage/<br>ORC reference<br>voltage                                                                                                                                                      |

| VDDP     | 25                                     | 19          | 15          | 10          | Power    | When VDD is<br>supplied, VDDP<br>has to be supplied<br>with the same<br>voltage.                                                                                                                                       |

| VDDP     | 2                                      | -           | -           | -           | Power    | I/O port supply                                                                                                                                                                                                        |

| VDDP     | 35                                     | 27          | -           | -           | Power    | I/O port supply                                                                                                                                                                                                        |

| VDDP     | 50                                     | 38          | 32          | 26          | Power    | I/O port supply                                                                                                                                                                                                        |

| VSSP     | 1                                      | -           | -           | -           | Power    | I/O port ground                                                                                                                                                                                                        |

| VSSP     | 49                                     | 37          | 31          | 25          | Power    | I/O port ground                                                                                                                                                                                                        |

| VSSP     | Exp.<br>Pad<br>(in<br>VQFN<br>64 only) | Exp.<br>Pad | Exp.<br>Pad | -           | Power    | Exposed Die PadThe exposed diepad is connectedinternally to VSSP.For properoperation, it ismandatory toconnect theexposed pad tothe board ground.For thermalaspects, pleaserefer to thePackage andReliability chapter. |

## 2.2.2 Port Pin for Boot Modes

Port functions can be overruled by the boot mode selected. The type of boot mode is selected via BMI. Table 6 shows the port pins used for the various boot modes.

| Pin   | Boot      | Boot Description                       |  |  |  |  |  |  |

|-------|-----------|----------------------------------------|--|--|--|--|--|--|

| P0.13 | CS(O)     | SSC BSL mode                           |  |  |  |  |  |  |

| P0.14 | SWDIO_0   | Debug mode (SWD)                       |  |  |  |  |  |  |

|       | SPD_0     | Debug mode (SPD)                       |  |  |  |  |  |  |

|       | RX/TX     | ASC BSL half-duplex mode               |  |  |  |  |  |  |

|       | RX        | ASC BSL full-duplex mode               |  |  |  |  |  |  |

|       | RX        | CAN BSL mode                           |  |  |  |  |  |  |

|       | SCLK(O)   | SSC BSL mode                           |  |  |  |  |  |  |

| P0.15 | SWDCLK_0  | Debug mode (SWD)                       |  |  |  |  |  |  |

|       | ТХ        | ASC BSL full-duplex mode               |  |  |  |  |  |  |

|       | TX        | CAN BSL mode                           |  |  |  |  |  |  |

|       | DATA(I/O) | SSC BSL mode                           |  |  |  |  |  |  |

| P1.2  | SWDCLK_1  | Debug mode (SWD)                       |  |  |  |  |  |  |

|       | ТХ        | ASC BSL full-duplex mode               |  |  |  |  |  |  |

|       | TX        | CAN BSL mode                           |  |  |  |  |  |  |

| P1.3  | SWDIO_1   | Debug mode (SWD)                       |  |  |  |  |  |  |

|       | SPD_1     | Debug mode (SPD)                       |  |  |  |  |  |  |

|       | RX/TX     | ASC BSL half-duplex mode               |  |  |  |  |  |  |

|       | RX        | ASC BSL full-duplex mode               |  |  |  |  |  |  |

|       | RX        | CAN BSL mode                           |  |  |  |  |  |  |

| P4.6  | HWCON0    | Boot Pins                              |  |  |  |  |  |  |

| P4.7  | HWCON1    | (Boot from pins mode must be selected) |  |  |  |  |  |  |

Table 6

Port Pin for Boot Modes

| Table 9 | Port I/O Functions (cont'd) |

|---------|-----------------------------|

|         |                             |

| Table    | 9 |                | Port                    | l/O Fur                   | nctions                   | s (con          | ťd)                       |                         |                 |                |                       |                 |                 |                 |                        |                        |                        |                        |                        |                        |                 |             |

|----------|---|----------------|-------------------------|---------------------------|---------------------------|-----------------|---------------------------|-------------------------|-----------------|----------------|-----------------------|-----------------|-----------------|-----------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|-----------------|-------------|

| Function | n |                |                         |                           |                           | Outputs         |                           |                         |                 |                | Inputs                |                 |                 |                 |                        |                        |                        |                        |                        |                        |                 |             |

|          | A | LT1            | ALT2                    | ALT3                      | ALT4                      | ALT5            | ALT6                      | ALT7                    | ALT8            | ALT9           | Input                 | Input           | Input           | Input           | Input                  | Input                  | Input                  | Input                  | Input                  | Input                  | Input           | Input       |

| P2.2     |   |                |                         |                           |                           |                 |                           |                         |                 |                | ACMP2.I<br>NN         | VADC0.<br>G0CH7 |                 | ORC0.AI<br>N    | USIC1_<br>CH0.DX<br>5E |                        | USIC0_<br>CH0.DX<br>3A | USIC0_<br>CH0.D<br>X4A | USIC0_<br>CH1.DX<br>5A |                        |                 | ERU0.<br>B1 |

| P2.3     |   |                |                         |                           |                           |                 |                           |                         |                 |                |                       |                 | VADC0.<br>G1CH5 | ORC1.AI<br>N    | USIC1_<br>CH0.DX<br>3E | USIC1_<br>CH0.DX<br>4E | USIC1_<br>CH1.DX<br>5C | USIC0_<br>CH0.D<br>X5B | USIC0_<br>CH1.DX<br>3C | USIC0_<br>CH1.DX<br>4C |                 | ERU0.<br>B1 |

| P2.4     |   |                |                         |                           |                           |                 |                           |                         |                 |                |                       |                 | VADC0.<br>G1CH6 | ORC2.AI<br>N    | USIC1_<br>CH1.DX<br>3C | USIC1_<br>CH1.DX<br>4C | USIC0_<br>CH0.DX<br>3B | USIC0_<br>CH0.D<br>X4B | USIC1_<br>CH0.DX<br>5F | USIC0_<br>CH1.DX<br>5B |                 | ERU0<br>A1  |

| P2.5     |   |                |                         |                           |                           |                 |                           |                         |                 |                |                       |                 | VADC0.<br>G1CH7 |                 | USIC1_<br>CH1.DX<br>5D |                        | USIC0_<br>CH0.DX<br>5D |                        | USIC0_<br>CH1.DX<br>3E | USIC0_<br>CH1.DX<br>4E |                 | ERU0.<br>A1 |

| P2.6     |   |                |                         |                           |                           |                 |                           |                         |                 |                | ACMP1.I<br>NN         | VADC0.<br>G0CH0 |                 | ORC4.AI<br>N    | USIC1_<br>CH1.DX<br>3E | USIC1_<br>CH1.DX<br>4E | USIC0_<br>CH0.DX<br>3E | USIC0_<br>CH0.D<br>X4E | USIC0_<br>CH1.DX<br>5D |                        |                 | ERU0<br>A1  |

| P2.7     |   |                |                         |                           |                           |                 |                           |                         |                 |                | ACMP1.I<br>NP         |                 | VADC0.<br>G1CH1 |                 | USIC1_<br>CH1.DX<br>5E |                        | USIC0_<br>CH0.DX<br>5C |                        | USIC0_<br>CH1.DX<br>3D | USIC0_<br>CH1.DX<br>4D |                 | ERU0.<br>A1 |

| P2.8     |   |                |                         |                           |                           |                 |                           |                         |                 |                | ACMP0.I<br>NN         | VADC0.<br>G0CH1 | VADC0.<br>G1CH0 | ORC6.AI<br>N    |                        |                        | USIC0_<br>CH0.DX<br>3D | USIC0_<br>CH0.D<br>X4D | USIC0_<br>CH1.DX<br>5C |                        |                 | ERU0<br>B1  |

| P2.9     |   |                |                         |                           |                           |                 |                           |                         |                 |                | ACMP0.I<br>NP         |                 | VADC0.<br>G1CH4 | ORC7.AI<br>N    |                        |                        | USIC0_<br>CH0.DX<br>5A |                        | USIC0_<br>CH1.DX<br>3B | USIC0_<br>CH1.DX<br>4B |                 | ERU0.<br>B0 |

| P2.10    |   |                | CCU40.<br>OUT2          | ERU0.G<br>OUT1            | LEDTS1<br>.COL4           | CCU80.<br>OUT30 | ACMP0.<br>OUT             | USIC0_<br>CH1.DO<br>UT0 |                 | CAN.N1<br>_TXD |                       | VADC0.<br>G0CH3 | VADC0.<br>G1CH2 |                 |                        |                        | USIC0_<br>CH0.DX<br>3C | USIC0_<br>CH0.D<br>X4C | USIC0_<br>CH1.DX<br>0F |                        | CAN.N1<br>_RXDE | ERU0<br>B0  |

| P2.11    |   |                | CCU40.<br>OUT3          | ERU0.G<br>OUT0            | LEDTS1<br>.COL3           | CCU80.<br>OUT31 | USIC0_<br>CH1.SC<br>LKOUT | USIC0_<br>CH1.DO<br>UT0 |                 | CAN.N1<br>_TXD | ACMP.R<br>EF          | VADC0.<br>G0CH4 | VADC0.<br>G1CH3 |                 |                        |                        |                        |                        | USIC0_<br>CH1.DX<br>0E | USIC0_<br>CH1.DX<br>1E | CAN.N1<br>_RXDF | ERU0<br>B1  |

| P2.12    |   | SCCU0.<br>DUT3 | VADC0.<br>EMUX00        | USIC1_<br>CH0.SC<br>LKOUT | USIC1_<br>CH1.SC<br>LKOUT |                 | ACMP2.<br>OUT             | USIC1_<br>CH1.DO<br>UT0 | LEDTS2<br>.COL6 |                | ACMP3.I<br>NN         |                 |                 |                 |                        |                        | USIC1_<br>CH0.DX<br>3A | USIC1_<br>CH0.D<br>X4A | USIC1_<br>CH1.DX<br>0C | USIC1_<br>CH1.DX<br>1B |                 | ERU1<br>A2  |

| P2.13    |   |                | CCU40.<br>OUT3          | USIC1_<br>CH0.MC<br>LKOUT | CCU81.<br>OUT31           |                 | VADC0.<br>EMUX01          | USIC1_<br>CH1.DO<br>UT0 | CCU81.<br>OUT33 | CCU41.<br>OUT3 | ACMP3.I<br>NP         |                 |                 |                 |                        |                        | USIC1_<br>CH0.DX<br>5A |                        | USIC1_<br>CH1.DX<br>0D |                        |                 | ERU1<br>A3  |

| P3.0     |   | SCCU0.<br>DUTO | USIC1_<br>CH1.DO<br>UT0 | USIC1_<br>CH1.SC<br>LKOUT | LEDTS2<br>.COLA           | CCU80.<br>OUT21 | ACMP1.<br>OUT             | USIC1_<br>CH0.SE<br>LO1 | CCU81.<br>OUT21 | CCU41.<br>OUT0 | BCCU0.<br>TRAPIN<br>C |                 | CCU41.I<br>N1AA | CCU41.I<br>N2AA | CCU41.I<br>N3AA        | CCU81.I<br>N0AA        | CCU81.I<br>N1AA        | CCU81.<br>IN2AA        | USIC1_<br>CH1.DX<br>0E | USIC1_<br>CH1.DX<br>1D | CCU81.I<br>N3AA | ERU1<br>A1  |

| P3.1     |   |                | USIC1_<br>CH1.DO<br>UT0 |                           | LEDTS2<br>.COL0           | CCU80.<br>OUT20 | ACMP3.<br>OUT             | USIC1_<br>CH0.SE<br>LO0 | CCU81.<br>OUT20 | CCU41.<br>OUT1 |                       |                 |                 |                 |                        |                        |                        | USIC1_<br>CH0.D<br>X2F | USIC1_<br>CH1.DX<br>0F |                        |                 | ERU1<br>A1  |

Infineon

XMC1400 AA-Step XMC1000 Family

V1.3, 2016-10 Subject to Agreement on the Use of Product Information

| Function | Outputs              | Outputs         | Inputs       | Inputs          | Pull Control                    | Pull Control                    | Pull Control        | Pull Control                                                              |  |  |

|----------|----------------------|-----------------|--------------|-----------------|---------------------------------|---------------------------------|---------------------|---------------------------------------------------------------------------|--|--|

|          | HWO0                 | HWO1            | HWIO         | HWI1            | HW0_PD                          | HW0_PU                          | HW1_PD              | HW1_PU                                                                    |  |  |

| P0.0     | LEDTS0.<br>EXTENDED7 |                 | LEDTS0.TSIN7 | LEDTS0.TSIN7    | Reserved for LEDTS<br>Scheme A: | Reserved for LEDTS<br>Scheme A: | pull-up enabled and | eserved for LEDTS Scheme B:<br>ull-up enabled and pull-down disabled, and |  |  |

| P0.1     | LEDTS0.<br>EXTENDED6 |                 | LEDTS0.TSIN6 | LEDTS0.TSIN6    | pull-down disabled<br>always    | pull-down enabled<br>always     | vice versa          |                                                                           |  |  |

| P0.2     | LEDTS0.<br>EXTENDED5 |                 | LEDTS0.TSIN5 | LEDTS0.TSIN5    |                                 |                                 |                     |                                                                           |  |  |

| P0.3     | LEDTS0.<br>EXTENDED4 |                 | LEDTS0.TSIN4 | LEDTS0.TSIN4    |                                 |                                 |                     |                                                                           |  |  |

| P0.4     | LEDTS0.<br>EXTENDED3 |                 | LEDTS0.TSIN3 | LEDTS0.TSIN3    |                                 |                                 |                     |                                                                           |  |  |

| P0.5     | LEDTS0.<br>EXTENDED2 |                 | LEDTS0.TSIN2 | LEDTS0.TSIN2    |                                 |                                 |                     |                                                                           |  |  |

| P0.6     | LEDTS0.<br>EXTENDED1 |                 | LEDTS0.TSIN1 | LEDTS0.TSIN1    |                                 |                                 |                     |                                                                           |  |  |

| P0.7     | LEDTS0.<br>EXTENDED0 |                 | LEDTS0.TSIN0 | LEDTS0.TSIN0    |                                 |                                 |                     |                                                                           |  |  |

| P0.8     | LEDTS1.<br>EXTENDED0 |                 | LEDTS1.TSIN0 | LEDTS1.TSIN0    |                                 |                                 |                     |                                                                           |  |  |

| P0.9     | LEDTS1.<br>EXTENDED1 |                 | LEDTS1.TSIN1 | LEDTS1.TSIN1    |                                 |                                 |                     |                                                                           |  |  |

| P0.10    | LEDTS1.<br>EXTENDED2 |                 | LEDTS1.TSIN2 | LEDTS1.TSIN2    |                                 |                                 |                     |                                                                           |  |  |

| P0.11    | LEDTS1.<br>EXTENDED3 |                 | LEDTS1.TSIN3 | LEDTS1.TSIN3    |                                 |                                 |                     |                                                                           |  |  |

| P0.12    | LEDTS1.<br>EXTENDED4 |                 | LEDTS1.TSIN4 | LEDTS1.TSIN4    |                                 |                                 |                     |                                                                           |  |  |

| P0.13    | LEDTS1.<br>EXTENDED5 |                 | LEDTS1.TSIN5 | LEDTS1.TSIN5    | 1                               |                                 |                     |                                                                           |  |  |

| P0.14    | LEDTS1.<br>EXTENDED6 |                 | LEDTS1.TSIN6 | LEDTS1.TSIN6    | 1                               |                                 |                     |                                                                           |  |  |

| P0.15    | LEDTS1.<br>EXTENDED7 |                 |              | LEDTS1.TSIN7    | 1                               |                                 |                     |                                                                           |  |  |

| P1.0     |                      | USIC0_CH0.DOUT0 |              | USIC0_CH0.HWIN0 | BCCU0.OUT2                      | BCCU0.OUT2                      |                     |                                                                           |  |  |

| P1.1     |                      | USIC0_CH0.DOUT1 |              | USIC0_CH0.HWIN1 | BCCU0.OUT3                      | BCCU0.OUT3                      |                     |                                                                           |  |  |

| P1.2     |                      | USIC0 CH0.DOUT2 |              | USIC0 CH0.HWIN2 | BCCU0.OUT4                      | BCCU0.OUT4                      |                     |                                                                           |  |  |

XMC1400 AA-Step XMC1000 Family

## 3.1.3 Pin Reliability in Overload

When receiving signals from higher voltage devices, low-voltage devices experience overload currents and voltages that go beyond their own IO power supplies specification.

Table 12 defines overload conditions that will not cause any negative reliability impact if all the following conditions are met:

- full operation life-time is not exceeded

- Operating Conditions are met for

- pad supply levels ( $V_{\text{DDP}}$ )

- temperature

If a pin current is outside of the **Operating Conditions** but within the overload conditions, then the parameters of this pin as stated in the Operating Conditions can no longer be guaranteed. Operation is still possible in most cases but with relaxed parameters.

Note: An overload condition on one or more pins does not require a reset.

Note: A series resistor at the pin to limit the current to the maximum permitted overload current is sufficient to handle failure situations like short to battery.

| Parameter                                                                  | Sym              | bol |      | Values | 5    | Unit | Note /         |

|----------------------------------------------------------------------------|------------------|-----|------|--------|------|------|----------------|

|                                                                            |                  |     | Min. | Тур.   | Max. |      | Test Condition |

| Input current on any port pin during overload condition                    | I <sub>OV</sub>  | SR  | -5   | -      | 5    | mA   |                |

| Absolute sum of all input<br>circuit currents during<br>overload condition | I <sub>OVS</sub> | SR  | -    | -      | 25   | mA   |                |

#### Table 12 Overload Parameters

**Figure 11** shows the path of the input currents during overload via the ESD protection structures. The diodes against  $V_{\text{DDP}}$  and ground are a simplified representation of these ESD protection structures.

## 3.2.2 Analog to Digital Converters (ADC)

Table 17 shows the Analog to Digital Converter (ADC) characteristics.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                                           | Symbol                    |                            | Value | S                          | Unit | Note / Test Condition                                                                                        |  |

|-----------------------------------------------------|---------------------------|----------------------------|-------|----------------------------|------|--------------------------------------------------------------------------------------------------------------|--|

|                                                     |                           | Min.                       | Тур.  | Max.                       |      |                                                                                                              |  |

| Supply voltage range<br>(internal reference)        | V <sub>DD_int</sub><br>SR | 2.0                        | -     | 3.0                        | V    | SHSCFG.AREF = $11_B$ ;<br>CALCTR.CALGNSTC =<br>$0C_H$ for $f_{SH}$ = 32 MHz,<br>$12_H$ for $f_{SH}$ = 48 MHz |  |

|                                                     |                           | 3.0                        | -     | 5.5                        | V    | SHSCFG.AREF = $10_B$                                                                                         |  |

| Supply voltage range<br>(external reference)        | $V_{\rm DD\_ext}$ SR      | 3.0                        | -     | 5.5                        | V    | SHSCFG.AREF = 00 <sub>B</sub>                                                                                |  |

| Analog input voltage range                          | $V_{\rm AIN}{ m SR}$      | V <sub>SSP</sub><br>- 0.05 | -     | V <sub>DDP</sub><br>+ 0.05 | V    |                                                                                                              |  |

| Auxiliary analog<br>reference ground <sup>2)</sup>  | $V_{REFGND}$ SR           | V <sub>SSP</sub><br>- 0.05 | -     | 1.0                        | V    | G0CH0                                                                                                        |  |

|                                                     |                           | V <sub>SSP</sub><br>- 0.05 | -     | 0.2                        | V    | G1CH0                                                                                                        |  |

| Internal reference<br>voltage (full scale<br>value) | V <sub>REFINT</sub><br>CC |                            | 5     |                            | V    |                                                                                                              |  |

| Switched capacitance of an                          | C <sub>AINS</sub><br>CC   | -                          | 1.2   | 2                          | pF   | GNCTRxz.GAINy = 00 <sub>B</sub><br>(unity gain)                                                              |  |

| analog input                                        |                           | -                          | 1.2   | 2                          | pF   | GNCTRxz.GAINy = 01 <sub>B</sub><br>(gain g1)                                                                 |  |

|                                                     |                           | -                          | 4.5   | 6                          | pF   | GNCTRxz.GAINy = 10 <sub>B</sub><br>(gain g2)                                                                 |  |

|                                                     |                           | -                          | 4.5   | 6                          | pF   | GNCTRxz.GAINy = 11 <sub>B</sub><br>(gain g3)                                                                 |  |

| Total capacitance of<br>an analog input             | $C_{\text{AINT}}$ CC      | -                          | -     | 10                         | pF   |                                                                                                              |  |

| Total capacitance of the reference input            | $C_{AREFT}$ CC            | -                          | -     | 10                         | pF   |                                                                                                              |  |

### Table 17 ADC Characteristics (Operating Conditions apply)<sup>1)</sup>

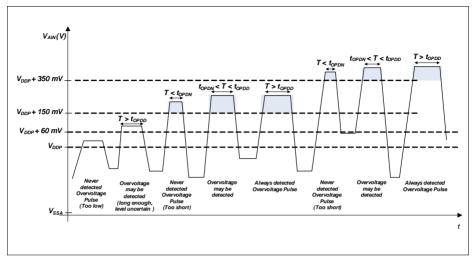

## 3.2.3 Out of Range Comparator (ORC) Characteristics

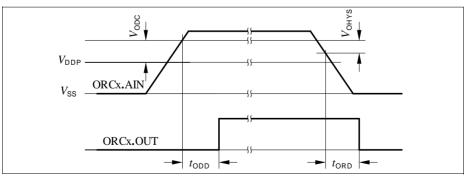

The Out-of-Range Comparator (ORC) triggers on analog input voltages ( $V_{AIN}$ ) above  $V_{DDP}$  on selected input pins (ORCx.AIN) and generates a service request trigger (ORCx.OUT).

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter          | Symbol            |    |      | Values | S    | Unit | Note / Test Condition                                              |  |

|--------------------|-------------------|----|------|--------|------|------|--------------------------------------------------------------------|--|

|                    |                   |    | Min. | Тур.   | Max. |      |                                                                    |  |

| DC Switching Level | $V_{ODC}$         | СС | -    | -      | 180  | mV   | $V_{\text{AIN}} \ge V_{\text{DDP}} + V_{\text{ODC}}$               |  |

| Hysteresis         | $V_{\rm OHYS}$    | CC | 15   | -      | 54   | mV   |                                                                    |  |

| Always detected    | t <sub>OPDD</sub> | CC | 103  | -      | -    | ns   | $V_{\rm AIN} \ge V_{\rm DDP}$ + 150 mV                             |  |

| Overvoltage Pulse  |                   |    | 88   | -      | -    | ns   | $V_{\rm AIN} \ge V_{\rm DDP}$ + 350 mV                             |  |

| Never detected     | t <sub>OPDN</sub> | CC | -    | -      | 21   | ns   | $V_{\rm AIN} \ge V_{\rm DDP}$ + 150 mV                             |  |

| Overvoltage Pulse  |                   |    | -    | -      | 11   | ns   | $V_{\rm AIN} \ge V_{\rm DDP}$ + 350 mV                             |  |

| Detection Delay    | t <sub>ODD</sub>  | CC | 39   | -      | 132  | ns   | $V_{\rm AIN} \ge V_{\rm DDP}$ + 150 mV                             |  |

|                    |                   |    | 31   | -      | 121  | ns   | $V_{\rm AIN} \ge V_{\rm DDP}$ + 350 mV                             |  |

| Release Delay      | t <sub>ORD</sub>  | СС | 44   | -      | 240  | ns   | $V_{\text{AIN}} \leq V_{\text{DDP}}; V_{\text{DDP}} = 5 \text{ V}$ |  |

|                    |                   |    | 57   | -      | 340  | ns   | $V_{\text{AIN}} \le V_{\text{DDP}}; V_{\text{DDP}} = 3.3$ V        |  |

| Enable Delay       | t <sub>OED</sub>  | CC | -    | -      | 300  | ns   | ORCCTRL.ENORCx = 1                                                 |  |

## Table 18Out of Range Comparator (ORC) Characteristics (Operating<br/>Conditions apply; V<sub>DDP</sub> = 3.0 V - 5.5 V; C<sub>1</sub> = 0.25pF)

Figure 13 ORCx.OUT Trigger Generation

Figure 14 ORC Detection Ranges

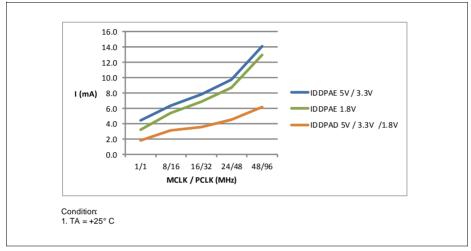

**Figure 17** shows typical graphs for active mode supply current for  $V_{DDP} = 5 \text{ V}$ ,  $V_{DDP} = 3.3 \text{ V}$ ,  $V_{DDP} = 1.8 \text{ V}$  across different clock frequencies.

Figure 17 Active mode, a) peripherals clocks enabled, b) peripherals clocks disabled: Supply current I<sub>DDPA</sub> over supply voltage V<sub>DDP</sub> for different clock frequencies

## 3.2.8 Flash Memory Parameters

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                       | Symbol                  |      | Value | s                 | Unit   | Note /                              |

|---------------------------------|-------------------------|------|-------|-------------------|--------|-------------------------------------|

|                                 |                         | Min. | Тур.  | Max.              | -      | Test Condition                      |

| Erase time per<br>page / sector | t <sub>ERASE</sub> CC   | 6.8  | 7.1   | 7.6               | ms     |                                     |

| Program time per<br>block       | t <sub>PSER</sub> CC    | 102  | 152   | 204               | μS     |                                     |

| Wake-Up time                    | t <sub>WU</sub> CC      | _    | 32.2  | -                 | μs     |                                     |

| Read time per word              | t <sub>a</sub> CC       | _    | 50    | -                 | ns     |                                     |

| Data Retention Time             | t <sub>RET</sub> CC     | 10   | -     | -                 | years  | Max. 100 erase / program cycles     |

| Flash Wait States 1)            | N <sub>WSFLASH</sub> CC | 0    | 0     | 0                 |        | $f_{\rm MCLK} = 8  \rm MHz$         |

|                                 |                         | 0    | 1     | 1                 |        | $f_{\rm MCLK} = 16  \rm MHz$        |

|                                 |                         | 1    | 2     | 2                 |        | $f_{\rm MCLK} = 32  \rm MHz$        |

|                                 |                         | 2    | 2     | 3                 |        | $f_{\rm MCLK} = 48 \ {\rm MHz}$     |

| Erase Cycles                    | N <sub>ECYC</sub> CC    | _    | -     | 5*10 <sup>4</sup> | cycles | Sum of page and sector erase cycles |

| Total Erase Cycles              | N <sub>TECYC</sub> CC   | _    | -     | 2*10 <sup>6</sup> | cycles |                                     |

Table 25 Flash Memory Parameters

1) Flash wait states are automatically inserted by the Flash module during memory read when needed. Typical values are calculated from the execution of the Dhrystone benchmark program.

## 3.3.2 **Power-Up and Supply Threshold Characteristics**

Table 26 provides the characteristics of the supply threshold in XMC1400.

The guard band between the lowest valid operating voltage and the brownout reset threshold provides a margin for noise immunity and hysteresis. The electrical parameters may be violated while  $V_{\text{DDP}}$  is outside its operating range.

The brownout detection triggers a reset within the defined range. The prewarning detection can be used to trigger an early warning and issue corrective and/or fail-safe actions in case of a critical supply voltage drop.

Note: These parameters are not subject to production test, but verified by design and/or characterization.

| Parameter                        | Symbol                                 | Values                                                           |      |                 | Unit | Note /                                                                      |

|----------------------------------|----------------------------------------|------------------------------------------------------------------|------|-----------------|------|-----------------------------------------------------------------------------|

|                                  |                                        | Min.                                                             | Тур. | Max.            | 1    | Test Condition                                                              |

| $V_{\rm DDP}$ ramp-up time       | <i>t</i> <sub>RAMPUP</sub> SR          | $\begin{array}{c} V_{\rm DDP} / \\ S_{\rm VDDPrise} \end{array}$ | -    | 10 <sup>7</sup> | μS   |                                                                             |

| $V_{\rm DDP}$ slew rate          | $S_{\rm VDDPOP}  {\rm SR}$             | 0                                                                | -    | 0.1             | V/µs | Slope during<br>normal operation                                            |

|                                  | $S_{\rm VDDP10}~{ m SR}$               | 0                                                                | -    | 10              | V/µs | Slope during fast<br>transient within +/-<br>10% of V <sub>DDP</sub>        |

|                                  | $S_{\rm VDDPrise}~{ m SR}$             | 0                                                                | -    | 10              | V/µs | Slope during<br>power-on or<br>restart after<br>brownout event              |

|                                  | S <sub>VDDPfall</sub> <sup>1)</sup> SR | 0                                                                | -    | 0.25            | V/µs | Slope during<br>supply falling out<br>of the +/-10%<br>limits <sup>2)</sup> |

| $V_{\rm DDP}$ prewarning voltage | V <sub>DDPPW</sub> CC                  | 2.1                                                              | 2.25 | 2.4             | V    | ANAVDEL.VDEL_<br>SELECT = 00 <sub>B</sub>                                   |

|                                  |                                        | 2.85                                                             | 3    | 3.15            | V    | ANAVDEL.VDEL_<br>SELECT = 01 <sub>B</sub>                                   |

|                                  |                                        | 4.2                                                              | 4.4  | 4.6             | V    | ANAVDEL.VDEL_<br>SELECT = 10 <sub>B</sub>                                   |

# Table 26 Power-Up and Supply Threshold Parameters (Operating Conditions apply)

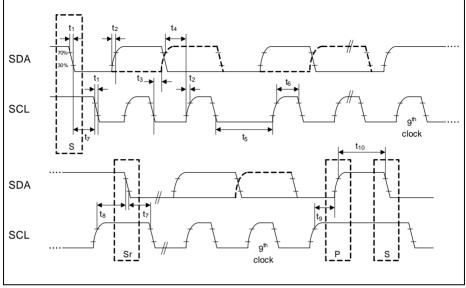

| Table 32 | <b>USIC SSC Slave Mode Timin</b> | na |

|----------|----------------------------------|----|

|          |                                  |    |

| Parameter                                                                                 | Symbol                | Values |      |      | Unit | Note /             |

|-------------------------------------------------------------------------------------------|-----------------------|--------|------|------|------|--------------------|

|                                                                                           |                       | Min.   | Тур. | Max. |      | Test Conditio<br>n |

| Select input DX2 hold after<br>last clock input DX1 receive<br>edge <sup>1)</sup>         | <sup>t</sup> 11<br>SR | 17     | -    | _    | ns   |                    |

| Receive data input<br>DX0/DX[5:3] setup time to<br>shift clock receive edge <sup>1)</sup> | <sup>t</sup> 12<br>SR | 21     | -    | -    | ns   |                    |

| Data input DX0/DX[5:3] hold<br>time from clock input DX1<br>receive edge <sup>1)</sup>    | <sup>t</sup> 13<br>SR | 15     | -    | -    | ns   |                    |

| Data output DOUT[3:0] valid time                                                          | t <sub>14</sub><br>CC | -      | -    | 71   | ns   |                    |

1) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

## Figure 26 USIC IIC Timing

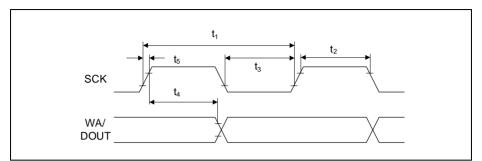

## 3.3.6.3 Inter-IC Sound (IIS) Interface Timing

The following parameters are applicable for a USIC channel operated in IIS mode. *Note: Operating Conditions apply.*

| Table 35 | USIC IIS Master | <b>Transmitter Timing</b> |

|----------|-----------------|---------------------------|

|----------|-----------------|---------------------------|

| Parameter       | Symbol            | Values              |      |                   | Unit | Note /         |

|-----------------|-------------------|---------------------|------|-------------------|------|----------------|

|                 |                   | Min.                | Тур. | Max.              |      | Test Condition |

| Clock period    | t <sub>1</sub> CC | 4/f <sub>MCLK</sub> | -    | -                 | ns   |                |

| Clock HIGH      | t <sub>2</sub> CC | 0.35 x              | -    | -                 | ns   |                |

|                 |                   | t <sub>1min</sub>   |      |                   |      |                |

| Clock Low       | t <sub>3</sub> CC | 0.35 x              | -    | -                 | ns   |                |

|                 |                   | t <sub>1min</sub>   |      |                   |      |                |

| Hold time       | t <sub>4</sub> CC | 0                   | -    | -                 | ns   |                |

| Clock rise time | t <sub>5</sub> CC | -                   | -    | 0.15 x            | ns   |                |

|                 |                   |                     |      | t <sub>1min</sub> |      |                |

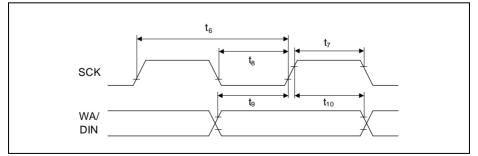

| Figure 27 | USIC IIS Master | Transmitter Timing | 1 |

|-----------|-----------------|--------------------|---|

|-----------|-----------------|--------------------|---|

| Parameter    | Symbol             | Values                      |      |      | Unit | Note /         |

|--------------|--------------------|-----------------------------|------|------|------|----------------|

|              |                    | Min.                        | Тур. | Max. |      | Test Condition |

| Clock period | t <sub>6</sub> SR  | 4/f <sub>MCLK</sub>         | -    | -    | ns   |                |

| Clock HIGH   | t <sub>7</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -    | -    | ns   |                |

| Clock Low    | t <sub>8</sub> SR  | 0.35 x<br>t <sub>6min</sub> | -    | -    | ns   |                |

| Set-up time  | t <sub>9</sub> SR  | 0.3 x<br>t <sub>6min</sub>  | -    | -    | ns   |                |

| Hold time    | t <sub>10</sub> SR | 15                          | -    | -    | ns   |                |

| Table 36 USIC IIS Slave Receiver 1 | Timing |

|------------------------------------|--------|

|------------------------------------|--------|

Figure 28 USIC IIS Slave Receiver Timing

### Package and Reliability

## 4.2 Package Outlines

Figure 29 PG-TSSOP-38-9