Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | 160                                                                        |

| Number of Logic Elements/Cells | 1280                                                                       |

| Total RAM Bits                 | 65536                                                                      |

| Number of I/O                  | 95                                                                         |

| Number of Gates                | -                                                                          |

| Voltage - Supply               | 1.14V ~ 1.26V                                                              |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 132-LFBGA, CSPBGA                                                          |

| Supplier Device Package        | 132-CSBGA (8x8)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/ice40hx1k-cb132 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Routing

There are many resources provided in the iCE40 devices to route signals individually with related control signals. The routing resources consist of switching circuitry, buffers and metal interconnect (routing) segments.

The inter-PLB connections are made with three different types of routing resources: Adjacent (spans two PLBs), x4 (spans five PLBs) and x12 (spans thirteen PLBs). The Adjacent, x4 and x12 connections provide fast and efficient connections in the diagonal, horizontal and vertical directions.

The design tool takes the output of the synthesis tool and places and routes the design.

### **Clock/Control Distribution Network**

Each iCE40 device has eight global inputs, two pins on each side of the device. Note that not all GBINs are available in all packages.

These global inputs can be used as high fanout nets, clock, reset or enable signals. The dedicated global pins are identified as GBIN[7:0] and the global buffers are identified as-GBUF[7:0]. These eight inputs may be used as general purpose I/O if they are not used to drive the clock nets. Global buffer GBUF7 in I/O Bank 3 also provides an optional direct LVDS25 or subLVDS differential clock input.

Table 2-2 lists the connections between a specific global buffer and the inputs on a PLB. All global buffers optionally connect to the PLB CLK input. Any four of the eight global buffers can drive logic inputs to a PLB. Even-numbered global buffers optionally drive the Set/Reset input to a PLB. Similarly, odd-numbered buffers optionally drive the PLB clock-enable input.

Table 2-2. Global Buffer (GBUF) Connections to Programmable Logic Blocks

| Global Buffer | LUT Inputs      | Clock | Reset | Clock Enable |

|---------------|-----------------|-------|-------|--------------|

| GBUF0         |                 | Yes   | Yes   |              |

| GBUF1         |                 | Yes   |       | Yes          |

| GBUF2         |                 | Yes   | Yes   |              |

| GBUF3         | Yes, any 4 of 8 | Yes   |       | Yes          |

| GBUF4         | GBUF Inputs     | Yes   | Yes   |              |

| GBUF5         | 7               | Yes   |       | Yes          |

| GBUF6         |                 | Yes   | Yes   |              |

| GBUF7         | 7               | Yes   |       | Yes          |

The maximum frequency for the global buffers are shown in the iCE40 External Switching Characteristics tables later in this document.

#### **Global Hi-Z Control**

The global high-impedance control signal, GHIZ, connects to all I/O pins on the iCE40 device. This GHIZ signal is automatically asserted throughout the configuration process, forcing all user I/O pins into their high-impedance state.

### Table 2-3. PLL Signal Descriptions

| Signal Name       | Direction | Description                                                                                                                                                                                 |

|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCECLK      | Input     | Input reference clock                                                                                                                                                                       |

| BYPASS            | Input     | When FEEDBACK_PATH is set to SIMPLE, the BYPASS control selects which clock signal connects to the PLLOUT output.                                                                           |

| BTFAGG            | input     | 0 = PLL generated signal<br>1 = REFERENCECLK                                                                                                                                                |

| EXTFEEDBACK       | Input     | External feedback input to PLL. Enabled when the FEEDBACK_PATH attribute is set to EXTERNAL.                                                                                                |

| DYNAMICDELAY[3:0] | Input     | Fine delay adjustment control inputs. Enabled when DELAY_ADJUSTMENT_MODE is set to DYNAMIC.                                                                                                 |

| LATCHINPUTVALUE   | Input     | When enabled, forces the PLL into low-power mode; PLL output is held static at the last input clock value. Set ENABLE ICEGATE_PORTA and PORTB to '1' to enable.                             |

| PLLOUTGLOBAL      | Output    | Output from the Phase-Locked Loop (PLL). Drives a global clock network on the FPGA. The port has optimal connections to global clock buffers GBUF4 and GBUF5.                               |

| PLLOUTCORE        | Output    | Output clock generated by the PLL, drives regular FPGA routing. The frequency generated on this output is the same as the frequency of the clock signal generated on the PLLOUTLGOBAL port. |

| LOCK              | Output    | When High, indicates that the PLL output is phase aligned or locked to the input reference clock.                                                                                           |

| RESET             | Input     | Active low reset.                                                                                                                                                                           |

### sysMEM Embedded Block RAM Memory

Larger iCE40 device includes multiple high-speed synchronous sysMEM Embedded Block RAMs (EBRs), each 4 kbit in size. This memory can be used for a wide variety of purposes including data buffering, and FIFO.

#### sysMEM Memory Block

The sysMEM block can implement single port, pseudo dual port, or FIFO memories with programmable logic resources. Each block can be used in a variety of depths and widths as shown in Table 2-4.

Table 2-4. sysMEM Block Configurations<sup>1</sup>

| Block RAM<br>Configuration                                           | Block RAM<br>Configuration<br>and Size | WADDR Port<br>Size (Bits) | WDATA Port<br>Size (Bits) | RADDR Port<br>Size (Bits) | RDATA Port<br>Size (Bits) | MASK Port<br>Size (Bits) |

|----------------------------------------------------------------------|----------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

| SB_RAM256x16<br>SB_RAM256x16NR<br>SB_RAM256x16NW<br>SB_RAM256x16NRNW | 256x16 (4K)                            | 8 [7:0]                   | 16 [15:0]                 | 8 [7:0]                   | 16 [15:0]                 | 16 [15:0]                |

| SB_RAM512x8<br>SB_RAM512x8NR<br>SB_RAM512x8NW<br>SB_RAM512x8NRNW     | 512x8 (4K)                             | 9 [8:0]                   | 8 [7:0]                   | 9 [8:0]                   | 8 [7:0]                   | No Mask Port             |

| SB_RAM1024x4<br>SB_RAM1024x4NR<br>SB_RAM1024x4NW<br>SB_RAM1024x4NRNW | 1024x4 (4K)                            | 10 [9:0]                  | 4 [3:0]                   | 10 [9:0]                  | 4 [3:0]                   | No Mask Port             |

| SB_RAM2048x2<br>SB_RAM2048x2NR<br>SB_RAM2048x2NW<br>SB_RAM2048x2NRNW | 2048x2 (4K)                            | 11 [10:0]                 | 2 [1:0]                   | 11 [10:0]                 | 2 [1:0]                   | No Mask Port             |

<sup>1.</sup> For iCE40 EBR primitives with a negative-edged Read or Write clock, the base primitive name is appended with a 'N' and a 'R' or 'W' depending on the clock that is affected.

#### **RAM Initialization and ROM Operation**

If desired, the contents of the RAM can be pre-loaded during device configuration.

By preloading the RAM block during the chip configuration cycle and disabling the write controls, the sysMEM block can also be utilized as a ROM.

Note the sysMEM Embedded Block RAM Memory address 0 cannot be initialized.

#### **Memory Cascading**

Larger and deeper blocks of RAM can be created using multiple EBR sysMEM Blocks.

#### **RAM4k Block**

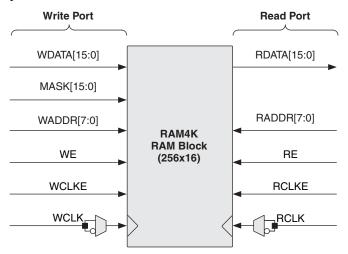

Figure 2-4 shows the 256x16 memory configurations and their input/output names. In all the sysMEM RAM modes, the input data and addresses for the ports are registered at the input of the memory array.

Figure 2-4. sysMEM Memory Primitives

Table 2-5. EBR Signal Descriptions

| Signal Name | Direction | Description                                                                               |

|-------------|-----------|-------------------------------------------------------------------------------------------|

| WDATA[15:0] | Input     | Write Data input.                                                                         |

| MASK[15:0]  | Input     | Masks write operations for individual data bit-lines.  0 = write bit; 1 = don't write bit |

| WADDR[7:0]  | Input     | Write Address input. Selects one of 256 possible RAM locations.                           |

| WE          | Input     | Write Enable input.                                                                       |

| WCLKE       | Input     | Write Clock Enable input.                                                                 |

| WCLK        | Input     | Write Clock input. Default rising-edge, but with falling-edge option.                     |

| RDATA[15:0] | Output    | Read Data output.                                                                         |

| RADDR[7:0]  | Input     | Read Address input. Selects one of 256 possible RAM locations.                            |

| RE          | Input     | Read Enable input.                                                                        |

| RCLKE       | Input     | Read Clock Enable input.                                                                  |

| RCLK        | Input     | Read Clock input. Default rising-edge, but with falling-edge option.                      |

For further information on the sysMEM EBR block, please refer to TN1250, Memory Usage Guide for iCE40 Devices.

### sys<sub>I</sub>O

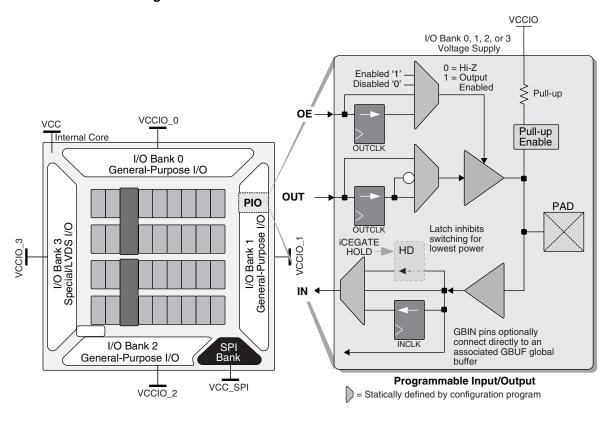

#### **Buffer Banks**

iCE40 devices have up to four I/O banks with independent  $V_{CCIO}$  rails with an additional configuration bank  $V_{CC\ SPI}$  for the SPI I/Os.

#### Programmable I/O (PIO)

The programmable logic associated with an I/O is called a PIO. The individual PIO are connected to their respective sysIO buffers and pads. The PIOs are placed on all four sides of the device.

Figure 2-5. I/O Bank and Programmable I/O Cell

The PIO contains three blocks: an input register block, output register block iCEgate<sup>™</sup> and tri-state register block. To save power, the optional iCEgate<sup>™</sup> latch can selectively freeze the state of individual, non-registered inputs within an I/O bank. Note that the freeze signal is common to the bank. These blocks can operate in a variety of modes along with the necessary clock and selection logic.

#### Input Register Block

The input register blocks for the PIOs on all edges contain registers that can be used to condition high-speed interface signals before they are passed to the device core. In Generic DDR mode, two registers are used to sample the data on the positive and negative edges of the system clock signal, creating two data streams.

#### **Output Register Block**

The output register block can optionally register signals from the core of the device before they are passed to the sysIO buffers. In Generic DDR mode, two registers are used to capture the data on the positive and negative edge of the system clock and then muxed creating one data stream.

Figure 2-6 shows the input/output register block for the PIOs.

fers. Bank 3 additionally supports differential LVDS25 input buffers. Each sysIO bank has its own dedicated power supply.

### Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$ ,  $V_{CCIO\_2}$ ,  $V_{PP\_2V5}$ , and  $V_{CC\_SPI}$  have reached the level defined in the Power-On-Reset Voltage table in the DC and Switching Characteristics section of this data sheet. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. The default configuration of the I/O pins in a device prior to configuration is tri-stated with a weak pull-up to  $V_{CCIO}$ . The I/O pins will maintain the pre-configuration state until  $V_{CC}$  and  $V_{CCIO}$  (for I/O banks containing configuration I/Os) have reached levels, at which time the I/Os will take on the software user-configured settings only after a proper download/configuration. Unused IOs are automatically blocked and the pullup termination is disabled.

#### **Supported Standards**

The iCE40 sysIO buffer supports both single-ended and differential input standards. The single-ended standard supported is LVCMOS. The buffer supports the LVCMOS 1.8, 2.5, and 3.3 V standards. The buffer has individually configurable options for bus maintenance (weak pull-up or none). The High Current output buffer have individually configurable options for drive strength.

Table 2-7 and Table 2-8 show the I/O standards (together with their supply and reference voltages) supported by the iCE40 devices.

Table 2-7. Supported Input Standards

| Input Standard          |          | V <sub>CCIO</sub> (Typical) |       |

|-------------------------|----------|-----------------------------|-------|

| input Standard          | 3.3 V    | 2.5 V                       | 1.8 V |

| Single-Ended Interfaces | <u> </u> |                             |       |

| LVCMOS33                | Yes      |                             |       |

| LVCMOS25                |          | Yes                         |       |

| LVCMOS18                |          |                             | Yes   |

| Differential Interfaces | <u> </u> |                             |       |

| LVDS25 <sup>1</sup>     |          | Yes                         |       |

| subLVDS <sup>1</sup>    |          |                             | Yes   |

<sup>1.</sup> Bank 3 only.

Table 2-8. Supported Output Standards

| Output Standard         | V <sub>CCIO</sub> (Typical) |  |

|-------------------------|-----------------------------|--|

| Single-Ended Interfaces |                             |  |

| LVCMOS33                | 3.3                         |  |

| LVCMOS25                | 2.5                         |  |

| LVCMOS18                | 1.8                         |  |

| Differential Interfaces |                             |  |

| LVDS25E <sup>1</sup>    | 2.5                         |  |

| subLVDSE <sup>1</sup>   | 1.8                         |  |

<sup>1.</sup> These interfaces can be emulated with external resistors in all devices.

### **Non-Volatile Configuration Memory**

All iCE40 devices provide a Non-Volatile Configuration Memory (NVCM) block which can be used to configure the device.

For more information on the NVCM, please refer to TN1248, iCE40 Programming and Configuration Usage Guide.

# iCE40 LP/HX Family Data Sheet DC and Switching Characteristics

October 2015 Data Sheet DS1040

# **Absolute Maximum Ratings**<sup>1, 2, 3, 4</sup>

|                                                               | iCE40 LP/HX        |

|---------------------------------------------------------------|--------------------|

| Supply Voltage V <sub>CC</sub>                                | . −0.5 V to 1.42 V |

| Output Supply Voltage V <sub>CCIO</sub> , V <sub>CC_SPI</sub> | . −0.5 V to 3.60 V |

| NVCM Supply Voltage V <sub>PP_2V5</sub>                       | . −0.5 V to 3.60 V |

| PLL Supply Voltage V <sub>CCPLL</sub>                         | . −0.5 V to 1.30 V |

| I/O Tri-state Voltage Applied                                 | . −0.5 V to 3.60 V |

| Dedicated Input Voltage Applied                               | . −0.5 V to 3.60 V |

| Storage Temperature (Ambient)                                 | . –65 °C to 150 °C |

| Junction Temperature (T <sub>J</sub> )                        | . –55 °C to 125 °C |

<sup>1.</sup> Stress above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

- 2. Compliance with the Lattice Thermal Management document is required.

- 3. All voltages referenced to GND.

- IOs can support a 200 mV Overshoot above the Recommend Operating Conditions V<sub>CCIO</sub> (Max) and -200mV Undershoot below V<sub>IL</sub> (Min).

Overshoot and Undershoot is permitted for 25% duty cycle but must not exceed 1.6 ns.

### Recommended Operating Conditions<sup>1</sup>

| Symbol                               | Parameter                                                            |                                                           |      | Max. | Units |

|--------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------|------|------|-------|

| V <sub>CC</sub> <sup>1</sup>         | Core Supply Voltage                                                  |                                                           | 1.14 | 1.26 | V     |

|                                      |                                                                      | Slave SPI Configuration                                   | 1.71 | 3.46 | V     |

| V                                    | V <sub>PP 2V5</sub> NVCM Programming and                             | Master SPI Configuration                                  | 2.30 | 3.46 | V     |

| V <sub>PP_2V5</sub>                  | V <sub>PP_2V5</sub> NVCM Programming and<br>Operating Supply Voltage | Configure from NVCM                                       | 2.30 | 3.46 | V     |

|                                      |                                                                      | NVCM Programming                                          | 2.30 | 3.00 | V     |

| V <sub>PP_FAST</sub> <sup>4</sup>    | Optional fast NVCM programming supply. L                             | Optional fast NVCM programming supply. Leave unconnected. |      | N/A  | V     |

| V <sub>CCPLL</sub> <sup>5, 6</sup>   | PLL Supply Voltage                                                   |                                                           | 1.14 | 1.26 | V     |

| 1, 2, 3                              | I/O Duiver Complex Velters                                           | V <sub>CCIO0-3</sub>                                      | 1.71 | 3.46 | V     |

| V <sub>CCIO</sub> <sup>1, 2, 3</sup> | I/O Driver Supply Voltage                                            | V <sub>CC_SPI</sub>                                       | 1.71 | 3.46 | V     |

| t <sub>JIND</sub>                    | Junction Temperature Industrial Operation                            |                                                           | -40  | 100  | °C    |

| t <sub>PROG</sub>                    | Junction Temperature NVCM Programming                                |                                                           | 10   | 30   | °C    |

|                                      |                                                                      |                                                           |      |      |       |

Like power supplies must be tied together. For example, if V<sub>CCIO</sub> and V<sub>CC\_SPI</sub> are both the same voltage, they must also be the same supply.

<sup>2.</sup> See recommended voltages by I/O standard in subsequent table.

<sup>3.</sup>  $V_{CCIO}$  pins of unused I/O banks should be connected to the  $V_{CC}$  power supply on boards.

V<sub>PP\_FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications, except CM36 and CM49 packages MUST have the V<sub>PP\_FAST</sub> ball connected to V<sub>CCIO\_0</sub> ball externally.

<sup>5.</sup> No PLL available on the iCE40LP384 and iCE40LP640 device.

<sup>6.</sup>  $V_{CCPLL}$  is tied to  $V_{CC}$  internally in packages without PLLs pins.

# Power Supply Ramp Rates<sup>1, 2</sup>

| Symbol            | Parameter                                       |                                                                                                | Min. | Max. | Units |

|-------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|-------|

|                   |                                                 | All configuration modes. No power supply sequencing.                                           | 0.40 | 10   | V/ms  |

|                   | Power supply ramp rates for all power supplies. | Configuring from Slave SPI. No power supply sequencing,                                        | 0.01 | 10   | V/ms  |

| <sup>t</sup> RAMP |                                                 | Configuring from NVCM. $V_{CC}$ and $V_{PP\_2V5}$ to be powered 0.25 ms before $V_{CC\_SPI}$ . | 0.01 | 10   | V/ms  |

|                   |                                                 | Configuring from MSPI. $V_{CC}$ and $V_{PP\_SPI}$ to be powered 0.25 ms before $V_{PP\_2V5}$ . | 0.01 | 10   | V/ms  |

<sup>1.</sup> Assumes monotonic ramp rates.

### Power-On-Reset Voltage Levels<sup>1</sup>

| Symbol             | Device                         | Parameter                                                                   |         | Min. | Max. | Units |

|--------------------|--------------------------------|-----------------------------------------------------------------------------|---------|------|------|-------|

| V <sub>PORUP</sub> | iCE40LP384                     | Power-On-Reset ramp-up trip point                                           | VCC     | 0.67 | 0.99 | V     |

| iCE<br>iCE         |                                | (band gap based circuit monitoring VCC, VCCIO 2, VCC SPI and                | VCCIO_2 | 0.70 | 1.59 | V     |

|                    |                                | VPP_2V5)                                                                    | VCC_SPI | 0.70 | 1.59 | V     |

|                    |                                | ·                                                                           | VPP_2V5 | 0.70 | 1.59 | V     |

|                    | iCE40LP640,                    | (band gap based circuit monitoring VCC, VCCIO_2, VCC_SPI and VPP_2V5)       | VCC     | 0.55 | 0.75 | V     |

|                    | iCE40LP/HX1K,<br>iCE40LP/HX4K, |                                                                             | VCCIO_2 | 0.86 | 1.29 | V     |

|                    | iCE40LP/HX8K                   |                                                                             | VCC_SPI | 0.86 | 1.29 | V     |

|                    |                                |                                                                             | VPP_2V5 | 0.86 | 1.33 | V     |

| V <sub>PORDN</sub> | iCE40LP384                     | Power-On-Reset ramp-down trip                                               | VCC     | _    | 0.64 | V     |

|                    |                                | point (band gap based circuit monitoring VCC, VCCIO_2, VCC_SPI and VPP_2V5) | VCCIO_2 | _    | 1.59 | V     |

|                    |                                |                                                                             | VCC_SPI | _    | 1.59 | V     |

|                    |                                |                                                                             | VPP_2V5 | _    | 1.59 | V     |

|                    | iCE40LP640,                    | Power-On-Reset ramp-down trip                                               | VCC     | _    | 0.75 | V     |

|                    | iCE40LP/HX1K,<br>iCE40LP/HX4K, | point (band gap based circuit monitoring VCC, VCCIO_2, VCC_SPI              | VCCIO_2 | _    | 1.29 | V     |

|                    | iCE40LP/HX8K                   | and VPP_2V5)                                                                | VCC_SPI | _    | 1.29 | V     |

|                    |                                |                                                                             | VPP_2V5 | _    | 1.33 | V     |

<sup>1.</sup> These POR trip points are only provided for guidance. Device operation is only characterized for power supply voltages specified under recommended operating conditions.

### **ESD Performance**

Please refer to the iCE40 Product Family Qualification Summary for complete qualification data, including ESD performance.

<sup>2.</sup> iCE40LP384 requires  $V_{CC}$  to be greater than 0.7V when  $V_{CCIO}$  and  $V_{CC\_SPI}$  are above GND.

### **DC Electrical Characteristics**

### **Over Recommended Operating Conditions**

| Symbol                          | Parameter                                       | Condition                                                                                                                           | Min. | Тур. | Max.  | Units |

|---------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------|

| ·-, ···                         | Input or I/O Leakage                            | $0V < V_{IN} < V_{CCIO} + 0.2 V$                                                                                                    | _    | _    | +/-10 | μΑ    |

| C <sub>1</sub> <sup>6, 7</sup>  | I/O Capacitance <sup>2</sup>                    | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}$<br>$V_{CC} = \text{Typ.}, V_{IO} = 0 \text{ to } V_{CCIO} + 0.2 \text{ V}$ | _    | 6    | _     | pf    |

| C <sub>2</sub> <sup>6, 7</sup>  | Global Input Buffer<br>Capacitance <sup>2</sup> | $V_{CCIO} = 3.3 \text{ V}, 2.5 \text{ V}, 1.8 \text{ V}$<br>$V_{CC} = \text{Typ.}, V_{IO} = 0 \text{ to } V_{CCIO} + 0.2 \text{ V}$ | _    | 6    | _     | pf    |

| $V_{HYST}$                      | Input Hysteresis                                | V <sub>CCIO</sub> = 1.8 V, 2.5 V, 3.3 V                                                                                             | _    | 200  | _     | mV    |

| I <sub>PU</sub> <sup>6, 7</sup> | Internal PIO Pull-up                            | $V_{CCIO} = 1.8 \text{ V}, 0 = < V_{IN} < = 0.65 V_{CCIO}$                                                                          | -3   | _    | -31   | μΑ    |

|                                 | Current                                         | $V_{CCIO} = 2.5 \text{ V}, 0 = < V_{IN} < = 0.65 V_{CCIO}$                                                                          | -8   | _    | -72   | μΑ    |

|                                 |                                                 | $V_{CCIO} = 3.3 \text{ V}, 0 = < V_{IN} < = 0.65 \text{ V}_{CCIO}$                                                                  | -11  |      | -128  | μΑ    |

- 1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tri-stated. It is not measured with the output driver active. Internal pull-up resistors are disabled.

- 2. T<sub>.1</sub> 25°C, f = 1.0 MHz.

- 3. Please refer to  $V_{IL}$  and  $V_{IH}$  in the sysIO Single-Ended DC Electrical Characteristics table of this document.

- 4. Only applies to IOs in the SPI bank following configuration.

- 5. Some products are clamped to a diode when  $V_{IN}$  is larger than  $V_{CCIO}$ .

- 6. High current IOs has three sysIO buffers connected together.

- 7. The iCE40LP640 and iCE40LP1K SWG16 package has CDONE and a sysIO buffer are connected together.

### Static Supply Current - LP Devices<sup>1, 2, 3, 4</sup>

| Symbol                                 | Parameter                                                   | Device      | Typ. V <sub>CC</sub> ⁴ | Units |

|----------------------------------------|-------------------------------------------------------------|-------------|------------------------|-------|

|                                        |                                                             | iCE40LP384  | 21                     | μΑ    |

| Icc                                    |                                                             | iCE40LP640  | 100                    | μΑ    |

|                                        | Core Power Supply                                           | iCE40LP1K   | 100                    | μΑ    |

|                                        |                                                             | iCE40LP4K   | 250                    | μΑ    |

|                                        |                                                             | iCE40LP8K   | 250                    | μΑ    |

| I <sub>CCPLL</sub> <sup>5, 6</sup>     | PLL Power Supply                                            | All devices | 0.5                    | μΑ    |

| I <sub>PP_2V5</sub>                    | NVCM Power Supply                                           | All devices | 1.0                    | μΑ    |

| I <sub>CCIO,</sub> I <sub>CC_SPI</sub> | Bank Power Supply <sup>4</sup><br>V <sub>CCIO</sub> = 2.5 V | All devices | 3.5                    | μΑ    |

Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip PLL is off. For more detail with your specific design, use the Power Calculator tool. Power specified with master SPI configuration mode. Other modes may be up to 25% higher.

- 2. Frequency = 0 MHz.

- 3.  $T_{J} = 25$  °C, power supplies at nominal voltage.

- 4. Does not include pull-up.

- 5. No PLL available on the iCE40LP384 and iCE40LP640 device.

- 6.  $V_{CCPLL}$  is tied to  $V_{CC}$  internally in packages without PLLs pins.

# Static Supply Current – HX Devices<sup>1, 2, 3, 4</sup>

| Symbol                          | Parameter                                                   | Device      | Typ. V <sub>CC</sub> ⁴ | Units |

|---------------------------------|-------------------------------------------------------------|-------------|------------------------|-------|

|                                 |                                                             | iCE40HX1K   | 296                    | μΑ    |

| I <sub>CC</sub>                 | Core Power Supply                                           | iCE40HX4K   | 1140                   | μΑ    |

|                                 |                                                             | iCE40HX8K   | 1140                   | μΑ    |

| I <sub>CCPLL</sub> <sup>5</sup> | PLL Power Supply                                            | All devices | 0.5                    | μΑ    |

| I <sub>PP_2V5</sub>             | NVCM Power Supply                                           | All devices | 1.0                    | μΑ    |

| Iccio, Icc_spi                  | Bank Power Supply <sup>4</sup><br>V <sub>CCIO</sub> = 2.5 V | All devices | 3.5                    | μΑ    |

Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip PLL is off. For more detail with your specific design, use the Power Calculator tool. Power specified with master SPI configuration mode. Other modes may be up to 25% higher.

- 2. Frequency = 0 MHz.

- 3.  $T_J = 25$  °C, power supplies at nominal voltage.

- 4. Does not include pull-up.

- 5.  $V_{\mbox{\footnotesize CCPLL}}$  is tied to  $V_{\mbox{\footnotesize CC}}$  internally in packages without PLLs pins.

# Programming NVCM Supply Current – LP Devices<sup>1, 2, 3, 4</sup>

| Symbol                                            | Parameter          | Device      | Typ. V <sub>CC</sub> ⁵ | Units |

|---------------------------------------------------|--------------------|-------------|------------------------|-------|

|                                                   |                    | iCE40LP384  | 60                     | μΑ    |

|                                                   | Core Power Supply  | iCE40LP640  | 120                    | μΑ    |

| Icc                                               |                    | iCE40LP1K   | 120                    | μΑ    |

|                                                   |                    | iCE40LP4K   | 350                    | μΑ    |

|                                                   |                    | iCE40LP8K   | 350                    | μΑ    |

| I <sub>CCPLL</sub> <sup>6, 7</sup>                | PLL Power Supply   | All devices | 0.5                    | μΑ    |

| I <sub>PP_2V5</sub>                               | NVCM Power Supply  | All devices | 2.5                    | mA    |

| I <sub>CCIO<sup>8</sup>, I<sub>CC_SPI</sub></sub> | Bank Power Supply⁵ | All devices | 3.5                    | mA    |

- 1. Assumes all inputs are held at  $V_{\mbox{\scriptsize CCIO}}$  or GND and all outputs are tri-stated.

- 2. Typical user pattern.

- 3. SPI programming is at 8 MHz.

- 4.  $T_{.1} = 25$  °C, power supplies at nominal voltage.

- 5. Per bank.  $V_{CCIO} = 2.5 \text{ V}$ . Does not include pull-up.

- 6. No PLL available on the iCE40-LP384 and iCE40-LP640 device.

- 7.  $V_{\mbox{\footnotesize CCPLL}}$  is tied to  $V_{\mbox{\footnotesize CC}}$  internally in packages without PLLs pins.

- 8. V<sub>PP\_FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications, except CM36 and CM49 packages MUST have the V<sub>PP\_FAST</sub> ball connected to V<sub>CCIO\_0</sub> ball externally.

# Programming NVCM Supply Current – HX Devices<sup>1, 2, 3, 4</sup>

| Symbol                          | Parameter          | Device      | Typ. V <sub>CC</sub> ⁵ | Units |

|---------------------------------|--------------------|-------------|------------------------|-------|

|                                 |                    | iCE40HX1K   | 278                    | μΑ    |

| I <sub>CC</sub>                 | Core Power Supply  | iCE40HX4K   | 1174                   | μΑ    |

|                                 |                    | iCE40HX8K   | 1174                   | μΑ    |

| I <sub>CCPLL</sub> <sup>6</sup> | PLL Power Supply   | All devices | 0.5                    | μΑ    |

| I <sub>PP_2V5</sub>             | NVCM Power Supply  | All devices | 2.5                    | mA    |

| Iccio <sup>7</sup> , Icc spi    | Bank Power Supply⁵ | All devices | 3.5                    | mA    |

- 1. Assumes all inputs are held at V<sub>CCIO</sub> or GND and all outputs are tri-stated.

- 2. Typical user pattern.

- 3. SPI programming is at 8 MHz.

- 4.  $T_{J} = 25$  °C, power supplies at nominal voltage.

- 5. Per bank. V<sub>CCIO</sub> = 2.5 V. Does not include pull-up.

- 6.  $V_{CCPLL}$  is tied to  $V_{CC}$  internally in packages without PLLs pins.

- 7. V<sub>PP FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications.

# Peak Startup Supply Current – LP Devices

| Symbol                                | Parameter               | Device     | Max  | Units |

|---------------------------------------|-------------------------|------------|------|-------|

|                                       |                         | iCE40LP384 | 7.7  | mA    |

|                                       |                         | iCELP640   | 6.4  | mA    |

| I <sub>CCPEAK</sub>                   | Core Power Supply       | iCE40LP1K  | 6.4  | mA    |

|                                       |                         | iCE40LP4K  | 15.7 | mA    |

|                                       |                         | iCE40LP8K  | 15.7 | mA    |

|                                       |                         | iCE40LP1K  | 1.5  | mA    |

| I <sub>CCPLLPEAK</sub> 1, 2, 4        | PLL Power Supply        | iCELP640   | 1.5  | mA    |

| CCPLLPEAK                             | PLL Power Supply        | iCE40LP4K  | 8.0  | mA    |

|                                       |                         | iCE40LP8K  | 8.0  | mA    |

|                                       |                         | iCE40LP384 | 3.0  | mA    |

|                                       |                         | iCELP640   | 7.7  | mA    |

| I <sub>PP_2V5PEAK</sub>               | NVCM Power Supply       | iCE40LP1K  | 7.7  | mA    |

|                                       |                         | iCE40LP4K  | 4.2  | mA    |

|                                       |                         | iCE40LP8K  | 4.2  | mA    |

|                                       |                         | iCE40LP384 | 5.7  | mA    |

| I <sub>PP_FASTPEAK</sub> <sup>3</sup> | NVCM Programming Supply | iCELP640   | 8.1  | mA    |

|                                       |                         | iCE40LP1K  | 8.1  | mA    |

|                                       |                         | iCE40LP384 | 8.4  | mA    |

|                                       |                         | iCELP640   | 3.3  | mA    |

| ICCIOPEAK <sup>5</sup> , ICC_SPIPEAK  | Bank Power Supply       | iCE40LP1K  | 3.3  | mA    |

|                                       |                         | iCE40LP4K  | 8.2  | mA    |

|                                       |                         | iCE40LP8K  | 8.2  | mA    |

- 1. No PLL available on the iCE40LP384 and iCE40LP640 device.

- 2.  $V_{CCPLL}$  is tied to  $V_{CC}$  internally in packages without PLLs pins.

- 3. V<sub>PP\_FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications, except CM36 and CM49 packages MUST have the V<sub>PP\_FAST</sub> ball connected to V<sub>CCIO\_0</sub> ball externally.

- 4. While no PLL is available in the iCE40-LP640 the  $I_{CCPLLPEAK}$  is additive to  $I_{CCPEAK}$ .

- 5. iCE40LP384 requires  $V_{CC}$  to be greater than 0.7 V when  $V_{CCIO}$  and  $V_{CC\_SPI}$  are above GND.

### sysIO Differential Electrical Characteristics

The LVDS25E/subLVDSE differential output buffers are available on all banks but the LVDS/subLVDS input buffers are only available on Bank 3 of iCE40 devices.

### LVDS25

### **Over Recommended Operating Conditions**

| Parameter<br>Symbol   | Parameter Description        | Test Conditions             | Min.                         | Тур.                 | Max.                 | Units |

|-----------------------|------------------------------|-----------------------------|------------------------------|----------------------|----------------------|-------|

| $V_{INP}$ , $V_{INM}$ | Input Voltage                | $V_{\text{CCIO}}^{1} = 2.5$ | 0                            |                      | 2.5                  | V     |

| $V_{THD}$             | Differential Input Threshold |                             | 250                          | 350                  | 450                  | mV    |

| $V_{CM}$              | Input Common Mode Voltage    | $V_{CCIO}^{1} = 2.5$        | (V <sub>CCIO</sub> /2) - 0.3 | V <sub>CCIO</sub> /2 | $(V_{CCIO}/2) + 0.3$ | V     |

| I <sub>IN</sub>       | Input Current                | Power on                    |                              | 1                    | ±10                  | μΑ    |

<sup>1.</sup> Typical.

### subLVDS

| Parameter<br>Symbol                | Parameter Description        | Test Conditions             | Min.                          | Тур.                 | Max.                  | Units |

|------------------------------------|------------------------------|-----------------------------|-------------------------------|----------------------|-----------------------|-------|

| V <sub>INP,</sub> V <sub>INM</sub> | Input Voltage                | $V_{\text{CCIO}}^{1} = 1.8$ | 0                             | _                    | 1.8                   | V     |

| $V_{THD}$                          | Differential Input Threshold |                             | 100                           | 150                  | 200                   | mV    |

| V <sub>CM</sub>                    | Input Common Mode Voltage    | $V_{\text{CCIO}}^{1} = 1.8$ | (V <sub>CCIO</sub> /2) - 0.25 | V <sub>CCIO</sub> /2 | $(V_{CCIO}/2) + 0.25$ | V     |

| I <sub>IN</sub>                    | Input Current                | Power on                    | _                             | _                    | ±10                   | μΑ    |

<sup>1.</sup> Typical.

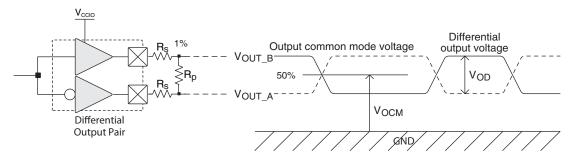

### **SubLVDS Emulation**

The iCE40 family supports the differential subLVDS standard. The output standard is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all banks of the devices. The subLVDS input standard is supported by the LVDS25 differential input buffer. The scheme shown in Figure 3-2 is one possible solution for subLVDSE output standard implementation. Use LVDS25E mode with suggested resistors for subLVDSE operation. Resistor values in Figure 3-2 are industry standard values for 1% resistors.

Figure 3-2. subLVDSE

Table 3-2. subLVDSE DC Conditions

| Parameter         | Description                 | Тур.  | Units |

|-------------------|-----------------------------|-------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20    | Ohms  |

| R <sub>S</sub>    | Driver series resistor      | 270   | Ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 120   | Ohms  |

| R <sub>T</sub>    | Receiver termination        | 100   | Ohms  |

| V <sub>OH</sub>   | Output high voltage         | 1.43  | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.07  | V     |

| $V_{OD}$          | Output differential voltage | 0.35  | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 0.9   | V     |

| Z <sub>BACK</sub> | Back impedance              | 100.5 | Ohms  |

| I <sub>DC</sub>   | DC output current           | 2.8   | mA    |

### **Derating Logic Timing**

Logic timing provided in the following sections of the data sheet and the Lattice design tools are worst case numbers in the operating range. Actual delays may be much faster. Lattice design tools can provide logic timing numbers at a particular temperature and voltage.

### Maximum sysIO Buffer Performance<sup>2</sup>

| I/O Standard           | Max. Speed | Units |

|------------------------|------------|-------|

|                        | Inputs     |       |

| LVDS25 <sup>1</sup>    | 400        | MHz   |

| subLVDS18 <sup>1</sup> | 400        | MHz   |

| LVCMOS33               | 250        | MHz   |

| LVCMOS25               | 250        | MHz   |

| LVCMOS18               | 250        | MHz   |

|                        | Outputs    |       |

| LVDS25E                | 250        | MHz   |

| subLVDS18E             | 155        | MHz   |

| LVCMOS33               | 250        | MHz   |

| LVCMOS25               | 250        | MHz   |

| LVCMOS18               | 155        | MHz   |

<sup>1.</sup> Supported in Bank 3 only.

### iCE40 Family Timing Adders

### Over Recommended Commercial Operating Conditions - LP Devices<sup>1, 2, 3, 4, 5</sup>

| Buffer Type      | Description                                  | Timing | Units |

|------------------|----------------------------------------------|--------|-------|

| Input Adjusters  |                                              |        |       |

| LVDS25           | LVDS, V <sub>CCIO</sub> = 2.5 V              | -0.18  | ns    |

| subLVDS          | subLVDS, V <sub>CCIO</sub> = 1.8 V           | 0.82   | ns    |

| LVCMOS33         | LVCMOS, V <sub>CCIO</sub> = 3.3 V            | 0.18   | ns    |

| LVCMOS25         | LVCMOS, V <sub>CCIO</sub> = 2.5 V            | 0.00   | ns    |

| LVCMOS18         | LVCMOS, V <sub>CCIO</sub> = 1.8 V            | 0.19   | ns    |

| Output Adjusters | ·                                            |        |       |

| LVDS25E          | LVDS, Emulated, V <sub>CCIO</sub> = 2.5 V    | 0.00   | ns    |

| subLVDSE         | subLVDS, Emulated, V <sub>CCIO</sub> = 1.8 V | 1.32   | ns    |

| LVCMOS33         | LVCMOS, V <sub>CCIO</sub> = 3.3 V            | -0.12  | ns    |

| LVCMOS25         | LVCMOS, V <sub>CCIO</sub> = 2.5 V            | 0.00   | ns    |

| LVCMOS18         | LVCMOS, V <sub>CCIO</sub> = 1.8 V            | 1.32   | ns    |

- 1. Timing adders are relative to LVCMOS25 and characterized but not tested on every device.

- 2. LVCMOS timing measured with the load specified in Switching Test Condition table.

- 3. All other standards tested according to the appropriate specifications.

- 4. Commercial timing numbers are shown.

- 5. Not all I/O standards are supported for all banks. See the Architecture section of this data sheet for details.

<sup>2.</sup> Measured with a toggling pattern

# iCE40 External Switching Characteristics – LP Devices (Continued)<sup>1, 2</sup>

| Parameter         | Description                                               | Device    | Min.  | Max. | Units |

|-------------------|-----------------------------------------------------------|-----------|-------|------|-------|

|                   | t <sub>HPLL</sub> Clock to Data Hold - PIO Input Register | iCE40LP1K | -0.90 | _    | ns    |

| t <sub>HPLL</sub> |                                                           | iCE40LP4K | -0.80 | _    | ns    |

|                   |                                                           | iCE40LP8K | -0.80 | _    | ns    |

<sup>1.</sup> Exact performance may vary with device and design implementation. Commercial timing numbers are shown at 85 °C and 1.14 V. Other operating conditions can be extracted from the iCECube2 software.

<sup>2.</sup> General I/O timing numbers based on LVCMOS 2.5, 0pf load.

<sup>3.</sup> Supported on devices with a PLL.

# iCE40 External Switching Characteristics – HX Devices 1,2

| Parameter              | Description                                   | Device               | Min.     | Max.     | Units |

|------------------------|-----------------------------------------------|----------------------|----------|----------|-------|

| Clocks                 | ,                                             | l                    |          | l        |       |

| Primary Clocks         |                                               |                      |          |          |       |

| f <sub>MAX_GBUF</sub>  | Frequency for Global Buffer Clock network     | All iCE40HX devices  | _        | 275      | MHz   |

| t <sub>W_GBUF</sub>    | Clock Pulse Width for Global Buffer           | All iCE40HX devices  | 0.88     | _        | ns    |

|                        |                                               | iCE40HX1K            | _        | 727      | ps    |

| t <sub>SKEW_GBUF</sub> | Global Buffer Clock Skew Within a Device      | iCE40HX4K            | _        | 300      | ps    |

|                        |                                               | iCE40HX8K            | _        | 300      | ps    |

| Pin-LUT-Pin Prop       | pagation Delay                                |                      | <b>'</b> | •        |       |

| t <sub>PD</sub>        | Best case propagation delay through one LUT-4 | All iCE40 HX devices | _        | 7.30     | ns    |

| General I/O Pin I      | Parameters (Using Global Buffer Clock witho   | ut PLL)              |          | •        | •     |

|                        |                                               | iCE40HX1K            | _        | 696      | ps    |

| t <sub>SKEW_IO</sub>   | Data bus skew across a bank of IOs            | iCE40HX4K            | _        | 290      | ps    |

|                        |                                               | iCE40HX8K            | _        | 290      | ps    |

|                        |                                               | iCE40HX1K            | _        | 5.00     | ns    |

| t <sub>CO</sub>        | Clock to Output - PIO Output Register         | iCE40HX4K            | _        | 5.41     | ns    |

|                        |                                               | iCE40HX8K            | _        | 5.41     | ns    |

|                        |                                               | iCE40HX1K            | -0.23    | _        | ns    |

| t <sub>SU</sub>        | Clock to Data Setup - PIO Input Register      | iCE40HX4K            | -0.43    | _        | ns    |

|                        |                                               | iCE40HX8K            | -0.43    | _        | ns    |

|                        |                                               | iCE40HX1K            | 1.92     | _        | ns    |

| t <sub>H</sub>         | Clock to Data Hold - PIO Input Register       | iCE40HX4K            | 2.38     | _        | ns    |

|                        |                                               | iCE40HX8K            | 2.38     | _        | ns    |

| General I/O Pin I      | Parameters (Using Global Buffer Clock with F  | PLL) <sup>3</sup>    | <b>'</b> | •        |       |

|                        |                                               | iCE40HX1K            | _        | 2.96     | ns    |

| t <sub>COPLL</sub>     | Clock to Output - PIO Output Register         | iCE40HX4K            | _        | 2.51     | ns    |

|                        |                                               | iCE40HX8K            | _        | 2.51     | ns    |

|                        |                                               | iCE40HX1K            | 3.10     | _        | ns    |

| t <sub>SUPLL</sub>     | Clock to Data Setup - PIO Input Register      | iCE40HX4K            | 4.16     | _        | ns    |

|                        |                                               | iCE40HX8K            | 4.16     | _        | ns    |

|                        |                                               | iCE40HX1K            | -0.60    | _        | ns    |

| t <sub>HPLL</sub>      | Clock to Data Hold - PIO Input Register       | iCE40HX4K            | -0.53    | _        | ns    |

| TH CC                  |                                               | iCE40HX8K            | -0.53    | <u> </u> | ns    |

<sup>1.</sup> Exact performance may vary with device and design implementation. Commercial timing numbers are shown at 85 °C and 1.14 V. Other operating conditions, including industrial, can be extracted from the iCECube2 software.

<sup>2.</sup> General I/O timing numbers based on LVCMOS 2.5, 0pf load.

<sup>3.</sup> Supported on devices with a PLL.

# SPI Master or NVCM Configuration Time<sup>1, 2</sup>

| Symbol              | Parameter                            | Conditions                             | Тур. | Units |

|---------------------|--------------------------------------|----------------------------------------|------|-------|

| <sup>†</sup> CONFIG | POR/CRESET_B to<br>Device I/O Active | iCE40LP384 - Low Frequency (Default)   | 25   | ms    |

|                     |                                      | iCE40LP384 - Medium Frequency          | 15   | ms    |

|                     |                                      | iCE40LP384 - High Frequency            | 11   | ms    |

|                     |                                      | iCE40LP640 - Low Frequency (Default)   | 53   | ms    |

|                     |                                      | iCE40LP640 - Medium Frequency          | 25   | ms    |

|                     |                                      | iCE40LP640 - High Frequency            | 13   | ms    |

|                     |                                      | iCE40LP/HX1K - Low Frequency (Default) | 53   | ms    |

|                     |                                      | iCE40LP/HX1K - Medium Frequency        | 25   | ms    |

|                     |                                      | iCE40LP/HX1K - High Frequency          | 13   | ms    |

|                     |                                      | iCE40LP/HX4K - Low Frequency (Default) | 230  | ms    |

|                     |                                      | iCE40LP/HX4K - Medium Frequency        | 110  | ms    |

|                     |                                      | iCE40LP/HX4K - High Frequency          | 70   | ms    |

|                     |                                      | iCE40LP/HX8K - Low Frequency (Default) | 230  | ms    |

|                     |                                      | iCE40LP/HX8K - Medium Frequency        | 110  | ms    |

|                     |                                      | iCE40LP/HX8K - High Frequency          | 70   | ms    |

<sup>1.</sup> Assumes sysMEM Block is initialized to an all zero pattern if they are used.

<sup>2.</sup> The NVCM download time is measured with a fast ramp rate starting from the maximum voltage of POR trip point.

# iCE40 LP/HX Family Data Sheet Ordering Information

March 2017 Data Sheet DS1040

# iCE40 Part Number Description

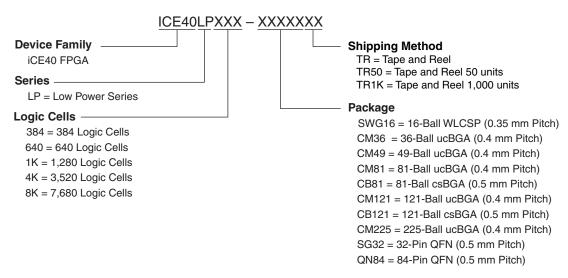

### **Ultra Low Power (LP) Devices**

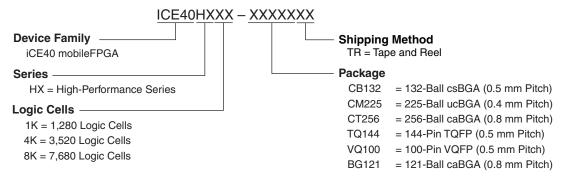

### **High Performance (HX) Devices**

All parts shipped in trays unless noted.

### Ordering Information

iCE40 devices have top-side markings as shown below:

### Industrial

Note: Markings are abbreviated for small packages.

© 2017 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging

| Part Number          | LUTs | Supply Voltage | Package            | Leads | Temp. |

|----------------------|------|----------------|--------------------|-------|-------|

| ICE40LP384-CM36      | 384  | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP384-CM36TR    | 384  | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP384-CM36TR1K  | 384  | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP384-CM49      | 384  | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP384-CM49TR    | 384  | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP384-CM49TR1K  | 384  | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP384-SG32      | 384  | 1.2 V          | Halogen-Free QFN   | 32    | IND   |

| ICE40LP384-SG32TR    | 384  | 1.2 V          | Halogen-Free QFN   | 32    | IND   |

| ICE40LP384-SG32TR1K  | 384  | 1.2 V          | Halogen-Free QFN   | 32    | IND   |

| ICE40LP640-SWG16TR   | 640  | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP640-SWG16TR50 | 640  | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP640-SWG16TR1K | 640  | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP1K-SWG16TR    | 1280 | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP1K-SWG16TR50  | 1280 | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP1K-SWG16TR1K  | 1280 | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP1K-CM36       | 1280 | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP1K-CM36TR     | 1280 | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP1K-CM36TR1K   | 1280 | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP1K-CM49       | 1280 | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP1K-CM49TR     | 1280 | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP1K-CM49TR1K   | 1280 | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP1K-CM81       | 1280 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP1K-CM81TR     | 1280 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP1K-CM81TR1K   | 1280 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP1K-CB81       | 1280 | 1.2 V          | Halogen-Free csBGA | 81    | IND   |

| ICE40LP1K-CB81TR     | 1280 | 1.2 V          | Halogen-Free csBGA | 81    | IND   |

| ICE40LP1K-CB81TR1K   | 1280 | 1.2 V          | Halogen-Free csBGA | 81    | IND   |

| ICE40LP1K-CM121      | 1280 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP1K-CM121TR    | 1280 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP1K-CM121TR1K  | 1280 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP1K-CB121      | 1280 | 1.2 V          | Halogen-Free csBGA | 121   | IND   |

| ICE40LP1K-QN84       | 1280 | 1.2 V          | Halogen-Free QFN   | 84    | IND   |

| ICE40LP4K-CM81       | 3520 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP4K-CM81TR     | 3520 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP4K-CM81TR1K   | 3520 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP4K-CM121      | 3520 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP4K-CM121TR    | 3520 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP4K-CM121TR1K  | 3520 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP4K-CM225      | 3520 | 1.2 V          | Halogen-Free ucBGA | 225   | IND   |

| ICE40LP8K-CM81       | 7680 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP8K-CM81TR     | 7680 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP8K-CM81TR1K   | 7680 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP8K-CM121      | 7680 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP8K-CM121TR    | 7680 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

# iCE40 LP/HX Family Data Sheet Revision History

March 2017 Data Sheet DS1040

| Date         | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

|--------------|---------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| March 2017   | 3.3     | Introduction                        | Updated Features section. Added 121-ball caBGA package for ICE40 HX4K/8K to Table 1-1, iCE40 Family Selection Guide.                                                                                                                                                                                                                      |                                                                                                                                        |

|              |         | Architecture                        | Updated PLB Blocks section. Changed "subtracters" to "subtractors" in the Carry Logic description.                                                                                                                                                                                                                                        |                                                                                                                                        |

|              |         |                                     | Updated Clock/Control Distribution Network section. Switched the "Clock Enable" and the "Reset" headings in Table 2-2, Global Buffer (GBUF) Connections to Programmable Logic Blocks.                                                                                                                                                     |                                                                                                                                        |

|              |         | Pinout Information                  | Updated Pin Information Summary section. Added BG121information under iCE40HX4K and iCE40HX8K.                                                                                                                                                                                                                                            |                                                                                                                                        |

|              |         | Ordering Information                | Updated iCE40 Part Number Description section. Added Shipping Method and BG121 package under High Performance (HX) Devices.                                                                                                                                                                                                               |                                                                                                                                        |

|              |         |                                     | Updated Ordering Information section. Added part numbers for BG121 under High-Performance Industrial Grade Devices, Halogen Free (RoHS) Packaging.                                                                                                                                                                                        |                                                                                                                                        |

|              |         | Supplemental<br>Information         | Corrected reference to "Package Diagrams Data Sheet".                                                                                                                                                                                                                                                                                     |                                                                                                                                        |

| October 2015 | 3.2     | 3.2                                 | Introduction                                                                                                                                                                                                                                                                                                                              | Updated Features section. Added footnote to 16 WLCSP Programmable I/O: Max Inputs (LVDS25) in Table 1-1, iCE40 Family Selection Guide. |

|              |         | DC and Switching                    | Updated sysCLOCK PLL Timing section. Changed t <sub>DT</sub> conditions.                                                                                                                                                                                                                                                                  |                                                                                                                                        |

|              |         | Characteristics                     | Updated Programming NVCM Supply Current – LP Devices section. Changed I <sub>PP_2V5</sub> and I <sub>CCIO</sub> , I <sub>CC_SPI</sub> units.                                                                                                                                                                                              |                                                                                                                                        |

| March 2015   | 3.1     | DC and Switching<br>Characteristics | Updated sysIO Single-Ended DC Electrical Characteristics section. Changed LVCMOS 3.3 and LVCMOS 2. 5 V <sub>OH</sub> Min. (V) from 0.5 to 0.4.                                                                                                                                                                                            |                                                                                                                                        |

| July 2014    | 3.0     | DC and Switching<br>Characteristics | Revised and/or added Typ. V <sub>CC</sub> data in the following sections.  — Static Supply Current – LP Devices  — Static Supply Current – HX Devices  — Programming NVCM Supply Current – LP Devices  — Programming NVCM Supply Current – HX Devices  In each section table, the footnote indicating Advanced device status was removed. |                                                                                                                                        |

|              |         | Pinout Information                  | Updated Pin Information Summary section. Added footnote 1 to CM49 under iCE40LP1K.                                                                                                                                                                                                                                                        |                                                                                                                                        |

| April 2014   | 02.9    | Ordering Information                | Changed "i" to "I" in part number description and ordering part numbers.                                                                                                                                                                                                                                                                  |                                                                                                                                        |

|              |         |                                     | Added part numbers to the Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging table.                                                                                                                                                                                                                                  |                                                                                                                                        |

| Date           | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|---------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2014  | 02.8    | Introduction                        | Updated Features section.  — Corrected standby power units.  — Included High Current LED Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |         |                                     | Updated Table 1-1, iCE40 Family Selection Guide. — Removed LP384 Programmable I/O for 81 ucBGA package.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |         | Architecture                        | Updated Supported Standards section. Added information on High Current LED drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                |         | DC and Switching<br>Characteristics | Corrected typos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |         |                                     | Added footnote to the Peak Startup Supply Current – LP Devices table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                |         | Ordering Information                | Updated part number description in the Ultra Low Power (LP) Devices section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                |         |                                     | Added part numbers to the Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging table.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| October 2013   | 02.7    | Introduction                        | Updated Features list and iCE40 Family Selection Guide table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                |         | Architecture                        | Revised iCE40-1K device to iCE40LP/HX1K device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |