Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | 48                                                                         |

| Number of Logic Elements/Cells | 384                                                                        |

| Total RAM Bits                 | -                                                                          |

| Number of I/O                  | 37                                                                         |

| Number of Gates                | -                                                                          |

| Voltage - Supply               | 1.14V ~ 1.26V                                                              |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 49-VFBGA                                                                   |

| Supplier Device Package        | 49-UCBGA (3x3)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/ice40lp384-cm49 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1-1. iCE40 Family Selection Guide (continued) | Table 1-1. | iCE40 Famil | y Selection | Guide | (continued) |

|-----------------------------------------------------|------------|-------------|-------------|-------|-------------|

|-----------------------------------------------------|------------|-------------|-------------|-------|-------------|

| 84 QFN                                    |       |  |                    |         |         |                    |         |         |

|-------------------------------------------|-------|--|--------------------|---------|---------|--------------------|---------|---------|

| (7 mm x 7 mm, 0.5 mm)                     | QN84  |  | 67(7) <sup>1</sup> |         |         |                    |         |         |

| 100 VQFP<br>(14 mm x 14 mm, 0.5 mm)       | VQ100 |  |                    |         |         | 72(9) <sup>1</sup> |         |         |

| 121 ucBGA<br>(5 mm x 5 mm, 0.4 mm)        | CM121 |  | 95(12)             | 93(13)  | 93(13)  |                    |         |         |

| 121 csBGA<br>(6 mm x 6 mm, 0.5 mm)        | CB121 |  | 92(12)             |         |         |                    |         |         |

| 121 caBGA<br>(9 mm x 9 mm, 0.8 mm)        | BG121 |  |                    |         |         |                    | 93(13)  | 93(13)  |

| 132 csBGA<br>(8 mm x 8 mm, 0.5 mm)        | CB132 |  |                    |         |         | 95(11)             | 95(12)  | 95(12)  |

| 144 TQFP<br>(20 mm x 20 mm, 0.5 mm)       | TQ144 |  |                    |         |         | 96(12)             | 107(14) |         |

| 225 ucBGA<br>(7 mm x 7 mm, 0.4 mm)        | CM225 |  |                    | 178(23) | 178(23) |                    |         | 178(23) |

| 256-ball caBGA<br>(14 mm x 14 mm, 0.8 mm) | CT256 |  |                    |         |         |                    |         | 206(26) |

- 1. No PLL available on the 16 WLCSP, 36 ucBGA, 81 csBGA, 84 QFN and 100 VQFP packages.

- 2. Only one PLL available on the 81 ucBGA package.

- 3. High Current I/Os only available on the 16 WLCSP package.

### Introduction

The iCE40 family of ultra-low power, non-volatile FPGAs has five devices with densities ranging from 384 to 7680 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic, these devices feature Embedded Block RAM (EBR), Non-volatile Configuration Memory (NVCM) and Phase Locked Loops (PLLs). These features allow the devices to be used in low-cost, high-volume consumer and system applications. Select packages offer High-Current drivers that are ideal to drive three white LEDs, or one RGB LED.

The iCE40 devices are fabricated on a 40 nm CMOS low power process. The device architecture has several features such as programmable low-swing differential I/Os and the ability to turn off on-chip PLLs dynamically. These features help manage static and dynamic power consumption, resulting in low static power for all members of the family. The iCE40 devices are available in two versions – ultra low power (LP) and high performance (HX) devices.

The iCE40 FPGAs are available in a broad range of advanced halogen-free packages ranging from the space saving 1.40x1.48 mm WLCSP to the PCB-friendly 20x20 mm TQFP. Table 1-1 shows the LUT densities, package and I/O options, along with other key parameters.

The iCE40 devices offer enhanced I/O features such as pull-up resistors. Pull-up features are controllable on a "per-pin" basis.

The iCE40 devices also provide flexible, reliable and secure configuration from on-chip NVCM. These devices can also configure themselves from external SPI Flash or be configured by an external master such as a CPU.

Lattice provides a variety of design tools that allow complex designs to be efficiently implemented using the iCE40 family of devices. Popular logic synthesis tools provide synthesis library support for iCE40. Lattice design tools use the synthesis tool output along with the user-specified preferences and constraints to place and route the design in the iCE40 device. These tools extract the timing from the routing and back-annotate it into the design for timing verification.

Lattice provides many pre-engineered IP (Intellectual Property) modules, including a number of reference designs, licensed free of charge, optimized for the iCE40 FPGA family. By using these configurable soft core IP cores as standardized blocks, users are free to concentrate on the unique aspects of their design, increasing their productivity.

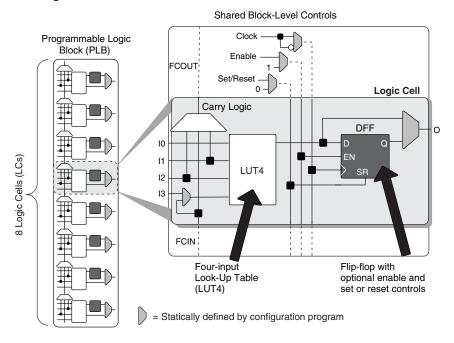

#### **PLB Blocks**

The core of the iCE40 device consists of Programmable Logic Blocks (PLB) which can be programmed to perform logic and arithmetic functions. Each PLB consists of eight interconnected Logic Cells (LC) as shown in Figure 2-2. Each LC contains one LUT and one register.

Figure 2-2. PLB Block Diagram

#### **Logic Cells**

Each Logic Cell includes three primary logic elements shown in Figure 2-2.

- A four-input Look-Up Table (LUT4) builds any combinational logic function, of any complexity, requiring up to four inputs. Similarly, the LUT4 element behaves as a 16x1 Read-Only Memory (ROM). Combine and cascade multiple LUT4s to create wider logic functions.

- A 'D'-style Flip-Flop (DFF), with an optional clock-enable and reset control input, builds sequential logic functions. Each DFF also connects to a global reset signal that is automatically asserted immediately following device configuration.

- Carry Logic boosts the logic efficiency and performance of arithmetic functions, including adders, subtractors, comparators, binary counters and some wide, cascaded logic functions.

Table 2-1. Logic Cell Signal Descriptions

| Function | Туре             | Signal Names           | Description                                                                                                          |

|----------|------------------|------------------------|----------------------------------------------------------------------------------------------------------------------|

| Input    | Data signal      | 10, 11, 12, 13         | Inputs to LUT4                                                                                                       |

| Input    | Control signal   | Enable                 | Clock enable shared by all LCs in the PLB                                                                            |

| Input    | Control signal   | Set/Reset <sup>1</sup> | Asynchronous or synchronous local set/reset shared by all LCs in the PLB.                                            |

| Input    | Control signal   | Clock                  | Clock one of the eight Global Buffers, or from the general-purpose interconnects fabric shared by all LCs in the PLB |

| Input    | Inter-PLB signal | FCIN                   | Fast carry in                                                                                                        |

| Output   | Data signals     | 0                      | LUT4 or registered output                                                                                            |

| Output   | Inter-PFU signal | FCOUT                  | Fast carry out                                                                                                       |

<sup>1.</sup> If Set/Reset is not used, then the flip-flop is never set/reset, except when cleared immediately after configuration.

#### Table 2-3. PLL Signal Descriptions

| Signal Name       | Direction | Description                                                                                                                                                                                 |

|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCECLK      | Input     | Input reference clock                                                                                                                                                                       |

| BYPASS            | Input     | When FEEDBACK_PATH is set to SIMPLE, the BYPASS control selects which clock signal connects to the PLLOUT output.                                                                           |

| DIFASS            | при       | 0 = PLL generated signal<br>1 = REFERENCECLK                                                                                                                                                |

| EXTFEEDBACK       | Input     | External feedback input to PLL. Enabled when the FEEDBACK_PATH attribute is set to EXTERNAL.                                                                                                |

| DYNAMICDELAY[3:0] | Input     | Fine delay adjustment control inputs. Enabled when DELAY_ADJUSTMENT_MODE is set to DYNAMIC.                                                                                                 |

| LATCHINPUTVALUE   | Input     | When enabled, forces the PLL into low-power mode; PLL output is held static at the last input clock value. Set ENABLE ICEGATE_PORTA and PORTB to '1' to enable.                             |

| PLLOUTGLOBAL      | Output    | Output from the Phase-Locked Loop (PLL). Drives a global clock network on the FPGA. The port has optimal connections to global clock buffers GBUF4 and GBUF5.                               |

| PLLOUTCORE        | Output    | Output clock generated by the PLL, drives regular FPGA routing. The frequency generated on this output is the same as the frequency of the clock signal generated on the PLLOUTLGOBAL port. |

| LOCK              | Output    | When High, indicates that the PLL output is phase aligned or locked to the input reference clock.                                                                                           |

| RESET             | Input     | Active low reset.                                                                                                                                                                           |

### sysMEM Embedded Block RAM Memory

Larger iCE40 device includes multiple high-speed synchronous sysMEM Embedded Block RAMs (EBRs), each 4 kbit in size. This memory can be used for a wide variety of purposes including data buffering, and FIFO.

#### sysMEM Memory Block

The sysMEM block can implement single port, pseudo dual port, or FIFO memories with programmable logic resources. Each block can be used in a variety of depths and widths as shown in Table 2-4.

Table 2-4. sysMEM Block Configurations<sup>1</sup>

| Block RAM<br>Configuration                                           | Block RAM<br>Configuration<br>and Size | WADDR Port<br>Size (Bits) | WDATA Port<br>Size (Bits) | RADDR Port<br>Size (Bits) | RDATA Port<br>Size (Bits) | MASK Port<br>Size (Bits) |

|----------------------------------------------------------------------|----------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|

| SB_RAM256x16<br>SB_RAM256x16NR<br>SB_RAM256x16NW<br>SB_RAM256x16NRNW | 256x16 (4K)                            | 8 [7:0]                   | 16 [15:0]                 | 8 [7:0]                   | 16 [15:0]                 | 16 [15:0]                |

| SB_RAM512x8<br>SB_RAM512x8NR<br>SB_RAM512x8NW<br>SB_RAM512x8NRNW     | 512x8 (4K)                             | 9 [8:0]                   | 8 [7:0]                   | 9 [8:0]                   | 8 [7:0]                   | No Mask Port             |

| SB_RAM1024x4<br>SB_RAM1024x4NR<br>SB_RAM1024x4NW<br>SB_RAM1024x4NRNW | 1024x4 (4K)                            | 10 [9:0]                  | 4 [3:0]                   | 10 [9:0]                  | 4 [3:0]                   | No Mask Port             |

| SB_RAM2048x2<br>SB_RAM2048x2NR<br>SB_RAM2048x2NW<br>SB_RAM2048x2NRNW | 2048x2 (4K)                            | 11 [10:0]                 | 2 [1:0]                   | 11 [10:0]                 | 2 [1:0]                   | No Mask Port             |

<sup>1.</sup> For iCE40 EBR primitives with a negative-edged Read or Write clock, the base primitive name is appended with a 'N' and a 'R' or 'W' depending on the clock that is affected.

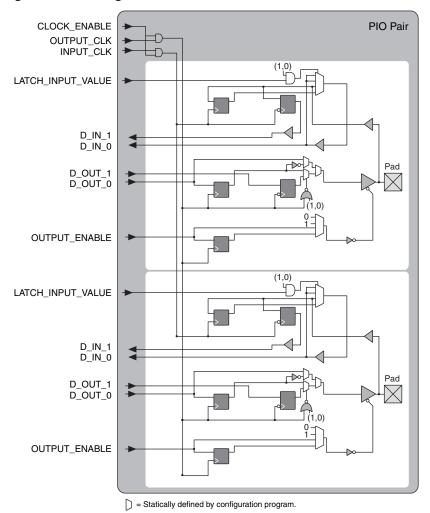

Figure 2-6. iCE I/O Register Block Diagram

Table 2-6. PIO Signal List

| Pin Name          | I/O Type | Description                   |

|-------------------|----------|-------------------------------|

| OUTPUT_CLK        | Input    | Output register clock         |

| CLOCK_ENABLE      | Input    | Clock enable                  |

| INPUT_CLK         | Input    | Input register clock          |

| OUTPUT_ENABLE     | Input    | Output enable                 |

| D_OUT_0/1         | Input    | Data from the core            |

| D_IN_0/1          | Output   | Data to the core              |

| LATCH_INPUT_VALUE | Input    | Latches/holds the Input Value |

### sysIO Buffer

Each I/O is associated with a flexible buffer referred to as a sysIO buffer. These buffers are arranged around the periphery of the device in groups referred to as banks. The sysIO buffers allow users to implement a wide variety of standards that are found in today's systems including LVCMOS and LVDS25.

High Current LED Drivers combine three sysIO buffers together. This allows for programmable drive strength. This also allows for high current drivers that are ideal to drive three white LEDs, or one RGB LED. Each bank is capable of supporting multiple I/O standards including single-ended LVCMOS buffers and differential LVDS25E output buf-

# Static Supply Current – HX Devices<sup>1, 2, 3, 4</sup>

| Symbol                          | Parameter                                                   | Device      | Typ. V <sub>CC</sub> ⁴ | Units |

|---------------------------------|-------------------------------------------------------------|-------------|------------------------|-------|

| Icc                             |                                                             | iCE40HX1K   | 296                    | μΑ    |

|                                 |                                                             | iCE40HX4K   | 1140                   | μΑ    |

|                                 |                                                             | iCE40HX8K   | 1140                   | μΑ    |

| I <sub>CCPLL</sub> <sup>5</sup> | PLL Power Supply                                            | All devices | 0.5                    | μΑ    |

| I <sub>PP_2V5</sub>             | NVCM Power Supply                                           | All devices | 1.0                    | μΑ    |

| Iccio, Icc_spi                  | Bank Power Supply <sup>4</sup><br>V <sub>CCIO</sub> = 2.5 V | All devices | 3.5                    | μΑ    |

Assumes blank pattern with the following characteristics: all outputs are tri-stated, all inputs are configured as LVCMOS and held at V<sub>CCIO</sub> or GND, on-chip PLL is off. For more detail with your specific design, use the Power Calculator tool. Power specified with master SPI configuration mode. Other modes may be up to 25% higher.

- 2. Frequency = 0 MHz.

- 3.  $T_J = 25$  °C, power supplies at nominal voltage.

- 4. Does not include pull-up.

- 5.  $V_{\mbox{\footnotesize CCPLL}}$  is tied to  $V_{\mbox{\footnotesize CC}}$  internally in packages without PLLs pins.

# Programming NVCM Supply Current – LP Devices<sup>1, 2, 3, 4</sup>

| Symbol                                            | Parameter          | Device      | Typ. V <sub>CC</sub> ⁵ | Units |

|---------------------------------------------------|--------------------|-------------|------------------------|-------|

| lcc                                               |                    | iCE40LP384  | 60                     | μΑ    |

|                                                   |                    | iCE40LP640  | 120                    | μΑ    |

|                                                   | Core Power Supply  | iCE40LP1K   | 120                    | μΑ    |

|                                                   |                    | iCE40LP4K   | 350                    | μΑ    |

|                                                   |                    | iCE40LP8K   | 350                    | μΑ    |

| I <sub>CCPLL</sub> <sup>6, 7</sup>                | PLL Power Supply   | All devices | 0.5                    | μΑ    |

| I <sub>PP_2V5</sub>                               | NVCM Power Supply  | All devices | 2.5                    | mA    |

| I <sub>CCIO<sup>8</sup>, I<sub>CC_SPI</sub></sub> | Bank Power Supply⁵ | All devices | 3.5                    | mA    |

- 1. Assumes all inputs are held at  $V_{\mbox{\scriptsize CCIO}}$  or GND and all outputs are tri-stated.

- 2. Typical user pattern.

- 3. SPI programming is at 8 MHz.

- 4.  $T_{.1} = 25$  °C, power supplies at nominal voltage.

- 5. Per bank.  $V_{CCIO} = 2.5 \text{ V}$ . Does not include pull-up.

- 6. No PLL available on the iCE40-LP384 and iCE40-LP640 device.

- 7.  $V_{\mbox{\footnotesize CCPLL}}$  is tied to  $V_{\mbox{\footnotesize CC}}$  internally in packages without PLLs pins.

- 8. V<sub>PP\_FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications, except CM36 and CM49 packages MUST have the V<sub>PP\_FAST</sub> ball connected to V<sub>CCIO\_0</sub> ball externally.

# Programming NVCM Supply Current – HX Devices<sup>1, 2, 3, 4</sup>

| Symbol                          | Parameter          | Device      | Typ. V <sub>CC</sub> ⁵ | Units |

|---------------------------------|--------------------|-------------|------------------------|-------|

|                                 |                    | iCE40HX1K   | 278                    | μΑ    |

| I <sub>CC</sub>                 | Core Power Supply  | iCE40HX4K   | 1174                   | μΑ    |

|                                 |                    | iCE40HX8K   | 1174                   | μΑ    |

| I <sub>CCPLL</sub> <sup>6</sup> | PLL Power Supply   | All devices | 0.5                    | μΑ    |

| I <sub>PP_2V5</sub>             | NVCM Power Supply  | All devices | 2.5                    | mA    |

| Iccio <sup>7</sup> , Icc spi    | Bank Power Supply⁵ | All devices | 3.5                    | mA    |

- 1. Assumes all inputs are held at V<sub>CCIO</sub> or GND and all outputs are tri-stated.

- 2. Typical user pattern.

- 3. SPI programming is at 8 MHz.

- 4.  $T_{J} = 25$  °C, power supplies at nominal voltage.

- 5. Per bank. V<sub>CCIO</sub> = 2.5 V. Does not include pull-up.

- 6.  $V_{CCPLL}$  is tied to  $V_{CC}$  internally in packages without PLLs pins.

- 7. V<sub>PP FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications.

# Peak Startup Supply Current – LP Devices

| Symbol                                              | Parameter               | Device     | Max  | Units |

|-----------------------------------------------------|-------------------------|------------|------|-------|

|                                                     |                         | iCE40LP384 | 7.7  | mA    |

|                                                     |                         | iCELP640   | 6.4  | mA    |

| I <sub>CCPEAK</sub>                                 | Core Power Supply       | iCE40LP1K  | 6.4  | mA    |

| ICCPEAK  ICCPLLPEAK  IPP_2V5PEAK  IPP_FASTPEAK  NVC |                         | iCE40LP4K  | 15.7 | mA    |

|                                                     |                         | iCE40LP8K  | 15.7 | mA    |

|                                                     |                         | iCE40LP1K  | 1.5  | mA    |

| CCPLLPEAK 1, 2, 4                                   | PLL Power Supply        | iCELP640   | 1.5  | mA    |

|                                                     | FLL Fower Supply        | iCE40LP4K  | 8.0  | mA    |

|                                                     |                         | iCE40LP8K  | 8.0  | mA    |

|                                                     |                         | iCE40LP384 | 3.0  | mA    |

|                                                     |                         | iCELP640   | 7.7  | mA    |

| I <sub>PP_2V5PEAK</sub>                             | NVCM Power Supply       | iCE40LP1K  | 7.7  | mA    |

|                                                     |                         | iCE40LP4K  | 4.2  | mA    |

|                                                     |                         | iCE40LP8K  | 4.2  | mA    |

|                                                     |                         | iCE40LP384 | 5.7  | mA    |

| I <sub>PP_FASTPEAK</sub> <sup>3</sup>               | NVCM Programming Supply | iCELP640   | 8.1  | mA    |

|                                                     |                         | iCE40LP1K  | 8.1  | mA    |

|                                                     |                         | iCE40LP384 | 8.4  | mA    |

|                                                     |                         | iCELP640   | 3.3  | mA    |

| ICCIOPEAK <sup>5</sup> , ICC_SPIPEAK                | Bank Power Supply       | iCE40LP1K  | 3.3  | mA    |

|                                                     |                         | iCE40LP4K  | 8.2  | mA    |

|                                                     |                         | iCE40LP8K  | 8.2  | mA    |

- 1. No PLL available on the iCE40LP384 and iCE40LP640 device.

- 2.  $V_{CCPLL}$  is tied to  $V_{CC}$  internally in packages without PLLs pins.

- 3. V<sub>PP\_FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications, except CM36 and CM49 packages MUST have the V<sub>PP\_FAST</sub> ball connected to V<sub>CCIO\_0</sub> ball externally.

- 4. While no PLL is available in the iCE40-LP640 the  $I_{CCPLLPEAK}$  is additive to  $I_{CCPEAK}$ .

- 5. iCE40LP384 requires  $V_{CC}$  to be greater than 0.7 V when  $V_{CCIO}$  and  $V_{CC\_SPI}$  are above GND.

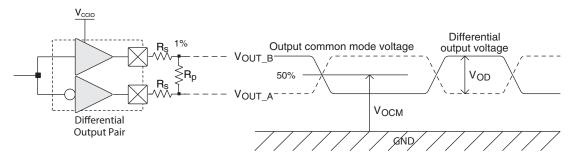

# sysIO Differential Electrical Characteristics

The LVDS25E/subLVDSE differential output buffers are available on all banks but the LVDS/subLVDS input buffers are only available on Bank 3 of iCE40 devices.

#### LVDS25

### **Over Recommended Operating Conditions**

| Parameter<br>Symbol   | Parameter Description        | Test Conditions             | Min.                         | Тур.                 | Max.                 | Units |

|-----------------------|------------------------------|-----------------------------|------------------------------|----------------------|----------------------|-------|

| $V_{INP}$ , $V_{INM}$ | Input Voltage                | $V_{\text{CCIO}}^{1} = 2.5$ | 0                            |                      | 2.5                  | V     |

| $V_{THD}$             | Differential Input Threshold |                             | 250                          | 350                  | 450                  | mV    |

| $V_{CM}$              | Input Common Mode Voltage    | $V_{CCIO}^{1} = 2.5$        | (V <sub>CCIO</sub> /2) - 0.3 | V <sub>CCIO</sub> /2 | $(V_{CCIO}/2) + 0.3$ | V     |

| I <sub>IN</sub>       | Input Current                | Power on                    |                              | 1                    | ±10                  | μΑ    |

<sup>1.</sup> Typical.

#### **subLVDS**

| Parameter<br>Symbol                | Parameter Description        | Test Conditions             | Min.                          | Тур.                 | Max.                  | Units |

|------------------------------------|------------------------------|-----------------------------|-------------------------------|----------------------|-----------------------|-------|

| V <sub>INP,</sub> V <sub>INM</sub> | Input Voltage                | $V_{\text{CCIO}}^{1} = 1.8$ | 0                             | _                    | 1.8                   | V     |

| $V_{THD}$                          | Differential Input Threshold |                             | 100                           | 150                  | 200                   | mV    |

| V <sub>CM</sub>                    | Input Common Mode Voltage    | $V_{\text{CCIO}}^{1} = 1.8$ | (V <sub>CCIO</sub> /2) - 0.25 | V <sub>CCIO</sub> /2 | $(V_{CCIO}/2) + 0.25$ | V     |

| I <sub>IN</sub>                    | Input Current                | Power on                    | _                             | _                    | ±10                   | μΑ    |

<sup>1.</sup> Typical.

### **SubLVDS Emulation**

The iCE40 family supports the differential subLVDS standard. The output standard is emulated using complementary LVCMOS outputs in conjunction with resistors across the driver outputs on all banks of the devices. The subLVDS input standard is supported by the LVDS25 differential input buffer. The scheme shown in Figure 3-2 is one possible solution for subLVDSE output standard implementation. Use LVDS25E mode with suggested resistors for subLVDSE operation. Resistor values in Figure 3-2 are industry standard values for 1% resistors.

Figure 3-2. subLVDSE

Table 3-2. subLVDSE DC Conditions

| Parameter         | Description                 | Тур.  | Units |

|-------------------|-----------------------------|-------|-------|

| Z <sub>OUT</sub>  | Output impedance            | 20    | Ohms  |

| R <sub>S</sub>    | Driver series resistor      | 270   | Ohms  |

| R <sub>P</sub>    | Driver parallel resistor    | 120   | Ohms  |

| R <sub>T</sub>    | Receiver termination        | 100   | Ohms  |

| V <sub>OH</sub>   | Output high voltage         | 1.43  | V     |

| V <sub>OL</sub>   | Output low voltage          | 1.07  | V     |

| $V_{OD}$          | Output differential voltage | 0.35  | V     |

| V <sub>CM</sub>   | Output common mode voltage  | 0.9   | V     |

| Z <sub>BACK</sub> | Back impedance              | 100.5 | Ohms  |

| I <sub>DC</sub>   | DC output current           | 2.8   | mA    |

# Typical Building Block Function Performance – LP Devices<sup>1, 2</sup>

## Pin-to-Pin Performance (LVCMOS25)

| Function        | Timing | Units |

|-----------------|--------|-------|

| Basic Functions |        | •     |

| 16-bit decoder  | 11.0   | ns    |

| 4:1 MUX         | 12.0   | ns    |

| 16:1 MUX        | 13.0   | ns    |

### **Register-to-Register Performance**

| Function                    | Timing | Units |  |  |  |  |

|-----------------------------|--------|-------|--|--|--|--|

| Basic Functions             |        |       |  |  |  |  |

| 16:1 MUX                    | 190    | MHz   |  |  |  |  |

| 16-bit adder                | 160    | MHz   |  |  |  |  |

| 16-bit counter              | 175    | MHz   |  |  |  |  |

| 64-bit counter              | 65     | MHz   |  |  |  |  |

| Embedded Memory Functions   | ·      | •     |  |  |  |  |

| 256x16 Pseudo-Dual Port RAM | 240    | MHz   |  |  |  |  |

The above timing numbers are generated using the iCECube2 design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

# Typical Building Block Function Performance – HX Devices<sup>1, 2</sup> Pin-to-Pin Performance (LVCMOS25)

| Function        | Timing | Units |

|-----------------|--------|-------|

| Basic Functions |        |       |

| 16-bit decoder  | 10.0   | ns    |

| 4:1 MUX         | 9.0    | ns    |

| 16:1 MUX        | 9.5    | ns    |

### **Register-to-Register Performance**

| Function                    | Timing | Units |  |  |  |  |

|-----------------------------|--------|-------|--|--|--|--|

| Basic Functions             | •      | ·     |  |  |  |  |

| 16:1 MUX                    | 305    | MHz   |  |  |  |  |

| 16-bit adder                | 220    | MHz   |  |  |  |  |

| 16-bit counter              | 255    | MHz   |  |  |  |  |

| 64-bit counter              | 105    | MHz   |  |  |  |  |

| Embedded Memory Functions   |        |       |  |  |  |  |

| 256x16 Pseudo-Dual Port RAM | 403    | MHz   |  |  |  |  |

<sup>1.</sup> The above timing numbers are generated using the iCECube2 design tool. Exact performance may vary with device and tool version. The tool uses internal parameters that have been characterized but are not tested on every device.

<sup>2.</sup> Using a  $V_{CC}$  of 1.14 V at Junction Temp 85 °C.

<sup>2.</sup> Using a  $V_{CC}$  of 1.14 V at Junction Temp 85 °C.

# iCE40 External Switching Characteristics – LP Devices 1,2

| Parameter              | Description                                   | Device               | Min.     | Max. | Units |

|------------------------|-----------------------------------------------|----------------------|----------|------|-------|

| Clocks                 | ·                                             |                      | •        |      | •     |

| Global Clocks          |                                               |                      |          |      |       |

| f <sub>MAX_GBUF</sub>  | Frequency for Global Buffer Clock network     | All iCE40LP devices  | _        | 275  | MHz   |

| t <sub>W_GBUF</sub>    | Clock Pulse Width for Global Buffer           | All iCE40LP devices  | 0.92     | _    | ns    |

|                        |                                               | iCE40LP384           | _        | 370  | ps    |

|                        |                                               | iCE40LP640           | _        | 230  | ps    |

| t <sub>SKEW_GBUF</sub> | Global Buffer Clock Skew Within a Device      | iCE40LP1K            | _        | 230  | ps    |

|                        |                                               | iCE40LP4K            | _        | 340  | ps    |

|                        |                                               | iCE40LP8K            | _        | 340  | ps    |

| Pin-LUT-Pin Propa      | ngation Delay                                 |                      | •        |      | •     |

| t <sub>PD</sub>        | Best case propagation delay through one LUT-4 | All iCE40LP devices  | _        | 9.36 | ns    |

| General I/O Pin Pa     | rameters (Using Global Buffer Clock withou    | it PLL) <sup>3</sup> | <b>"</b> |      |       |

|                        |                                               | iCE40LP384           |          | 300  | ps    |

|                        |                                               | iCE40LP640           | _        | 200  | ps    |

| t <sub>SKEW_IO</sub>   | Data bus skew across a bank of IOs            | iCE40LP1K            | _        | 200  | ps    |

|                        |                                               | iCE40LP4K            | _        | 280  | ps    |

|                        |                                               | iCE40LP8K            | _        | 280  | ps    |

|                        |                                               | iCE40LP384           | _        | 6.33 | ns    |

|                        |                                               | iCE40LP640           | _        | 5.91 | ns    |

| t <sub>CO</sub>        | Clock to Output - PIO Output Register         | iCE40LP1K            | _        | 5.91 | ns    |

|                        |                                               | iCE40LP4K            | _        | 6.58 | ns    |

|                        |                                               | iCE40LP8K            | _        | 6.58 | ns    |

|                        |                                               | iCE40LP384           | -0.08    | _    | ns    |

|                        |                                               | iCE40LP640           | -0.33    | _    | ns    |

| t <sub>SU</sub>        | Clock to Data Setup - PIO Input Register      | iCE40LP1K            | -0.33    |      | ns    |

|                        |                                               | iCE40LP4K            | -0.63    | _    | ns    |

|                        |                                               | iCE40LP8K            | -0.63    | _    | ns    |

|                        |                                               | iCE40LP384           | 1.99     | _    | ns    |

|                        |                                               | iCE40LP640           | 2.81     | _    | ns    |

| t <sub>H</sub>         | Clock to Data Hold - PIO Input Register       | iCE40LP1K            | 2.81     | _    | ns    |

|                        |                                               | iCE40LP4K            | 3.48     | _    | ns    |

|                        |                                               | iCE40LP8K            | 3.48     |      | ns    |

| General I/O Pin Pa     | rameters (Using Global Buffer Clock with P    | •                    |          |      |       |

|                        |                                               | iCE40LP1K            |          | 2.20 | ns    |

| t <sub>COPLL</sub>     | Clock to Output - PIO Output Register         | iCE40LP4K            |          | 2.30 | ns    |

|                        |                                               | iCE40LP8K            |          | 2.30 | ns    |

|                        |                                               | iCE40LP1K            | 5.23     | _    | ns    |

| t <sub>SUPLL</sub>     | Clock to Data Setup - PIO Input Register      | iCE40LP4K            | 6.13     | _    | ns    |

|                        |                                               | iCE40LP8K            | 6.13     | _    | ns    |

# iCE40 External Switching Characteristics – LP Devices (Continued)<sup>1, 2</sup>

| Parameter         | Description                             | Device    | Min.  | Max. | Units |

|-------------------|-----------------------------------------|-----------|-------|------|-------|

|                   |                                         | iCE40LP1K | -0.90 | _    | ns    |

| t <sub>HPLL</sub> | Clock to Data Hold - PIO Input Register | iCE40LP4K | -0.80 | _    | ns    |

|                   |                                         | iCE40LP8K | -0.80 | _    | ns    |

<sup>1.</sup> Exact performance may vary with device and design implementation. Commercial timing numbers are shown at 85 °C and 1.14 V. Other operating conditions can be extracted from the iCECube2 software.

<sup>2.</sup> General I/O timing numbers based on LVCMOS 2.5, 0pf load.

<sup>3.</sup> Supported on devices with a PLL.

# SPI Master or NVCM Configuration Time<sup>1, 2</sup>

| Symbol              | Parameter                         | Conditions                             | Тур. | Units |

|---------------------|-----------------------------------|----------------------------------------|------|-------|

|                     |                                   | iCE40LP384 - Low Frequency (Default)   | 25   | ms    |

|                     |                                   | iCE40LP384 - Medium Frequency          | 15   | ms    |

|                     |                                   | iCE40LP384 - High Frequency            | 11   | ms    |

|                     |                                   | iCE40LP640 - Low Frequency (Default)   | 53   | ms    |

|                     |                                   | iCE40LP640 - Medium Frequency          | 25   | ms    |

|                     |                                   | iCE40LP640 - High Frequency            | 13   | ms    |

|                     |                                   | iCE40LP/HX1K - Low Frequency (Default) | 53   | ms    |

| t <sub>CONFIG</sub> | POR/CRESET_B to Device I/O Active | iCE40LP/HX1K - Medium Frequency        | 25   | ms    |

|                     |                                   | iCE40LP/HX1K - High Frequency          | 13   | ms    |

|                     |                                   | iCE40LP/HX4K - Low Frequency (Default) | 230  | ms    |

|                     |                                   | iCE40LP/HX4K - Medium Frequency        | 110  | ms    |

|                     |                                   | iCE40LP/HX4K - High Frequency          | 70   | ms    |

|                     |                                   | iCE40LP/HX8K - Low Frequency (Default) | 230  | ms    |

|                     |                                   | iCE40LP/HX8K - Medium Frequency        | 110  | ms    |

|                     |                                   | iCE40LP/HX8K - High Frequency          | 70   | ms    |

<sup>1.</sup> Assumes sysMEM Block is initialized to an all zero pattern if they are used.

<sup>2.</sup> The NVCM download time is measured with a fast ramp rate starting from the maximum voltage of POR trip point.

# **Signal Descriptions (Continued)**

| Signal Name | I/O | Descriptions                                                                                                                                                                                                                                                         |

|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VPP_FAST    | _   | Optional fast NVCM programming supply. $V_{PP\_FAST}$ , used only for fast production programming, must be left floating or unconnected in applications, except CM36 and CM49 packages MUST have the $V_{PP\_FAST}$ ball connected to $V_{CCIO\_0}$ ball externally. |

| VPP_2V5     | _   | VPP_2V5 NVCM programming and operating supply                                                                                                                                                                                                                        |

# **Pin Information Summary**

|                                        | iCE40LP384 |                   | iCE40LP640        | iCE40LP1K |       |                      |                      |      |      |      |       |       |

|----------------------------------------|------------|-------------------|-------------------|-----------|-------|----------------------|----------------------|------|------|------|-------|-------|

|                                        | SG32       | CM36 <sup>2</sup> | CM49 <sup>2</sup> | SWG16     | SWG16 | CM36 <sup>1, 2</sup> | CM49 <sup>1, 2</sup> | CM81 | CB81 | QN84 | CM121 | CB121 |

| General Purpose I/O per Ban            | k          | I                 | I                 |           | 1     |                      |                      |      | I    | ı    | I     |       |

| Bank 0                                 | 6          | 4                 | 10                | 3         | 3     | 4                    | 10                   | 17   | 17   | 17   | 24    | 24    |

| Bank 1                                 | 5          | 7                 | 7                 | 0         | 0     | 7                    | 7                    | 15   | 16   | 17   | 25    | 21    |

| Bank 2                                 | 0          | 4                 | 4                 | 1         | 1     | 4                    | 4                    | 11   | 8    | 11   | 18    | 19    |

| Bank 3                                 | 6          | 6                 | 12                | 2         | 2     | 6                    | 10                   | 16   | 17   | 18   | 24    | 24    |

| Configuration                          | 4          | 4                 | 4                 | 4         | 4     | 4                    | 4                    | 4    | 4    | 4    | 4     | 4     |

| Total General Purpose Single Ended I/O | 21         | 25                | 37                | 10        | 10    | 25                   | 35                   | 63   | 62   | 67   | 95    | 92    |

| High Current Outputs per Ba            | nk         | 1                 | 1                 |           | ı     |                      | l .                  |      | 1    |      | I     |       |

| Bank 0                                 | 0          | 0                 | 0                 | 3         | 3     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Bank 1                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Bank 2                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Bank 3                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Total Current Outputs                  | 0          | 0                 | 0                 | 3         | 3     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Differential Inputs per Bank           |            | •                 | •                 |           | •     |                      |                      |      | •    | •    | •     |       |

| Bank 0                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Bank 1                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Bank 2                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Bank 3                                 | 3          | 3                 | 6                 | 1         | 1     | 3                    | 5                    | 8    | 9    | 7    | 12    | 12    |

| Total Differential Inputs              | 3          | 3                 | 6                 | 1         | 1     | 3                    | 5                    | 8    | 9    | 7    | 12    | 12    |

| Dedicated Inputs per Bank              |            | ı                 | ı                 |           |       |                      | l .                  |      | ı    |      | ı     |       |

| Bank 0                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Bank 1                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Bank 2                                 | 2          | 2                 | 2                 | 1         | 1     | 2                    | 2                    | 2    | 2    | 2    | 2     | 2     |

| Bank 3                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Configuration                          | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 0     |

| Total Dedicated Inputs                 | 2          | 2                 | 2                 | 1         | 1     | 2                    | 2                    | 2    | 2    | 2    | 2     | 2     |

| Vccio Pins                             |            | ı                 | ı                 |           |       |                      | l .                  |      | ı    |      | ı     |       |

| Bank 0                                 | 1          | 1                 | 1                 | 1         | 1     | 1                    | 1                    | 1    | 1    | 1    | 2     | 1     |

| Bank 1                                 | 1          | 1                 | 1                 | 0         | 0     | 0                    | 0                    | 1    | 1    | 1    | 2     | 1     |

| Bank 2                                 | 1          | 1                 | 1                 | 1         | 1     | 1                    | 1                    | 1    | 1    | 1    | 2     | 1     |

| Bank 3                                 | 1          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 1    | 1    | 1    | 2     | 2     |

| VCC                                    | 1          | 1                 | 2                 | 1         | 1     | 1                    | 2                    | 3    | 3    | 4    | 4     | 4     |

| VCC_SPI                                | 1          | 1                 | 1                 | 0         | 0     | 1                    | 1                    | 1    | 1    | 1    | 1     | 1     |

| VPP_2V5                                | 1          | 1                 | 1                 | 0         | 0     | 1                    | 1                    | 1    | 1    | 1    | 1     | 1     |

| VPP_FAST <sup>3</sup>                  | 0          | 0                 | 0                 | 0         | 0     | 1                    | 1                    | 1    | 0    | 1    | 1     | 1     |

| VCCPLL                                 | 0          | 0                 | 0                 | 0         | 0     | 0                    | 1                    | 1    | 0    | 0    | 1     | 1     |

| GND                                    | 2          | 3                 | 3                 | 2         | 2     | 3                    | 4                    | 5    | 8    | 4    | 8     | 11    |

| NC                                     | 0          | 0                 | 0                 | 0         | 0     | 0                    | 0                    | 0    | 0    | 0    | 0     | 3     |

| Total Count of Bonded Pins             | 32         | 36                | 49                | 16        | 16    | 36                   | 49                   | 81   | 81   | 84   | 121   | 121   |

V<sub>CCIO0</sub> and V<sub>CCIO1</sub> are connected together.

V<sub>CCIO2</sub> and V<sub>CCIO3</sub> are connected together.

V<sub>PP\_FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications, except CM36 and CM49 packages MUST have the V<sub>PP\_FAST</sub> ball connected to V<sub>CCIO\_0</sub> ball externally.

# **Pin Information Summary (Continued)**

| General Purpose I/O per B Bank 0 Bank 1 Bank 2 Bank 3 Configuration Total General Purpose Single Ended I/O High Current Outputs per Bank 0 | 17<br>15<br>9<br>18<br>4<br>63<br><b>Bank</b> | 23<br>21<br>19<br>26<br>4<br>93 | 46<br>42<br>40<br>46<br>4<br>178 | 17<br>15<br>9<br>18<br>4 | 23<br>21<br>19 | 46<br>42 | VQ100<br>19<br>19 | 24<br>25 | TQ144 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------|----------------------------------|--------------------------|----------------|----------|-------------------|----------|-------|

| Bank 0 Bank 1 Bank 2 Bank 3 Configuration Total General Purpose Single Ended I/O High Current Outputs per                                  | 17<br>15<br>9<br>18<br>4<br>63<br><b>Bank</b> | 21<br>19<br>26<br>4             | 42<br>40<br>46<br>4              | 15<br>9<br>18            | 21<br>19       | 42       |                   |          |       |

| Bank 1  Bank 2  Bank 3  Configuration  Total General Purpose Single Ended I/O  High Current Outputs per                                    | 15<br>9<br>18<br>4<br>63<br><b>Bank</b>       | 21<br>19<br>26<br>4             | 42<br>40<br>46<br>4              | 15<br>9<br>18            | 21<br>19       | 42       |                   |          |       |

| Bank 2 Bank 3 Configuration Total General Purpose Single Ended I/O High Current Outputs per                                                | 9<br>18<br>4<br>63<br><b>Bank</b>             | 19<br>26<br>4                   | 40<br>46<br>4                    | 9<br>18                  | 19             |          | 19                | 25       | OF.   |

| Bank 3  Configuration  Total General Purpose Single Ended I/O  High Current Outputs per                                                    | 18<br>4<br>63<br><b>Bank</b><br>0             | 26<br>4                         | 46                               | 18                       |                | 40       |                   |          | 25    |

| Configuration Total General Purpose Single Ended I/O High Current Outputs per                                                              | 4<br>63<br><b>Bank</b><br>0                   | 4                               | 4                                |                          | 1              | 40       | 12                | 20       | 20    |

| Total General Purpose<br>Single Ended I/O<br>High Current Outputs per                                                                      | 63<br><b>Bank</b>                             |                                 |                                  | 4                        | 26             | 46       | 18                | 22       | 24    |

| High Current Outputs per                                                                                                                   | Bank<br>0                                     | 93                              | 178                              |                          | 4              | 4        | 4                 | 4        | 4     |

|                                                                                                                                            | 0                                             |                                 |                                  | 63                       | 93             | 178      | 72                | 95       | 96    |

| Bank 0                                                                                                                                     |                                               |                                 |                                  |                          | •              | •        | •                 |          |       |

|                                                                                                                                            |                                               | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Bank 1                                                                                                                                     | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Bank 2                                                                                                                                     | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Bank 3                                                                                                                                     | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Total Differential Inputs                                                                                                                  | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Differential Inputs per Bar                                                                                                                | nk                                            |                                 |                                  |                          | •              |          | •                 | •        |       |

| Bank 0                                                                                                                                     | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Bank 1                                                                                                                                     | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Bank 2                                                                                                                                     | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Bank 3                                                                                                                                     | 9                                             | 13                              | 23                               | 9                        | 13             | 23       | 9                 | 11       | 12    |

| Total Differential Inputs                                                                                                                  | 9                                             | 13                              | 23                               | 9                        | 13             | 23       | 9                 | 11       | 12    |

| Dedicated Inputs per Bank                                                                                                                  | k                                             |                                 |                                  |                          |                | •        | •                 | •        |       |

| Bank 0                                                                                                                                     | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Bank 1                                                                                                                                     | 0                                             | 0                               | 1                                | 0                        | 0              | 1        | 0                 | 1        | 1     |

| Bank 2                                                                                                                                     | 2                                             | 2                               | 2                                | 2                        | 2              | 2        | 2                 | 2        | 2     |

| Bank 3                                                                                                                                     | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Configuration                                                                                                                              | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 0        | 0     |

| Total Dedicated Inputs                                                                                                                     | 2                                             | 2                               | 3                                | 2                        | 2              | 3        | 2                 | 3        | 3     |

| Vccio Pins                                                                                                                                 |                                               |                                 |                                  |                          | •              |          |                   |          |       |

| Bank 0                                                                                                                                     | 1                                             | 1                               | 3                                | 1                        | 1              | 3        | 2                 | 2        | 2     |

| Bank 1                                                                                                                                     | 1                                             | 1                               | 3                                | 1                        | 1              | 3        | 2                 | 2        | 2     |

| Bank 2                                                                                                                                     | 1                                             | 1                               | 3                                | 1                        | 1              | 3        | 2                 | 2        | 2     |

| Bank 3                                                                                                                                     | 1                                             | 2                               | 4                                | 1                        | 2              | 4        | 3                 | 3        | 2     |

| VCC                                                                                                                                        | 3                                             | 4                               | 8                                | 3                        | 4              | 8        | 4                 | 5        | 4     |

| VCC_SPI                                                                                                                                    | 1                                             | 1                               | 1                                | 1                        | 1              | 1        | 1                 | 1        | 1     |

| VPP_2V5                                                                                                                                    | 1                                             | 1                               | 1                                | 1                        | 1              | 1        | 1                 | 1        | 1     |

| VPP_FAST <sup>1</sup>                                                                                                                      | 1                                             | 1                               | 1                                | 1                        | 1              | 1        | 1                 | 1        | 1     |

| VCCPLL                                                                                                                                     | 1                                             | 2                               | 2                                | 1                        | 2              | 2        | 0                 | 1        | 1     |

| GND                                                                                                                                        | 5                                             | 12                              | 18                               | 5                        | 12             | 18       | 10                | 14       | 10    |

| NC                                                                                                                                         | 0                                             | 0                               | 0                                | 0                        | 0              | 0        | 0                 | 2        | 19    |

| Total Count of Bonded<br>Pins                                                                                                              | 81                                            | 121                             | 225                              | 81                       | 121            | 225      | 100               | 132      | 144   |

<sup>1.</sup> V<sub>PP\_FAST</sub>, used only for fast production programming, must be left floating or unconnected in applications.

# iCE40 LP/HX Family Data Sheet Ordering Information

March 2017 Data Sheet DS1040

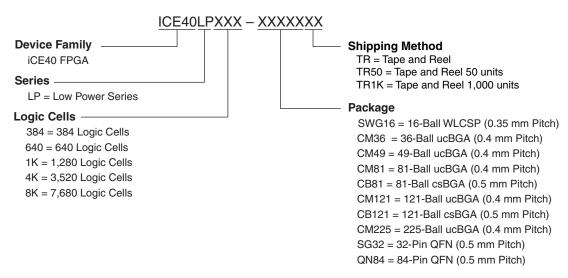

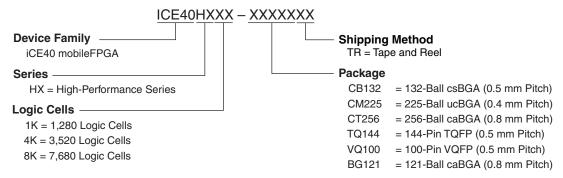

# iCE40 Part Number Description

### **Ultra Low Power (LP) Devices**

### **High Performance (HX) Devices**

All parts shipped in trays unless noted.

## Ordering Information

iCE40 devices have top-side markings as shown below:

#### Industrial

Note: Markings are abbreviated for small packages.

© 2017 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging

| Part Number          | LUTs | Supply Voltage | Package            | Leads | Temp. |

|----------------------|------|----------------|--------------------|-------|-------|

| ICE40LP384-CM36      | 384  | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP384-CM36TR    | 384  | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP384-CM36TR1K  | 384  | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP384-CM49      | 384  | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP384-CM49TR    | 384  | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP384-CM49TR1K  | 384  | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP384-SG32      | 384  | 1.2 V          | Halogen-Free QFN   | 32    | IND   |

| ICE40LP384-SG32TR    | 384  | 1.2 V          | Halogen-Free QFN   | 32    | IND   |

| ICE40LP384-SG32TR1K  | 384  | 1.2 V          | Halogen-Free QFN   | 32    | IND   |

| ICE40LP640-SWG16TR   | 640  | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP640-SWG16TR50 | 640  | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP640-SWG16TR1K | 640  | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP1K-SWG16TR    | 1280 | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP1K-SWG16TR50  | 1280 | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP1K-SWG16TR1K  | 1280 | 1.2 V          | Halogen-Free WLCSP | 16    | IND   |

| ICE40LP1K-CM36       | 1280 | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP1K-CM36TR     | 1280 | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP1K-CM36TR1K   | 1280 | 1.2 V          | Halogen-Free ucBGA | 36    | IND   |

| ICE40LP1K-CM49       | 1280 | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP1K-CM49TR     | 1280 | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP1K-CM49TR1K   | 1280 | 1.2 V          | Halogen-Free ucBGA | 49    | IND   |

| ICE40LP1K-CM81       | 1280 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP1K-CM81TR     | 1280 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP1K-CM81TR1K   | 1280 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP1K-CB81       | 1280 | 1.2 V          | Halogen-Free csBGA | 81    | IND   |

| ICE40LP1K-CB81TR     | 1280 | 1.2 V          | Halogen-Free csBGA | 81    | IND   |

| ICE40LP1K-CB81TR1K   | 1280 | 1.2 V          | Halogen-Free csBGA | 81    | IND   |

| ICE40LP1K-CM121      | 1280 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP1K-CM121TR    | 1280 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP1K-CM121TR1K  | 1280 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP1K-CB121      | 1280 | 1.2 V          | Halogen-Free csBGA | 121   | IND   |

| ICE40LP1K-QN84       | 1280 | 1.2 V          | Halogen-Free QFN   | 84    | IND   |

| ICE40LP4K-CM81       | 3520 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP4K-CM81TR     | 3520 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP4K-CM81TR1K   | 3520 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP4K-CM121      | 3520 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP4K-CM121TR    | 3520 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP4K-CM121TR1K  | 3520 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP4K-CM225      | 3520 | 1.2 V          | Halogen-Free ucBGA | 225   | IND   |

| ICE40LP8K-CM81       | 7680 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP8K-CM81TR     | 7680 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP8K-CM81TR1K   | 7680 | 1.2 V          | Halogen-Free ucBGA | 81    | IND   |

| ICE40LP8K-CM121      | 7680 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP8K-CM121TR    | 7680 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| Part Number         | LUTs | Supply Voltage | Package            | Leads | Temp. |

|---------------------|------|----------------|--------------------|-------|-------|

| ICE40LP8K-CM121TR1K | 7680 | 1.2 V          | Halogen-Free ucBGA | 121   | IND   |

| ICE40LP8K-CM225     | 7680 | 1.2 V          | Halogen-Free ucBGA | 225   | IND   |

# High-Performance Industrial Grade Devices, Halogen Free (RoHS) Packaging

| Part Number       | LUTs | Supply Voltage | Package            | Leads | Temp. |

|-------------------|------|----------------|--------------------|-------|-------|

| ICE40HX1K-CB132   | 1280 | 1.2 V          | Halogen-Free csBGA | 132   | IND   |

| ICE40HX1K-VQ100   | 1280 | 1.2 V          | Halogen-Free VQFP  | 100   | IND   |

| ICE40HX1K-TQ144   | 1280 | 1.2 V          | Halogen-Free TQFP  | 144   | IND   |

| ICE40HX4K-BG121   | 3520 | 1.2 V          | Halogen-Free caBGA | 121   | IND   |

| ICE40HX4K-BG121TR | 3520 | 1.2 V          | Halogen-Free caBGA | 121   | IND   |

| ICE40HX4K-CB132   | 3520 | 1.2 V          | Halogen-Free csBGA | 132   | IND   |

| ICE40HX4K-TQ144   | 3520 | 1.2 V          | Halogen-Free TQFP  | 144   | IND   |

| ICE40HX8K-BG121   | 7680 | 1.2 V          | Halogen-Free caBGA | 121   | IND   |

| ICE40HX8K-BG121TR | 7680 | 1.2 V          | Halogen-Free caBGA | 121   | IND   |

| ICE40HX8K-CB132   | 7680 | 1.2 V          | Halogen-Free csBGA | 132   | IND   |

| ICE40HX8K-CM225   | 7680 | 1.2 V          | Halogen-Free ucBGA | 225   | IND   |

| ICE40HX8K-CT256   | 7680 | 1.2 V          | Halogen-Free caBGA | 256   | IND   |

| Date                            | Version | Section                             | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------|---------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2014 02.8 Introduction |         | Introduction                        | Updated Features section.  — Corrected standby power units.  — Included High Current LED Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                 |         |                                     | Updated Table 1-1, iCE40 Family Selection Guide. — Removed LP384 Programmable I/O for 81 ucBGA package.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                 |         | Architecture                        | Updated Supported Standards section. Added information on High Current LED drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                 |         | DC and Switching                    | Corrected typos.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                 |         | Characteristics                     | Added footnote to the Peak Startup Supply Current – LP Devices table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                 |         | Ordering Information                | Updated part number description in the Ultra Low Power (LP) Devices section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                 |         |                                     | Added part numbers to the Ultra Low Power Industrial Grade Devices, Halogen Free (RoHS) Packaging table.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| October 2013                    | 02.7    | Introduction                        | Updated Features list and iCE40 Family Selection Guide table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |