#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                  |

| Core Size                  | 16/32-Bit                                                              |

| Speed                      | 41.78MHz                                                               |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                             |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 30                                                                     |

| Program Memory Size        | 126KB (63K x 16)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 8K x 32                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-VFQFN Exposed Pad, CSP                                              |

| Supplier Device Package    | 64-LFCSP-VQ (9x9)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7124bcpz126-rl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE OF CONTENTS

| Features                                       |

|------------------------------------------------|

| Applications1                                  |

| Functional Block Diagram1                      |

| Revision History                               |

| General Description                            |

| Specifications                                 |

| Timing Specifications9                         |

| Absolute Maximum Ratings14                     |

| ESD Caution14                                  |

| Pin Configurations and Function Descriptions15 |

| Typical Performance Characteristics            |

| Terminology                                    |

| ADC Specifications                             |

| DAC Specifications                             |

| Overview of the ARM7TDMI Core                  |

| Thumb Mode (T)                                 |

| Long Multiply (M)28                            |

| EmbeddedICE (I)                                |

| Exceptions                                     |

| ARM Registers                                  |

| Interrupt Latency                              |

| Memory Organization                            |

| Memory Access                                  |

| Flash/EE Memory                                |

| SRAM                                           |

| Memory Mapped Registers                        |

| ADC Circuit Overview                           |

| Transfer Function                              |

| Typical Operation                              |

| MMRs Interface                                 |

| Converter Operation                            |

| Driving the Analog Inputs                      |

| Calibration                                    |

| Temperature Sensor                             |

| Band Gap Reference                         | 45  |

|--------------------------------------------|-----|

| Nonvolatile Flash/EE Memory                |     |

| Programming                                |     |

| Flash/EE Memory Security                   |     |

| Flash/EE Control Interface                 |     |

| Execution Time from SRAM and Flash/EE      | 50  |

| Reset and Remap                            | 50  |

| Other Analog Peripherals                   | 53  |

| DAC                                        | 53  |

| Power Supply Monitor                       | 55  |

| Comparator                                 | 55  |

| Oscillator and PLL—Power Control           |     |

| Digital Peripheral                         | 60  |

| General-Purpose Input/Output               | 60  |

| Serial Port Mux                            | 62  |

| UART Serial Interface                      | 62  |

| Serial Peripheral Interface                | 68  |

| I <sup>2</sup> C                           |     |

| PWM General Overview                       | 80  |

| Programmable Logic Array (PLA)             | 83  |

| Processor Reference Peripherals            |     |

| Interrupt System                           |     |

| IRQ                                        |     |

| Fast Interrupt Request (FIQ)               |     |

| Vectored Interrupt Controller (VIC)        |     |

| Timers                                     |     |

| External Memory Interfacing                |     |

| Hardware Design Considerations             | 103 |

| Power Supplies                             |     |

| Grounding and Board Layout Recommendations |     |

| Clock Oscillator                           |     |

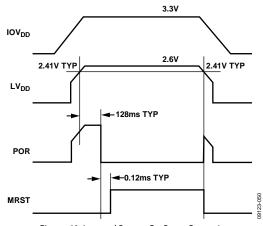

| Power-On Reset Operation                   | 105 |

| Outline Dimensions                         |     |

| Ordering Guide                             | 107 |

## **Data Sheet**

# ADuC7124/ADuC7126

| Parameter                              | Min    | Тур                     | Max                    | Unit    | Test Conditions/Comments                               |

|----------------------------------------|--------|-------------------------|------------------------|---------|--------------------------------------------------------|

| ANALOG OUTPUTS                         |        |                         |                        |         |                                                        |

| Output Voltage Range 0                 |        | 0 to DAC <sub>REF</sub> |                        | V       | DAC <sub>REF</sub> range: DACGND to DACV <sub>DD</sub> |

| Output Voltage Range 1                 |        | 0 to 2.5                |                        | V       |                                                        |

| Output Voltage Range 2                 |        | 0 to DACV <sub>DD</sub> |                        | V       |                                                        |

| Output Impedance                       |        | 0.5                     |                        | Ω       |                                                        |

| DAC IN OP AMP MODE                     |        |                         |                        |         |                                                        |

| DAC Output Buffer in Op Amp Mode       |        |                         |                        |         |                                                        |

| Input Offset Voltage                   |        | ±0.4                    |                        | mV      |                                                        |

| Input Offset Voltage Drift             |        | 4                       |                        | μV/°C   |                                                        |

| Input Offset Current                   |        | 2                       |                        | nA      |                                                        |

| Input Bias Current                     |        | 2.5                     |                        | nA      |                                                        |

| Gain                                   |        | 70                      |                        | dB      | 5 kΩ load                                              |

| Unity Gain Frequency                   |        | 4.5                     |                        | MHz     | $R_L = 5 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$     |

| CMRR                                   |        | 78                      |                        | dB      |                                                        |

| Settling Time                          |        | 12                      |                        | μs      | $R_L = 5 k\Omega$ , $C_L = 100 pF$                     |

| Output Slew Rate                       |        | 3.2                     |                        | V/µs    | $R_L = 5 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$     |

| PSRR                                   |        | 75                      |                        | dB      |                                                        |

| DAC AC CHARACTERISTICS                 |        |                         |                        |         |                                                        |

| Voltage Output Settling Time           |        | 10                      |                        | μs      |                                                        |

| Digital-to-Analog Glitch Energy        |        | ±10                     |                        | nV-sec  | 1 LSB change at major carry (where maximum             |

|                                        |        |                         |                        |         | number of bits simultaneously change in the            |

|                                        |        |                         |                        |         | DACxDAT register)                                      |

| COMPARATOR                             |        |                         |                        |         |                                                        |

| Input Offset Voltage                   |        | ±15                     |                        | mV      |                                                        |

| Input Bias Current                     |        | 1                       |                        | μA      |                                                        |

| Input Voltage Range                    | AGND   |                         | AV <sub>DD</sub> – 1.2 | V       |                                                        |

| Input Capacitance                      |        | 8.5                     |                        | рF      |                                                        |

| Hysteresis <sup>4, 6</sup>             | 2      |                         | 15                     | mV      | Hysteresis can be turned on or off via the             |

|                                        |        |                         |                        |         | CMPHYST bit in the CMPCON register                     |

| Response Time                          |        | 4                       |                        | μs      | 100 mV overdrive and configured with                   |

|                                        |        |                         |                        |         | CMPRES = 11                                            |

| TEMPERATURE SENSOR                     |        |                         |                        |         |                                                        |

| Voltage Output at 25°C                 |        | 1.415                   |                        | V       | ADuC7124                                               |

|                                        |        | 1.392                   |                        | V       | ADuC7126                                               |

| Voltage Temperature Coefficient        |        | 3.914                   |                        | mV/°C   | ADuC7124                                               |

|                                        |        | 4.52                    |                        | mV/°C   | ADuC7126                                               |

| Accuracy                               |        | ±3                      |                        | °C      | A single point calibration is required                 |

| $\theta_{JA}$ Thermal Impedance        |        |                         |                        |         |                                                        |

| 64-Lead LFCSP                          |        | 24                      |                        | °C/W    |                                                        |

| POWER SUPPLY MONITOR (PSM)             |        |                         |                        |         |                                                        |

| IOV <sub>DD</sub> Trip Point Selection |        | 2.79                    |                        | v       | Two selectable trip points                             |

|                                        |        | 3.07                    |                        | v       | we selectuale trip points                              |

| Power Supply Trip Point Accuracy       |        | ±2.5                    |                        | %       | Of the selected nominal trip point voltage             |

| POWER-ON RESET                         | -      | ±2.3<br>2.41            |                        | 90<br>V | or the selected normal trip point voltage              |

|                                        |        | 2.41                    |                        | v       |                                                        |

| WATCHDOG TIMER (WDT)                   |        |                         | F12                    |         |                                                        |

| Timeout Period                         | 0      |                         | 512                    | sec     |                                                        |

| FLASH/EE MEMORY                        |        |                         |                        |         |                                                        |

| Endurance <sup>9</sup>                 | 10,000 |                         |                        | Cycles  |                                                        |

| Data Retention <sup>10</sup>           | 20     |                         |                        | Years   | $T_J = 85^{\circ}C$                                    |

| DIGITAL INPUTS                         |        |                         |                        |         | All digital inputs excluding XCLKI and XCLKO           |

| Logic 1 Input Current                  |        | ±0.2                    | ±1                     | μΑ      | $V_{IH} = V_{DD} \text{ or } V_{IH} = 5 \text{ V}$     |

| Logic 0 Input Current                  |        | -40                     | -60                    | μΑ      | $V_{IL} = 0 V$ ; except TDI, TDO, and RTCK             |

|                                        |        | -80                     | -120                   | μA      | $V_{IL} = 0 V$ ; TDI, TDO, and RTCK                    |

| Input Capacitance                      |        | 5                       |                        | pF      |                                                        |

| Parameter                                          | Min  | Тур    | Max   | Unit | Test Conditions/Comments                             |

|----------------------------------------------------|------|--------|-------|------|------------------------------------------------------|

| LOGIC INPUTS <sup>3</sup>                          |      |        |       |      | All logic inputs excluding XCLKI                     |

| V <sub>INL</sub> , Input Low Voltage               |      |        | 0.8   | V    |                                                      |

| V <sub>INH</sub> , Input High Voltage              | 2.0  |        |       | V    |                                                      |

| LOGIC OUTPUTS                                      |      |        |       |      | All digital outputs excluding XCLKO                  |

| V <sub>он</sub> , Output High Voltage              | 2.4  |        |       | V    | $I_{\text{SOURCE}} = 1.6 \text{ mA}$                 |

| V <sub>oL</sub> , Output Low Voltage <sup>11</sup> |      |        | 0.4   | V    | I <sub>SINK</sub> = 1.6 mA                           |

| CRYSTAL INPUTS XCLKI and XCLKO                     |      |        |       |      |                                                      |

| Logic Inputs, XCLKI Only                           |      |        |       |      |                                                      |

| VINL, Input Low Voltage                            |      | 0.8    |       | V    |                                                      |

| V <sub>INH</sub> , Input High Voltage              |      | 1.6    |       | V    |                                                      |

| XCLKI Input Capacitance                            |      | 20     |       | pF   |                                                      |

| XCLKO Output Capacitance                           |      | 20     |       | pF   |                                                      |

| INTERNAL OSCILLATOR                                |      | 32.768 |       | kHz  |                                                      |

|                                                    |      |        | ±3    | %    |                                                      |

| MCU CLOCK RATE <sup>4</sup>                        |      |        |       |      |                                                      |

| From 32 kHz Internal Oscillator                    |      | 326    |       | kHz  | CD = 7                                               |

| From 32 kHz External Crystal                       |      | 41.78  |       | MHz  | CD = 0                                               |

| Using an External Clock                            | 0.05 |        | 44    | MHz  | $T_A = 85^{\circ}C$                                  |

|                                                    | 0.05 |        | 41.78 | MHz  | T <sub>A</sub> = 125°C                               |

| START-UP TIME                                      |      |        |       |      | Core clock = 41.78 MHz                               |

| At Power-On                                        |      | 66     |       | ms   |                                                      |

| From Pause/Nap Mode                                |      | 2.6    |       | μs   | CD = 0                                               |

| Hom Hube, hup mode                                 |      | 247    |       | μs   | CD = 7                                               |

| From Sleep Mode                                    |      | 1.58   |       | ms   |                                                      |

| From Stop Mode                                     |      | 1.7    |       | ms   |                                                      |

| PROGRAMMABLE LOGIC ARRAY (PLA)                     |      |        |       | 1115 |                                                      |

| Pin Propagation Delay                              |      | 12     |       | ns   | From input pin to output pin                         |

| Element Propagation Delay                          |      | 2.5    |       | ns   |                                                      |

| POWER REQUIREMENTS <sup>12, 13</sup>               |      | 2.5    |       | 115  |                                                      |

| Power Supply Voltage Range                         |      |        |       |      |                                                      |

| $AV_{DD}$ to AGND and IOV <sub>DD</sub> to IOGND   | 2.7  |        | 3.6   | V    |                                                      |

| Analog Power Supply Currents                       | 2.7  |        | 5.0   | v    |                                                      |

| AV <sub>DD</sub> Current                           |      | 165    |       | μA   | ADC in idle mode                                     |

| DACV <sub>DD</sub> Current <sup>14</sup>           |      | 0.02   |       | μΑ   | Abelindie mode                                       |

| Digital Power Supply Current                       |      | 0.02   |       | μ    |                                                      |

| IOV <sub>DD</sub> Current in Active Mode           |      |        |       |      | Code executing from Flash/EE                         |

| 10 Vbb current in Active Mode                      |      | 8.1    | 12.5  | mA   | CD = 7                                               |

|                                                    |      | 11.6   | 17    | mA   | CD = 3                                               |

|                                                    |      | 33.3   | 50    | mA   | CD = 0 (41.78 MHz clock)                             |

| IOV <sub>DD</sub> Current in Pause Mode            |      | 20.6   | 30    | mA   | CD = 0 (41.78 MHz clock)<br>CD = 0 (41.78 MHz clock) |

| IOV <sub>DD</sub> Current in Sleep Mode            |      | 110    | 50    | μΑ   | $T_A = 85^{\circ}C$                                  |

|                                                    |      | 600    | 680   | μΑ   | $T_A = 125^{\circ}C$                                 |

| Additional Power Supply Currents                   |      | 000    | 000   | μΛ   |                                                      |

| Additional Fower Supply Currents                   |      | 1.26   |       | mA   | At 1 MSPS                                            |

|                                                    |      | 0.7    |       | mA   | At 62.5 kSPS                                         |

| DAC                                                |      | 315    |       | μA   | Per DAC                                              |

## **Data Sheet**

## ADuC7124/ADuC7126

| Parameter          | Min | Тур | Max | Unit | Test Conditions/Comments             |

|--------------------|-----|-----|-----|------|--------------------------------------|

| ESD TESTS          |     |     |     |      | 2.5 V reference, $T_A = 25^{\circ}C$ |

| HBM Passed Up To   |     |     | 3   | kV   |                                      |

| FICDM Passed Up To |     |     | 1.5 | kV   |                                      |

<sup>1</sup> All ADC channel specifications are guaranteed during normal core operation.

<sup>2</sup> Apply to all ADC input channels.

<sup>3</sup> Measured using the factory-set default values in the ADC offset register (ADCOF) and gain coefficient register (ADCGN).

<sup>4</sup> Not production tested but supported by design and/or characterization data on production release.

<sup>5</sup> Measured using the factory-set default values in ADCOF and ADCGN with an external AD845 op amp as an input buffer stage as shown in Figure 37. Based on external ADC

system components, the user may need to execute a system calibration to remove external endpoint errors and achieve these specifications (see the Calibration section). <sup>6</sup> The input signal can be centered on any dc common-mode voltage (V<sub>CM</sub>) as long as this value is within the ADC voltage input range specified.

<sup>7</sup> DAC linearity is calculated using a reduced code range of 100 to 3995.

<sup>8</sup> DAC gain error is calculated using a reduced code range of 100 to internal 2.5 V V<sub>REF</sub>.

<sup>9</sup> Endurance is qualified as per JEDEC Standard 22 Method A117 and measured at -40°C, +25°C, +85°C, and +125°C.

<sup>10</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 85°C as per JEDEC Standard 22 Method A117. Retention lifetime derates with junction temperature.

<sup>11</sup> Test carried out with a maximum of eight I/Os set to a low output level.

<sup>12</sup> Power supply current consumption is measured in normal, pause, and sleep modes under the following conditions: normal mode with 3.6 V supply, pause mode with 3.6 V supply, and sleep mode with 3.6 V supply.

<sup>13</sup> IOV<sub>DD</sub> power supply current increases typically by 2 mA during a Flash/EE erase cycle.

<sup>14</sup> This current must be added to the AV<sub>DD</sub> current.

#### TIMING SPECIFICATIONS

#### I<sup>2</sup>C Timing

#### Table 2. I<sup>2</sup>C Timing in Fast Mode (400 kHz)

|                         |                                                              | S   | lave   | Master |      |

|-------------------------|--------------------------------------------------------------|-----|--------|--------|------|

| Parameter               | Description                                                  | Min | Max    | Тур    | Unit |

| tL                      | SCL low pulse width                                          | 200 |        | 1360   | ns   |

| t <sub>H</sub>          | SCL high pulse width                                         | 100 |        | 1140   | ns   |

| t <sub>shd</sub>        | Start condition hold time                                    | 300 |        |        | ns   |

| t <sub>DSU</sub>        | Data setup time                                              | 100 |        | 740    | ns   |

| <b>t</b> DHD            | Data hold time                                               | 0   |        | 400    | ns   |

| t <sub>RSU</sub>        | Setup time for repeated start                                | 100 |        |        | ns   |

| <b>t</b> <sub>PSU</sub> | Stop condition setup time                                    | 100 |        | 800    | ns   |

| tBUF                    | Bus-free time between a stop condition and a start condition | 1.3 |        |        | μs   |

| t <sub>R</sub>          | Rise time for both SCL and SDA                               |     | 300    | 200    | ns   |

| t <sub>F</sub>          | Fall time for both SCL and SDA                               |     | 300 ns |        |      |

#### Table 3. I<sup>2</sup>C Timing in Standard Mode (100 kHz)

|                  |                                                              |     | Slave |      |  |

|------------------|--------------------------------------------------------------|-----|-------|------|--|

| Parameter        | Description                                                  | Min | Max   | Unit |  |

| tL               | SCL low pulse width                                          | 4.7 |       | μs   |  |

| t <sub>H</sub>   | SCL high pulse width                                         | 4.0 |       | ns   |  |

| t <sub>SHD</sub> | Start condition hold time                                    | 4.0 |       | μs   |  |

| t <sub>DSU</sub> | Data setup time                                              | 250 |       | ns   |  |

| t <sub>DHD</sub> | Data hold time                                               | 0   | 3.45  | μs   |  |

| t <sub>RSU</sub> | Setup time for repeated start                                | 4.7 |       | μs   |  |

| t <sub>PSU</sub> | Stop condition setup time                                    | 4.0 |       | μs   |  |

| tBUF             | Bus-free time between a stop condition and a start condition | 4.7 |       | μs   |  |

| t <sub>R</sub>   | Rise time for both SCL and SDA                               |     | 1     | μs   |  |

| tF               | Fall time for both SCL and SDA                               |     | 300   | ns   |  |

| Parameter        | Description                                         | Min                        | Тур                            | Max  | Unit |

|------------------|-----------------------------------------------------|----------------------------|--------------------------------|------|------|

| t <sub>cs</sub>  | CS to SCLK edge                                     | 200                        |                                |      | ns   |

| t <sub>sL</sub>  | SCLK low pulse width                                |                            | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>sн</sub>  | SCLK high pulse width                               |                            | $(SPIDIV + 1) \times t_{HCLK}$ |      | ns   |

| t <sub>DAV</sub> | Data output valid after SCLK edge                   |                            |                                | 25   | ns   |

| t <sub>DSU</sub> | Data input setup time before SCLK edge <sup>1</sup> | $1 \times t_{UCLK}$        |                                |      | ns   |

| t <sub>DHD</sub> | Data input hold time after SCLK edge <sup>1</sup>   | $2 \times t_{\text{UCLK}}$ |                                |      | ns   |

| t <sub>DF</sub>  | Data output fall time                               |                            | 5                              | 12.5 | ns   |

| t <sub>DR</sub>  | Data output rise time                               |                            | 5                              | 12.5 | ns   |

| t <sub>sr</sub>  | SCLK rise time                                      |                            | 5                              | 12.5 | ns   |

| t <sub>sF</sub>  | SCLK fall time                                      |                            | 5                              | 12.5 | ns   |

| t <sub>SFS</sub> | CS high after SCLK edge                             | 0                          |                                |      | ns   |

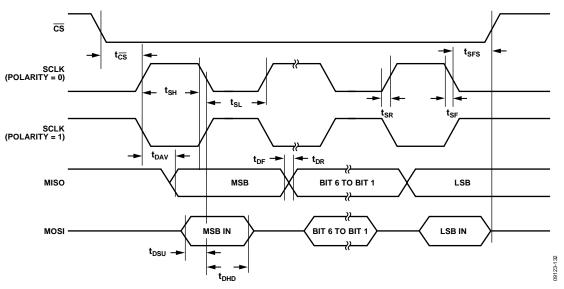

#### Table 6. SPI Slave Mode Timing (Phase Mode = 1)

$^{1}$  t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider.

## **Data Sheet**

| Pin No. | Mnemonic                          | Description                                                                                                                                                                                                 |

|---------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 62      | P1.1/SPM1/SOUT0/I2C0SDA/PLAI[1]   | General-Purpose Input and Output Port 1.1 (P1.1).<br>Serial Port Multiplexed (SPM1).<br>UARTO Output (SOUTO).<br>I2CO (I2COSDA).<br>Programmable Logic Array Input Element 1 (PLAI[1]).                     |

| 63      | P1.0/T1/SPM0/SIN0/I2C0SCL/PLAI[0] | General-Purpose Input and Output Port 1.0 (P1.0).<br>Timer1 Input (T1).<br>Serial Port Multiplexed (SPM0).<br>UART0 Input (SIN0).<br>I2C0 (I2C0SCL).<br>Programmable Logic Array Input Element 0 (PLAI[0]). |

| 64      | P4.2/AD10/PLAO[10]                | General-Purpose Input and Output Port 4.2 (P4.2).<br>External Memory Interface (AD10).<br>Programmable Logic Array Output Element 10 (PLAO[10]).                                                            |

| 65      | P4.3/AD11/PLAO[11]                | General-Purpose Input and Output Port 4.3 (P4.3).<br>External Memory Interface (AD11).<br>Programmable Logic Array Output Element 11 (PLAO[11]).                                                            |

| 66      | P4.4/AD12/PLAO[12]                | General-Purpose Input and Output Port 4.4 (P4.4).<br>External Memory Interface (AD12).<br>Programmable Logic Array Output Element 12 (PLAO[12]).                                                            |

| 67      | P4.5/AD13/PLAO[13]/RTCK           | General-Purpose Input and Output Port 4.5 (P4.5).<br>External Memory Interface (AD13).<br>Programmable Logic Array Output Element 13 (PLAO[13]).<br>JTAG Return Test Clock (RTCK).                          |

| 68      | IOV <sub>DD</sub>                 | 3.3 V Supply for GPIO and Input of the On-Chip Voltage Regulator.                                                                                                                                           |

| 69      | IOGND                             | Ground for GPIO. Typically connected to DGND.                                                                                                                                                               |

| 70      | V <sub>REF</sub>                  | 2.5 V Internal Voltage Reference. Must be connected to a 0.47 $\mu F$ capacitor when using the internal reference.                                                                                          |

| 71      | DAC <sub>REF</sub>                | External Voltage Reference for the DACs. Range: DACGND to DACV $_{DD}$ .                                                                                                                                    |

| 72      | AV <sub>DD</sub>                  | 3.3 V Analog Power.                                                                                                                                                                                         |

| 73, 74  | AGND                              | Analog Ground. Ground reference point for the analog circuitry.                                                                                                                                             |

| 75      | GND <sub>REF</sub>                | Ground Voltage Reference for the ADC. For optimal performance, the analog power supply should be separated from IOGND and DGND.                                                                             |

| 76      | ADC11                             | Single-Ended or Differential Analog Input 11.                                                                                                                                                               |

| 77      | ADC0                              | Single-Ended or Differential Analog Input 0.                                                                                                                                                                |

| 78      | ADC1                              | Single-Ended or Differential Analog Input 1.                                                                                                                                                                |

| 79      | ADC2/CMP0                         | Single-Ended or Differential Analog Input 2 (ADC2).<br>Comparator Positive Input (CMP0).                                                                                                                    |

| 80      | ADC3/CMP1                         | Single-Ended or Differential Analog Input 3 (ADC3).<br>Comparator Negative Input (CMP1).                                                                                                                    |

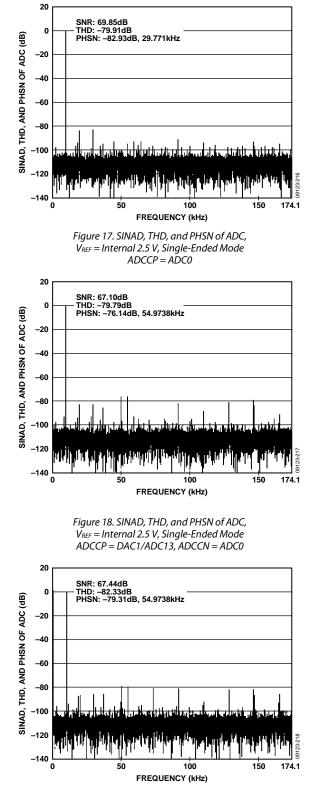

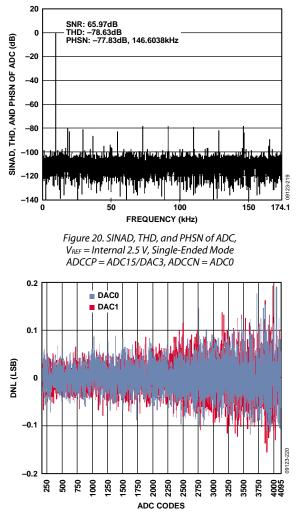

Figure 19. SINAD, THD, and PHSN of ADC,  $V_{REF}$  = Internal 2.5 V, Single-Ended Mode ADCCP = ADC8, ADCCN = ADC0

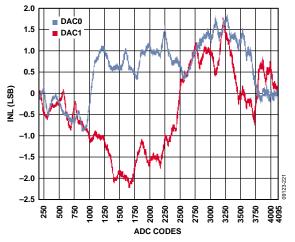

Figure 21. DAC DNL Error, DAC0 Max Positive DNL: 0.188951, DAC1 Max Positive DNL: 0.190343 DAC0 Max Negative DNL: -0.120081, DAC1 Max Negative DNL: -0.15697

Figure 22. DAC INL Error, DAC0 Max Positive INL: 1.84106, DAC1 Max Positive INL: 1.75312 DAC0 Max Negative INL: -0.887319, DAC1 Max Negative INL: -2.23708

### **ADCCN** Register

| Name:          | ADCCN      |

|----------------|------------|

| Address:       | 0xFFFF0508 |

| Default Value: | 0x01       |

| Access:        | Read/write |

|                |            |

ADCCN is an ADC negative channel selection register. This MMR is described in Table 32.

#### Table 32. ADCCN MMR Bit Designation

| Bit   | Value  | Description                      |

|-------|--------|----------------------------------|

| [7:5] |        | Reserved.                        |

| [4:0] |        | Negative channel selection bits. |

|       | 00000  | ADC0.                            |

|       | 00001  | ADC1.                            |

|       | 00010  | ADC2.                            |

|       | 00011  | ADC3.                            |

|       | 00100  | ADC4.                            |

|       | 00101  | ADC5.                            |

|       | 00110  | ADC6.                            |

|       | 00111  | ADC7.                            |

|       | 01000  | ADC8.                            |

|       | 01001  | ADC9.                            |

|       | 01010  | ADC10.                           |

|       | 01011  | ADC11.                           |

|       | 01100  | DAC0/ADC12.                      |

|       | 01101  | DAC1/ADC13.                      |

|       | 01110  | DAC2/ADC14.                      |

|       | 01111  | DAC3/ADC15.                      |

|       | 10000  | Reserved.                        |

|       | 10001  | AGND.                            |

|       | 10010  | Reserved.                        |

|       | 10011  | Reserved.                        |

|       | Others | Reserved.                        |

#### ADCSTA Register

| Name:          | ADCSTA     |

|----------------|------------|

| Address:       | 0xFFFF050C |

| Default Value: | 0x00       |

| Access:        | Read only  |

ADCSTA is an ADC status register that indicates when an ADC conversion result is ready. The ADCSTA register contains only one bit, ADCReady (Bit 0), representing the status of the ADC. This bit is set at the end of an ADC conversion, generating an ADC interrupt. It is cleared automatically by reading the ADCDAT MMR. When the ADC is performing a conversion, the status of the ADC can be read externally via the ADC<sub>BUSY</sub> pin. This pin is high during a conversion. When the conversion is finished, ADC<sub>BUSY</sub> goes back low. This information is available

on P0.5 (see the General-Purpose Input/Output section) if enabled in the ADCCON register.

### ADCDAT Register

| Name:          | ADCDAT     |

|----------------|------------|

| Address:       | 0xFFFF0510 |

| Default Value: | 0x00000000 |

| Access:        | Read only  |

ADCDAT is an ADC data result register that holds the 12-bit ADC result, as shown in Figure 30.

### ADCRST Register

| Name:          | ADCRST     |

|----------------|------------|

| Address:       | 0xFFFF0514 |

| Default Value: | 0x00       |

| Access:        | Read/write |

ADCRST resets the digital interface of the ADC. Writing any value to this register resets all the ADC registers to their default values.

#### **ADCGN** Register

| Name:          | ADCGN      |

|----------------|------------|

| Address:       | 0xFFFF0530 |

| Default Value: | 0x0200     |

| Access:        | Read/write |

ADCGN is a 10-bit gain calibration register.

#### **ADCOF** Register

| Name:          | ADCOF      |

|----------------|------------|

| Address:       | 0xFFFF0534 |

| Default Value: | 0x0200     |

| Access:        | Read/write |

ADCOF is a 10-bit offset calibration register.

## **CONVERTER OPERATION**

The ADC incorporates a successive approximation (SAR) architecture involving a charge-sampled input stage. This architecture can operate in three different modes: differential, pseudo differential, and single-ended.

#### **Differential Mode**

The ADuC7124/ADuC7126 each contains a successive approximation ADC based on two capacitive DACs. Figure 32 and Figure 33 show simplified schematics of the ADC in acquisition and conversion phases, respectively. The ADC comprises control logic, a SAR, and two capacitive DACs. In Figure 32 (the acquisition phase), SW3 is closed and SW1 and SW2 are in

## CALIBRATION

By default, the factory-set values written to the ADC offset (ADCOF) and gain coefficient registers (ADCGN) yield optimum performance in terms of end-point errors and linearity for standalone operation of the part (see the Specifications section). If system calibration is required, it is possible to modify the default offset and gain coefficients to improve endpoint errors, but note that any modification to the factory-set ADCOF and ADCGN values can degrade ADC linearity performance.

For system offset error correction, the ADC channel input stage must be tied to AGND. A continuous software ADC conversion loop must be implemented by modifying the value in ADCOF until the ADC result (ADCDAT) reads Code 0 to Code 1. If the ADCDAT value is greater than 1, ADCOF should be decremented until ADCDAT reads Code 0 to Code 1. Offset error correction is done digitally and has a resolution of 0.25 LSB and a range of  $\pm 3.125\%$  of V<sub>REF</sub>.

For system gain error correction, the ADC channel input stage must be tied to  $V_{REF}$ . A continuous software ADC conversion loop must be implemented to modify the value in ADCGN until the ADC result (ADCDAT) reads Code 4094 to Code 4095. If the ADCDAT value is less than 4094, ADCGN should be incremented until ADCDAT reads Code 4094 to Code 4095. Similar to the offset calibration, the gain calibration resolution is 0.25 LSB with a range of  $\pm 3\%$  of  $V_{REF}$ .

### **TEMPERATURE SENSOR**

The ADuC7124/ADuC7126 provide voltage outputs from an on-chip band gap reference that is proportional to absolute temperature. This voltage output can also be routed through the front-end ADC multiplexer (effectively, an additional ADC channel input), facilitating an internal temperature sensor channel, measuring die temperature.

An ADC temperature sensor conversion differs from a standard ADC voltage. The ADC performance specifications do not apply to the temperature sensor.

Chopping of the internal amplifier must be enabled using the TSCON register. To enable this mode, the user must set Bit 0 of TSCON. The user must also take two consecutive ADC readings and average them in this mode.

The ADCCON register must be configured to 0x37A3.

To calculate die temperature, use the following formula:

$$T - T_{REF} = (V_{ADC} - V_{TREF}) \times K$$

where:

*T* is the temperature result.

$T_{REF} = 25^{\circ}$ C.

For the ADuC7124,  $V_{TREF} = 1.415$  V and for the ADuC7126,  $V_{TREF} = 1.392$  V, which corresponds to  $T_{REF} = 25^{\circ}$ C, as described in Table 1.

$V_{ADC}$  is the average ADC result from two consecutive conversions.

*K* is the gain of the ADC in temperature sensor mode as determined by characterization data. K = 0.2555°C/mV for ADuC7124. K = 0.2212°C/mV for ADuC7126. This corresponds to the 1/voltage temperature coefficient specification from Table 1.

Using the default values from Table 1 and without any calibration, this equation becomes

$$T - 25^{\circ}\text{C} = (V_{ADC} - 1415) \times 0.2555 \text{ for ADuC7124}$$

$$T - 25^{\circ}\text{C} = (V_{ADC} - 1392) \times 0.2212$$

for ADuC7126

where  $V_{ADC}$  is in mV.

For better accuracy, the user should perform a single point calibration at a controlled temperature value.

For the calculation with no calibration, use 25°C and 1415 mV for the ADuC7124 and 1392mV for the ADuC7126. The idea of a single point calibration is to use other known ( $T_{REF}$ ,  $V_{TREF}$ ) values to replace the common T = 25°C and 1415 mV for the ADuC7124 and 1392 mV for the ADuC7126 for every part.

For some users, it is not possible to obtain such a known pair.

For such cases, the ADuC7124/ADuC7126 comes with a single point calibration value loaded in the TEMPREF register. For more details on this register, see Table 35. During production testing of the ADuC7124/ADuC7126, the TEMPREF register is loaded with an offset adjustment factor. Each part has a different value in the TEMPREF register. Using this single point calibration, the same formula is still used.

$$T - T_{REF} = (V_{ADC} - V_{TREF}) \times K$$

where:

$T_{REF}$  = 25°C but is not guaranteed.  $V_{TREF}$  can be calculated using the TEMPREF register.

#### **TSCON** Register

| Name:          | TSCON      |

|----------------|------------|

| Address:       | 0xFFFF0544 |

| Default Value: | 0x00       |

| Access:        | Read/write |

#### Table 34. TSCON MMR Bit Descriptions

| Bit   | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| [7:1] | Reserved.                                                                                       |

| 0     | Temperature sensor chop enable bit. This bit must be set.                                       |

|       | This bit is set to 1 to enable chopping of the internal amplifier to the ADC.                   |

|       | This bit is cleared to disable chopping. This results in incorrect temperature sensor readings. |

|       | This bit is cleared by default.                                                                 |

#### Table 56. FEE0PRO and FEE0HID MMR Bit Descriptions

| Bit    | Description                                                                                                                           |

|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| 31     | Read protection.                                                                                                                      |

|        | Cleared by the user to protect Block 0.                                                                                               |

|        | Set by the user to allow reading of Block 0.                                                                                          |

| [30:0] | Write protection for Page 123 to Page 0. Each bit protects protects a group of 4 pages.                                               |

|        | Cleared by the user to protect the pages when writing<br>to flash. Thus preventing an accidental write to specific<br>pages in flash. |

|        | Set by the user to allow writing to the pages.                                                                                        |

#### Table 57. FEE1PRO and FEE1HID MMR Bit Descriptions

| Bit    | Description                                                                                                                           |

|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| 31     | Read protection.                                                                                                                      |

|        | Cleared by the user to protect Block 1.                                                                                               |

|        | Set by the user to allow reading of Block 1.                                                                                          |

| 30     | Write protection for Page 127 to Page 120.                                                                                            |

|        | Cleared by the user to protect the pages when writing<br>to flash. Thus preventing an accidental write to specific<br>pages in flash. |

|        | Set by the user to allow writing to the pages.                                                                                        |

| [29:0] | Write protection for Page 119 to Page 116 and for Page 0 to Page 3.                                                                   |

|        | Cleared by the user to protect the pages in writing.                                                                                  |

|        | Set by the user to allow writing to the pages.                                                                                        |

#### **EXECUTION TIME FROM SRAM AND FLASH/EE**

This section describes SRAM and Flash/EE access times during execution for applications where execution time is critical.

#### **Execution from SRAM**

Fetching instructions from SRAM takes one clock cycle because the access time of the SRAM is 2 ns, and a clock cycle is 24 ns minimum. However, if the instruction involves reading or writing data to memory, one extra cycle must be added if the data is in SRAM (or three cycles if the data is in Flash/EE): one cycle to execute the instruction and two cycles to get the 32-bit data from Flash/EE. A control flow instruction (a branch instruction, for example) takes one cycle to fetch but also takes two cycles to fill the pipeline with the new instructions.

#### **Execution from Flash/EE**

Because the Flash/EE width is 16 bits and access time for 16-bit words is 22 ns, execution from Flash/EE cannot be done in one cycle (as can be done from SRAM when the CD bit = 0). Also, some dead times are needed before accessing data for any value of the CD bits.

In ARM mode, where instructions are 32 bits, two cycles are needed to fetch any instruction when CD = 0. In Thumb mode, where instructions are 16 bits, one cycle is needed to fetch any instruction.

Timing is identical in both modes when executing instructions that involve using the Flash/EE for data memory. If the instruction to be executed is a control flow instruction, an extra cycle is needed to decode the new address of the program counter, and then four cycles are needed to fill the pipeline. A data processing instruction involving only the core register does not require any extra clock cycles. However, if it involves data in Flash/EE, an extra clock cycle is needed to decode the address of the data, and two cycles are needed to get the 32-bit data from Flash/EE. An extra cycle must also be added before fetching another instruction. Data transfer instructions are more complex and are summarized in Table 58.

#### Table 58. Execution Cycles in ARM/Thumb Mode

| Instructions     | Fetch<br>Cvcles | Dead<br>Time   | Data Access                         | Dead<br>Time   |

|------------------|-----------------|----------------|-------------------------------------|----------------|

|                  | 2/1             | 1              | 2                                   | 1              |

| 20               | _, .            | 1              | 2                                   | 1              |

| LDH              | 2/1             |                |                                     |                |

| LDM/PUSH         | 2/1             | N <sup>2</sup> | $2 \times N^2$                      | N <sup>1</sup> |

| STR <sup>1</sup> | 2/1             | 1              | 2 × 20 ns                           | 1              |

| STRH             | 2/1             | 1              | 20 ns                               | 1              |

| STRM/POP         | 2/1             | $N^1$          | $2 \times N \times 20 \text{ ns}^1$ | $N^1$          |

<sup>1</sup> The SWAP instruction combines an LD and STR instruction with only one fetch, giving a total of eight cycles + 40 ns.

$^2$  N is the number of data bytes to load or store in the multiple load/store instruction (1 < N  $\leq$  16).

### **RESET AND REMAP**

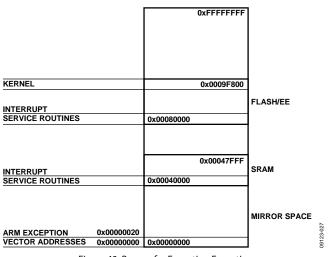

The ARM exception vectors are all situated at the bottom of the memory array, from Address 0x00000000 to Address 0x00000020, as shown in Figure 40.

Figure 40. Remap for Exception Execution

By default, and after any reset, the Flash/EE is mirrored at the bottom of the memory array. The remap function allows the programmer to mirror the SRAM at the bottom of the memory array, which facilitates execution of exception routines from SRAM instead of from Flash/EE. This means exceptions are executed twice as fast, being executed in 32-bit ARM mode with 32-bit wide SRAM instead of 16-bit wide Flash/EE memory.

### MMRs and Keys

Access:

The operating mode, clocking mode, and programmable clock divider are controlled via three MMRs, PLLCON (see Table 73), and POWCONx. PLLCON controls the operating mode of the clock system, POWCON0 controls the core clock frequency and the power-down mode, and POWCON1 controls the clock frequency to I<sup>2</sup>C and SPI.

#### Table 72. PLLKEYx Registers

| Name          | Address    | Default Value | Access |

|---------------|------------|---------------|--------|

| PLLKEY1       | 0xFFFF0410 | 0x0000        | W      |

| PLLKEY2       | 0xFFFF0418 | 0x0000        | W      |

| PLLCON Reg    | gister     |               |        |

| Name:         |            | PLLCON        |        |

| Address:      |            | 0xFFFF0414    |        |

| Default Value | 2:         | 0x21          |        |

|               |            |               |        |

Read/write

### Table 73. PLLCON MMR Bit Descriptions

| Bit   | Value | Name  | Description                                                           |

|-------|-------|-------|-----------------------------------------------------------------------|

| [7:6] |       |       | Reserved.                                                             |

| 5     |       | OSEL  | 32 kHz PLL input selection.<br>Set by the user to select the internal |

|       |       |       | 32 kHz oscillator. Set by default.                                    |

|       |       |       | Cleared by the user to select the external 32 kHz crystal.            |

| [4:2] |       |       | Reserved.                                                             |

| [1:0] |       | MDCLK | Clocking modes.                                                       |

|       | 00    |       | Reserved.                                                             |

|       | 01    |       | PLL. Default configuration.                                           |

|       | 10    |       | Reserved.                                                             |

|       | 11    |       | External clock on the P0.7 Pin.                                       |

To prevent accidental programming, a certain sequence must be followed to write to the PLLCON register. The PLLCON write sequence is as follows:

- 1. Write Code 0xAA to Register PLLKEY1.

- 2. Write user value to Register PLLCON.

- 3. Write Code 0x55 to Register PLLKEY2.

#### Table 74. POWKEYx Registers

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| POWKEY1 | 0xFFFF0404 | 0x0000        | W      |

| POWKEY2 | 0xFFFF040C | 0x0000        | W      |

POWKEY1 and POWKEY2 are used to prevent accidental programming to POWCON0.

#### **POWCON0** Register

| Name:          | POWCON0    |

|----------------|------------|

| Address:       | 0xFFFF0408 |

| Default Value: | 0x0003     |

| Access:        | Read/write |

#### Table 75. POWCON0 MMR Bit Descriptions

| Bit   | Value  | Name | Description                                               |

|-------|--------|------|-----------------------------------------------------------|

| 7     |        |      | Reserved.                                                 |

| [6:4] |        | PC   | Operating modes.                                          |

|       | 000    |      | Active mode.                                              |

|       | 001    |      | Pause mode.                                               |

|       | 010    |      | Nap mode.                                                 |

|       | 011    |      | Sleep mode. IRQ0 to IRQ3 and Timer2 can wake up the part. |

|       | 100    |      | Stop mode. IRQ0 to IRQ3 can wake up the part.             |

|       | Others |      | Reserved.                                                 |

| 3     |        |      | Reserved.                                                 |

| [2:0] |        | CD   | CPU clock divider bits.                                   |

|       | 000    |      | 41.78 MHz.                                                |

|       | 001    |      | 20.89 MHz.                                                |

|       | 010    |      | 10.44 MHz.                                                |

|       | 011    |      | 5.22 MHz.                                                 |

|       | 100    |      | 2.61 MHz.                                                 |

|       | 101    |      | 1.31 MHz.                                                 |

|       | 110    |      | 653 kHz.                                                  |

|       | 111    |      | 326 kHz.                                                  |

To prevent accidental programming, a certain sequence must be followed to write to the POWCONx register. The POWCON0 write sequence is as follows:

- 1. Write Code 0x01 to Register POWKEY1.

- 2. Write a user value to Register POWCON0.

- 3. Write Code 0xF4 to Register POWKEY2.

#### Table 76. POWKEYx Registers

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| POWKEY3 | 0xFFFF0434 | 0x0000        | W      |

| POWKEY4 | 0xFFFF043C | 0x0000        | W      |

POWKEY3 and POWKEY4 are used to prevent accidental programming to POWCON1.

#### **POWCON1** Register

| Name:          | POWCON1    |

|----------------|------------|

| Address:       | 0xFFFF0438 |

| Default Value: | 0x124      |

| Access:        | Read/write |

| COM1DIV0 Register                                                                                                                                                   |                             | COM0DIV1 Register                                                                |                                                  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------|--------------------------------------------------|--|

| Name:                                                                                                                                                               | COM1DIV0                    | Name:                                                                            | COM0DIV1                                         |  |

| Address:                                                                                                                                                            | 0xFFFF0740                  | Address:                                                                         | 0xFFFF0704                                       |  |

| Default Value:                                                                                                                                                      | 0x00                        | Default Value:                                                                   | 0x00                                             |  |

| Access:                                                                                                                                                             | Read/write                  | Access:                                                                          | Read/write                                       |  |

| COM1DIV0 is a low byte divisor latch for UART1. COM1TX,<br>COM1RX, and COM1DIV0 share the same address location.<br>COM1TX and COM1RX can be accessed when Bit 7 in |                             | COM0DIV1 is a divisor latch (high byte) register for UART0.<br>COM1DIV1 Register |                                                  |  |

| COM1CON0 register is cleared                                                                                                                                        | l. COM1DIV0 can be accessed | Name:                                                                            | COM1DIV1                                         |  |

| when Bit 7 of COM1CON0 is set.                                                                                                                                      |                             | Address:                                                                         | 0xFFFF0744                                       |  |

| COM0IEN0 Register                                                                                                                                                   | COMMENT                     | Default Value:                                                                   | 0x00                                             |  |

| Name:<br>Address:                                                                                                                                                   | COM0IEN0<br>0xFFFF0704      | Access:                                                                          | Read/write                                       |  |

| Default Value:                                                                                                                                                      | 0x00                        | COM1DIV1 is a divisor latch (l<br>COM0IID0 Register                              | high byte) register for UART1.                   |  |

| Access:                                                                                                                                                             | Read/write                  | Name:                                                                            | COM0IID0                                         |  |

| COM0IEN0 is the interrupt en                                                                                                                                        | able register for UART0.    | Address:                                                                         | 0xFFFF0708                                       |  |

| COM1IEN0 Register Name:                                                                                                                                             | COM1IEN0                    | Default Value:                                                                   | 0x01                                             |  |

| Address:                                                                                                                                                            | 0xFFFF0744                  | Access:                                                                          | Read only                                        |  |

| Default Value:                                                                                                                                                      | 0x00                        | COM0IID0 is the interrupt idea<br>also indicates if the UART is in               | ntification register for UART0. It<br>FIFO mode. |  |

| Access:                                                                                                                                                             | Read/write                  | COM1IID0 Register                                                                |                                                  |  |

|                                                                                                                                                                     |                             | News                                                                             | COMILIDA                                         |  |

COM1IEN0 is the interrupt enable register for UART1.

## Table 92. COMxIEN0 MMR Bit Descriptions

| Bit   | Name  | Description                                                                                                                                                                                                                                                                                                                                         |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4] |       | Reserved.                                                                                                                                                                                                                                                                                                                                           |

| 3     | EDSSI | Modem status interrupt enable bit.<br>Set by the user to enable generation of an<br>interrupt if any of COMXSTA1[3:1] are set.<br>Cleared by the user.                                                                                                                                                                                              |

| 2     | ELSI  | Rx status interrupt enable bit.<br>Set by the user to enable generation of an<br>interrupt if any of COMxSTA0[3:0] are set.<br>Cleared by the user.                                                                                                                                                                                                 |

| 1     | ETBEI | Enable transmit buffer empty interrupt.<br>Set by the user to enable interrupt when the<br>buffer is empty during a transmission.<br>Cleared by the user.                                                                                                                                                                                           |

| 0     | ERBFI | Enable receive buffer full interrupt.<br>In non-FIFO mode, set by the user to enable<br>an interrupt when buffer is full during a<br>reception. Cleared by the user.<br>In FIFO mode, set by the user to enable an<br>interrupt when trigger level is reached. It also<br>controls the character receive timeout<br>interrupt. Cleared by the user. |

| Address:                                                                                                | 0XFFFF0/04                   |

|---------------------------------------------------------------------------------------------------------|------------------------------|

| Default Value:                                                                                          | 0x00                         |

| Access:                                                                                                 | Read/write                   |

| COM0DIV1 is a divisor latch (hi                                                                         | igh byte) register for UART0 |

| COM1DIV1 Register                                                                                       |                              |

| Name:                                                                                                   | COM1DIV1                     |

| Address:                                                                                                | 0xFFFF0744                   |

| Default Value:                                                                                          | 0x00                         |

| Access:                                                                                                 | Read/write                   |

| COM1DIV1 is a divisor latch (hi                                                                         | igh byte) register for UART1 |

| COM0IID0 Register                                                                                       |                              |

| Name:                                                                                                   | COM0IID0                     |

| Address:                                                                                                | 0xFFFF0708                   |

| Default Value:                                                                                          | 0x01                         |

| Access:                                                                                                 | Read only                    |

| COM0IID0 is the interrupt identification register for UARTC also indicates if the UART is in FIFO mode. |                              |

| COM1IID0 Register                                                                                       |                              |

| Name:                                                                                                   | COM1IID0                     |

|                                                                                                         |                              |

| Address:       | 0xFFFF0748 |

|----------------|------------|

| Default Value: | 0x01       |

| Access:        | Read only  |

COM1IID0 is the interrupt identification register for UART1. It also indicates if the UART is in FIFO mode.

### **COM1CON0** Register

| Name:          | COM1CON0   |

|----------------|------------|

| Address:       | 0xFFFF074C |

| Default Value: | 0x00       |

| Access:        | Read/write |

COM1CON0 is the line control register for UART1.

### Table 95. COMxCON0 MMR Bit Descriptions

|      | Description                                                                                            |

|------|--------------------------------------------------------------------------------------------------------|

| DLAB | Divisor latch access.                                                                                  |

|      | Set by the user to enable access to the                                                                |

|      | COMxDIV0 and COMxDIV1 registers.                                                                       |

|      | Cleared by the user to disable access to                                                               |

|      | COMxDIV0 and COMxDIV1 and enable access to                                                             |

|      | COMxRX and COMxTX.                                                                                     |

| BRK  | Set break.                                                                                             |

|      | Set by the user to force SOUTx to 0.                                                                   |

|      | Cleared to operate in normal mode.                                                                     |

| SP   | Stick parity.                                                                                          |

|      | Set by the user to force parity to defined values:                                                     |

|      | 1 if $EPS = 1$ and $PEN = 1$ , 0 if $EPS = 0$ and $PEN = 1$ .                                          |

| EPS  | Even parity select bit.                                                                                |

|      | Set for even parity.                                                                                   |

|      | Cleared for odd parity.                                                                                |

| PEN  | Parity enable bit.                                                                                     |

|      | Set by the user to transmit and check the                                                              |

|      | parity bit.                                                                                            |

|      | Cleared by the user for no parity transmission or                                                      |

|      | checking.                                                                                              |

| Stop | Stop bit.                                                                                              |

|      | Set by the user to transmit 1 <sup>1</sup> / <sub>2</sub> stop bits if the word                        |

|      | length is five bits or two stop bits if the word<br>length is six bits, seven bits, or eight bits. The |

|      | receiver checks the first stop bit only, regardless                                                    |

|      | of the number of stop bits selected.                                                                   |

|      | Cleared by the user to generate one stop bit in                                                        |

|      | the transmitted data.                                                                                  |

| WLS  | Word length select:                                                                                    |

|      | 00 = five bits, $01 =$ six bits, $10 =$ seven bits, $11 =$                                             |

|      | eight bits.                                                                                            |

|      | BRK<br>SP<br>EPS<br>PEN<br>Stop                                                                        |

### COM0CON1 Register

| Name:          | COM0CON1   |

|----------------|------------|

| Address:       | 0xFFFF0710 |

| Default Value: | 0x00       |

| Access:        | Read/write |

COM0CON1 is the modem control register for UART0.

### COM1CON1 Register

| Name:          | COM1CON1   |

|----------------|------------|

| Address:       | 0xFFFF0750 |

| Default Value: | 0x00       |

| Access:        | Read/write |

COM1CON1 is the modem control register for UART1.

#### Table 96. COMxCON1 MMR Bit Descriptions

| Bit   | Name     | Description                                                                                                                                                                                                                                                                                                                                               |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5] |          | Reserved.                                                                                                                                                                                                                                                                                                                                                 |

| 4     | LOOPBACK | Loop back.<br>Set by the user to enable loopback mode.<br>In loopback mode, SOUTx is forced high.<br>The modem signals are also directly con-<br>nected to the status inputs (RTS to CTS and<br>DTR to DSR).<br>Cleared by the user to be in normal mode.                                                                                                 |