Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                |

| Core Size                  | 16/32-Bit                                                            |

| Speed                      | 41.78MHz                                                             |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                           |

| Peripherals                | POR, PWM, WDT                                                        |

| Number of I/O              | 40                                                                   |

| Program Memory Size        | 126KB (63K x 16)                                                     |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 8K x 32                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                          |

| Data Converters            | A/D 12x12b; D/A 4x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 80-LQFP                                                              |

| Supplier Device Package    | 80-LQFP (12x12)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7126bstz126i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **REVISION HISTORY**

## 10/14-Rev. C to Rev. D Changes to Features Section ......1 Changes to Pin 17 and Pin 30 Descriptions; Table 10.....19 Changes to Flash/EE Memory Section and SRAM Section......30 Changes to Flash/EE Memory Section, Programming Section, and Serial Downloading (In-Circuit Programming) Section ...46 Changes to Flash/EE Memory Security Section......47 Changes to Table 56 and Table 57 ......50 Changes to Table 69 ......56 Changes to Table 78 .....60 Update Table 109.....76 Changes to Table 110 ......77 Changes to T1CAP Register ......96 5/12-Rev. B to Rev. C

| Changed bit to byte in General Description Section      | 4   |

|---------------------------------------------------------|-----|

| Changes to Table 2 and Table 3                          | 8   |

| Changes to Table 4 and to Figure 2 and Figure 3         | 9   |

| Changes to Table 5 and Figure 4                         | 10  |

| Changes to Table 6 and Figure 5                         | 11  |

| Changes Table 7 and Figure 6                            | 12  |

| Changes to Pin 50 and Pin 51 in Table 9                 | 14  |

| Changes to Serial Downloading (In-Circuit Programming)  |     |

| Section                                                 | 44  |

| Changes to Table 77                                     | 59  |

| Changes to Table 78                                     | 58  |

| Changes to Table 90                                     | 60  |

| Changes to Normal 450 UART Baud Rate Generation         |     |

| Section                                                 | 61  |

| Changes to Serial Peripheral Interface Section          | 66  |

| Added equation to Timers Section and added Hr: Min: Sec |     |

| 1/128 Format Section                                    | 91  |

| Changes to Figure 69                                    | 103 |

| Updated Outline Dimensions                              | 104 |

| Changes to Ordering Guide                               | 105 |

|                                                         |     |

## 1/11-Rev A to Rev B

| Changes to Table 1 . | 5 |

|----------------------|---|

|                      |   |

## 10/10-Rev. 0 to Rev. A

| Added ADuC7126                                                         | Universal   |

|------------------------------------------------------------------------|-------------|

| Changes to Features Section                                            | 1           |

| Moved Figure 1                                                         | 1           |

| Changes to Figure 1                                                    | 1           |

| Changes to General Description Section                                 | 4           |

| Changes to Voltage Output at 25°C, Voltage TC, IOV                     | DD Current  |

| in Active Mode, and $\mathrm{IOV}_{\text{DD}}$ Current in Pause Mode F | Parameters, |

| Table 1                                                                | 5           |

| Change to Table 8                                                      | 13          |

| Changed REFGND to GND <sub>REF</sub>                                   | 13          |

| ADuC7 | 124/AE | )uC71 | 26 |

|-------|--------|-------|----|

|       |        |       |    |

| Changes to Figure 7 and Table 9                                                    | 14 |

|------------------------------------------------------------------------------------|----|

| Added Figure 8 and Table 10; Renumbered Sequentially                               | 18 |

| Change to Figure 17 Caption                                                        | 25 |

| Change to Memory Mapped Registers Section                                          | 29 |

| Change to Figure 26                                                                | 30 |

| Changes to Table 18                                                                | 32 |

| Changes to Table 21                                                                | 33 |

| Changes to Table 22                                                                | 34 |

| Moved Table 25                                                                     | 35 |

| Change to Table 25                                                                 | 35 |

| Added Table 26                                                                     |    |

| Change to Table 27                                                                 | 36 |

| Changes to Temperature Sensor Section                                              | 42 |

| Deleted Table 59; Renumbered Sequentially                                          | 43 |

| Added Downloading (In-Circuit Programming) via I <sup>2</sup>                      |    |

| C Section                                                                          | 44 |

| Change to JTAG Access Section and Table 37                                         |    |

| Changes to Table 45                                                                |    |

| Changes to RSTCFG Register Section                                                 |    |

| Deleted Table 72 and Table 75                                                      |    |

| Deleted Table 78                                                                   |    |

| Changes to DAC Section, Table 62, and Table 64                                     |    |

| Changes to References to ADC and the DACs Setion, Table 6                          |    |

| Configuring DAC Buffers in Op Amp Mode Section,                                    | ,  |

| DACBCFG Register Section, and Table 67                                             | 52 |

| Added DACBKEY1 Register Section and DACBKEY2 Regist                                |    |

| Section                                                                            |    |

| Changes to Table 69 and Figure 45                                                  |    |

| Changes to and External Crystal Selection and External Clo                         |    |

| Selection                                                                          |    |

| Changes to PLLCON Register and POWCON0 Register                                    |    |

| Section                                                                            | 56 |

| Changes to Table 78                                                                |    |

| Changes to Table 75                                                                |    |

| Changes to Table 84 and Table 90                                                   |    |

| Changes to Table 93, COM0FCR Register Section, COM1FC                              |    |

| Register Section, and Table 94                                                     |    |

| Changes to Serial Peripheral Interface Section                                     |    |

| Change to SPI Registers Section                                                    |    |

| 6 6                                                                                |    |

| Changes to SPIDIV Register Section and Table 101                                   |    |

| Change to I <sup>2</sup> C Master Transmit Register Section                        |    |

| Change to Table 109                                                                |    |

| Change to I <sup>2</sup> C Slave Status Registers Section                          |    |

| Change to Table 113                                                                |    |

| Changes to Table 114 Title and Figure 50                                           |    |

| Change to IRQCLRE Register Register                                                |    |

| Change to Figure 54                                                                |    |

| Changes to Table 141, T1CLRI Register Section, and T1CAP                           |    |

| Register Section                                                                   |    |

| Changes to Table 143                                                               |    |

|                                                                                    | 94 |

| Added External Memory Interfacting Section, Table 145,<br>Table 146, and Figure 57 |    |

# ADuC7124/ADuC7126

| Parameter                                          | Min  | Тур    | Max   | Unit | Test Conditions/Comments                             |

|----------------------------------------------------|------|--------|-------|------|------------------------------------------------------|

| LOGIC INPUTS <sup>3</sup>                          |      |        |       |      | All logic inputs excluding XCLKI                     |

| V <sub>INL</sub> , Input Low Voltage               |      |        | 0.8   | V    |                                                      |

| V <sub>INH</sub> , Input High Voltage              | 2.0  |        |       | V    |                                                      |

| LOGIC OUTPUTS                                      |      |        |       |      | All digital outputs excluding XCLKO                  |

| V <sub>он</sub> , Output High Voltage              | 2.4  |        |       | V    | $I_{\text{SOURCE}} = 1.6 \text{ mA}$                 |

| V <sub>oL</sub> , Output Low Voltage <sup>11</sup> |      |        | 0.4   | V    | I <sub>SINK</sub> = 1.6 mA                           |

| CRYSTAL INPUTS XCLKI and XCLKO                     |      |        |       |      |                                                      |

| Logic Inputs, XCLKI Only                           |      |        |       |      |                                                      |

| VINL, Input Low Voltage                            |      | 0.8    |       | V    |                                                      |

| V <sub>INH</sub> , Input High Voltage              |      | 1.6    |       | V    |                                                      |

| XCLKI Input Capacitance                            |      | 20     |       | pF   |                                                      |

| XCLKO Output Capacitance                           |      | 20     |       | pF   |                                                      |

| INTERNAL OSCILLATOR                                |      | 32.768 |       | kHz  |                                                      |

|                                                    |      |        | ±3    | %    |                                                      |

| MCU CLOCK RATE <sup>4</sup>                        |      |        |       |      |                                                      |

| From 32 kHz Internal Oscillator                    |      | 326    |       | kHz  | CD = 7                                               |

| From 32 kHz External Crystal                       |      | 41.78  |       | MHz  | CD = 0                                               |

| Using an External Clock                            | 0.05 |        | 44    | MHz  | $T_A = 85^{\circ}C$                                  |

|                                                    | 0.05 |        | 41.78 | MHz  | T <sub>A</sub> = 125°C                               |

| START-UP TIME                                      |      |        |       |      | Core clock = 41.78 MHz                               |

| At Power-On                                        |      | 66     |       | ms   |                                                      |

| From Pause/Nap Mode                                |      | 2.6    |       | μs   | CD = 0                                               |

| Hom Hube, hup mode                                 |      | 247    |       | μs   | CD = 7                                               |

| From Sleep Mode                                    |      | 1.58   |       | ms   |                                                      |

| From Stop Mode                                     |      | 1.7    |       | ms   |                                                      |

| PROGRAMMABLE LOGIC ARRAY (PLA)                     |      |        |       | 1115 |                                                      |

| Pin Propagation Delay                              |      | 12     |       | ns   | From input pin to output pin                         |

| Element Propagation Delay                          |      | 2.5    |       | ns   |                                                      |

| POWER REQUIREMENTS <sup>12, 13</sup>               |      | 2.5    |       | 115  |                                                      |

| Power Supply Voltage Range                         |      |        |       |      |                                                      |

| $AV_{DD}$ to AGND and IOV <sub>DD</sub> to IOGND   | 2.7  |        | 3.6   | V    |                                                      |

| Analog Power Supply Currents                       | 2.7  |        | 5.0   | v    |                                                      |

| AV <sub>DD</sub> Current                           |      | 165    |       | μA   | ADC in idle mode                                     |

| DACV <sub>DD</sub> Current <sup>14</sup>           |      | 0.02   |       | μΑ   | Abelindie mode                                       |

| Digital Power Supply Current                       |      | 0.02   |       | μ    |                                                      |

| IOV <sub>DD</sub> Current in Active Mode           |      |        |       |      | Code executing from Flash/EE                         |

| 10 Vbb current in Active Mode                      |      | 8.1    | 12.5  | mA   | CD = 7                                               |

|                                                    |      | 11.6   | 17    | mA   | CD = 3                                               |

|                                                    |      | 33.3   | 50    | mA   | CD = 0 (41.78 MHz clock)                             |

| IOV <sub>DD</sub> Current in Pause Mode            |      | 20.6   | 30    | mA   | CD = 0 (41.78 MHz clock)<br>CD = 0 (41.78 MHz clock) |

| IOV <sub>DD</sub> Current in Sleep Mode            |      | 110    | 50    | μΑ   | $T_A = 85^{\circ}C$                                  |

|                                                    |      | 600    | 680   | μΑ   | $T_A = 125^{\circ}C$                                 |

| Additional Power Supply Currents                   |      | 000    | 000   | μΛ   |                                                      |

| Additional Fower Supply Currents                   |      | 1.26   |       | mA   | At 1 MSPS                                            |

|                                                    |      | 0.7    |       | mA   | At 62.5 kSPS                                         |

| DAC                                                |      | 315    |       | μA   | Per DAC                                              |

## **Data Sheet**

## ADuC7124/ADuC7126

| Parameter          | Min | Тур | Max | Unit | Test Conditions/Comments             |

|--------------------|-----|-----|-----|------|--------------------------------------|

| ESD TESTS          |     |     |     |      | 2.5 V reference, $T_A = 25^{\circ}C$ |

| HBM Passed Up To   |     |     | 3   | kV   |                                      |

| FICDM Passed Up To |     |     | 1.5 | kV   |                                      |

<sup>1</sup> All ADC channel specifications are guaranteed during normal core operation.

<sup>2</sup> Apply to all ADC input channels.

<sup>3</sup> Measured using the factory-set default values in the ADC offset register (ADCOF) and gain coefficient register (ADCGN).

<sup>4</sup> Not production tested but supported by design and/or characterization data on production release.

<sup>5</sup> Measured using the factory-set default values in ADCOF and ADCGN with an external AD845 op amp as an input buffer stage as shown in Figure 37. Based on external ADC

system components, the user may need to execute a system calibration to remove external endpoint errors and achieve these specifications (see the Calibration section). <sup>6</sup> The input signal can be centered on any dc common-mode voltage (V<sub>CM</sub>) as long as this value is within the ADC voltage input range specified.

<sup>7</sup> DAC linearity is calculated using a reduced code range of 100 to 3995.

<sup>8</sup> DAC gain error is calculated using a reduced code range of 100 to internal 2.5 V V<sub>REF</sub>.

<sup>9</sup> Endurance is qualified as per JEDEC Standard 22 Method A117 and measured at -40°C, +25°C, +85°C, and +125°C.

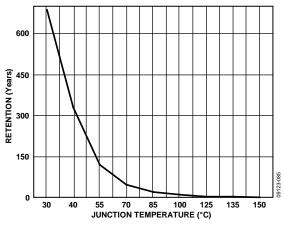

<sup>10</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 85°C as per JEDEC Standard 22 Method A117. Retention lifetime derates with junction temperature.

<sup>11</sup> Test carried out with a maximum of eight I/Os set to a low output level.

<sup>12</sup> Power supply current consumption is measured in normal, pause, and sleep modes under the following conditions: normal mode with 3.6 V supply, pause mode with 3.6 V supply, and sleep mode with 3.6 V supply.

<sup>13</sup> IOV<sub>DD</sub> power supply current increases typically by 2 mA during a Flash/EE erase cycle.

<sup>14</sup> This current must be added to the AV<sub>DD</sub> current.

#### TIMING SPECIFICATIONS

#### I<sup>2</sup>C Timing

#### Table 2. I<sup>2</sup>C Timing in Fast Mode (400 kHz)

|                         |                                                              | S   | lave | Master |      |

|-------------------------|--------------------------------------------------------------|-----|------|--------|------|

| Parameter               | Description                                                  | Min | Max  | Тур    | Unit |

| tL                      | SCL low pulse width                                          | 200 |      | 1360   | ns   |

| t <sub>H</sub>          | SCL high pulse width                                         | 100 |      | 1140   | ns   |

| t <sub>shd</sub>        | Start condition hold time                                    | 300 |      |        | ns   |

| t <sub>DSU</sub>        | Data setup time                                              | 100 |      | 740    | ns   |

| t <sub>DHD</sub>        | Data hold time                                               | 0   |      | 400    | ns   |

| t <sub>RSU</sub>        | Setup time for repeated start                                | 100 |      |        | ns   |

| <b>t</b> <sub>PSU</sub> | Stop condition setup time                                    | 100 |      | 800    | ns   |

| tBUF                    | Bus-free time between a stop condition and a start condition | 1.3 |      |        | μs   |

| t <sub>R</sub>          | Rise time for both SCL and SDA                               |     | 300  | 200    | ns   |

| t <sub>F</sub>          | Fall time for both SCL and SDA                               |     | 300  |        | ns   |

#### Table 3. I<sup>2</sup>C Timing in Standard Mode (100 kHz)

|                  |                                                              |     | Slave |      |  |

|------------------|--------------------------------------------------------------|-----|-------|------|--|

| Parameter        | Description                                                  | Min | Max   | Unit |  |

| tL               | SCL low pulse width                                          | 4.7 |       | μs   |  |

| t <sub>H</sub>   | SCL high pulse width                                         | 4.0 |       | ns   |  |

| t <sub>SHD</sub> | Start condition hold time                                    | 4.0 |       | μs   |  |

| t <sub>DSU</sub> | Data setup time                                              | 250 |       | ns   |  |

| t <sub>DHD</sub> | Data hold time                                               | 0   | 3.45  | μs   |  |

| t <sub>RSU</sub> | Setup time for repeated start                                | 4.7 |       | μs   |  |

| t <sub>PSU</sub> | Stop condition setup time                                    | 4.0 |       | μs   |  |

| tBUF             | Bus-free time between a stop condition and a start condition | 4.7 |       | μs   |  |

| t <sub>R</sub>   | Rise time for both SCL and SDA                               |     | 1     | μs   |  |

| tF               | Fall time for both SCL and SDA                               |     | 300   | ns   |  |

## **OVERVIEW OF THE ARM7TDMI CORE**

The ARM7° core is a 32-bit reduced instruction set computer (RISC). It uses a single 32-bit bus for instruction and data. The length of the data can be eight bits, 16 bits, or 32 bits. The length of the instruction word is 32 bits.

The ARM7TDMI is an ARM7 core with four additional features.

- T support for the Thumb<sup>®</sup> (16-bit) instruction set.

- D support for debug.

- M support for long multiplications.

- I includes the EmbeddedICE module to support embedded system debugging.

## THUMB MODE (T)

An ARM instruction is 32 bits long. The ARM7TDMI processor supports a second instruction set that has been compressed into 16 bits, called the Thumb instruction set. Faster execution from 16-bit memory and greater code density can usually be achieved by using the Thumb instruction set instead of the ARM instruction set, which makes the ARM7TDMI core particularly suitable for embedded applications.

However, the Thumb mode has two limitations:

- Thumb code typically requires more instructions for the same job. As a result, ARM code is usually best for maximizing the performance of time-critical code.

- The Thumb instruction set does not include some of the instructions needed for exception handling, which automatically switches the core to ARM code for exception handling.

See the ARM7TDMI user guide for details on the core architecture, the programming model, and both the ARM and ARM Thumb instruction sets.

## LONG MULTIPLY (M)

The ARM7TDMI instruction set includes four extra instructions that perform 32-bit by 32-bit multiplication with a 64-bit result and 32-bit by 32-bit multiplication-accumulation (MAC) with a 64-bit result. These results are achieved in fewer cycles than required on a standard ARM7 core.

## EmbeddedICE (I)

EmbeddedICE provides integrated on-chip support for the core. The EmbeddedICE module contains the breakpoint and watchpoint registers that allow code to be halted for debugging purposes. These registers are controlled through the JTAG test port.

When a breakpoint or watchpoint is encountered, the processor halts and enters debug state. Once in a debug state, the processor registers can be inspected as well as the Flash/EE, SRAM, and memory mapped registers.

## EXCEPTIONS

ARM supports five types of exceptions and a privileged processing mode for each type. The five types of exceptions are

- Normal interrupt or IRQ. This is provided to service general-purpose interrupt handling of internal and external events.

- Fast interrupt or FIQ. This is provided to service data transfers or communication channels with low latency. FIQ has priority over IRQ.

- Memory abort.

- Attempted execution of an undefined instruction.

- Software interrupt instruction (SWI). This can be used to make a call to an operating system.

Typically, the programmer defines an interrupt as IRQ, but for higher priority interrupt, that is, faster response time, the programmer can define an interrupt as FIQ.

## **ARM REGISTERS**

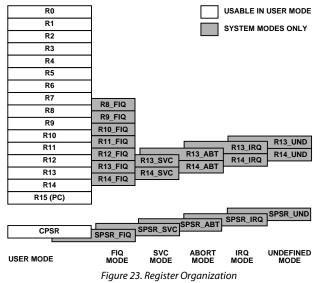

ARM7TDMI has a total of 37 registers: 31 general-purpose registers and six status registers. Each operating mode has dedicated banked registers.

When writing user-level programs, 15 general-purpose, 32-bit registers (R0 to R14), the program counter (R15), and the current program status register (CPSR) are usable. The remaining registers are only used for system-level programming and exception handling.

When an exception occurs, some of the standard registers are replaced with registers specific to the exception mode. All exception modes have replacement banked registers for the stack pointer (R13) and the link register (R14), as represented in Figure 23. The fast interrupt mode has more registers (R8 to R12) for fast interrupt processing. This means that the interrupt processing can begin without the need to save or restore these registers, and therefore, save critical time in the interrupt handling process.

## ADC CIRCUIT OVERVIEW

The analog-to-digital converter is a fast, multichannel, 12-bit ADC. It can operate from 2.7 V to 3.6 V supplies and is capable of providing a throughput of up to 1 MSPS when the clock source is 41.78 MHz. This block provides the user with a multichannel multiplexer, a differential track-and-hold, an on-chip reference, and an ADC.

The ADC consists of a 12-bit successive approximation converter based around two capacitor DACs. Depending on the input signal configuration, the ADC can operate in one of three different modes.

- Fully differential mode, for small and balanced signals

- Single-ended mode, for any single-ended signals

- Pseudo differential mode, for any single-ended signals, taking advantage of the common-mode rejection offered by the pseudo differential input

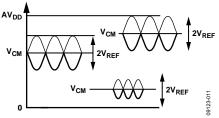

The converter accepts an analog input range of 0 V to  $V_{REF}$  when operating in single-ended or pseudo differential mode. In fully differential mode, the input signal must be balanced around a common-mode voltage ( $V_{CM}$ ) in the 0 V to AV<sub>DD</sub> range with a maximum amplitude of 2 ×  $V_{REF}$  (see Figure 27).

Figure 27. Examples of Balanced Signals in Fully Differential Mode

A high precision, low drift, factory calibrated, 2.5 V reference is provided on chip. An external reference can also be connected as described in the Band Gap Reference section.

Single or continuous conversion modes can be initiated in the software. An external  $CONV_{START}$  pin, an output generated from the on-chip PLA, or a Timer0 or Timer1 overflow can also be used to generate a repetitive trigger for ADC conversions.

A voltage output from an on-chip band gap reference proportional to absolute temperature can also be routed through the front-end ADC multiplexer, effectively an additional ADC channel input. This facilitates an internal temperature sensor channel that measures die temperature.

## TRANSFER FUNCTION

#### Pseudo Differential and Single-Ended Modes

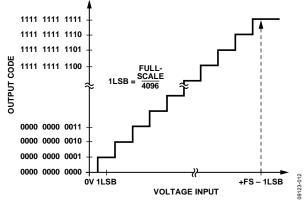

In pseudo differential or single-ended mode, the input range is 0 V to  $V_{REF}$ . The output coding is straight binary in pseudo differential and single-ended modes with

1 LSB = *Full-Scale*/4096, or 2.5 V/4096 = 0.61 mV, or 610  $\mu$ V when *V<sub>REF</sub>* = 2.5 V The ideal code transitions occur midway between successive integer LSB values (that is, ½ LSB, 3/2 LSB, 5/2 LSB, ..., FS – 3/2 LSB). The ideal input/output transfer characteristic is shown in Figure 28.

Figure 28. ADC Transfer Function in Pseudo Differential or Single-Ended Mode

### **Fully Differential Mode**

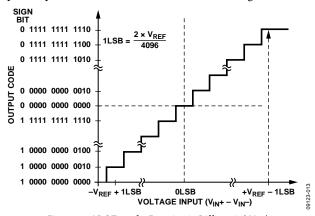

The amplitude of the differential signal is the difference between the signals applied to the V<sub>IN+</sub> and V<sub>IN-</sub> pins (that is, V<sub>IN+</sub> – V<sub>IN-</sub>). V<sub>IN+</sub> is selected by the ADCCP register, and V<sub>IN-</sub> is selected by the ADCCN register. The maximum amplitude of the differential signal is, therefore,  $-V_{REF}$  to  $+V_{REF}$  p-p (that is,  $2 \times V_{REF}$ ). This is regardless of the common mode (CM). The common mode is the average of the two signals, for example,  $(V_{IN+} + V_{IN-})/2$ , and is, therefore, the voltage that the two inputs are centered on. This results in the span of each input being CM ± V<sub>REF</sub>/2. This voltage must be set up externally, and its range varies with V<sub>REF</sub> (see the Driving the Analog Inputs section).

The output coding is twos complement in fully differential mode with 1 LSB =  $2 \times V_{REF}/4096$ , or  $2 \times 2.5 V/4096 = 1.22 mV$  when  $V_{REF} = 2.5 V$ . The output result is ±11 bits, but this is shifted by one to the right. This allows the result in ADCDAT to be declared as a signed integer when writing C code. The designed code transitions occur midway between successive integer LSB values (that is, ½ LSB, 3/2 LSB, 5/2 LSB, ..., FS – 3/2 LSB). The ideal input/output transfer characteristic is shown in Figure 29.

## **NONVOLATILE FLASH/EE MEMORY**

The ADuC7124/ADuC7126 incorporate Flash/EE memory technology on-chip to provide the user with nonvolatile, incircuit reprogrammable memory space.

Like EEPROM, flash memory can be programmed in-system at a byte level, although it must first be erased. The erase is performed in page blocks. As a result, flash memory is often and more correctly referred to as Flash/EE memory.

Overall, Flash/EE memory represents a step closer to the ideal memory device that includes nonvolatility, in-circuit programmability, high density, and low cost. Incorporated in the ADuC7124/ADuC7126, Flash/EE memory technology allows the user to update program code space in-circuit, without the need to replace one-time programmable (OTP) devices at remote operating nodes.

## Flash/EE Memory

The ADuC7124/ADuC7126 contain two 64 kB arrays of Flash/EE memory. In flash Block 0, the lower 62 kB is available to the user, and the upper 2 kB of this Flash/EE program memory array contain permanently embedded firmware, allowing in-circuit serial download. The 2 kB of embedded firmware also contain a power-on configuration routine that downloads factory calibrated coefficients to the various calibrated peripherals (band gap references and so on). This 2 kB embedded firmware is hidden from user code. It is not possible for the user to read, write, or erase this page. In flash Block 1, all 64 kB of Flash/EE memory are available to the user.

The 126 kB of Flash/EE memory can be programmed in-circuit, using the serial download mode or the JTAG mode provided.

## Flash/EE Memory Reliability

The Flash/EE memory arrays on the parts are fully qualified for two key Flash/EE memory characteristics: Flash/EE memory cycling endurance and Flash/EE memory data retention.

Endurance quantifies the ability of the Flash/EE memory to be cycled through many program, read, and erase cycles. A single endurance cycle is composed of four independent, sequential events, defined as

- 1. Initial page erase sequence.

- 2. Read/verify sequence (single Flash/EE).

- 3. Byte program sequence memory.

- 4. Second read/verify sequence (endurance cycle).

In reliability qualification, every half word (16-bit wide) location of the three pages (top, middle, and bottom) in the Flash/EE memory is cycled 10,000 times from 0x0000 to 0xFFFF. As indicated in Table 1, the Flash/EE memory endurance qualification is carried out in accordance with JEDEC Retention Lifetime Specification A117 over the industrial temperature range of  $-40^{\circ}$  to  $+125^{\circ}$ C. The results allow the specification of a minimum endurance figure over a supply temperature of 10,000 cycles. Retention quantifies the ability of the Flash/EE memory to retain its programmed data over time. Again, the parts are qualified in accordance with the formal JEDEC Retention Lifetime Specification (A117) at a specific junction temperature ( $T_J = 85^{\circ}$ C). As part of this qualification procedure, the Flash/EE memory is cycled to its specified endurance limit (see the Flash/EE Memory section) before data retention is characterized. This means that the Flash/EE memory is guaranteed to retain its data for its fully specified retention lifetime every time the Flash/EE memory is reprogrammed. In addition, note that retention lifetime, based on the activation energy of 0.6 eV, derates with  $T_J$  as shown in Figure 39.

Figure 39. Flash/EE Memory Data Retention

## PROGRAMMING

The 126 kB of Flash/EE memory can be programmed in-circuit, using the serial download mode or the provided JTAG mode.

## Serial Downloading (In-Circuit Programming)

The ADuC7124/ADuC7126 facilitate code download via the standard UART serial port. It is only available on UART0 (P1.0 and P1.1). The parts enter serial download mode after a reset or power cycle if the BM pin is pulled low through an external 1 k $\Omega$  resistor. When in serial download mode, the user can download code to the full 126 kB of Flash/EE memory while the device is in-circuit in its target application hardware. An executable PC serial download is provided as part of the development system for serial downloading via the UART. The AN-724 application note describes the UART download protocol.

## Downloading (In-Circuit Programming) via I<sup>2</sup>C

The ADuC7126BSTZ126I and ADuC7126BSTZ126IRL models facilitate code download via the the I<sup>2</sup>C port. The models enter download mode after a reset or power cycle if the BM pin is pulled low through an external 1 k $\Omega$  resistor and Flash Address 0x80014 = 0xFFFFFFF. Once in download mode, the user can download code to the full 126 kB of Flash/EE memory while the device is in-circuit in its target application hardware. An executable PC I<sup>2</sup>C download is provided as part of the development system

# ADuC7124/ADuC7126

#### Table 45. FEE1STA Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1STA | 0xFFFFF880 | 0x0000        | R      |

#### Table 46. FEE1MOD Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1MOD | 0xFFFFF884 | 0x80          | R/W    |

#### Table 47. FEE1CON Register

| Name Address |            | Default Value | Access |  |

|--------------|------------|---------------|--------|--|

| FEE1CON      | 0xFFFFF888 | 0x00          | R/W    |  |

#### Table 48. FEE1DAT Register

| Name Address |            | Default Value | Access |  |

|--------------|------------|---------------|--------|--|

| FEE1DAT      | 0xFFFFF88C | 0xXXXX        | R/W    |  |

FEE1DAT is a 16-bit data register.

#### Table 49. FEE1ADR Register

| Name Address |            | Default Value | Access |

|--------------|------------|---------------|--------|

| FEE1ADR      | 0xFFFFF890 | 0x0000        | R/W    |

FEE1ADR is a 16-bit address register.

#### Table 50. FEE1SGN Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1SGN | 0xFFFFF898 | 0xFFFFFF      | R      |

FEE1SGN is a 24-bit code signature.

#### Table 51. FEE1PRO Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1PRO | 0xFFFFF89C | 0x0000000     | R/W    |

FEE1PRO provides protection following subsequent reset MMR. It requires a software key (see Table 57).

#### Table 52. FEE1HID Register

| Name Address |            | Default Value | Access |

|--------------|------------|---------------|--------|

| FEE1HID      | 0xFFFFF8A0 | 0xFFFFFFF     | R/W    |

FEE1HID provides immediate protection MMR. It does not require any software keys (see Table 57).

#### Command Sequence for Executing a Mass Erase

FEE0DAT = 0x3CFF; FEE0ADR = 0xFFC3; FEE0MOD = FEE0MOD|0x8; //Erase key enable FEE0CON = 0x06; //Mass erase command

#### Bit Description [15:6] Reserved. 5 Reserved. 4 Reserved. 3 Flash/EE interrupt status bit. Set automatically when an interrupt occurs, that is, when a command is complete and the Flash/EE interrupt enable bit in the FEExMOD register is set. Cleared when reading the FEExSTA register. 2 Flash/EE controller busy. Set automatically when the controller is busy. Cleared automatically when the controller is not busy. 1 Command fail. Set automatically when a command completes unsuccessfully. Cleared automatically when reading the FEExSTA register. 0 Command complete. Set by MicroConverter when a command is complete. Cleared automatically when reading the FEExSTA register.

#### Table 53. FEExSTA MMR Bit Descriptions

| Bit     | Value | Name       | Description                                                      |

|---------|-------|------------|------------------------------------------------------------------|

| [15:12] |       |            | Reserved.                                                        |

| 11      | 1     | PWMPO      | Clearing this bit powers<br>down the PWM. Always<br>clear to 00. |

| [10:9]  | 00    | PWMCLKDIV  |                                                                  |

| 8       |       | SPIPO      | Clearing this bit powers down the SPI.                           |

| [7:6]   |       | SPICLKDIV  | SPI block driving clock divider bits.                            |

|         | 00    |            | 41.78 MHz.                                                       |

|         | 01    |            | 20.89 MHz.                                                       |

|         | 10    |            | 10.44 MHz.                                                       |

|         | 11    |            | 5.22 MHz.                                                        |

| 5       |       | I2C1PO     | Clearing this bit powers down I2C1.                              |

| [4:3]   |       | I2C1CLKDIV | I2C0 block driving clock divider bits.                           |

|         | 00    |            | 41.78 MHz.                                                       |

|         | 01    |            | 10.44 MHz.                                                       |

|         | 10    |            | 5.22 MHz.                                                        |

|         | 11    |            | 1.31 MHz.                                                        |

| 2       |       | I2C0PO     | Clearing this bit powers down I2C0.                              |

| [1:0]   |       | I2C0CLKDIV | I2C1 block driving clock divider bits.                           |

|         | 00    |            | 41.78 MHz.                                                       |

|         | 01    |            | 10.44 MHz.                                                       |

|         | 10    |            | 5.22 MHz.                                                        |

|         | 11    |            | 1.31 MHz.                                                        |

## Table 77. POWCON1 MMR Bit Descriptions<sup>1</sup>

<sup>1</sup> Divided clock for SPI/I2C0/I2C1 must be greater than or equal to the CPU clock as selected by POWCON0 [2:0].

The POWCON1 write sequence is as follows:

- 1. Write Code 0x76 to Register POWKEY3.

- 2. Write user value to Register POWCON1.

- 3. Write Code 0xB1 to Register POWKEY4.

| Bit   | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | FIFOMODE    | FIFO mode flag.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |             | 0x0: non-FIFO mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|       |             | 0x1: reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |             | 0x2: reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |             | 0x3: FIFO mode. Set automatically if<br>FIFOEN is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [5:4] | Reserved    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [3:1] | STATUS[2:0] | Interrupt status bits that work only when<br>NINT is set.<br>[000]: modem status interrupt. Cleared by<br>reading COMxSTA1. Priority 4.<br>[001]: for non-FIFO mode, transmit buffer<br>empty interrupt.<br>For FIFO mode, Tx FIFO is empty.<br>Cleared by writing COMxTX or reading<br>COMxIID0. Priority 3.<br>[010]: non-FIFO mode. Receive buffer data<br>ready interrupt. Cleared automatically by<br>reading COMxRX.<br>For FIFO mode, set trigger level reached.<br>Cleared automatically when FIFO drops<br>below the trigger level. Priority 2.<br>[011]: receive line status error interrupt.<br>Cleared by reading COMxSTA0. Priority 1.<br>[110]: Rx FIFO timeout interrupt (FIFO<br>mode only). Set automatically if there is at<br>least one byte in the Rx FIFO, and there is<br>no access to the Rx FIFO in the next four-<br>frames accessing cycle. Cleared by reading<br>COMxRX, setting RXRST, or when a new<br>byte arrives in the Rx FIFO <sup>1</sup> . Priority 2.<br>[Other state]: reserved. |

| 0     | NINT        | Set to disable interrupt flags by STATUS[2:0]. Clear to enable interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 93. COMxIID0 MMR Bit Descriptions

<sup>1</sup> A frame time is the time allotted for one start bit, n data bits, one parity bit, and one stop bit. Here, n is the word length selected with the WLS bits in COMxCON0.

WLS[1:0] = 00: timeout threshold = time for 32 bits =  $(1 + 5 + 1 + 1) \times 4$ . WLS[1:0] = 01: timeout threshold = time for 36 bits =  $(1 + 6 + 1 + 1) \times 4$ .

WLS[1:0] = 10: timeout threshold = time for 40 bits =  $(1 + 7 + 1 + 1) \times 4$ .

WLS[1:0] = 11: timeout threshold = time for 44 bits =  $(1 + 8 + 1 + 1) \times 4$ .

#### **COM0FCR Register**

| Name:          | COM0FCR    |

|----------------|------------|

| Address:       | 0xFFFF0708 |

| Default Value: | 0x00       |

| Access:        | Read/write |

The FIFO control register (FCR) is a write-only register at the same address as the interrupt identification register (IIR), which is a read-only register.

### **COM1FCR Register**

| Name:          | COM1FCR    |

|----------------|------------|

| Address:       | 0xFFFF0748 |

| Default Value: | 0x00       |

| Access:        | Read/write |

The FIFO control register (FCR) is a write-only register at the same address as the interrupt identification register (IIR), which is a read-only register.

| Table 94. | COMxFCR | MMR Bit | Descriptions |

|-----------|---------|---------|--------------|

|-----------|---------|---------|--------------|

| Bit   | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5] | RXFIFOTL | Receiver FIFO trigger level. RXFIFOTL sets the<br>trigger level for the receiver FIFO. When the<br>trigger level is reached, a receiver data-ready<br>interrupt is generated (if the interrupt<br>request is enabled). When the FIFO drops<br>below the trigger level, the interrupt is<br>cleared.<br>0x0: one byte.<br>0x1: two bytes.<br>0x2: four bytes.<br>0x3: six bytes.<br>0x4: eight bytes.<br>0x5: 10 bytes.<br>0x6: 12 bytes. |

| [4:3] | Reserved | 0x7: 14 bytes.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2     | TXRST    | Tx FIFO reset. Writing a 1 flushes the Tx FIFO.<br>Does not affect shift register. Note that<br>TXRST should be cleared manually to make<br>Tx FIFO work after flushing.                                                                                                                                                                                                                                                                 |

| 1     | RXRST    | Rx FIFO reset. Writing a 1 flushes the Rx FIFO.<br>Does not affect shift register. Note that<br>RXRST should be cleared manually to make<br>the Rx FIFO work after flushing.                                                                                                                                                                                                                                                             |

| 0     | FIFOEN   | Transmitter and receiver FIFOs mode enable.<br>FIFOEN must be set before other FCR bits are<br>written to. Set for FIFO mode. The transmitte<br>and receiver FIFOs are enabled. Cleared for<br>non-FIFO mode; the transmitter and receiver<br>FIFOs are disabled, and the FIFO pointers are<br>cleared.                                                                                                                                  |

#### **COM0CON0** Register

| Name:          | COM0CON0   |

|----------------|------------|

| Address:       | 0xFFFF070C |

| Default Value: | 0x00       |

| Access:        | Read/write |

COM0CON0 is the line control register for UART0.

# ADuC7124/ADuC7126

### **COM1CON0** Register

| Name:          | COM1CON0   |

|----------------|------------|

| Address:       | 0xFFFF074C |

| Default Value: | 0x00       |

| Access:        | Read/write |

COM1CON0 is the line control register for UART1.

### Table 95. COMxCON0 MMR Bit Descriptions

| Name | Description                                                                                            |

|------|--------------------------------------------------------------------------------------------------------|

| DLAB | Divisor latch access.                                                                                  |

|      | Set by the user to enable access to the                                                                |

|      | COMxDIV0 and COMxDIV1 registers.                                                                       |

|      | Cleared by the user to disable access to                                                               |

|      | COMxDIV0 and COMxDIV1 and enable access to                                                             |

|      | COMxRX and COMxTX.                                                                                     |

| BRK  | Set break.                                                                                             |

|      | Set by the user to force SOUTx to 0.                                                                   |

|      | Cleared to operate in normal mode.                                                                     |

| SP   | Stick parity.                                                                                          |

|      | Set by the user to force parity to defined values:                                                     |

|      | 1 if $EPS = 1$ and $PEN = 1$ , 0 if $EPS = 0$ and $PEN = 1$ .                                          |

| EPS  | Even parity select bit.                                                                                |

|      | Set for even parity.                                                                                   |

|      | Cleared for odd parity.                                                                                |

| PEN  | Parity enable bit.                                                                                     |

|      | Set by the user to transmit and check the                                                              |

|      | parity bit.                                                                                            |

|      | Cleared by the user for no parity transmission or                                                      |

|      | checking.                                                                                              |

| Stop | Stop bit.                                                                                              |

|      | Set by the user to transmit 1½ stop bits if the word                                                   |

|      | length is five bits or two stop bits if the word<br>length is six bits, seven bits, or eight bits. The |

|      | receiver checks the first stop bit only, regardless                                                    |

|      | of the number of stop bits selected.                                                                   |

|      | Cleared by the user to generate one stop bit in                                                        |

|      | the transmitted data.                                                                                  |

| WLS  | Word length select:                                                                                    |

|      | 00 = five bits, $01 =$ six bits, $10 =$ seven bits, $11 =$                                             |

| 1    | eight bits.                                                                                            |

|      | DLAB<br>BRK<br>SP<br>EPS<br>PEN<br>Stop                                                                |

### COM0CON1 Register

| Name:          | COM0CON1   |

|----------------|------------|

| Address:       | 0xFFFF0710 |

| Default Value: | 0x00       |

| Access:        | Read/write |

COM0CON1 is the modem control register for UART0.

## COM1CON1 Register

| Name:          | COM1CON1   |

|----------------|------------|

| Address:       | 0xFFFF0750 |

| Default Value: | 0x00       |

| Access:        | Read/write |

COM1CON1 is the modem control register for UART1.

#### Table 96. COMxCON1 MMR Bit Descriptions

| Bit   | Name     | Description                                                                                                                                                                                                                                                                                                                                               |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:5] |          | Reserved.                                                                                                                                                                                                                                                                                                                                                 |

| 4     | LOOPBACK | Loop back.<br>Set by the user to enable loopback mode.<br>In loopback mode, SOUTx is forced high.<br>The modem signals are also directly con-<br>nected to the status inputs (RTS to CTS and<br>DTR to DSR).<br>Cleared by the user to be in normal mode.                                                                                                 |

| 3     | PEN      | Parity enable bit.<br>Set by the user to transmit and check the<br>parity bit.<br>Cleared by the user for no parity transmission<br>or checking.                                                                                                                                                                                                          |

| 2     | Stop     | Stop bit.<br>Set by the user to transmit 1½ stop bits if<br>the word length is five bits or two stop bits<br>if the word length is six bits, seven bits, or<br>eight bits. The receiver checks the first stop<br>bit only, regardless of the number of stop<br>bits selected.<br>Cleared by the user to generate one stop<br>bit in the transmitted data. |

| 1     | RTS      | Request to send.<br>Set by the user to force the RTS output to 0.<br>Cleared by the user to force the RTS output<br>to 1.                                                                                                                                                                                                                                 |

| 0     | DTR      | Data terminal ready.<br>Set by the user to force the DTR output to<br>0.<br>Cleared by the user to force the DTR output<br>to 1.                                                                                                                                                                                                                          |

## COM0STA0 Register

| Name:          | COM0STA0   |

|----------------|------------|

| Address:       | 0xFFFF0714 |

| Default Value: | 0xE0       |

| Access:        | Read only  |

COM0STA0 is the line status register for UART0.

## SPI Registers

The following MMR registers control the SPI interface: SPISTA, SPIRX, SPITX, SPIDIV, and SPICON.

## SPI Status Register

| Name:          | SPISTA                                                                                   |

|----------------|------------------------------------------------------------------------------------------|

| Address:       | 0xFFFF0A00                                                                               |

| Default Value: | 0x0000                                                                                   |

| Access:        | Read only                                                                                |

| Function:      | This 32-bit MMR contains the status of the SPI interface in both master and slave modes. |

| Bit     | Name           | Description                                                                                                                                               |

|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| [15:12] |                | Reserved.                                                                                                                                                 |

| 11      | SPIREX         | SPI Rx FIFO excess bytes present. This bit is set when there are more bytes in the Rx FIFO than indicated in the SPIMDE bits in SPICON                    |

|         |                | This bit is cleared when the number of bytes in the FIFO is equal to or less than the number in SPIMDE.                                                   |

| [10:8]  | SPIRXFSTA[2:0] | SPI Rx FIFO status bits.                                                                                                                                  |

|         |                | [000] = Rx FIFO is empty.                                                                                                                                 |

|         |                | [001] = one valid byte in the FIFO.                                                                                                                       |

|         |                | [010] = two valid bytes in the FIFO.                                                                                                                      |

|         |                | [011] = three valid bytes in the FIFO.                                                                                                                    |

|         |                | [100] = four valid bytes in the FIFO.                                                                                                                     |

| 7       | SPIFOF         | SPI Rx FIFO overflow status bit.                                                                                                                          |

|         |                | Set when the Rx FIFO was already full when new data was loaded to the FIFO. This bit generates an interrupt except when SPIRFLH is set in SPICON.         |

|         |                | Cleared when the SPISTA register is read.                                                                                                                 |

| 6       | SPIRXIRQ       | SPI Rx IRQ status bit.                                                                                                                                    |

|         |                | Set when a receive interrupt occurs. This bit is set when SPITMDE in SPICON is cleared and the required number of bytes has been received.                |

|         |                | Cleared when the SPISTA register is read.                                                                                                                 |

| 5       | SPITXIRQ       | SPI Tx IRQ status bit.                                                                                                                                    |

|         |                | Set when a transmit interrupt occurs. This bit is set when SPITMDE in SPICON is set and the required number of bytes has been transmitted.                |

|         |                | Cleared when the SPISTA register is read.                                                                                                                 |

| 4       | SPITXUF        | SPI Tx FIFO underflow.                                                                                                                                    |

|         |                | This bit is set when a transmit is initiated without any valid data in the Tx FIFO. This bit generates an interrupt except when SPITFLH is set in SPICON. |

|         |                | Cleared when the SPISTA register is read.                                                                                                                 |

| [3:1]   | SPITXFSTA[2:0] | SPI Tx FIFO status bits.                                                                                                                                  |

|         |                | [000] = Tx FIFO is empty.                                                                                                                                 |

|         |                | [001] = one valid byte in the FIFO.                                                                                                                       |

|         |                | [010] = two valid bytes in the FIFO.                                                                                                                      |

|         |                | [011] = three valid bytes in the FIFO.                                                                                                                    |

|         |                | [100] = four valid bytes in the FIFO.                                                                                                                     |

| 0       | SPIISTA        | SPI interrupt status bit.                                                                                                                                 |

|         |                | Set to 1 when an SPI-based interrupt occurs.                                                                                                              |

|         |                | Cleared after reading SPISTA.                                                                                                                             |

## Table 100. SPISTA MMR Bit Descriptions

## **Data Sheet**

| Bit | Name    | Description                                                                                                           |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------|

| 9   | SPIOEN  | Slave MISO output enable bit.                                                                                         |

|     |         | Set this bit for MISO to operate as normal.                                                                           |

|     |         | Clear this bit to disable the output driver on the MISO pin. The MISO pin is open-drain when this bit is cleared.     |

| 8   | SPIROW  | SPIRX overflow overwrite enable.                                                                                      |

|     |         | Set by the user, the valid data in the SPIRX register is overwritten by the new serial byte received.                 |

|     |         | Cleared by the user, the new serial byte received is discarded.                                                       |

| 7   | SPIZEN  | SPI transmits zeros when Tx FIFO is empty.                                                                            |

|     |         | Set this bit to transmit 0x00 when there is no valid data in the Tx FIFO.                                             |

|     |         | Clear this bit to transmit the last transmitted value when there is no valid data in the Tx FIFO.                     |

| 6   | SPITMDE | SPI transfer and interrupt mode.                                                                                      |

|     |         | Set by the user to initiate transfer with a write to the SPITX register. Interrupt occurs only when SPITX is empty.   |

|     |         | Cleared by the user to initiate transfer with a read of the SPIRX register. Interrupt occurs only when SPIRX is full. |

| 5   | SPILF   | LSB first transfer enable bit.                                                                                        |

|     |         | Set by the user, the LSB is transmitted first.                                                                        |

|     |         | Cleared by the user, the MSB is transmitted first.                                                                    |

| 4   | SPIWOM  | SPI wire-OR'ed mode enable bit.                                                                                       |

|     |         | Set to 1 enable open-drain data output. External pull-ups required on data output pins.                               |

|     |         | Cleared for normal output levels.                                                                                     |

| 3   | SPICPO  | Serial clock polarity mode bit.                                                                                       |

|     |         | Set by the user, the serial clock idles high.                                                                         |

|     |         | Cleared by the user, the serial clock idles low.                                                                      |

| 2   | SPICPH  | Serial clock phase mode bit.                                                                                          |

|     |         | Set by the user, the serial clock pulses at the beginning of each serial bit transfer.                                |

|     |         | Cleared by the user, the serial clock pulses at the end of each serial bit transfer.                                  |

| 1   | SPIMEN  | Master mode enable bit.                                                                                               |

|     |         | Set by the user to enable master mode.                                                                                |

|     |         | Cleared by the user to enable slave mode.                                                                             |

| 0   | SPIEN   | SPI enable bit.                                                                                                       |

|     |         | Set by the user to enable the SPI.                                                                                    |

|     |         | Cleared by the user to disable the SPI.                                                                               |

## **Data Sheet**

## ADuC7124/ADuC7126

| Name:          | I2C0MRX, I2C1MRX                                                |

|----------------|-----------------------------------------------------------------|

| Address:       | 0xFFFF0808, 0xFFFF0908                                          |

| Default Value: | 0x00                                                            |

| Access:        | Read only                                                       |

| Function:      | This 8-bit MMR is the I <sup>2</sup> C master receive register. |

#### I<sup>2</sup>C Master Transmit Register

| Name:          | I2C0MTX, I2C1MTX                                                 |

|----------------|------------------------------------------------------------------|

| Address:       | 0xFFFF080C 0xFFFF090C                                            |

| Default Value: | 0x00, 0x00                                                       |

| Access:        | Read/write                                                       |

| Function:      | This 8-bit MMR is the I <sup>2</sup> C master transmit register. |

#### I<sup>2</sup>C Master Read Count Register

| Name:          | I2C0MCNT0, I2C1MCNT0                                                                                                 |  |

|----------------|----------------------------------------------------------------------------------------------------------------------|--|