# E·XFL

## XMOS - XUF208-256-QF48-C10 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | XCore                                                         |

| Core Size                  | 32-Bit 8-Core                                                 |

| Speed                      | 1000MIPS                                                      |

| Connectivity               | USB                                                           |

| Peripherals                | -                                                             |

| Number of I/O              | 27                                                            |

| Program Memory Size        | 1MB (1M x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 256K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                  |

| Data Converters            | -                                                             |

| Oscillator Type            | External                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                               |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 48-UFQFN Exposed Pad                                          |

| Supplier Device Package    | 48-UQFN (6x6)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xuf208-256-qf48-c10 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 XUF208-256-QF48 Features

#### ► Multicore Microcontroller with Advanced Multi-Core RISC Architecture

- Eight real-time logical cores

- Core share up to 500 MIPS

- Up to 1000 MIPS in dual issue mode

- Each logical core has:

- Guaranteed throughput of between 1/5 and 1/8 of tile MIPS

- 16x32bit dedicated registers

- 167 high-density 16/32-bit instructions

- All have single clock-cycle execution (except for divide)

- 32x32 ${\rightarrow}64$  bit MAC instructions for DSP, arithmetic and user-definable cryptographic functions

#### ▶ USB PHY, fully compliant with USB 2.0 specification

#### Programmable I/O

- 27 general-purpose I/O pins, configurable as input or output

- Up to 9 x 1 bit port, 2 x 4 bit port, 1 x 8 bit port

- 1 xCONNECT link

- Port sampling rates of up to 60 MHz with respect to an external clock

- 32 channel ends for communication with other cores, on or off-chip

#### Memory

- 256KB internal single-cycle SRAM for code and data storage

- 8KB internal OTP for application boot code

- 2MB internal flash for application code and overlays

#### Hardware resources

- 6 clock blocks

- 10 timers

- 4 locks

#### JTAG Module for On-Chip Debug

#### Security Features

• Programming lock disables debug and prevents read-back of memory contents

-XM()S

AES bootloader ensures secrecy of IP held on external flash memory

#### Ambient Temperature Range

- Commercial qualification: 0°C to 70°C

- Industrial qualification: -40 °C to 85 °C

#### Speed Grade

• 10: 500 MIPS

#### Power Consumption

- 170 mA (typical)

- ▶ 48-pin QF package 0.4 mm pitch

#### 8.1 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 10 provide a strong level of protection and are sufficient for providing strong IP security.

## 9 Memory

#### 9.1 OTP

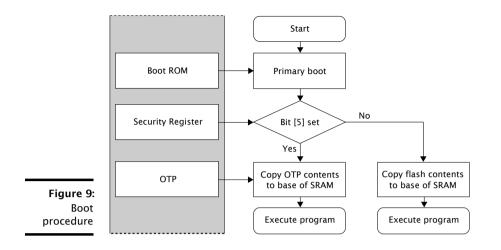

The xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds data in four sectors each containing 512 rows of 32 bits which can be used to implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

#### 9.2 SRAM

The xCORE Tile integrates a single 256KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and

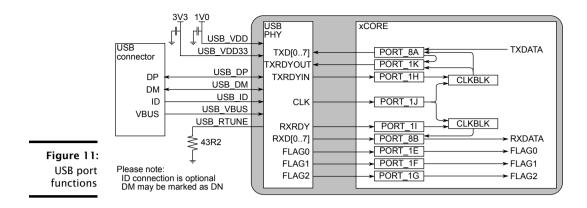

Figure 11 shows how two clock blocks can be used to clock the USB ports. One clock block for the TXDATA path, and one clock block for the RXDATA path. Details on how to connect those ports are documented in an application note on USB for xCORE-200.

## 10.1 Logical Core Requirements

The XMOS XUD software component runs in a single logical core with endpoint and application cores communicating with it via a combination of channel communication and shared memory variables.

Each IN (host requests data from device) or OUT (data transferred from host to device) endpoint requires one logical core.

# 11 JTAG

The JTAG module can be used for loading programs, boundary scan testing, incircuit source-level debugging and programming the OTP memory.

The JTAG chain structure is illustrated in Figure 12. It comprises a single 1149.1 compliant TAP that can be used for boundary scan of the I/O pins. It has a 4-bit IR and 32-bit DR. It also provides access to a chip TAP that in turn can access the xCORE Tile for loading code and debugging.

The JTAG module can be reset by holding TMS high for five clock cycles.

The JTAG device identification register can be read by using the IDCODE instruction. Its contents are specified in Figure 13.

Figure 13: IDCODE return value

|          | Bit | t31 |      |    |   |   |   |   |   |   |   |    |            | De | evice | e Ide | ntifi | catio | on R                  | egist | ter |   |   |   |   |   |   |   |   |   |   | E | it0 |

|----------|-----|-----|------|----|---|---|---|---|---|---|---|----|------------|----|-------|-------|-------|-------|-----------------------|-------|-----|---|---|---|---|---|---|---|---|---|---|---|-----|

| 13:      |     | Ve  | ersi | on |   |   |   |   |   |   |   | Ра | art Number |    |       |       |       |       | Manufacturer Identity |       |     |   |   |   |   |   |   |   |   |   |   |   |     |

| DE<br>ue | 0   | C   | )    | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0          | 0  | 0     | 0     | 0     | 0     | 1                     | 1     | 0   | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1   |

| ue       | 0   |     |      |    | ( | ) |   |   | ( | ) |   |    | (          | 0  |       |       | (     | 5     |                       |       | (   | 5 |   |   |   | 3 |   |   |   | 3 |   |   |     |

The PLL\_AVDD supply should be separated from the other noisier supplies on the board. The PLL requires a very clean power supply, and a low pass filter (for example, a  $4.7 \Omega$  resistor and 100 nF multi-layer ceramic capacitor) is recommended on this pin.

The following ground pins are provided:

► GND for all supplies

All ground pins must be connected directly to the board ground.

The VDD and VDDIO supplies should be decoupled close to the chip by several 100 nF low inductance multi-layer ceramic capacitors between the supplies and GND (for example, 100nF 0402 for each supply pin). The ground side of the decoupling capacitors should have as short a path back to the GND pins as possible. A bulk decoupling capacitor of at least 10 uF should be placed on each of these supplies.

RST\_N is an active-low asynchronous-assertion global reset signal. Following a reset, the PLL re-establishes lock after which the device boots up according to the boot mode (*see* §8). RST\_N and must be asserted low during and after power up for 100 ns.

#### 12.1 USB connections

USB\_VBUS should be connected to the VBUS pin of the USB connector. A 2.2  $\mu$ F capacitor to ground is required on the VBUS pin. A ferrite bead may be used to reduce HF noise.

For self-powered systems, a bleeder resistor may be required to stop VBUS from floating when no USB cable is attached.

$\mathsf{USB\_DP}$  and  $\mathsf{USB\_DN}$  should be connected to the USB connector.  $\mathsf{USB\_ID}$  does not need to be connected.

#### 12.2 USB signal routing and placement

The USB\_DP and USB\_DN lines are the positive and negative data polarities of a high speed USB signal respectively. Their high-speed differential nature implies that they must be coupled and properly isolated. The board design must ensure that the board traces for USB\_DP and USB\_DN are tightly matched. In addition, according to the USB 2.0 specification, the USB\_DP and USB\_DN differential impedance must be 90  $\Omega$ .

#### 12.2.1 General routing and placement guidelines

The following guidelines will help to avoid signal quality and EMI problems on high speed USB designs. They relate to a four-layer (Signal, GND, Power, Signal) PCB.

For best results, most of the routing should be done on the top layer (assuming the USB connector and XS2-UF8A-256-QF48 are on the top layer) closest to GND.

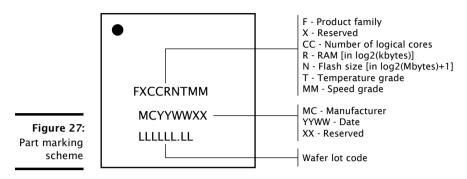

## 14.1 Part Marking

# 15 Ordering Information

| Figure 28:   | Product Code        | Marking   | Qualification | Speed Grade |

|--------------|---------------------|-----------|---------------|-------------|

| Orderable    | XUF208-256-QF48-C10 | U30881C10 | Commercial    | 500 MIPS    |

| part numbers | XUF208-256-QF48-I10 | U30881I10 | Industrial    | 500 MIPS    |

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing node configuration

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to 0xnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

control-token

24-bit response

16-bit

32-bit

control-token

192

channel-end identifier

register number

data

1

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |  |  |

|---------------|------------------------|-----------------|---------------|--|--|

| 193           | channel-end identifier | register number | 1             |  |  |

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.4 Accessing a register of an analogue peripheral

Peripheral registers can be accessed through the interconnect using the functions write\_periph\_32(device, peripheral, ...), read\_periph\_32(device, peripheral, ...)  $\leftrightarrow$ , write\_periph\_8(device, peripheral, ...), and read\_periph\_8(device, peripheral  $\leftrightarrow$ , ...); where device is the name of the analogue device, and peripheral is the number of the peripheral. These functions implement the protocols described below.

A channel-end should be allocated to communicate with the configuration registers. The destination of the channel-end should be set to 0xnnnnpp02 where nnnn is the node-identifier and pp is the peripheral identifier.

#### **B.5** Security configuration: 0x05

| Bits  | Perm | Init | Description                                                 |

|-------|------|------|-------------------------------------------------------------|

| 31    | RW   |      | Disables write permission on this register                  |

| 30:15 | RO   | -    | Reserved                                                    |

| 14    | RW   |      | Disable access to XCore's global debug                      |

| 13    | RO   | -    | Reserved                                                    |

| 12    | RW   |      | lock all OTP sectors                                        |

| 11:8  | RW   |      | lock bit for each OTP sector                                |

| 7     | RW   |      | Enable OTP reduanacy                                        |

| 6     | RO   | -    | Reserved                                                    |

| 5     | RW   |      | Override boot mode and read boot image from OTP             |

| 4     | RW   |      | Disable JTAG access to the PLL/BOOT configuration registers |

| 3:1   | RO   | -    | Reserved                                                    |

| 0     | RW   |      | Disable access to XCore's JTAG debug TAP                    |

Copy of the security register as read from OTP.

0x05: Security configuration

## B.6 Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator has been stopped for at least 10 core clock cycles (this can be achieved by inserting two nop instructions between the SETPS and GETPS). The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06:** Ring Oscillator Control

| Bits | Perm | Init | Description                        |

|------|------|------|------------------------------------|

| 31:2 | RO   | -    | Reserved                           |

| 1    | RW   | 0    | Core ring oscillator enable.       |

| 0    | RW   | 0    | Peripheral ring oscillator enable. |

## B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

-XMOS-

| 0x07:<br>Ring | Bits  | Perm | Init | Description                   |

|---------------|-------|------|------|-------------------------------|

| Oscillator    | 31:16 | RO   | -    | Reserved                      |

| Value         | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.8 Ring Oscillator Value: 0x08

This register contains the current count of the xCORE Tile Wire ring oscillator. This value is not reset on a system reset.

**0x08** Ring Oscillator Value

| 08:<br>ing | Bits  | Perm | Init | Description                   |

|------------|-------|------|------|-------------------------------|

| tor        | 31:16 | RO   | -    | Reserved                      |

| lue        | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.9 Ring Oscillator Value: 0x09

This register contains the current count of the Peripheral Cell ring oscillator. This value is not reset on a system reset.

**0x09:** Ring Oscillator Value

| Bits  | Perm | Init | Description                   |

|-------|------|------|-------------------------------|

| 31:16 | RO   | -    | Reserved                      |

| 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.10 Ring Oscillator Value: 0x0A

This register contains the current count of the Peripheral Wire ring oscillator. This value is not reset on a system reset.

**0x0A:** Ring Oscillator Value

| A:       | Bits  | Perm | Init | Description                   |

|----------|-------|------|------|-------------------------------|

| ig<br>or | 31:16 | RO   | -    | Reserved                      |

| ie       | 15:0  | RO   | 0    | Ring oscillator Counter data. |

-XMOS

#### B.11 RAM size: 0x0C

The size of the RAM in bytes

#### B.18 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

**0x16:** Debug interrupt data

| 1 <b>6:</b><br>ug | Bits | Perm | Init | Description |

|-------------------|------|------|------|-------------|

| ata               | 31:0 | DRW  |      | Value.      |

## B.19 Debug core control: 0x18

This register enables the debugger to temporarily disable logical cores. When returning from the debug interrupts, the cores set in this register will not execute. This enables single stepping to be implemented.

0x18: Debug core control

|   | Bits | Perm | Init | Description                                                                                                                                 |

|---|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------|

|   | 31:8 | RO   | -    | Reserved                                                                                                                                    |

| : | 7:0  | DRW  |      | 1-hot vector defining which threads are stopped when not in debug mode. Every bit which is set prevents the respective thread from running. |

#### B.20 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over JTAG. This is the same set of registers as the Debug Scratch registers in the xCORE tile configuration.

0x20 .. 0x27: Debug scratch

| 0x27:<br>ebug | Bits | Perm | Init | Description |

|---------------|------|------|------|-------------|

| ratch         | 31:0 | DRW  |      | Value.      |

## B.21 Instruction breakpoint address: 0x30 .. 0x33

-XM()S

This register contains the address of the instruction breakpoint. If the PC matches this address, then a debug interrupt will be taken. There are four instruction breakpoints that are controlled individually.

0x30 .. 0x33: Instruction breakpoint address

| ction<br>point | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| dress          | 31:0 | DRW  |      | Value.      |

## B.22 Instruction breakpoint control: 0x40 .. 0x43

This register controls which logical cores may take an instruction breakpoint, and under which condition.

|         | Bits  | Perm | Init | Description                                                                                              |

|---------|-------|------|------|----------------------------------------------------------------------------------------------------------|

|         | 31:24 | RO   | -    | Reserved                                                                                                 |

|         | 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |

| 3:      | 15:2  | RO   | -    | Reserved                                                                                                 |

| n<br>nt | 1     | DRW  | 0    | When 0 break when PC == IBREAK_ADDR. When 1 = break when PC != IBREAK_ADDR.                              |

| ol      | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |

0x40 .. 0x43 Instruction breakpoint control

## B.23 Data watchpoint address 1: 0x50 .. 0x53

This set of registers contains the first address for the four data watchpoints.

| <b>0x50 0x53:</b><br>Data |      |      |      |             |

|---------------------------|------|------|------|-------------|

| watchpoint                | Bits | Perm | Init | Description |

| address 1                 | 31:0 | DRW  |      | Value.      |

## B.24 Data watchpoint address 2: 0x60 .. 0x63

This set of registers contains the second address for the four data watchpoints.

| <b>0x60 0x63:</b><br>Data |      |      |      |             |

|---------------------------|------|------|------|-------------|

| watchpoint                | Bits | Perm | Init | Description |

| address 2                 | 31:0 | DRW  |      | Value.      |

#### **B.25** Data breakpoint control register: 0x70 ... 0x73

This set of registers controls each of the four data watchpoints.

|         | Bits  | Perm | Init | Description                                                                                              |

|---------|-------|------|------|----------------------------------------------------------------------------------------------------------|

|         | 31:24 | RO   | -    | Reserved                                                                                                 |

|         | 23:16 | DRW  | 0    | A bit for each thread in the machine allowing the breakpoint to be enabled individually for each thread. |

| -<br>3: | 15:3  | RO   | -    | Reserved                                                                                                 |

| a<br>t  | 2     | DRW  | 0    | When 1 the breakpoints will be be triggered on loads.                                                    |

| l       | 1     | DRW  | 0    | Determines the break condition: $0 = A AND B$ , $1 = A OR B$ .                                           |

| r       | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                            |

0x70 .. 0x73: Data breakpoint control register

#### B.26 Resources breakpoint mask: 0x80 .. 0x83

This set of registers contains the mask for the four resource watchpoints.

0x80 .. 0x83: Resources breakpoint mask

| burces<br>kpoint | Bits | Perm | Init | Description |

|------------------|------|------|------|-------------|

| mask             | 31:0 | DRW  |      | Value.      |

#### B.27 Resources breakpoint value: 0x90 .. 0x93

This set of registers contains the value for the four resource watchpoints.

0x90 .. 0x93: Resources breakpoint value

| irces<br>point | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| alue           | 31:0 | DRW  |      | Value.      |

#### B.28 Resources breakpoint control register: 0x9C .. 0x9F

This set of registers controls each of the four resource watchpoints.

-XMOS

XS2-UF8A-256-QF48

0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                     |

|------|------|------|-----------------------------------------------------------------------------------------------------------------|

| 31   | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch, XCore(PS_DBG_Scratch) and JTAG |

| 30:1 | RO   | -    | Reserved                                                                                                        |

| 0    | CRW  | 0    | When 1 the PSwitch is restricted to RO access to all CRW registers from SSwitch                                 |

## C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

**0x05:** Cause debug interrupts

|     | Bits | Perm | Init | Description                                 |

|-----|------|------|------|---------------------------------------------|

|     | 31:2 | RO   | -    | Reserved                                    |

| · ( | 1    | CRW  | 0    | 1 when the processor is in debug mode.      |

|     | 0    | CRW  | 0    | Request a debug interrupt on the processor. |

## C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| Bits  | Perm | Init | Description                                                   |

|-------|------|------|---------------------------------------------------------------|

| 31    | CRW  | 0    | Clock disable. Writing '1' will remove the clock to the tile. |

| 30:16 | RO   | -    | Reserved                                                      |

| 15:0  | CRW  | 0    | Clock divider.                                                |

## C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

-XMOS

### D.8 System JTAG device ID register: 0x09

**0x09**: System JTAG device ID register

|         | Bits  | Perm | Init | Description |

|---------|-------|------|------|-------------|

| -       | 31:28 | RO   |      |             |

| 9:<br>G | 27:12 | RO   |      |             |

| D       | 11:1  | RO   |      |             |

| er      | 0     | RO   |      |             |

#### D.9 System USERCODE register: 0x0A

**0x0A** System USERCODE register

| <b>4:</b><br>n | Bits  | Perm | Init | Description                                |

|----------------|-------|------|------|--------------------------------------------|

| E              | 31:18 | RO   |      | JTAG USERCODE value programmed into OTP SR |

| er             | 17:0  | RO   |      | metal fixable ID code                      |

#### D.10 Directions 0-7: 0x0C

This register contains eight directions, for packets with a mismatch in bits 7..0 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

| Bits  | Perm | Init | Description                                     |

|-------|------|------|-------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose dimension is 7. |

| 27:24 | RW   | 0    | The direction for packets whose dimension is 6. |

| 23:20 | RW   | 0    | The direction for packets whose dimension is 5. |

| 19:16 | RW   | 0    | The direction for packets whose dimension is 4. |

| 15:12 | RW   | 0    | The direction for packets whose dimension is 3. |

| 11:8  | RW   | 0    | The direction for packets whose dimension is 2. |

| 7:4   | RW   | 0    | The direction for packets whose dimension is 1. |

| 3:0   | RW   | 0    | The direction for packets whose dimension is 0. |

0x0C: Directions 0-7

#### D.11 Directions 8-15: 0x0D

This register contains eight directions, for packets with a mismatch in bits 15..8 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

-XMOS-

## D.18 Static link configuration: 0xA0 .. 0xA7

These registers are used for static (ie, non-routed) links. When a link is made static, all traffic is forwarded to the designated channel end and no routing is attempted. The registers control links C, D, A, B, G, H, E, and F in that order.

| Bits | Perm | Init | Description                                                                                     |

|------|------|------|-------------------------------------------------------------------------------------------------|

| 31   | RW   | 0    | Enable static forwarding.                                                                       |

| 30:9 | RO   | -    | Reserved                                                                                        |

| 8    | RW   | 0    | The destination processor on this node that packets received in static mode are forwarded to.   |

| 7:5  | RO   | -    | Reserved                                                                                        |

| 4:0  | RW   | 0    | The destination channel end on this node that packets received in static mode are forwarded to. |

**0xA0 .. 0xA7:** Static link configuration

# F USB PHY Configuration

The USB PHY is connected to the ports shown in section 10.

The USB PHY is peripheral 1. The control registers are accessed using 32-bit reads and writes (use write\_periph\_32(device, 1, ...) and read\_periph\_32(device,  $\rightarrow$  1, ...) for reads and writes).

| Number | Perm | Description             |

|--------|------|-------------------------|

| 0x00   | WO   | UIFM reset              |

| 0x04   | RW   | UIFM IFM control        |

| 0x08   | RW   | UIFM Device Address     |

| 0x0C   | RW   | UIFM functional control |

| 0x10   | RW   | UIFM on-the-go control  |

| 0x14   | RO   | UIFM on-the-go flags    |

| 0x18   | RW   | UIFM Serial Control     |

| 0x1C   | RW   | UIFM signal flags       |

| 0x20   | RW   | UIFM Sticky flags       |

| 0x24   | RW   | UIFM port masks         |

| 0x28   | RW   | UIFM SOF value          |

| 0x2C   | RO   | UIFM PID                |

| 0x30   | RO   | UIFM Endpoint           |

| 0x34   | RW   | UIFM Endpoint match     |

| 0x38   | RW   | OTG Flags mask          |

| 0x3C   | RW   | UIFM power signalling   |

| 0x40   | RW   | UIFM PHY control        |

Figure 34: Summary

#### F.1 UIFM reset: 0x00

A write to this register with any data resets all UIFM state, but does not otherwise affect the phy.

| 0x00:      | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| UIFM reset | 31:0 | WO   |      | Value.      |

#### F.2 UIFM IFM control: 0x04

General settings of the UIFM IFM state machine.

**0x20:** UIFM Sticky flags

| Bits | Perm | Init | Description               |  |

|------|------|------|---------------------------|--|

| 31:7 | RO   | -    | Reserved                  |  |

| 6:0  | RW   | 0    | Stickyness for each flag. |  |

#### F.10 UIFM port masks: 0x24

Set of masks that identify how port 1N, port 1O and port 1P are affected by changes to the flags in FLAGS

| Bits  | Perm | Init | Description                                                                                                                                         |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1?. If any flag listed in this bitmask is high, port 1? will be high. |

| 23:16 | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1P. If any flag listed in this bitmask is high, port 1P will be high. |

| 15:8  | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 10. If any flag listed in this bitmask is high, port 10 will be high. |

| 7:0   | RW   | 0    | Bit mask that determines which flags in UIFM_IFM_FLAG[6:0] contribute to port 1N. If any flag listed in this bitmask is high, port 1N will be high. |

**0x24:** UIFM port masks

### F.11 UIFM SOF value: 0x28

USB Start-Of-Frame counter

**0x28:** UIFM SOF value

| Bits  | Perm | Init | Description                             |

|-------|------|------|-----------------------------------------|

| 31:11 | RO   | -    | Reserved                                |

| 10:8  | RW   | 0    | Most significant 3 bits of SOF counter  |

| 7:0   | RW   | 0    | Least significant 8 bits of SOF counter |

-XMOS

## F.12 UIFM PID: 0x2C

The last USB packet identifier received

63

The RST\_N net should be open-drain, active-low, and have a pull-up to VDDIO.

## G.3 Full xSYS header

For a full xSYS header you will need to connect the pins as discussed in Section G.2, and then connect a 2-wire xCONNECT Link to the xSYS header. The links can be found in the Signal description table (Section 4): they are labelled XL0, XL1, etc in the function column. The 2-wire link comprises two inputs and outputs, labelled  ${}^{1}_{out}$ ,  ${}^{0}_{out}$ ,  ${}^{0}_{in}$ , and  ${}^{1}_{in}$ . For example, if you choose to use XL0 for xSCOPE I/O, you need to connect up XL0 ${}^{1}_{out}$ , XL0 ${}^{0}_{out}$ , XL0 ${}^{1}_{in}$ , as follows:

- XL0<sup>1</sup><sub>out</sub> (X0D43) to pin 6 of the xSYS header with a 33R series resistor close to the device.

- XL0<sup>0</sup><sub>out</sub> (X0D42) to pin 10 of the xSYS header with a 33R series resistor close to the device.

- >  $XLO_{in}^{0}$  (X0D41) to pin 14 of the xSYS header.

- >  $XLO_{in}^{1}$  (X0D40) to pin 18 of the xSYS header.

# H Schematics Design Check List

✓ This section is a checklist for use by schematics designers using the XUF208-256-QF48. Each of the following sections contains items to check for each design.

#### H.1 Power supplies

- □ VDDIO and OTP\_VCC supply is within specification before the VDD (core) supply is turned on. Specifically, the VDDIO and OTP\_VCC supply is within specification before VDD (core) reaches 0.4V (Section 12).

- The VDD (core) supply ramps monotonically (rises constantly) from 0V to its final value (0.95V 1.05V) within 10ms (Section 12).

- The VDD (core) supply is capable of supplying 375 mA (Section 12 and Figure 18).

- PLL\_AVDD is filtered with a low pass filter, for example an RC filter, see Section 12

#### H.2 Power supply decoupling

- The design has multiple decoupling capacitors per supply, for example at least four0402 or 0603 size surface mount capacitors of 100nF in value, per supply (Section 12).

- A bulk decoupling capacitor of at least 10uF is placed on each supply (Section 12).

#### H.3 Power on reset

The RST\_N pins are asserted (low) during or after power up. The device is not used until these resets have taken place.

#### H.4 Clock

- The CLK input pin is supplied with a clock with monotonic rising edges and low jitter.

- You have chosen an input clock frequency that is supported by the device (Section 7).

#### H.5 Boot

- $\square$  X0D01 has a 1K pull-up to VDDIO (Section 8).

- The device is kept in reset for at least 1 ms after VDDIO has reached its minimum level (Section 8).

#### H.6 JTAG, XScope, and debugging

- $\Box$  You have decided as to whether you need an XSYS header or not (Section G)

- $\Box$  If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section G).

#### H.7 GPIO

- $\hfill \Box$  You have not mapped both inputs and outputs to the same multi-bit port.

- Pins X0D04, X0D05, X0D06, and X0D07 are output only and are, during and after reset, pulled low or not connected (Section 8)

#### H.8 Multi device designs

Skip this section if your design only includes a single XMOS device.

- $\Box$  One device is connected to a QSPI or SPI flash for booting.

- Devices that boot from link have, for example, X0D06 pulled high and have link XL0 connected to a device to boot from (Section 8).

# L Revision History

| Date       | Description                                                                |

|------------|----------------------------------------------------------------------------|

| 2016-01-05 | Preliminary release                                                        |

| 2016-04-20 | Typical internal pull-up and pull down current diagrams added - Section 13 |

Copyright © 2016, All Rights Reserved.

Xmos Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. Xmos Ltd. makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.