# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Active                                                       |

| Number of LABs/CLBs            | 240                                                          |

| Number of Logic Elements/Cells | 2160                                                         |

| Total RAM Bits                 | 73728                                                        |

| Number of I/O                  | 108                                                          |

| Number of Gates                | 100000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 144-LQFP                                                     |

| Supplier Device Package        | 144-TQFP (20x20)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s100e-4tq144c |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

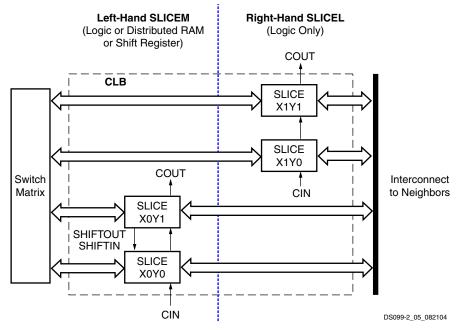

Figure 16: Arrangement of Slices within the CLB

#### **Slice Location Designations**

The Xilinx development software designates the location of a slice according to its X and Y coordinates, starting in the bottom left corner, as shown in Figure 14. The letter 'X' followed by a number identifies columns of slices, incrementing from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row, incrementing from the bottom of the die. Figure 16 shows the CLB located in the lower left-hand corner of the die. The SLICEM always has an even 'X' number, and the SLICEL always has an odd 'X' number.

### **Slice Overview**

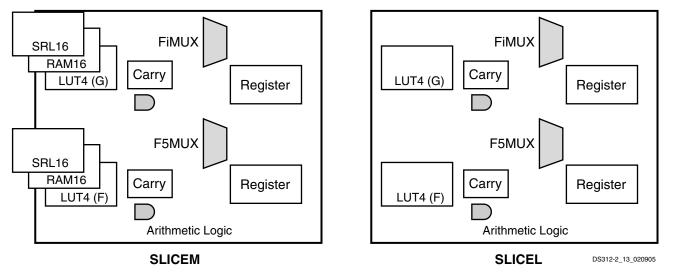

A slice includes two LUT function generators and two storage elements, along with additional logic, as shown in Figure 17.

Both SLICEM and SLICEL have the following elements in common to provide logic, arithmetic, and ROM functions:

- Two 4-input LUT function generators, F and G

- Two storage elements

- Two wide-function multiplexers, F5MUX and FiMUX

- Carry and arithmetic logic

DS312-2\_38\_021305

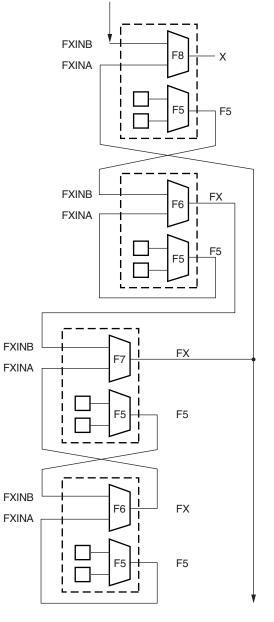

Figure 20: MUXes and Dedicated Feedback in Spartan-3E CLB

### Table 11: MUX Capabilities

|       |       |              | Tota             | al Number of Inputs per Function |                          |  |  |

|-------|-------|--------------|------------------|----------------------------------|--------------------------|--|--|

| MUX   | Usage | Input Source | For Any Function | For MUX                          | For Limited<br>Functions |  |  |

| F5MUX | F5MUX | LUTs         | 5                | 6 (4:1 MUX)                      | 9                        |  |  |

| FiMUX | F6MUX | F5MUX        | 6                | 11 (8:1 MUX)                     | 19                       |  |  |

|       | F7MUX | F6MUX        | 7                | 20 (16:1 MUX)                    | 39                       |  |  |

|       | F8MUX | F7MUX        | 8                | 37 (32:1 MUX)                    | 79                       |  |  |

www.xilinx.com

initialized distributed RAM contents are not disturbed during the configuration process.

The distributed RAM is useful for smaller amounts of memory. Larger memory requirements can use the dedicated 18Kbit RAM blocks (see Block RAM).

# **Shift Registers**

For additional information, refer to the "Using Look-Up Tables as Shift Registers (SRL16)" chapter in UG331.

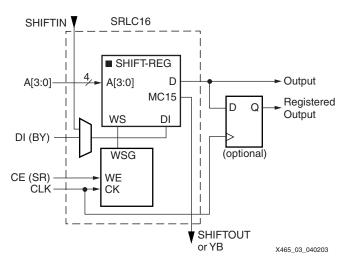

It is possible to program each SLICEM LUT as a 16-bit shift register (see Figure 28). Used in this way, each LUT can delay serial data anywhere from 1 to 16 clock cycles without using any of the dedicated flip-flops. The resulting programmable delays can be used to balance the timing of data pipelines.

The SLICEM LUTs cascade from the G-LUT to the F-LUT through the DIFMUX (see Figure 15). SHIFTIN and SHIFTOUT lines cascade a SLICEM to the SLICEM below to form larger shift registers. The four SLICEM LUTs of a single CLB can be combined to produce delays up to 64 clock cycles. It is also possible to combine shift registers across more than one CLB.

Figure 28: Logic Cell SRL16 Structure

Each shift register provides a shift output MC15 for the last bit in each LUT, in addition to providing addressable access to any bit in the shift register through the normal D output. The address inputs A[3:0] are the same as the distributed RAM address lines, which come from the LUT inputs F[4:1] or G[4:1]. At the end of the shift register, the CLB flip-flop can be used to provide one more shift delay for the addressable bit.

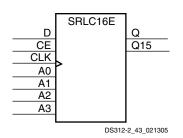

The shift register element is known as the SRL16 (Shift Register LUT 16-bit), with a 'C' added to signify a cascade ability (Q15 output) and 'E' to indicate a Clock Enable. See Figure 29 for an example of the SRLC16E component.

# Figure 29: SRL16 Shift Register Component with Cascade and Clock Enable

The functionality of the shift register is shown in Table 20. The SRL16 shifts on the rising edge of the clock input when the Clock Enable control is High. This shift register cannot be initialized either during configuration or during operation except by shifting data into it. The clock enable and clock inputs are shared between the two LUTs in a SLICEM. The clock enable input is automatically kept active if unused.

| Table | 20: | SRL16 | Shift | Register | Function |

|-------|-----|-------|-------|----------|----------|

|-------|-----|-------|-------|----------|----------|

|    | Inp | uts |   | Outputs |       |  |

|----|-----|-----|---|---------|-------|--|

| Am | CLK | CE  | D | Q       | Q15   |  |

| Am | Х   | 0   | Х | Q[Am]   | Q[15] |  |

| Am | 1   | 1   | D | Q[Am-1] | Q[15] |  |

Notes:

1. m = 0, 1, 2, 3.

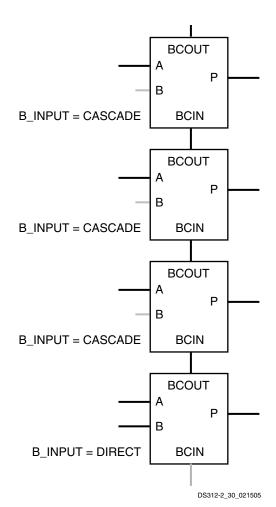

The BCIN and BCOUT ports have associated dedicated routing that connects adjacent multipliers within the same column. Via the cascade connection, the BCOUT port of one multiplier block drives the BCIN port of the multiplier block directly above it. There is no connection to the BCIN port of the bottom-most multiplier block in a column or a connection from the BCOUT port of the top-most block in a column. As an example, Figure 39 shows the multiplier cascade capability within the XC3S100E FPGA, which has a single column of multiplier, four blocks tall. For clarity, the figure omits the register control inputs.

Figure 39: Multiplier Cascade Connection

When using the BREG register, the cascade connection forms a shift register structure typically used in DSP algorithms such as direct-form FIR filters. When the BREG register is omitted, the cascade structure essentially feeds the same input value to more than one multiplier. This parallel connection serves to create wide-input multipliers, implement transpose FIR filters, and is used in any application that requires that several multipliers have the same input value.

The CLKFX\_DIVIDE is an integer ranging from 1 to 32, inclusive and forms the denominator in Equation 1. For example, if CLKFX\_MULTIPLY = 5 and CLKFX\_DIVIDE = 3, the frequency of the output clock signal is 5/3 that of the input clock signal. These attributes and their acceptable ranges are described in Table 34.

#### Table 34: DFS Attributes

🗶 XILINX.

| Attribute      | Description                   | Values                             |  |  |

|----------------|-------------------------------|------------------------------------|--|--|

| CLKFX_MULTIPLY | Frequency multiplier constant | Integer from 2 to 32, inclusive    |  |  |

| CLKFX_DIVIDE   | Frequency divisor constant    | Integer from 1<br>to 32, inclusive |  |  |

Any combination of integer values can be assigned to the CLKFX\_MULTIPLY and CLKFX\_DIVIDE attributes, provided that two conditions are met:

- 1. The two values fall within their corresponding ranges, as specified in Table 34.

- The f<sub>CLKFX</sub> output frequency calculated in Equation 1 falls within the DCM's operating frequency specifications (see Table 107 in Module 3).

#### **DFS With or Without the DLL**

Although the CLKIN input is shared with both units, the DFS unit functions with or separately from the DLL unit. Separate from the DLL, the DFS generates an output frequency from the CLKIN frequency according to the respective CLKFX\_MULTIPLY and CLKFX\_DIVIDE values. Frequency synthesis does not require a feedback loop. Furthermore, without the DLL, the DFS unit supports a broader operating frequency range.

With the DLL, the DFS unit operates as described above, only with the additional benefit of eliminating the clock distribution delay. In this case, a feedback loop from the CLK0 or CLK2X output to the CLKFB input must be present.

When operating with the DLL unit, the DFS's CLKFX and CLKFX180 outputs are phase-aligned with the CLKIN input every CLKFX\_DIVIDE cycles of CLKIN and every CLKFX\_MULTIPLY cycles of CLKFX. For example, when CLKFX\_MULTIPLY = 5 and CLKFX\_DIVIDE = 3, the input and output clock edges coincide every three CLKIN input

periods, which is equivalent in time to five CLKFX output periods.

Smaller CLKFX\_MULTIPLY and CLKFX\_DIVIDE values result in faster lock times. Therefore, CLKFX\_MULTIPLY and CLKFX\_DIVIDE must be factored to reduce their values wherever possible. For example, given CLKFX\_MULTIPLY = 9 and CLKFX\_DIVIDE = 6, removing a factor of three yields CLKFX\_MULTIPLY = 3 and CLKFX\_DIVIDE = 2. While both value-pairs result in the multiplication of clock frequency by 3/2, the latter value-pair enables the DLL to lock more quickly.

# **Phase Shifter (PS)**

The DCM provides two approaches to controlling the phase of a DCM clock output signal relative to the CLKIN signal: First, eight of the nine DCM clock outputs – CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, CLKFX, and CLKFX180 – provide either quadrant or half-period phase shifting of the input clock.

Second, the PS unit provides additional fine phase shift control of all nine DCM outputs. The PS unit accomplishes this by introducing a "fine phase shift" delay ( $T_{PS}$ ) between the CLKFB and CLKIN signals inside the DLL unit. In FIXED phase shift mode, the fine phase shift is specified at design time with a resolution down to  $1/_{256}$ <sup>th</sup> of a CLKIN cycle or one delay step (DCM\_DELAY\_STEP), whichever is greater. This fine phase shift value is relative to the coarser quadrant or half-period phase shift of the DCM clock output. When used, the PS unit shifts the phase of all nine DCM clock output signals.

#### Enabling Phase Shifting and Selecting an Operating Mode

The CLKOUT\_PHASE\_SHIFT attribute controls the PS unit for the specific DCM instantiation. As described in Table 35, this attribute has three possible values: NONE, FIXED, and VARIABLE. When CLKOUT\_PHASE\_SHIFT = NONE, the PS unit is disabled and the DCM output clocks are phase-aligned to the CLKIN input via the CLKFB feedback path. Figure 44a shows this case.

The PS unit is enabled when the CLKOUT\_PHASE\_SHIFT attribute is set to FIXED or VARIABLE modes. These two modes are described in the sections that follow.

#### Table 35: PS Attributes

| Attribute          | Description                                                                        | Values                     |

|--------------------|------------------------------------------------------------------------------------|----------------------------|

| CLKOUT_PHASE_SHIFT | Disables the PS component or chooses between Fixed Phase and Variable Phase modes. | NONE, FIXED, VARIABLE      |

| PHASE_SHIFT        | Determines size and direction of initial fine phase shift.                         | Integers from -255 to +255 |

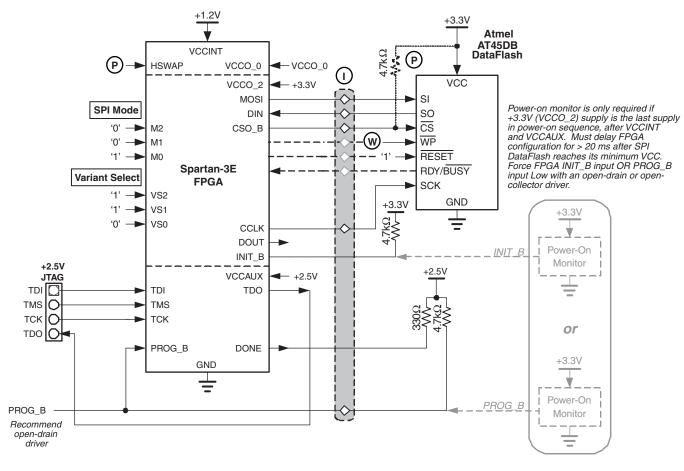

Figure 57, page 82 demonstrates how to configure multiple FPGAs with different configurations, all stored in a single SPI Flash. The diagram uses standard SPI Flash memories but the same general technique applies for Atmel DataFlash.

DS312-2\_50a\_082009

Figure 54: Atmel SPI-based DataFlash Configuration Interface

### Table 59: Byte-Wide Peripheral Interface (BPI) Connections (Cont'd)

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                         | During Configuration                                                                                                                                                                                                                                                                                                                                                                            | After Configuration                                                                                                  |

|----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| HDC      | Output                          | PROM Write Enable                                                                                                                                                                                                                                                                                                                                   | Connect to PROM write-enable<br>input (WE#). FPGA drives this<br>signal High throughout<br>configuration.                                                                                                                                                                                                                                                                                       | User I/O                                                                                                             |

| LDC2     | Output                          | PROM Byte Mode                                                                                                                                                                                                                                                                                                                                      | This signal is not used for x8<br>PROMs. For PROMs with a x8/x16<br>data width control, connect to<br>PROM byte-mode input (BYTE#).<br>See Precautions Using x8/x16<br>Flash PROMs. FPGA drives this<br>signal Low throughout<br>configuration.                                                                                                                                                 | User I/O. Drive this pin High<br>after configuration to use a<br>x8/x16 PROM in x16 mode.                            |

| A[23:0]  | Output                          | Address                                                                                                                                                                                                                                                                                                                                             | Connect to PROM address inputs.<br>High-order address lines may not<br>be available in all packages and<br>not all may be required. Number of<br>address lines required depends on<br>the size of the attached Flash<br>PROM. FPGA address generation<br>controlled by M0 mode pin.<br>Addresses presented on falling<br>CCLK edge.<br>Only 20 address lines are available<br>in TQ144 package. | User I/O                                                                                                             |

| D[7:0]   | Input                           | Data Input                                                                                                                                                                                                                                                                                                                                          | FPGA receives byte-wide data on<br>these pins in response the address<br>presented on A[23:0]. Data<br>captured by FPGA on rising edge<br>of CCLK.                                                                                                                                                                                                                                              | User I/O. If bitstream option <i>Persist=Yes</i> , becomes part of SelectMap parallel peripheral interface.          |

| CSO_B    | Output                          | Chip Select Output. Active Low.                                                                                                                                                                                                                                                                                                                     | Not used in single FPGA<br>applications. In a daisy-chain<br>configuration, this pin connects to<br>the CSI_B pin of the next FPGA in<br>the chain. If HSWAP = 1 in a<br>multi-FPGA daisy-chain<br>application, connect this signal to a<br>4.7 k $\Omega$ pull-up resistor to VCCO_2.<br>Actively drives Low when selecting<br>a downstream device in the chain.                               | User I/O                                                                                                             |

| BUSY     | Output                          | <b>Busy Indicator</b> . Typically only used after configuration, if bitstream option <i>Persist=Yes</i> .                                                                                                                                                                                                                                           | Not used during configuration but actively drives.                                                                                                                                                                                                                                                                                                                                              | User I/O. If bitstream option<br><i>Persist=Yes</i> , becomes<br>part of SelectMap parallel<br>peripheral interface. |

| CCLK     | Output                          | <b>Configuration Clock</b> . Generated<br>by FPGA internal oscillator.<br>Frequency controlled by<br><b>ConfigRate</b> bitstream generator<br>option. If CCLK PCB trace is long or<br>has multiple connections, terminate<br>this output to maintain signal<br>integrity. See CCLK Design<br>Considerations.                                        | Not used in single FPGA<br>applications but actively drives. In<br>a daisy-chain configuration, drives<br>the CCLK inputs of all other<br>FPGAs in the daisy-chain.                                                                                                                                                                                                                             | User I/O. If bitstream option <b>Persist=Yes</b> , becomes part of SelectMap parallel peripheral interface.          |

| INIT_B   | Open-drain<br>bidirectional I/O | <b>Initialization Indicator</b> . Active Low.<br>Goes Low at start of configuration<br>during the Initialization memory<br>clearing process. Released at the<br>end of memory clearing, when the<br>mode select pins are sampled. In<br>daisy-chain applications, this signal<br>requires an external 4.7 k $\Omega$ pull-up<br>resistor to VCCO_2. | Active during configuration. If CRC<br>error detected during<br>configuration, FPGA drives INIT_B<br>Low.                                                                                                                                                                                                                                                                                       | User I/O. If unused in the<br>application, drive INIT_B<br>High.                                                     |

# Maximum Bitstream Size for Daisy-Chains

The maximum bitstream length supported by Spartan-3E FPGAs in serial daisy-chains is 4,294,967,264 bits (4 Gbits), roughly equivalent to a daisy-chain with 720 XC3S1600E FPGAs. This is a limit only for serial daisy-chains where configuration data is passed via the FPGA's DOUT pin. There is no such limit for JTAG chains.

# **Configuration Sequence**

For additional information including I/O behavior before and during configuration, refer to the "Sequence of Events" chapter in <u>UG332</u>.

The Spartan-3E configuration process is three-stage process that begins after the FPGA powers on (a POR event) or after the PROG\_B input is asserted. Power-On Reset (POR) occurs after the  $V_{CCINT}$ ,  $V_{CCAUX}$ , and the  $V_{CCO}$  Bank 2 supplies reach their respective input threshold levels. After either a POR or PROG\_B event, the three-stage configuration process begins.

- 1. The FPGA clears (initializes) the internal configuration memory.

- 2. Configuration data is loaded into the internal memory.

- 3. The user-application is activated by a start-up process.

Figure 66 is a generalized block diagram of the Spartan-3E configuration logic, showing the interaction of different device inputs and Bitstream Generator (BitGen) options. A flow diagram for the configuration sequence of the Serial and Parallel modes appears in Figure 66. Figure 67 shows the Boundary-Scan or JTAG configuration sequence.

# Initialization

Configuration automatically begins after power-on or after asserting the FPGA PROG\_B pin, unless delayed using the FPGA's INIT\_B pin. The FPGA holds the open-drain INIT\_B signal Low while it clears its internal configuration memory. Externally holding the INIT\_B pin Low forces the configuration sequencer to wait until INIT\_B again goes High.

The FPGA signals when the memory-clearing phase is complete by releasing the open-drain INIT\_B pin, allowing the pin to go High via the external pull-up resistor to VCCO\_2.

# Loading Configuration Data

After initialization, configuration data is written to the FPGA's internal memory. The FPGA holds the Global Set/Reset (GSR) signal active throughout configuration, holding all FPGA flip-flops in a reset state. The FPGA signals when the entire configuration process completes by releasing the DONE pin, allowing it to go High. The FPGA configuration sequence can also be initiated by asserting PROG\_B. Once released, the FPGA begins clearing its internal configuration memory, and progresses through the remainder of the configuration process.

# Single-Ended I/O Standards

#### Table 80: Recommended Operating Conditions for User I/Os Using Single-Ended Standards

| IOSTANDARD                | V <sub>CCO</sub> for Drivers <sup>(2)</sup> |         |         |                     | V <sub>REF</sub>          |         |                          | V <sub>IH</sub> <sup>(3)</sup> |

|---------------------------|---------------------------------------------|---------|---------|---------------------|---------------------------|---------|--------------------------|--------------------------------|

| Attribute                 | Min (V)                                     | Nom (V) | Max (V) | Min (V)             | Nom (V)                   | Max (V) | Max (V)                  | Min (V)                        |

| LVTTL                     | 3.0                                         | 3.3     | 3.465   |                     |                           |         | 0.8                      | 2.0                            |

| LVCMOS33 <sup>(4)</sup>   | 3.0                                         | 3.3     | 3.465   |                     |                           |         | 0.8                      | 2.0                            |

| LVCMOS25 <sup>(4,5)</sup> | 2.3                                         | 2.5     | 2.7     |                     |                           |         | 0.7                      | 1.7                            |

| LVCMOS18                  | 1.65                                        | 1.8     | 1.95    | V <sub>R</sub>      | <sub>FF</sub> is not used | d for   | 0.4                      | 0.8                            |

| LVCMOS15                  | 1.4                                         | 1.5     | 1.6     | these I/O standards |                           |         | 0.4                      | 0.8                            |

| LVCMOS12                  | 1.1                                         | 1.2     | 1.3     |                     |                           |         | 0.4                      | 0.7                            |

| PCI33_3 <sup>(6)</sup>    | 3.0                                         | 3.3     | 3.465   |                     |                           |         | 0.3 • V <sub>CCO</sub>   | 0.5 • V <sub>CCO</sub>         |

| PCI66_3 <sup>(6)</sup>    | 3.0                                         | 3.3     | 3.465   |                     |                           |         | 0.3 • V <sub>CCO</sub>   | 0.5 • V <sub>CCO</sub>         |

| HSTL_I_18                 | 1.7                                         | 1.8     | 1.9     | 0.8                 | 0.9                       | 1.1     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1         |

| HSTL_III_18               | 1.7                                         | 1.8     | 1.9     | -                   | 1.1                       | -       | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1         |

| SSTL18_I                  | 1.7                                         | 1.8     | 1.9     | 0.833               | 0.900                     | 0.969   | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125       |

| SSTL2_I                   | 2.3                                         | 2.5     | 2.7     | 1.15                | 1.25                      | 1.35    | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125       |

#### Notes:

- Descriptions of the symbols used in this table are as follows: 1.

- $\begin{array}{l} V_{CCO} \mbox{the symbols dised in this table are as follows.} \\ V_{CCO} \mbox{the supply voltage for output drivers} \\ V_{REF} \mbox{the reference voltage for setting the input switching threshold} \\ V_{IL} \mbox{the input voltage that indicates a Low logic level} \\ V_{IH} \mbox{the input voltage that indicates a High logic level} \end{array}$

- The V<sub>CCO</sub> rails supply only output drivers, not input circuits. 2.

- For device operation, the maximum signal voltage (V<sub>IH</sub> max) may be as high as V<sub>IN</sub> max. See Table 73. З.

- There is approximately 100 mV of hysteresis on inputs using LVCMOS33 and LVCMOS25 I/O standards. 4.

- All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) use the LVCMOS25 standard and draw power from the V<sub>CCAUX</sub> rail (2.5V). The Dual-Purpose configuration pins use the LVCMOS standard before the User mode. When using these pins as part of a standard 2.5V 5. configuration interface, apply 2.5V to the V<sub>CCO</sub> lines of Banks 0, 1, and 2 at power-on as well as throughout configuration.

- For information on PCI IP solutions, see www.xilinx.com/pci. The PCIX IOSTANDARD is available and has equivalent characteristics but no 6. PCI-X IP is supported.

# I/O Timing

#### Table 86: Pin-to-Pin Clock-to-Output Times for the IOB Output Path

|                       |                                                                                                     |                                                          |           | Speed Grade        |                    |       |

|-----------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------|--------------------|--------------------|-------|

| Symbol                | Description                                                                                         | Conditions                                               | Device    | -5                 | -4                 | Units |

|                       |                                                                                                     |                                                          |           | Max <sup>(2)</sup> | Max <sup>(2)</sup> |       |

| Clock-to-Outp         | out Times                                                                                           |                                                          |           |                    |                    |       |

| T <sub>ICKOFDCM</sub> | When reading from the Output Flip-Flop                                                              | LVCMOS25 <sup>(3)</sup> , 12 mA                          | XC3S100E  | 2.66               | 2.79               | ns    |

|                       |                                                                                                     | output drive, Fast slew<br>rate, with DCM <sup>(4)</sup> | XC3S250E  | 3.00               | 3.45               | ns    |

|                       |                                                                                                     |                                                          | XC3S500E  | 3.01               | 3.46               | ns    |

|                       |                                                                                                     |                                                          | XC3S1200E | 3.01               | 3.46               | ns    |

|                       |                                                                                                     |                                                          | XC3S1600E | 3.00               | 3.45               | ns    |

| T <sub>ICKOF</sub>    | When reading from OFF, the time from the                                                            | LVCMOS25 <sup>(3)</sup> , 12 mA                          | XC3S100E  | 5.60               | 5.92               | ns    |

|                       | active transition on the Global Clock pin to data appearing at the Output pin. The DCM is not used. | output drive, Fast slew rate, without DCM                | XC3S250E  | 4.91               | 5.43               | ns    |

|                       |                                                                                                     |                                                          | XC3S500E  | 4.98               | 5.51               | ns    |

|                       |                                                                                                     |                                                          | XC3S1200E | 5.36               | 5.94               | ns    |

|                       |                                                                                                     |                                                          | XC3S1600E | 5.45               | 6.05               | ns    |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77 and Table 80.

- 2. For minimums, use the values reported by the Xilinx timing analyzer.

- 3. This clock-to-output time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or a standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. If the former is true, *add* the appropriate Input adjustment from Table 91. If the latter is true, *add* the appropriate Output adjustment from Table 94.

- 4. DCM output jitter is included in all measurements.

|                                                                                                           |                                                                      |                                               | IFD      |           | Speed | Grade |       |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------|----------|-----------|-------|-------|-------|

| Symbol                                                                                                    | Description                                                          | Conditions                                    | DELAY_   | Device    | -5    | -4    | Units |

|                                                                                                           |                                                                      |                                               | VALUE=   |           | Min   | Min   |       |

| Setup Tim                                                                                                 | ies                                                                  |                                               |          |           |       |       |       |

| T <sub>PSDCM</sub>                                                                                        | When writing to the Input                                            | LVCMOS25 <sup>(2)</sup> ,                     | 0        | XC3S100E  | 2.65  | 2.98  | ns    |

|                                                                                                           | Flip-Flop (IFF), the time from the setup of data at the Input pin to | IFD_DELAY_VALUE = 0, with DCM <sup>(3)</sup>  |          | XC3S250E  | 2.25  | 2.59  | ns    |

|                                                                                                           | the active transition at a Global                                    |                                               |          | XC3S500E  | 2.25  | 2.59  | ns    |

|                                                                                                           | Clock pin. The DCM is used. No Input Delay is programmed.            |                                               |          | XC3S1200E | 2.25  | 2.58  | ns    |

|                                                                                                           |                                                                      |                                               |          | XC3S1600E | 2.25  | 2.59  | ns    |

| T <sub>PSFD</sub>                                                                                         | When writing to IFF, the time                                        | LVCMOS25 <sup>(2)</sup> ,                     | 2        | XC3S100E  | 3.16  | 3.58  | ns    |

| from the setup of data at the<br>Input pin to an active transition at<br>the Global Clock pin. The DCM is | IFD_DELAY_VALUE = default software setting                           | 3                                             | XC3S250E | 3.44      | 3.91  | ns    |       |

|                                                                                                           | the Global Clock pin. The DCM is not used. The Input Delay is        |                                               | 3        | XC3S500E  | 4.00  | 4.73  | ns    |

|                                                                                                           | programmed.                                                          |                                               | 3        | XC3S1200E | 2.60  | 3.31  | ns    |

|                                                                                                           |                                                                      |                                               | 3        | XC3S1600E | 3.33  | 3.77  | ns    |

| Hold Time                                                                                                 | es                                                                   |                                               |          |           |       |       |       |

| T <sub>PHDCM</sub>                                                                                        | When writing to IFF, the time                                        | LVCMOS25 <sup>(4)</sup> ,                     | 0        | XC3S100E  | -0.54 | -0.52 | ns    |

|                                                                                                           | from the active transition at the Global Clock pin to the point      | IFD_DELAY_VALUE = 0, with $DCM^{(3)}$         |          | XC3S250E  | 0.06  | 0.14  | ns    |

|                                                                                                           | when data must be held at the<br>Input pin. The DCM is used. No      |                                               |          | XC3S500E  | 0.07  | 0.14  | ns    |

|                                                                                                           | Input Delay is programmed.                                           |                                               |          | XC3S1200E | 0.07  | 0.15  | ns    |

|                                                                                                           |                                                                      |                                               |          | XC3S1600E | 0.06  | 0.14  | ns    |

| T <sub>PHFD</sub>                                                                                         | When writing to IFF, the time                                        | LVCMOS25 <sup>(4)</sup> ,                     | 2        | XC3S100E  | -0.31 | -0.24 | ns    |

|                                                                                                           | from the active transition at the<br>Global Clock pin to the point   | IFD_DELAY_VALUE =<br>default software setting | 3        | XC3S250E  | -0.32 | -0.32 | ns    |

|                                                                                                           | when data must be held at the Input pin. The DCM is not used.        | 3                                             | 3        | XC3S500E  | -0.77 | -0.77 | ns    |

|                                                                                                           | The Input Delay is programmed.                                       |                                               | 3        | XC3S1200E | 0.13  | 0.16  | ns    |

|                                                                                                           |                                                                      |                                               | 3        | XC3S1600E | -0.05 | -0.03 | ns    |

#### Table 87: Pin-to-Pin Setup and Hold Times for the IOB Input Path (System Synchronous)

Notes:

1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77 and Table 80.

2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, subtract the appropriate adjustment from Table 91. If this is true of the data Input, add the appropriate Input adjustment from the same table.

3. DCM output jitter is included in all measurements.

4. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, add the appropriate Input adjustment from Table 91. If this is true of the data Input, subtract the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock's active edge.

# Block RAM Timing

### Table 103: Block RAM Timing

| Symbol            | Description                                                                                                                                                            |      | -5   | -4   |      | Units |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

|                   |                                                                                                                                                                        | Min  | Max  | Min  | Мах  |       |

| Clock-to-O        | utput Times                                                                                                                                                            |      |      |      |      |       |

| Т <sub>ВСКО</sub> | When reading from block RAM, the delay from the active transition at the CLK input to data appearing at the DOUT output                                                | -    | 2.45 | -    | 2.82 | ns    |

| Setup Time        | es l                                                                                                                                                                   |      |      |      |      | -     |

| T <sub>BACK</sub> | Setup time for the ADDR inputs before the active transition at the CLK input of the block RAM                                                                          | 0.33 | -    | 0.38 | -    | ns    |

| T <sub>BDCK</sub> | Setup time for data at the DIN inputs before the active transition at the CLK input of the block RAM                                                                   | 0.23 | -    | 0.23 | -    | ns    |

| T <sub>BECK</sub> | Setup time for the EN input before the active transition at the CLK input of the block RAM                                                                             | 0.67 | -    | 0.77 | -    | ns    |

| T <sub>BWCK</sub> | Setup time for the WE input before the active transition at the CLK input of the block RAM                                                                             | 1.09 | -    | 1.26 | -    | ns    |

| Hold Times        | ;<br>;                                                                                                                                                                 |      | 1    |      |      |       |

| T <sub>BCKA</sub> | Hold time on the ADDR inputs after the active transition at the CLK input                                                                                              | 0.12 | -    | 0.14 | -    | ns    |

| T <sub>BCKD</sub> | Hold time on the DIN inputs after the active transition at the CLK input                                                                                               | 0.12 | -    | 0.13 | -    | ns    |

| T <sub>BCKE</sub> | Hold time on the EN input after the active transition at the CLK input                                                                                                 | 0    | -    | 0    | -    | ns    |

| T <sub>BCKW</sub> | Hold time on the WE input after the active transition at the $\ensuremath{CLK}$ input                                                                                  | 0    | -    | 0    | -    | ns    |

| Clock Timi        | ng                                                                                                                                                                     |      |      |      |      | -     |

| T <sub>BPWH</sub> | High pulse width of the CLK signal                                                                                                                                     | 1.39 | -    | 1.59 | -    | ns    |

| T <sub>BPWL</sub> | Low pulse width of the CLK signal                                                                                                                                      | 1.39 | -    | 1.59 | -    | ns    |

| Clock Freq        | uency                                                                                                                                                                  |      |      |      |      |       |

| F <sub>BRAM</sub> | Block RAM clock frequency. RAM read output value written<br>back into RAM, for shift-registers and circular buffers.<br>Write-only or read-only performance is faster. | 0    | 270  | 0    | 230  | MHz   |

Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 77.

www.xilinx.com

# Spartan-3 FPGA Family: Pinout Descriptions

DS312 (4.0) October 29, 2012

#### **Product Specification**

# Introduction

This section describes the various pins on a Spartan®-3E FPGA and how they connect within the supported component packages.

# **Pin Types**

Most pins on a Spartan-3E FPGA are general-purpose, user-defined I/O pins. There are, however, up to 11 different functional types of pins on Spartan-3E packages, as outlined in Table 124. In the package footprint drawings that follow, the individual pins are color-coded according to pin type as in the table.

| Type / Color<br>Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin Name(s) in Type <sup>(1)</sup>                                                                                                                                             |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O                  | Unrestricted, general-purpose user-I/O pin. Most pins can be paired together to form differential I/Os.                                                                                                                                                                                                                                                                                                                                                                                                                           | IO<br>IO_Lxxy_#                                                                                                                                                                |

| INPUT                | Unrestricted, general-purpose input-only pin. This pin does not have an output structure, differential termination resistor, or PCI clamp diode.                                                                                                                                                                                                                                                                                                                                                                                  | IP<br>IP_Lxxy_#                                                                                                                                                                |

| DUAL                 | Dual-purpose pin used in some configuration modes during the configuration<br>process and then usually available as a user I/O after configuration. If the pin is not<br>used during configuration, this pin behaves as an I/O-type pin. Some of the<br>dual-purpose pins are also shared with bottom-edge global (GCLK) or right-half<br>(RHCLK) clock inputs. See the Configuration section in Module 2 for additional<br>information on these signals.                                                                         | M[2:0]<br>HSWAP<br>CCLK<br>MOSI/CSI_B<br>D[7:1]<br>D0/DIN<br>CSO_B<br>RDWR_B<br>BUSY/DOUT<br>INIT_B<br>A[23:20]<br>A19/VS2<br>A18/VS1<br>A17/VS0<br>A[16:0]<br>LDC[2:0]<br>HDC |

| VREF                 | Dual-purpose pin that is either a user-I/O pin or Input-only pin, or, along with all other VREF pins in the same bank, provides a reference voltage input for certain I/O standards. If used for a reference voltage within a bank, all VREF pins within the bank must be connected.                                                                                                                                                                                                                                              | IP/VREF_#<br>IP_Lxxy_#/VREF_#<br>IO/VREF_#<br>IO_Lxxy_#/VREF_#                                                                                                                 |

| CLK                  | Either a user-I/O pin or Input-only pin, or an input to a specific clock buffer driver.<br>Every package has 16 global clock inputs that optionally clock the entire device. The<br>RHCLK inputs optionally clock the right-half of the device. The LHCLK inputs<br>optionally clock the left-half of the device. Some of the clock pins are shared with the<br>dual-purpose configuration pins and are considered DUAL-type. See the Clocking<br>Infrastructure section in Module 2 for additional information on these signals. | IO_Lxxy_#/GCLK[15:10, 7:2]<br>IP_Lxxy_#/GCLK[9:8, 1:0]<br>IO_Lxxy_#/LHCLK[7:0]<br>IO_Lxxy_#/RHCLK[7:0]                                                                         |

| CONFIG               | Dedicated configuration pin. Not available as a user-I/O pin. Every package has two dedicated configuration pins. These pins are powered by VCCAUX. See the Configuration section in Module 2 for details.                                                                                                                                                                                                                                                                                                                        | DONE, PROG_B                                                                                                                                                                   |

| JTAG                 | Dedicated JTAG pin. Not available as a user-I/O pin. Every package has four dedicated JTAG pins. These pins are powered by VCCAUX.                                                                                                                                                                                                                                                                                                                                                                                                | TDI, TMS, TCK, TDO                                                                                                                                                             |

| GND                  | Dedicated ground pin. The number of GND pins depends on the package used. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                  | GND                                                                                                                                                                            |

#### Table 124: Types of Pins on Spartan-3E FPGAs

© Copyright 2005–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

www.xilinx.com

#### Table 124: Types of Pins on Spartan-3E FPGAs (Cont'd)

| Type / Color<br>Code | Description                                                                                                                                                                                                                                            | Pin Name(s) in Type <sup>(1)</sup> |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|

| VCCAUX               | Dedicated auxiliary power supply pin. The number of VCCAUX pins depends on the package used. All must be connected to +2.5V. See the Powering Spartan-3E FPGAs section in Module 2 for details.                                                        | VCCAUX                             |  |  |  |

| VCCINT               | Dedicated internal core logic power supply pin. The number of VCCINT pins depends on the package used. All must be connected to +1.2V. See the Powering Spartan-3E FPGAs section in Module 2 for details.                                              | VCCINT                             |  |  |  |

| VCCO                 | Along with all the other VCCO pins in the same bank, this pin supplies power to the output buffers within the I/O bank and sets the input threshold voltage for some I/O standards. See the Powering Spartan-3E FPGAs section in Module 2 for details. | VCCO_#                             |  |  |  |

| N.C.                 | This package pin is not connected in this specific device/package combination but may be connected in larger devices in the same package.                                                                                                              | N.C.                               |  |  |  |

#### Notes:

- 1. # = I/O bank number, an integer between 0 and 3.

- 2. IRDY/TRDY designations are for PCI designs; refer to PCI documentation for details.

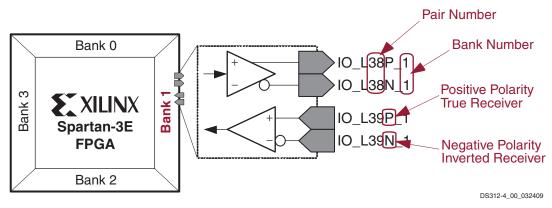

# **Differential Pair Labeling**

I/Os with Lxxy\_# are part of a differential pair. 'L' indicates differential capability. The 'xx' field is a two-digit integer, unique to each bank that identifies a differential pin-pair. The 'y' field is either 'P' for the true signal or 'N' for the inverted signal in the differential pair. The '#' field is the I/O bank number.

The pin name suffix has the following significance. Figure 79 provides a specific example showing a differential input to and a differential output from Bank 1. 'L' indicates that the pin is part of a differential pair.

'xx' is a two-digit integer, unique for each bank, that identifies a differential pin-pair.

'y' is replaced by 'P' for the true signal or 'N' for the inverted. These two pins form one differential pin-pair.

'#' is an integer, 0 through 3, indicating the associated  $\ensuremath{\mathsf{I/O}}$  bank.

Figure 79: Differential Pair Labeling

# **Mechanical Drawings**

Material Declaration Data Sheets (MDDS) are also available on the <u>Xilinx web site</u> for each package.

Detailed mechanical drawings for each package type are available from the Xilinx® web site at the specified location in Table 127.

| Package | Package Drawing | MDDS         |

|---------|-----------------|--------------|

| VQ100   | Package Drawing | PK173_VQ100  |

| VQG100  |                 | PK130_VQG100 |

| CP132   | Package Drawing | PK147_CP132  |

| CPG132  |                 | PK101_CPG132 |

| TQ144   | Package Drawing | PK169_TQ144  |

| TQG144  |                 | PK126_TQG144 |

| PQ208   | Package Drawing | PK166_PQ208  |

| PQG208  |                 | PK123_PQG208 |

| FT256   | Package Drawing | PK158_FT256  |

| FTG256  |                 | PK115_FTG256 |

| FG320   | Package Drawing | PK152_FG320  |

| FGG320  |                 | PK106_FGG320 |

| FG400   | Package Drawing | PK182_FG400  |

| FGG400  |                 | PK108_FGG400 |

| FG484   | Package Drawing | PK183_FG484  |

| FGG484  |                 | PK110_FGG484 |

# Package Pins by Type

Each package has three separate voltage supply inputs—VCCINT, VCCAUX, and VCCO—and a common ground return, GND. The numbers of pins dedicated to these functions vary by package, as shown in Table 128.

| Package | VCCINT | VCCAUX | VCCO | GND |  |  |  |

|---------|--------|--------|------|-----|--|--|--|

| VQ100   | 4      | 4      | 8    | 12  |  |  |  |

| CP132   | 6      | 4      | 8    | 16  |  |  |  |

| TQ144   | 4      | 4      | 9    | 13  |  |  |  |

| PQ208   | 4      | 8      | 12   | 20  |  |  |  |

| FT256   | 8      | 8      | 16   | 28  |  |  |  |

| FG320   | 8      | 8      | 20   | 28  |  |  |  |

| FG400   | 16     | 8      | 24   | 42  |  |  |  |

| FG484   | 16     | 10     | 28   | 48  |  |  |  |

A majority of package pins are user-defined I/O or input pins. However, the numbers and characteristics of these I/O depend on the device type and the package in which it is available, as shown in Table 129. The table shows the maximum number of single-ended I/O pins available, assuming that all I/O-, INPUT-, DUAL-, VREF-, and CLK-type pins are used as general-purpose I/O. Likewise, the table shows the maximum number of differential pin-pairs available on the package. Finally, the table shows how the total maximum user-I/Os are distributed by pin type, including the number of unconnected—i.e., N.C.—pins on the device.

### Table 137: TQ144 Package Pinout (Cont'd)

| Bank   | XC3S100E Pin Name | XC3S250E Pin Name | TQ144 Pin | Туре   |

|--------|-------------------|-------------------|-----------|--------|

| GND    | GND               | GND               | P27       | GND    |

| GND    | GND               | GND               | P37       | GND    |

| GND    | GND               | GND               | P46       | GND    |

| GND    | GND               | GND               | P55       | GND    |

| GND    | GND               | GND               | P61       | GND    |

| GND    | GND               | GND               | P73       | GND    |

| GND    | GND               | GND               | P90       | GND    |

| GND    | GND               | GND               | P99       | GND    |

| GND    | GND               | GND               | P118      | GND    |

| GND    | GND               | GND               | P127      | GND    |

| GND    | GND               | GND               | P133      | GND    |

| VCCAUX | DONE              | DONE              | P72       | CONFIG |

| VCCAUX | PROG_B            | PROG_B            | P1        | CONFIG |

| VCCAUX | ТСК               | ТСК               | P110      | JTAG   |

| VCCAUX | TDI               | TDI               | P144      | JTAG   |

| VCCAUX | TDO               | TDO               | P109      | JTAG   |

| VCCAUX | TMS               | TMS               | P108      | JTAG   |

| VCCAUX | VCCAUX            | VCCAUX            | P30       | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX            | P65       | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX            | P102      | VCCAUX |

| VCCAUX | VCCAUX            | VCCAUX            | P137      | VCCAUX |

| VCCINT | VCCINT            | VCCINT            | P9        | VCCINT |

| VCCINT | VCCINT            | VCCINT            | P45       | VCCINT |

| VCCINT | VCCINT            | VCCINT            | P80       | VCCINT |

| VCCINT | VCCINT            | VCCINT            | P115      | VCCINT |

### Table 148: FG320 Package Pinout (Cont'd)

| Bank | XC3S500E Pin Name | XC3S1200E Pin Name | XC3S1600E Pin Name | FG320<br>Ball | Туре                                      |

|------|-------------------|--------------------|--------------------|---------------|-------------------------------------------|

| 1    | IO_L17N_1         | IO_L17N_1          | IO_L17N_1          | H15           | I/O                                       |

| 1    | IO_L17P_1         | IO_L17P_1          | IO_L17P_1          | H14           | I/O                                       |

| 1    | IO_L18N_1         | IO_L18N_1          | IO_L18N_1          | G16           | I/O                                       |

| 1    | IO_L18P_1         | IO_L18P_1          | IO_L18P_1          | G15           | I/O                                       |

| 1    | IO_L19N_1         | IO_L19N_1          | IO_L19N_1          | F17           | I/O                                       |

| 1    | IO_L19P_1         | IO_L19P_1          | IO_L19P_1          | F18           | I/O                                       |

| 1    | IO_L20N_1         | IO_L20N_1          | IO_L20N_1          | G13           | I/O                                       |

| 1    | IO_L20P_1         | IO_L20P_1          | IO_L20P_1          | G14           | I/O                                       |

| 1    | IO_L21N_1         | IO_L21N_1          | IO_L21N_1          | F14           | I/O                                       |

| 1    | IO_L21P_1         | IO_L21P_1          | IO_L21P_1          | F15           | I/O                                       |

| 1    | N.C. ( <b>♦</b> ) | IO_L22N_1          | IO_L22N_1          | E16           | 500E: N.C.<br>1200E: I/O<br>1600E: I/O    |

| 1    | N.C. (�)          | IO_L22P_1          | IO_L22P_1          | E15           | 500E: N.C.<br>1200E: I/O<br>1600E: I/O    |

| 1    | IO_L23N_1/LDC0    | IO_L23N_1/LDC0     | IO_L23N_1/LDC0     | D16           | DUAL                                      |

| 1    | IO_L23P_1/HDC     | IO_L23P_1/HDC      | IO_L23P_1/HDC      | D17           | DUAL                                      |

| 1    | IO_L24N_1/LDC2    | IO_L24N_1/LDC2     | IO_L24N_1/LDC2     | C17           | DUAL                                      |

| 1    | IO_L24P_1/LDC1    | IO_L24P_1/LDC1     | IO_L24P_1/LDC1     | C18           | DUAL                                      |

| 1    | IP                | IP                 | IP                 | B18           | INPUT                                     |

| 1    | Ю                 | IP                 | IP                 | E17           | 500E: I/O<br>1200E: INPUT<br>1600E: INPUT |

| 1    | IP                | IP                 | IP                 | E18           | INPUT                                     |

| 1    | IP                | IP                 | IP                 | G18           | INPUT                                     |

| 1    | IP                | IP                 | IP                 | H13           | INPUT                                     |

| 1    | IP                | IP                 | IP                 | K17           | INPUT                                     |

| 1    | IP                | IP                 | IP                 | K18           | INPUT                                     |

| 1    | IP                | IP                 | IP                 | L13           | INPUT                                     |

| 1    | IP                | IP                 | IP                 | L14           | INPUT                                     |

| 1    | IP                | IP                 | IP                 | N17           | INPUT                                     |

| 1    | Ю                 | IP                 | IP                 | P15           | 500E: I/O<br>1200E: INPUT<br>1600E: INPUT |

| 1    | IP                | IP                 | IP                 | R17           | INPUT                                     |

| 1    | IP/VREF_1         | IP/VREF_1          | IP/VREF_1          | D18           | VREF                                      |

| 1    | IP/VREF_1         | IP/VREF_1          | IP/VREF_1          | H18           | VREF                                      |

| 1    | VCCO_1            | VCCO_1             | VCCO_1             | F16           | VCCO                                      |

| 1    | VCCO_1            | VCCO_1             | VCCO_1             | H12           | VCCO                                      |

| 1    | VCCO_1            | VCCO_1             | VCCO_1             | J18           | VCCO                                      |

| 1    | VCCO_1            | VCCO_1             | VCCO_1             | L12           | VCCO                                      |

| 1    | VCCO_1            | VCCO_1             | VCCO_1             | N16           | VCCO                                      |

| 2    | IO                | Ю                  | IO                 | P9            | I/O                                       |

| 2    | 10                | 10                 | IO                 | R11           | I/O                                       |

|                                     | Bank 0                            |                                |                                        |                                      |                                       |                             |                                    |                                    |                                      |               |

|-------------------------------------|-----------------------------------|--------------------------------|----------------------------------------|--------------------------------------|---------------------------------------|-----------------------------|------------------------------------|------------------------------------|--------------------------------------|---------------|

| 11                                  | 12                                | 13                             | 14                                     | 15                                   | 16                                    | 17                          | 18                                 | 19                                 | 20                                   | 1             |

| GND                                 | I/O                               | <b>I/O</b><br>L09N_0<br>VREF_0 | <b>I/O</b><br>L09P_0                   | <b>I/O</b><br>L06N_0                 | <b>I/O</b><br>L04P_0                  | <b>I/O</b><br>L04N_0        | <b>I/O</b><br>L03N_0<br>VREF_0     | <b>I/O</b><br>L03P_0               | GND                                  | Α             |

| INPUT<br>L14N_0                     | INPUT<br>L14P_0                   | <b>I/O</b><br>L10N_0           | GND                                    | <b>I/O</b><br>L06P_0                 | VCCO_0                                | <b>I/O</b><br>L01N_0        | INPUT                              | TDO                                | INPUT                                | В             |

| I/O<br>VREF_0                       | <b>I/O</b><br>L12N_0              | <b>I/O</b><br>L10P_0           | <b>I/O</b><br>L07N_0                   | INPUT<br>L05P_0                      | INPUT<br>L02N_0                       | <b>I/O</b><br>L01P_0        | GND                                | <b>I/O</b><br>L30N_1<br>LDC2       | <b>I/O</b><br>L30P_1<br>LDC1         | с             |

| VCCAUX                              | <b>I/O</b><br>L12P_0              | VCCO_0                         | <b>I/O</b><br>L07P_0                   | INPUT<br>L05N_0                      | INPUT<br>L02P_0                       | тск                         | <b>I/O</b><br>L29N_1<br>LDC0       | VCCO_1                             | <b>I/O</b><br>L28N_1                 | D             |

| <b>I/O</b><br>L16P_0<br>GCLK6       | <b>I/O</b><br>L13N_0              | I/O                            | INPUT<br>L08N_0                        | INPUT<br>L08P_0                      | I/O                                   | TMS                         | <b>I/O</b><br>L29P_1<br>HDC        | INPUT<br>VREF_1                    | <b>I/O</b><br>L28P_1                 | E             |

| <b>I/O</b><br>L15P_0<br>GCLK4       | <b>I/O</b><br>L13P_0              | I/O                            | I/O                                    | GND                                  | <b>I/O</b><br>L25P_1                  | <b>I/O</b><br>L27P_1        | <b>I/O</b><br>L27N_1               | <b>I/O</b><br>L26N_1               | <b>I/O</b><br>L26P_1                 | F             |

| <b>I/O</b><br>L15N_0<br>GCLK5       | GND                               | INPUT<br>L11P_0                | INPUT<br>L11N_0                        | INPUT                                | <b>I/O</b><br>L25N_1                  | VCCO_1                      | INPUT                              | GND                                | <b>I/O</b><br>L24P_1                 | G             |

| VCCINT                              | VCCAUX                            | VCCINT                         | INPUT                                  | <b>I/O</b><br>L22N_1                 | <b>I/O</b><br>L22P_1                  | <b>I/O</b><br>L23P_1        | <b>I/O</b><br>L23N_1               | <b>I/O</b><br>L21N_1               | <b>I/O</b><br>L24N_1<br>VREF_1       | н             |

| GND                                 | VCCINT                            | <b>I/O</b><br>L19N_1<br>A0     | <b>I/O</b><br>L19P_1                   | INPUT                                | <b>I/O</b><br>L18P_1<br>A2            | <b>I/O</b><br>L20N_1        | <b>I/O</b><br>L20P_1               | <b>I/O</b><br>L21P_1               | I/O<br>L17N_1<br>A3<br>RHCLK7        | J             |

| VCCINT                              | GND                               | L16P_1<br>A6<br>RHCLK4         | I/O<br>L16N_1<br>A5<br>RHCLK5          | VCCO_1                               | <b>I/O</b><br>L18N_1<br>A1            | GND                         | INPUT<br>VREF_1                    | VCCO_1                             | <b>I/O</b><br>L17P_1<br>A4<br>RHCLK6 | K F           |

| GND                                 | VCCINT                            | GND                            | I/O<br>L15N_1<br>A7<br>RHCLK3<br>TRDY1 | <b>I/O</b><br>L15P_1<br>A8<br>RHCLK2 | <b>I/O</b><br>L14N_1<br>A9<br>RHCLK1  | VCCAUX                      | INPUT                              | <b>I/O</b><br>L13N_1<br>VREF_1     | GND                                  | л<br>Bank     |

| VCCINT                              | GND                               | VCCINT                         | VCCAUX                                 | <b>I/O</b><br>L11P_1                 | <b>I/O</b><br>L14P_1<br>A10<br>RHCLK0 | <b>I/O</b><br>L12P_1<br>A12 | <b>I/O</b><br>L12N_1<br>A11        | <b>I/O</b><br>L13P_1               | INPUT                                | М             |

| <b>I/O</b><br>D5                    | VCCINT                            | GND                            | INPUT                                  | <b>I/O</b><br>L11N_1                 | <b>I/O</b><br>L09P_1                  | VCCO_1                      | <b>I/O</b><br>L10P_1               | <b>I/O</b><br>L10N_1               | INPUT                                | N             |

| INPUT<br>L17P_2<br>RDWR_B<br>GCLK0  | INPUT<br>L17N_2<br>M2<br>GCLK1    | I/O                            | <b>I/O</b><br>L25N_2                   | INPUT                                | <b>I/O</b><br>L09N_1                  | <b>I/O</b><br>L07P_1        | <b>I/O</b><br>L07N_1               | GND                                | <b>I/O</b><br>L08N_1<br>VREF_1       | Ρ             |

| VCCO_2                              | INPUT<br>L20P_2                   | 1/0                            | <b>I/O</b><br>L25P_2                   | GND                                  | INPUT                                 | <b>I/O</b><br>L05P_1        | <b>I/O</b><br>L05N_1               | INPUT                              | <b>I/O</b><br>L08P_1                 | R             |

| <b>I/O</b><br>M1                    | INPUT<br>L20N_2                   | INPUT<br>L23N_2<br>VREF_2      | INPUT<br>L23P_2                        | <b>I/O</b><br>L28N_2                 | INPUT                                 | <b>I/O</b><br>L02P_1<br>A14 | <b>I/O</b><br>L02N_1<br>A13        | VCCO_1                             | <b>I/O</b><br>L06N_1                 | т             |

| GND                                 | <b>I/O</b><br>L21N_2              | <b>I/O</b><br>L24N_2           | VCCO_2                                 | <b>I/O</b><br>L28P_2                 | <b>I/O</b><br>L30P_2<br>A21           | <b>I/O</b><br>L01P_1<br>A16 | <b>I/O</b><br>L01N_1<br>A15        | <b>I/O</b><br>L03P_1               | <b>I/O</b><br>L06P_1                 | U             |

| <b>I/O</b><br>L18N_2<br>D1<br>GCLK3 | <b>I/O</b><br>L21P_2              | <b>I/O</b><br>L24P_2           | INPUT<br>L26N_2                        | INPUT<br>L26P_2                      | <b>I/O</b><br>L30N_2<br>A20           | DONE                        | GND                                | <b>I/O</b><br>L03N_1<br>VREF_1     | <b>I/O</b><br>L04P_1                 | v             |

| VCCO_2                              | <b>I/O</b><br>L22N_2<br>VREF_2    | <b>I/O</b><br>L22P_2           | GND                                    | I/O                                  | INPUT<br>L29N_2                       | VCCO_2                      | <b>I/O</b><br>L31P_2<br>VS2<br>A19 | <b>I/O</b><br>L32N_2<br>CCLK       | <b>I/O</b><br>L04N_1                 | w             |

| <b>I/O</b><br>L19P_2<br>M0          | <b>I/O</b><br>L19N_2<br>DIN<br>D0 | 1/0                            | <b>I/O</b><br>L27N_2<br>A22            | <b>I/O</b><br>L27P_2<br>A23          | INPUT<br>L29P_2                       | <b>I/O</b><br>VREF_2        | <b>I/O</b><br>L31N_2<br>VS1<br>A18 | <b>I/O</b><br>L32P_2<br>VS0<br>A17 | GND                                  | Y             |

|                                     | Bank 2                            |                                |                                        |                                      |                                       |                             |                                    |                                    | DS31                                 | 2-4_09_101905 |

# **FG400 Footprint**

**Right Half of Package** (top view)

www.xilinx.com

#### Table 155: User I/Os Per Bank for the XC3S1600E in the FG484 Package

| Package | 1/O Bank | Maximum I/O |     | All Po | ssible I/O Pins b | у Туре              |                    |

|---------|----------|-------------|-----|--------|-------------------|---------------------|--------------------|

| Edge    | I/O Bank | Maximum I/O | I/O | INPUT  | DUAL              | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> |

| Тор     | 0        | 94          | 56  | 22     | 1                 | 7                   | 8                  |