Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Active                                                       |

| Number of LABs/CLBs            | 240                                                          |

| Number of Logic Elements/Cells | 2160                                                         |

| Total RAM Bits                 | 73728                                                        |

| Number of I/O                  | 66                                                           |

| Number of Gates                | 100000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 100-TQFP                                                     |

| Supplier Device Package        | 100-VQFP (14x14)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s100e-4vq100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Architectural Overview**

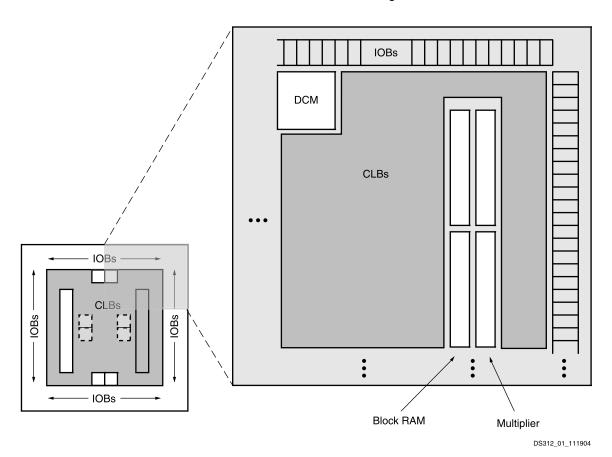

The Spartan-3E family architecture consists of five fundamental programmable functional elements:

- Configurable Logic Blocks (CLBs) contain flexible Look-Up Tables (LUTs) that implement logic plus storage elements used as flip-flops or latches. CLBs perform a wide variety of logical functions as well as store data.

- Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3-state operation. Supports a variety of signal standards, including four high-performance differential standards. Double Data-Rate (DDR) registers are included.

- Block RAM provides data storage in the form of 18-Kbit dual-port blocks.

- Multiplier Blocks accept two 18-bit binary numbers as inputs and calculate the product.

Digital Clock Manager (DCM) Blocks provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase-shifting clock signals.

These elements are organized as shown in Figure 1. A ring of IOBs surrounds a regular array of CLBs. Each device has two columns of block RAM except for the XC3S100E, which has one column. Each RAM column consists of several 18-Kbit RAM blocks. Each block RAM is associated with a dedicated multiplier. The DCMs are positioned in the center with two at the top and two at the bottom of the device. The XC3S100E has only one DCM at the top and bottom, while the XC3S1200E and XC3S1600E add two DCMs in the middle of the left and right sides.

The Spartan-3E family features a rich network of traces that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

Figure 1: Spartan-3E Family Architecture

### **Double-Data-Rate Transmission**

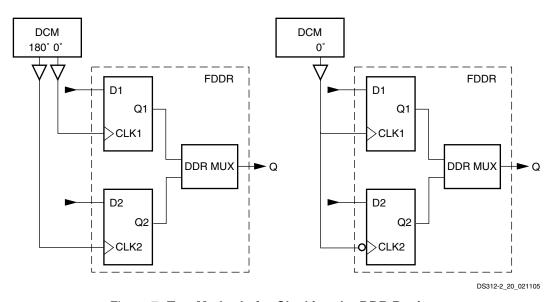

Double-Data-Rate (DDR) transmission describes the technique of synchronizing signals to both the rising and falling edges of the clock signal. Spartan-3E devices use register pairs in all three IOB paths to perform DDR operations.

The pair of storage elements on the IOB's Output path (OFF1 and OFF2), used as registers, combine with a special multiplexer to form a DDR D-type flip-flop (ODDR2). This primitive permits DDR transmission where output data bits are synchronized to both the rising and falling edges of a clock. DDR operation requires two clock signals (usually 50% duty cycle), one the inverted form of the other. These signals trigger the two registers in alternating fashion, as shown in Figure 7. The Digital Clock Manager (DCM) generates the two clock signals by mirroring an incoming signal, and then shifting it 180 degrees. This approach ensures minimal skew between the two signals. Alternatively, the inverter inside the IOB can be used to invert the clock signal, thus only using one clock line and both rising and falling edges of that clock line as the two clocks for the DDR flip-flops.

The storage-element pair on the Three-State path (TFF1 and TFF2) also can be combined with a local multiplexer to form a DDR primitive. This permits synchronizing the output enable to both the rising and falling edges of a clock. This DDR operation is realized in the same way as for the output path.

The storage-element pair on the input path (IFF1 and IFF2) allows an I/O to receive a DDR signal. An incoming DDR clock signal triggers one register, and the inverted clock signal triggers the other register. The registers take turns capturing bits of the incoming DDR data signal. The primitive to allow this functionality is called IDDR2.

Aside from high bandwidth data transfers, DDR outputs also can be used to reproduce, or *mirror*, a clock signal on the output. This approach is used to transmit clock and data signals together (source synchronously). A similar approach is used to reproduce a clock signal at multiple outputs. The advantage for both approaches is that skew across the outputs is minimal.

Figure 7: Two Methods for Clocking the DDR Register

### **Register Cascade Feature**

In the Spartan-3E family, one of the IOBs in a differential pair can cascade its input storage elements with those in the other IOB as part of a differential pair. This is intended to make DDR operation at high speed much simpler to implement. The new DDR connections that are available are shown in Figure 5 (dashed lines), and are only available for routing between IOBs and are not accessible to the FPGA fabric. Note that this feature is only available when using the differential I/O standards LVDS, RSDS, and MINI\_LVDS.

### **IDDR2**

As a DDR input pair, the master IOB registers incoming data on the rising edge of ICLK1 (= D1) and the rising edge of ICLK2 (= D2), which is typically the same as the falling edge of ICLK1. This data is then transferred into the FPGA fabric. At some point, both signals must be brought into the same clock domain, typically ICLK1. This can be difficult at high frequencies because the available time is only one half of a clock cycle assuming a 50% duty cycle. See Figure 8 for a graphical illustration of this function.

Table 14: Carry Logic Functions (Cont'd)

| Function | Description                                                                                                                                                                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CY0G     | Carry generation for top half of slice. Fixed selection of:  G1 or G2 inputs to the LUT (both equal 1 when a carry is to be generated)  GAND gate for multiplication  BY input for carry initialization  Fixed 1 or 0 input for use as a simple Boolean function |

| CYMUXF   | Carry generation or propagation mux for bottom half of slice. Dynamic selection via CYSELF of:  CYINIT carry propagation (CYSELF = 1)  CY0F carry generation (CYSELF = 0)                                                                                        |

| CYMUXG   | Carry generation or propagation mux for top half of slice. Dynamic selection via CYSELF of:  CYMUXF carry propagation (CYSELG = 1)  CY0G carry generation (CYSELG = 0)                                                                                           |

| CYSELF   | Carry generation or propagation select for bottom half of slice. Fixed selection of:  F-LUT output (typically XOR result)  Fixed 1 to always propagate                                                                                                           |

| CYSELG   | Carry generation or propagation select for top half of slice. Fixed selection of:  G-LUT output (typically XOR result)  Fixed 1 to always propagate                                                                                                              |

| XORF     | Sum generation for bottom half of slice. Inputs from:  F-LUT CYINIT carry signal from previous stage Result is sent to either the combinatorial or registered output for the top of the slice.                                                                   |

| XORG     | Sum generation for top half of slice. Inputs from:  G-LUT  CYMUXF carry signal from previous stage Result is sent to either the combinatorial or registered output for the top of the slice.                                                                     |

| FAND     | Multiplier partial product for bottom half of slice. Inputs:  F-LUT F1 input  F-LUT F2 input  Result is sent through CY0F to become the carry generate signal into CYMUXF                                                                                        |

| GAND     | Multiplier partial product for top half of slice. Inputs:  G-LUT G1 input  G-LUT G2 input  Result is sent through CY0G to become the carry generate signal into CYMUXG                                                                                           |

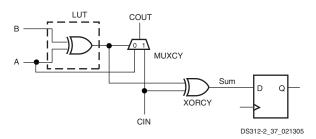

The basic usage of the carry logic is to generate a half-sum in the LUT via an XOR function, which generates or propagates a carry out COUT via the carry mux CYMUXF (or CYMUXG), and then complete the sum with the dedicated XORF (or XORG) gate and the carry input CIN. This structure allows two bits of an arithmetic function in each slice. The CYMUXF (or CYMUXG) can be instantiated using the MUXCY element, and the XORF (or XORG) can be instantiated using the XORCY element.

The FAND (or GAND) gate is used for partial product multiplication and can be instantiated using the MULT\_AND component. Partial products are generated by two-input AND gates and then added. The carry logic is efficient for the adder, but one of the inputs must be outside the LUT as shown in Figure 23.

Figure 23: Using the MUXCY and XORCY in the Carry Logic

The FAND (or GAND) gate is used to duplicate one of the partial products, while the LUT generates both partial products and the XOR function, as shown in Figure 24.

**Spartan-3 FPGA Family: Functional Description**

cancel out the clock skew. When the DLL phase-aligns the CLK0 signal with the CLKIN signal, it asserts the LOCKED output, indicating a lock on to the CLKIN signal.

#### **DLL Attributes and Related Functions**

The DLL unit has a variety of associated attributes as described in Table 29. Each attribute is described in detail in the sections that follow.

Table 29: DLL Attributes

| Attribute         | Description                                                                                                           | Values                                                                                                        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| CLK_FEEDBACK      | Chooses either the CLK0 or CLK2X output to drive the CLKFB input                                                      | NONE, <u>1X</u> , 2X                                                                                          |

| CLKIN_DIVIDE_BY_2 | Halves the frequency of the CLKIN signal just as it enters the DCM                                                    | <i>FALSE</i> , TRUE                                                                                           |

| CLKDV_DIVIDE      | Selects the constant used to divide the CLKIN input frequency to generate the CLKDV output frequency                  | 1.5, <b>2</b> , 2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6.0, 6.5, 7.0, 7.5, <b>8</b> , 9, 10, 11, 12, 13, 14, 15, and 16 |

| CLKIN_PERIOD      | Additional information that allows the DLL to operate with the most efficient lock time and the best jitter tolerance | Floating-point value representing the CLKIN period in nanoseconds                                             |

# **DLL Clock Input Connections**

For best results, an external clock source enters the FPGA via a Global Clock Input (GCLK). Each specific DCM has four possible direct, optimal GCLK inputs that feed the DCM's CLKIN input, as shown in Table 30. Table 30 also provides the specific pin numbers by package for each GCLK input. The two additional DCM's on the XC3S1200E and XC3S1600E have similar optimal connections from the left-edge LHCLK and the right-edge RHCLK inputs, as described in Table 31 and Table 32.

The DCM supports differential clock inputs (for example, LVDS, LVPECL\_25) via a pair of GCLK inputs that feed an internal single-ended signal to the DCM's CLKIN input.

#### Design Note

Avoid using global clock input GCLK1 as it is always shared with the M2 mode select pin. Global clock inputs GCLK0, GCLK2, GCLK3, GCLK12, GCLK13, GCLK14, and GCLK15 have shared functionality in some configuration modes.

Table 30: Direct Clock Input Connections and Optional External Feedback to Associated DCMs

|                                                   | Differen                                                | tial Dair                                                                       | Differen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | tial Dair                                                   |               |               |                            | ſ              | to Associated DCMs                                                                          |                                                                                         |                                                                                     | Hal Dale                                                 |

|---------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------|---------------|----------------------------|----------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------|

|                                                   |                                                         | ntial Pair                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ntial Pair                                                  | -             |               |                            |                |                                                                                             | Differential Pair                                                                       |                                                                                     | itial Pair                                               |

| Package                                           | N                                                       | P                                                                               | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P                                                           |               |               |                            |                | N                                                                                           | P                                                                                       | N                                                                                   | P                                                        |

|                                                   |                                                         | mber for S                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |               |               |                            |                |                                                                                             |                                                                                         | ingle-Ende                                                                          | -                                                        |

| /Q100                                             | P91                                                     | P90                                                                             | P89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P88                                                         |               |               |                            |                | P86                                                                                         | P85                                                                                     | P84                                                                                 | P83                                                      |

| CP132                                             | B7                                                      | A7                                                                              | C8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | B8                                                          |               |               |                            |                | A9                                                                                          | B9                                                                                      | C9                                                                                  | A10                                                      |

| ΓQ144                                             | P131                                                    | P130                                                                            | P129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P128                                                        |               |               |                            |                | P126                                                                                        | P125                                                                                    | P123                                                                                | P122                                                     |

| PQ208                                             | P186                                                    | P185                                                                            | P184                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P183                                                        |               |               |                            |                | P181                                                                                        | P180                                                                                    | P178                                                                                | P177                                                     |

| FT256                                             | D8                                                      | C8                                                                              | B8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A8                                                          |               |               |                            |                | A9                                                                                          | A10                                                                                     | F9                                                                                  | E9                                                       |

| FG320                                             | D9                                                      | C9                                                                              | B9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | B8                                                          |               |               |                            |                | A10                                                                                         | B10                                                                                     | E10                                                                                 | D10                                                      |

| FG400                                             | A9                                                      | A10                                                                             | G10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | H10                                                         |               |               |                            |                | E10                                                                                         | E11                                                                                     | G11                                                                                 | F11                                                      |

| FG484                                             | B11                                                     | C11                                                                             | H11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | H12                                                         |               |               |                            |                | C12                                                                                         | B12                                                                                     | E12                                                                                 | F12                                                      |

| ı                                                 | Ψ                                                       | Ψ                                                                               | Ψ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ψ                                                           | Assoc         | iated G       | ilobal B                   | uffers         | Ψ                                                                                           | Ψ                                                                                       | Ψ                                                                                   | Ψ                                                        |

|                                                   | GCLK11                                                  | GCLK10                                                                          | GCLK9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | GCLK8                                                       | 710           | Ξ             | 710                        | /11            | GCLK7                                                                                       | GCLK6                                                                                   | GCLK5                                                                               | GCLK                                                     |

|                                                   |                                                         | XC3S1<br>250E, XC3S<br>200E, XC3S                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | BUFGMUX_X1Y10 | BUFGMUX_X1Y11 | BUFGMUX_X2Y10              | BUFGMUX_X2Y11  | Top Right DCM  XC3S100: DCM_X0Y1  XC3S250E, XC3S500E: DCM_X1Y  XC3S1200E, XC3S1600E: DCM_X2 |                                                                                         |                                                                                     |                                                          |

| · ·                                               |                                                         |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | _ T           |               | <b>T</b>                   | <u>т</u>       |                                                                                             |                                                                                         |                                                                                     |                                                          |

| !                                                 |                                                         |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | <b>V</b>      | <b>4</b>      | <b>↓</b>                   | <b>Y</b>       | •                                                                                           |                                                                                         |                                                                                     |                                                          |

| ·                                                 |                                                         |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | Н             | G             | F                          | Е              |                                                                                             |                                                                                         |                                                                                     |                                                          |

| ·                                                 |                                                         |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | Clock         | G<br>Line (s  | F<br>see Tabl              | <b>E</b> e 41) |                                                                                             |                                                                                         |                                                                                     |                                                          |

|                                                   |                                                         |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | Clock         | G Line (s     | F<br>see Tabl              | <b>E</b> e 41) |                                                                                             |                                                                                         |                                                                                     |                                                          |

|                                                   |                                                         |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             | Clock D       | G Line (s     | F see Tabl B               | E e 41) A      |                                                                                             |                                                                                         |                                                                                     |                                                          |

|                                                   |                                                         |                                                                                 | Left DCM<br>00: N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             | Clock D       | G Line (s     | F see Tabl B               | E e 41) A      |                                                                                             |                                                                                         | Right DCM<br>DCM X0Y0                                                               |                                                          |

|                                                   | XC3S2                                                   |                                                                                 | 00: N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1_X0Y0                                                      | Clock D       | G Line (s     | F see Tabl B               | E e 41) A      |                                                                                             | XC3S100:                                                                                | Right DCM<br>DCM_X0Y0<br>5 <b>500E</b> : DCM                                        |                                                          |