# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                        |

|--------------------------------|---------------------------------------------------------------|

| Number of LABs/CLBs            | 240                                                           |

| Number of Logic Elements/Cells | 2160                                                          |

| Total RAM Bits                 | 73728                                                         |

| Number of I/O                  | 66                                                            |

| Number of Gates                | 100000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 100-TQFP                                                      |

| Supplier Device Package        | 100-VQFP (14x14)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s100e-4vqg100i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

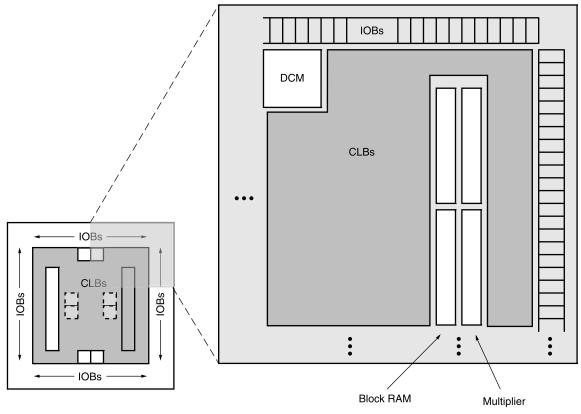

## **Architectural Overview**

The Spartan-3E family architecture consists of five fundamental programmable functional elements:

- **Configurable Logic Blocks (CLBs)** contain flexible Look-Up Tables (LUTs) that implement logic plus storage elements used as flip-flops or latches. CLBs perform a wide variety of logical functions as well as store data.

- Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3-state operation. Supports a variety of signal standards, including four high-performance differential standards. Double Data-Rate (DDR) registers are included.

- **Block RAM** provides data storage in the form of 18-Kbit dual-port blocks.

- **Multiplier Blocks** accept two 18-bit binary numbers as inputs and calculate the product.

• **Digital Clock Manager (DCM) Blocks** provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase-shifting clock signals.

These elements are organized as shown in Figure 1. A ring of IOBs surrounds a regular array of CLBs. Each device has two columns of block RAM except for the XC3S100E, which has one column. Each RAM column consists of several 18-Kbit RAM blocks. Each block RAM is associated with a dedicated multiplier. The DCMs are positioned in the center with two at the top and two at the bottom of the device. The XC3S100E has only one DCM at the top and bottom, while the XC3S1200E and XC3S1600E add two DCMs in the middle of the left and right sides.

The Spartan-3E family features a rich network of traces that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

DS312\_01\_111904

Figure 1: Spartan-3E Family Architecture

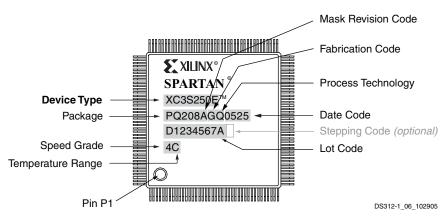

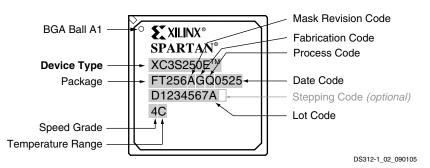

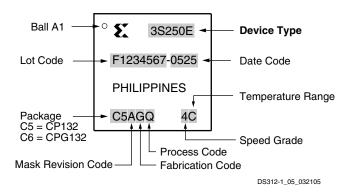

## Package Marking

Figure 2 provides a top marking example for Spartan-3E FPGAs in the quad-flat packages. Figure 3 shows the top marking for Spartan-3E FPGAs in BGA packages except the 132-ball chip-scale package (CP132 and CPG132). The markings for the BGA packages are nearly identical to those for the quad-flat packages, except that the marking is rotated with respect to the ball A1 indicator. Figure 4 shows the top marking for Spartan-3E FPGAs in the CP132 and CPG132 packages. On the QFP and BGA packages, the optional numerical Stepping Code follows the Lot Code.

The "5C" and "4I" part combinations can have a dual mark of "5C/4I". Devices with a single mark are only guaranteed for the marked speed grade and temperature range. All "5C" and "4I" part combinations use the Stepping 1 production silicon.

Figure 2: Spartan-3E QFP Package Marking Example

Figure 4: Spartan-3E CP132 and CPG132 Package Marking Example

#### Notes:

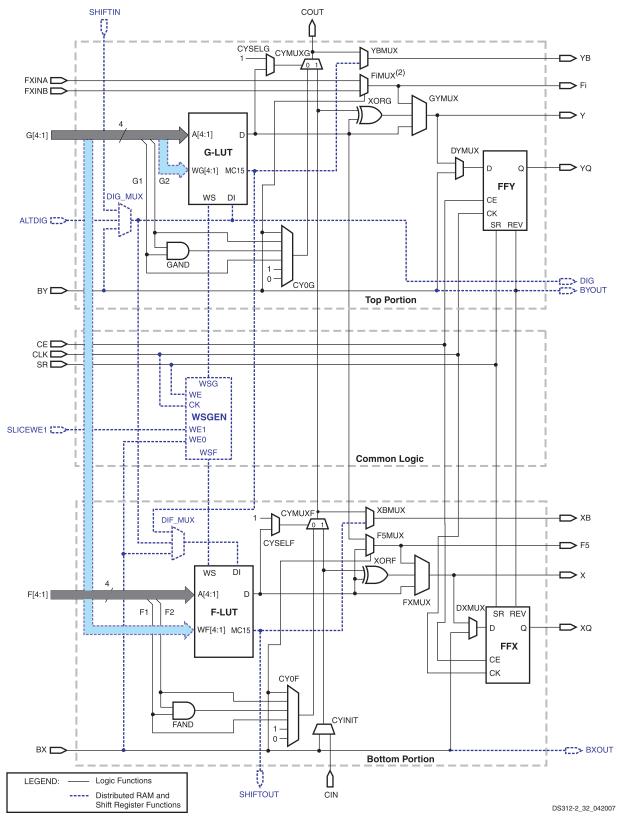

- 1. Options to invert signal polarity as well as other options that enable lines for various functions are not shown.

- 2. The index i can be 6, 7, or 8, depending on the slice. The upper SLICEL has an F8MUX, and the upper SLICEM has an F7MUX. The lower SLICEL and SLICEM both have an F6MUX.

#### Figure 15: Simplified Diagram of the Left-Hand SLICEM

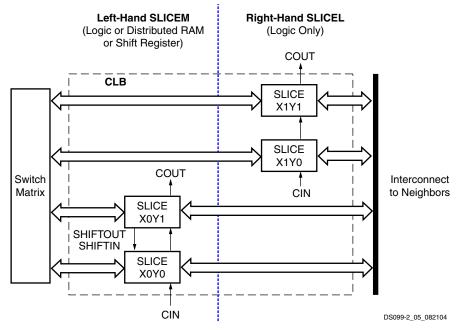

Figure 16: Arrangement of Slices within the CLB

### **Slice Location Designations**

The Xilinx development software designates the location of a slice according to its X and Y coordinates, starting in the bottom left corner, as shown in Figure 14. The letter 'X' followed by a number identifies columns of slices, incrementing from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row, incrementing from the bottom of the die. Figure 16 shows the CLB located in the lower left-hand corner of the die. The SLICEM always has an even 'X' number, and the SLICEL always has an odd 'X' number.

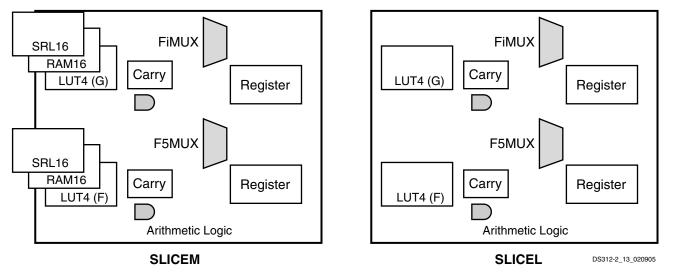

## **Slice Overview**

A slice includes two LUT function generators and two storage elements, along with additional logic, as shown in Figure 17.

Both SLICEM and SLICEL have the following elements in common to provide logic, arithmetic, and ROM functions:

- Two 4-input LUT function generators, F and G

- Two storage elements

- Two wide-function multiplexers, F5MUX and FiMUX

- Carry and arithmetic logic

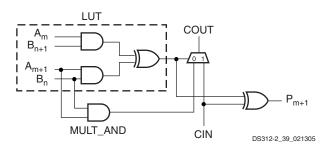

# Figure 24: Using the MULT\_AND for Multiplication in Carry Logic

The MULT\_AND is useful for small multipliers. Larger multipliers can be built using the dedicated 18x18 multiplier blocks (see Dedicated Multipliers).

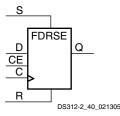

## **Storage Elements**

The storage element, which is programmable as either a D-type flip-flop or a level-sensitive transparent latch, provides a means for synchronizing data to a clock signal, among other uses. The storage elements in the top and bottom portions of the slice are called FFY and FFX, respectively. FFY has a fixed multiplexer on the D input selecting either the combinatorial output Y or the bypass signal BY. FFX selects between the combinatorial output X or the bypass signal BX.

The functionality of a slice storage element is identical to that described earlier for the I/O storage elements. All signals have programmable polarity; the default active-High function is described.

| Signal | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D      | Input. For a flip-flop data on the D input is loaded when R and S (or CLR and PRE) are Low and CE is High during the Low-to-High clock transition. For a latch, Q reflects the D input while the gate (G) input and gate enable (GE) are High and R and S (or CLR and PRE) are Low. The data on the D input during the High-to-Low gate transition is stored in the latch. The data on the Q output of the latch remains unchanged as long as G or GE remains Low. |

| Q      | Output. Toggles after the Low-to-High clock transition for a flip-flop and immediately for a latch.                                                                                                                                                                                                                                                                                                                                                                |

| С      | Clock for edge-triggered flip-flops.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| G      | Gate for level-sensitive latches.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CE     | Clock Enable for flip-flops.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GE     | Gate Enable for latches.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| S      | Synchronous Set (Q = High). When the S input is High and R is Low, the flip-flop is set, output High, during the Low-to-High clock (C) transition. A latch output is immediately set, output High.                                                                                                                                                                                                                                                                 |

| R      | Synchronous Reset (Q = Low); has precedence over Set.                                                                                                                                                                                                                                                                                                                                                                                                              |

| PRE    | Asynchronous Preset (Q = High). When the PRE input is High and CLR is Low, the flip-flop is set, output High, during the Low-to-High clock (C) transition. A latch output is immediately set, output High.                                                                                                                                                                                                                                                         |

| CLR    | Asynchronous Clear (Q = Low); has precedence over Preset to reset Q output Low                                                                                                                                                                                                                                                                                                                                                                                     |

| SR     | CLB input for R, S, CLR, or PRE                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| REV    | CLB input for opposite of SR. Must be asynchronous or synchronous to match SR.                                                                                                                                                                                                                                                                                                                                                                                     |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

The control inputs R, S, CE, and C are all shared between the two flip-flops in a slice.

# Figure 25: FD Flip-Flop Component with Synchronous Reset, Set, and Clock Enable

# Table 16: FD Flip-Flop Functionality with SynchronousReset, Set, and Clock Enable

|   |   | Outputs |     |   |           |

|---|---|---------|-----|---|-----------|

| R | S | CE      | D C |   | Q         |

| 1 | Х | Х       | Х   | ↑ | 0         |

| 0 | 1 | Х       | Х   | ↑ | 1         |

| 0 | 0 | 0       | Х   | Х | No Change |

| 0 | 0 | 1       | 1   | ↑ | 1         |

| 0 | 0 | 1       | 0   | ↑ | 0         |

# Table 15: Storage Element Signals Simular

cancel out the clock skew. When the DLL phase-aligns the CLK0 signal with the CLKIN signal, it asserts the LOCKED output, indicating a lock on to the CLKIN signal.

#### **DLL Attributes and Related Functions**

The DLL unit has a variety of associated attributes as described in Table 29. Each attribute is described in detail in the sections that follow.

#### Table 29: DLL Attributes

**EXILINX**

| Attribute         | Description                                                                                                           | Values                                                                                                |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| CLK_FEEDBACK      | Chooses either the CLK0 or CLK2X output to drive the CLKFB input                                                      | NONE, <u>1X</u> , 2X                                                                                  |

| CLKIN_DIVIDE_BY_2 | Halves the frequency of the CLKIN signal just as it enters the DCM                                                    | <i>FALSE</i> , TRUE                                                                                   |

| CLKDV_DIVIDE      | Selects the constant used to divide the CLKIN input frequency to generate the CLKDV output frequency                  | 1.5, <u>2</u> , 2.5, 3, 3.5, 4, 4.5, 5, 5.5, 6.0, 6.5, 7.0, 7.5, 8, 9, 10, 11, 12, 13, 14, 15, and 16 |

| CLKIN_PERIOD      | Additional information that allows the DLL to operate with the most efficient lock time and the best jitter tolerance | Floating-point value representing the CLKIN period in nanoseconds                                     |

### **DLL Clock Input Connections**

For best results, an external clock source enters the FPGA via a Global Clock Input (GCLK). Each specific DCM has four possible direct, optimal GCLK inputs that feed the DCM's CLKIN input, as shown in Table 30. Table 30 also provides the specific pin numbers by package for each GCLK input. The two additional DCM's on the XC3S1200E and XC3S1600E have similar optimal connections from the left-edge LHCLK and the right-edge RHCLK inputs, as described in Table 31 and Table 32.

The DCM supports differential clock inputs (for example, LVDS, LVPECL\_25) via a pair of GCLK inputs that feed an internal single-ended signal to the DCM's CLKIN input.

#### Design Note

Avoid using global clock input GCLK1 as it is always shared with the M2 mode select pin. Global clock inputs GCLK0, GCLK2, GCLK3, GCLK12, GCLK13, GCLK14, and GCLK15 have shared functionality in some configuration modes.

##

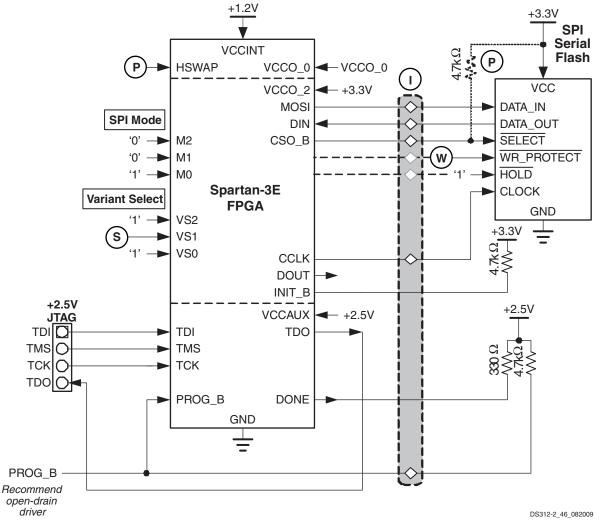

## SPI Serial Flash Mode

For additional information, refer to the "Master SPI Mode" chapter in UG332.

In SPI Serial Flash mode (M[2:0] = <0:0:1>), the Spartan-3E FPGA configures itself from an attached industry-standard SPI serial Flash PROM, as illustrated in Figure 53 and Figure 54. The FPGA supplies the CCLK output clock from its internal oscillator to the clock input of the attached SPI Flash PROM.

(S) Although SPI is a standard four-wire interface, various available SPI Flash PROMs use different command protocols. The FPGA's variant select pins, VS[2:0], define how the FPGA communicates with the SPI Flash, including which SPI Flash command the FPGA issues to start the read operation and the number of dummy bytes inserted before the FPGA expects to receive valid data from the SPI Flash. Table 53 shows the available SPI Flash PROMs expected to operate with Spartan-3E FPGAs. Other compatible devices might work but have not been tested for suitability with Spartan-3E FPGAs. All other VS[2:0] values are reserved for future use. Consult the data sheet for the desired SPI Flash device to determine its suitability. The basic timing requirements and waveforms are provided in

# Serial Peripheral Interface (SPI) Configuration Timing in Module 3.

Figure 53 shows the general connection diagram for those SPI Flash PROMs that support the 0x03 READ command or the 0x0B FAST READ commands.

Figure 54 shows the connection diagram for Atmel DataFlash serial PROMs, which also use an SPI-based protocol. 'B'-series DataFlash devices are limited to FPGA applications operating over the commercial temperature range. Industrial temperature range applications must use 'C'- or 'D'-series DataFlash devices, which have a shorter DataFlash select setup time, because of the faster FPGA CCLK frequency at cold temperatures. can also be eliminated from the interface. However, RDWR\_B must remain Low during configuration.

After configuration, all of the interface pins except DONE and PROG\_B are available as user I/Os. Alternatively, the bidirectional SelectMAP configuration interface is available after configuration. To continue using SelectMAP mode, set the **Persist** bitstream generator option to **Yes**. The external host can then read and verify configuration data. The Persist option will maintain A20-A23 as configuration pins although they are not used in SelectMAP mode.

The Slave Parallel mode is also used with BPI mode to create multi-FPGA daisy-chains. The lead FPGA is set for BPI mode configuration; all the downstream daisy-chain FPGAs are set for Slave Parallel configuration, as highlighted in Figure 59.

| Pin Name | ame FPGA Direction Description Dur |                                                                                                                                                                                                                                    | During Configuration                                                                                                                                                 | After Configuration                                                                                                     |  |

|----------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| HSWAP    | Input                              | <b>User I/O Pull-Up Control</b> . When<br>Low during configuration, enables<br>pull-up resistors in all I/O pins to<br>respective I/O bank V <sub>CCO</sub> input.<br>0: Pull-ups during configuration                             | during configuration, enables<br>up resistors in all I/O pins to<br>pective I/O bank V <sub>CCO</sub> input.<br>ull-ups during configuration                         |                                                                                                                         |  |

|          |                                    | 1: No pull-ups                                                                                                                                                                                                                     |                                                                                                                                                                      |                                                                                                                         |  |

| M[2:0]   | Input                              | Iode Select. Selects the FPGA<br>onfiguration mode. See Design<br>Considerations for the HSWAP,<br>M[2:0], and VS[2:0] Pins.M2 = 1, M1 = 1, M0 = 0 Sampled<br>when INIT_B goes High.U                                              |                                                                                                                                                                      | User I/O                                                                                                                |  |

| D[7:0]   | Input                              | Data Input.                                                                                                                                                                                                                        |                                                                                                                                                                      |                                                                                                                         |  |

| BUSY     | Output                             | Busy Indicator.<br>If CCLK frequency is < 50 MHz,<br>this pin may be ignored. When<br>High, indicates that the FPGA is<br>not ready to receive additional<br>configuration data. Host must hold<br>data an additional clock cycle. |                                                                                                                                                                      | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |  |

| CSI_B    | Input                              | Chip Select Input. Active Low.                                                                                                                                                                                                     | Must be Low throughout configuration.                                                                                                                                | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |  |

| RDWR_B   | Input                              | <b>Read/Write Control</b> . Active Low write enable.                                                                                                                                                                               | Must be Low throughout configuration.                                                                                                                                | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |  |

| CCLK     | Input                              | <b>Configuration Clock</b> . If CCLK PCB trace is long or has multiple connections, terminate this output to maintain signal integrity. See CCLK Design Considerations.                                                            | External clock.                                                                                                                                                      | User I/O If bitstream option<br><i>Persist=Yes</i> , becomes<br>part of SelectMap parallel<br>peripheral interface.     |  |

| CSO_B    | Output                             | Chip Select Output. Active Low.                                                                                                                                                                                                    | Not used in single FPGA<br>applications. In a daisy-chain<br>configuration, this pin connects to<br>the CSI_B pin of the next FPGA in<br>the chain. Actively drives. | User I/O                                                                                                                |  |

#### Table 65: Slave Parallel Mode Connections

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | During Configuration                                                                                      | After Configuration                                                                                    |

|----------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| INIT_B   | Open-drain<br>bidirectional I/O | <b>Initialization Indicator</b> . Active Low.<br>Goes Low at the start of<br>configuration during the Initialization<br>memory clearing process. Released<br>at the end of memory clearing, when<br>mode select pins are sampled. In<br>daisy-chain applications, this signal<br>requires an external 4.7 k $\Omega$ pull-up<br>resistor to VCCO_2.                                                                                                                                                                      | Active during configuration. If<br>CRC error detected during<br>configuration, FPGA drives<br>INIT_B Low. | User I/O. If unused in the<br>application, drive INIT_B<br>High.                                       |

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external 330 $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                                            | Low indicates that the FPGA is not yet configured.                                                        | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully configured. |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low. When<br>asserted Low for 500 ns or longer,<br>forces the FPGA to restart its<br>configuration process by clearing<br>configuration memory and resetting<br>the DONE and INIT_B pins once<br>PROG_B returns High. Recommend<br>external 4.7 k $\Omega$ pull-up resistor to<br>2.5V. Internal pull-up value may be<br>weaker (see Table 78). If driving<br>externally with a 3.3V output, use an<br>open-drain or open-collector driver<br>or use a current limiting series<br>resistor. | Must be High to allow<br>configuration to start.                                                          | Drive PROG_B Low and<br>release to reprogram<br>FPGA.                                                  |

#### Table 65: Slave Parallel Mode Connections (Cont'd)

## **Voltage Compatibility**

W Most Slave Parallel interface signals are within the FPGA's I/O Bank 2, supplied by the VCCO\_2 supply input. The VCCO\_2 voltage can be 1.8V, 2.5V, or 3.3V to match the requirements of the external host, ideally 2.5V. Using 1.8V or 3.3V requires additional design considerations as the DONE and PROG\_B pins are powered by the FPGA's 2.5V V<sub>CCAUX</sub> supply. See <u>XAPP453</u>: *The 3.3V Configuration of Spartan-3 FPGAs* for additional information.

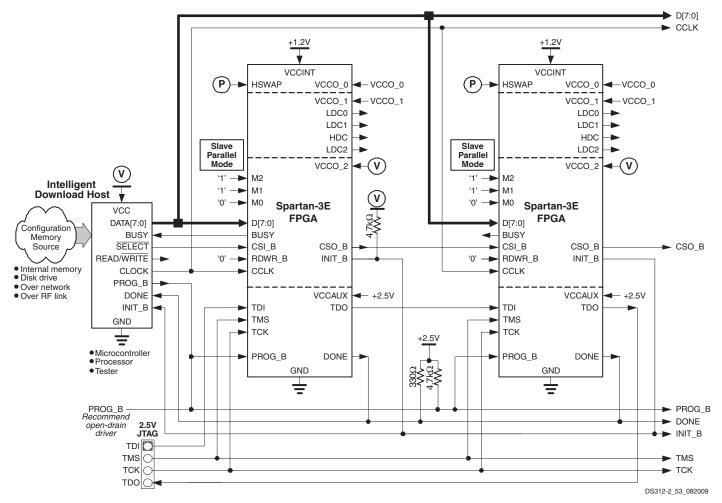

### **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain. Use Slave Parallel mode (M[2:0] = <1:1:0>) for all FPGAs in the daisy-chain. The schematic in Figure 62 is optimized for FPGA downloading and does not support the SelectMAP read interface. The FPGA's RDWR\_B pin must be Low during configuration.

After the lead FPGA is filled with its configuration data, the lead FPGA enables the next FPGA in the daisy-chain by asserting is chip-select output, CSO\_B.

Figure 62: Daisy-Chaining using Slave Parallel Mode

## **Slave Serial Mode**

For additional information, refer to the "Slave Serial Mode" chapter in UG332.

In Slave Serial mode (M[2:0] = <1:1:1>), an external host such as a microprocessor or microcontroller writes serial configuration data into the FPGA, using the synchronous serial interface shown in Figure 63. The serial configuration data is presented on the FPGA's DIN input pin with sufficient setup time before each rising edge of the externally generated CCLK clock input. The intelligent host starts the configuration process by pulsing PROG\_B and monitoring that the INIT\_B pin goes High, indicating that the FPGA is ready to receive its first data. The host then continues supplying data and clock signals until either the DONE pin goes High, indicating a successful configuration, or until the INIT\_B pin goes Low, indicating a configuration error. The configuration process requires more clock cycles than indicated from the configuration file size. Additional clocks are required during the FPGA's start-up sequence, especially if the FPGA is programmed to wait for selected Digital Clock Managers (DCMs) to lock to their respective clock inputs (see Start-Up, page 105).

# **E** XILINX.

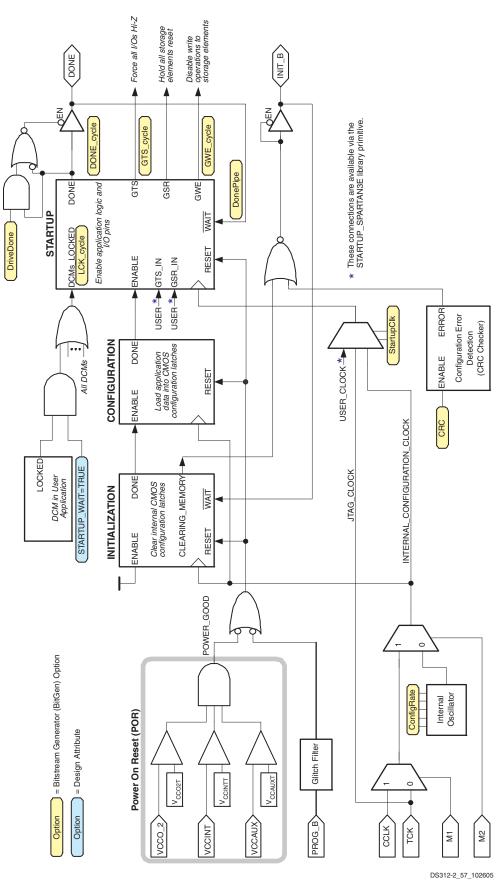

Figure 66: Generalized Spartan-3E FPGA Configuration Logic Block Diagram

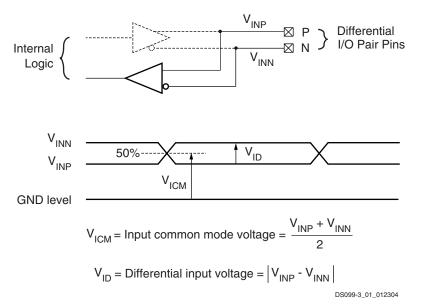

## Differential I/O Standards

Figure 69: Differential Input Voltages

| Table 82: Recommended O | perating Conditions for Use | r I/Os Using Differentia | Signal Standards   |

|-------------------------|-----------------------------|--------------------------|--------------------|

|                         | peruang contantene for coo  | i woo oonig binoronda    | orginal otariaarao |

| IOSTANDARD               | V <sub>CCO</sub> for Drivers <sup>(1)</sup> |             |         | V <sub>ID</sub> |          |          | V <sub>ICM</sub> |         |         |

|--------------------------|---------------------------------------------|-------------|---------|-----------------|----------|----------|------------------|---------|---------|

| Attribute                | Min (V)                                     | Nom (V)     | Max (V) | Min (mV)        | Nom (mV) | Max (mV) | Min (V)          | Nom (V) | Max (V) |

| LVDS_25                  | 2.375                                       | 2.50        | 2.625   | 100             | 350      | 600      | 0.30             | 1.25    | 2.20    |

| BLVDS_25                 | 2.375                                       | 2.50        | 2.625   | 100             | 350      | 600      | 0.30             | 1.25    | 2.20    |

| MINI_LVDS_25             | 2.375                                       | 2.50        | 2.625   | 200             | -        | 600      | 0.30             | -       | 2.2     |

| LVPECL_25 <sup>(2)</sup> |                                             | Inputs Only |         | 100             | 800      | 1000     | 0.5              | 1.2     | 2.0     |

| RSDS_25                  | 2.375                                       | 2.50        | 2.625   | 100             | 200      | -        | 0.3              | 1.20    | 1.4     |

| DIFF_HSTL_I_18           | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.8              | -       | 1.1     |

| DIFF_HSTL_III_18         | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.8              | -       | 1.1     |

| DIFF_SSTL18_I            | 1.7                                         | 1.8         | 1.9     | 100             | -        | -        | 0.7              | -       | 1.1     |

| DIFF_SSTL2_I             | 2.3                                         | 2.5         | 2.7     | 100             | -        | -        | 1.0              | -       | 1.5     |

#### Notes:

1. The  $V_{CCO}$  rails supply only differential output drivers, not input circuits.

2. V<sub>REF</sub> inputs are not used for any of the differential I/O standards.

#### Table 94: Output Timing Adjustments for IOB

| Convert O<br>LVCMOS25 w<br>Fast Slew Ra | ith 12mA C | Add<br>Adjus<br>Be | Units |       |    |

|-----------------------------------------|------------|--------------------|-------|-------|----|

| Signal Standa                           |            |                    | Speed | Grade | -  |

|                                         |            | _                  | -5    | -4    |    |

| Single-Ended                            | Standards  | 5                  |       | r     | 1  |

| LVTTL                                   | Slow       | 2 mA               | 5.20  | 5.41  | ns |

|                                         |            | 4 mA               | 2.32  | 2.41  | ns |

|                                         |            | 6 mA               | 1.83  | 1.90  | ns |

|                                         |            | 8 mA               | 0.64  | 0.67  | ns |

|                                         |            | 12 mA              | 0.68  | 0.70  | ns |

|                                         |            | 16 mA              | 0.41  | 0.43  | ns |

|                                         | Fast       | 2 mA               | 4.80  | 5.00  | ns |

|                                         |            | 4 mA               | 1.88  | 1.96  | ns |

|                                         |            | 6 mA               | 1.39  | 1.45  | ns |

|                                         |            | 8 mA               | 0.32  | 0.34  | ns |

|                                         |            | 12 mA              | 0.28  | 0.30  | ns |

|                                         |            | 16 mA              | 0.28  | 0.30  | ns |

| LVCMOS33                                | Slow       | 2 mA               | 5.08  | 5.29  | ns |

|                                         |            | 4 mA               | 1.82  | 1.89  | ns |

|                                         |            | 6 mA               | 1.00  | 1.04  | ns |

|                                         |            | 8 mA               | 0.66  | 0.69  | ns |

|                                         |            | 12 mA              | 0.40  | 0.42  | ns |

|                                         |            | 16 mA              | 0.41  | 0.43  | ns |

|                                         | Fast       | 2 mA               | 4.68  | 4.87  | ns |

|                                         |            | 4 mA               | 1.46  | 1.52  | ns |

|                                         |            | 6 mA               | 0.38  | 0.39  | ns |

|                                         |            | 8 mA               | 0.33  | 0.34  | ns |

|                                         |            | 12 mA              | 0.28  | 0.30  | ns |

|                                         |            | 16 mA              | 0.28  | 0.30  | ns |

| LVCMOS25                                | Slow       | 2 mA               | 4.04  | 4.21  | ns |

|                                         |            | 4 mA               | 2.17  | 2.26  | ns |

|                                         |            | 6 mA               | 1.46  | 1.52  | ns |

|                                         |            | 8 mA               | 1.04  | 1.08  | ns |

|                                         |            | 12 mA              | 0.65  | 0.68  | ns |

|                                         | Fast       | 2 mA               | 3.53  | 3.67  | ns |

|                                         |            | 4 mA               | 1.65  | 1.72  | ns |

|                                         |            | 6 mA               | 0.44  | 0.46  | ns |

|                                         |            | 8 mA               | 0.20  | 0.21  | ns |

|                                         |            | 12 mA              | 0     | 0     | ns |

#### Table 94: Output Timing Adjustments for IOB (Cont'd)

| Convert Output Time from<br>LVCMOS25 with 12mA Drive and<br>Fast Slew Rate to the Following |                              |       | Adjus<br>Bel | the<br>tment<br>ow<br>Grade | Units |  |

|---------------------------------------------------------------------------------------------|------------------------------|-------|--------------|-----------------------------|-------|--|

| Signal Standa                                                                               | Signal Standard (IOSTANDARD) |       |              |                             | -     |  |

|                                                                                             |                              |       | -5           | -4                          |       |  |

| LVCMOS18                                                                                    | Slow                         | 2 mA  | 5.03         | 5.24                        | ns    |  |

|                                                                                             |                              | 4 mA  | 3.08         | 3.21                        | ns    |  |

|                                                                                             |                              | 6 mA  | 2.39         | 2.49                        | ns    |  |

|                                                                                             |                              | 8 mA  | 1.83         | 1.90                        | ns    |  |

|                                                                                             | Fast                         | 2 mA  | 3.98         | 4.15                        | ns    |  |

|                                                                                             |                              | 4 mA  | 2.04         | 2.13                        | ns    |  |

|                                                                                             |                              | 6 mA  | 1.09         | 1.14                        | ns    |  |

|                                                                                             |                              | 8 mA  | 0.72         | 0.75                        | ns    |  |

| LVCMOS15                                                                                    | Slow                         | 2 mA  | 4.49         | 4.68                        | ns    |  |

|                                                                                             |                              | 4 mA  | 3.81         | 3.97                        | ns    |  |

|                                                                                             |                              | 6 mA  | 2.99         | 3.11                        | ns    |  |

|                                                                                             | Fast                         | 2 mA  | 3.25         | 3.38                        | ns    |  |

|                                                                                             |                              | 4 mA  | 2.59         | 2.70                        | ns    |  |

|                                                                                             |                              | 6 mA  | 1.47         | 1.53                        | ns    |  |

| LVCMOS12                                                                                    | Slow                         | 2 mA  | 6.36         | 6.63                        | ns    |  |

|                                                                                             | Fast                         | 2 mA  | 4.26         | 4.44                        | ns    |  |

| HSTL_I_18                                                                                   |                              |       | 0.33         | 0.34                        | ns    |  |

| HSTL_III_18                                                                                 |                              |       | 0.53         | 0.55                        | ns    |  |

| PCI33_3                                                                                     |                              |       | 0.44         | 0.46                        | ns    |  |

| PCI66_3                                                                                     |                              |       | 0.44         | 0.46                        | ns    |  |

| SSTL18_I                                                                                    |                              |       | 0.24         | 0.25                        | ns    |  |

| SSTL2_I                                                                                     |                              |       | -0.20        | -0.20                       | ns    |  |

| Differential Sta                                                                            | ndards                       |       | 1            |                             |       |  |

| LVDS_25                                                                                     |                              |       | -0.55        | -0.55                       | ns    |  |

| BLVDS_25                                                                                    |                              |       | 0.04         | 0.04                        | ns    |  |

| MINI_LVDS_25                                                                                |                              |       | -0.56        | -0.56                       | ns    |  |

| LVPECL_25                                                                                   |                              |       | Input        | Only                        | ns    |  |

| RSDS_25                                                                                     |                              | -0.48 | -0.48        | ns                          |       |  |

| DIFF_HSTL_I_                                                                                | 18                           | 0.42  | 0.42         | ns                          |       |  |

| DIFF_HSTL_III                                                                               | _18                          | 0.53  | 0.55         | ns                          |       |  |

| DIFF_SSTL18_                                                                                | I                            |       | 0.40         | 0.40                        | ns    |  |

| DIFF_SSTL2_I                                                                                |                              |       | 0.44         | 0.44                        | ns    |  |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77, Table 80, and Table 82.

- 2. These adjustments are used to convert output- and three-state-path times originally specified for the LVCMOS25 standard with 12 mA drive and Fast slew rate to times that correspond to other signal standards. Do not adjust times that measure when outputs go into a high-impedance state.

## Table 105: Switching Characteristics for the DLL

|                                        | Description                                                                                                                          |                                                 |                                               | Speed Grade |                                      |        |                                      |       |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------|-------------|--------------------------------------|--------|--------------------------------------|-------|

| Symbol                                 |                                                                                                                                      |                                                 | Device                                        | -5          |                                      | -4     |                                      | Units |

|                                        |                                                                                                                                      |                                                 |                                               | Min         | Max                                  | Min    | Мах                                  |       |

| Output Frequency Ranges                |                                                                                                                                      |                                                 |                                               |             |                                      |        |                                      |       |

| CLKOUT_FREQ_CLK0                       | Frequency for the CLK0 and CLK180 outputs                                                                                            | Stepping 0                                      | XC3S100E<br>XC3S250E<br>XC3S500E<br>XC3S1600E | N/A         | N/A                                  | 5      | 90                                   | MHz   |

|                                        |                                                                                                                                      |                                                 | XC3S1200E                                     |             |                                      |        | 200                                  | MHz   |

|                                        |                                                                                                                                      | Stepping 1                                      | All                                           | 5           | 275                                  |        | 240                                  | MHz   |

| CLKOUT_FREQ_CLK90                      | Frequency for the CLK90 and CLK270 outputs                                                                                           | Stepping 0                                      | XC3S100E<br>XC3S250E<br>XC3S500E<br>XC3S1600E | N/A         | N/A                                  | 5      | 90                                   | MHz   |

|                                        |                                                                                                                                      |                                                 | XC3S1200E                                     |             |                                      |        | 167                                  | MHz   |

|                                        |                                                                                                                                      | Stepping 1                                      | All                                           | 5           | 200                                  |        | 200                                  | MHz   |

| CLKOUT_FREQ_2X                         | Frequency for the CLK2X and CLK2X180 outputs                                                                                         | Stepping 0                                      | XC3S100E<br>XC3S250E<br>XC3S500E<br>XC3S1600E | N/A         | N/A                                  | 10     | 180                                  | MHz   |

|                                        |                                                                                                                                      |                                                 | XC3S1200E                                     |             |                                      |        | 311                                  | MHz   |

|                                        |                                                                                                                                      | Stepping 1                                      | All                                           | 10          | 333                                  |        | 311                                  | MHz   |

| CLKOUT_FREQ_DV                         | Frequency for the CLKDV output                                                                                                       | Stepping 0                                      | XC3S100E<br>XC3S250E<br>XC3S500E<br>XC3S1600E | N/A         | N/A                                  | 0.3125 | 60                                   | MHz   |

|                                        |                                                                                                                                      |                                                 | XC3S1200E                                     |             |                                      |        | 133                                  | MHz   |

|                                        |                                                                                                                                      | Stepping 1                                      | All                                           | 0.3125      | 183                                  |        | 160                                  | MHz   |

| Output Clock Jitter <sup>(2,3,4)</sup> |                                                                                                                                      |                                                 |                                               |             |                                      |        |                                      |       |

| CLKOUT_PER_JITT_0                      | Period jitter at the CLK0 output                                                                                                     |                                                 | All                                           | -           | ±100                                 | -      | ±100                                 | ps    |

| CLKOUT_PER_JITT_90                     | Period jitter at the CLK90 output                                                                                                    | ıt                                              |                                               | -           | ±150                                 | -      | ±150                                 | ps    |

| CLKOUT_PER_JITT_180                    | Period jitter at the CLK180 outp                                                                                                     | out                                             |                                               | -           | ±150                                 | -      | ±150                                 | ps    |

| CLKOUT_PER_JITT_270                    | Period jitter at the CLK270 outp                                                                                                     | out                                             |                                               | -           | ±150                                 | -      | ±150                                 | ps    |

| CLKOUT_PER_JITT_2X                     | Period jitter at the CLK2X and C                                                                                                     | Period jitter at the CLK2X and CLK2X180 outputs |                                               | -           | ±[1% of<br>CLKIN<br>period<br>+ 150] | -      | ±[1% of<br>CLKIN<br>period<br>+ 150] | ps    |

| CLKOUT_PER_JITT_DV1                    | Period jitter at the CLKDV output when performing integer division                                                                   |                                                 |                                               | -           | ±150                                 | -      | ±150                                 | ps    |

| CLKOUT_PER_JITT_DV2                    | Period jitter at the CLKDV output when performing non-integer division                                                               |                                                 |                                               | -           | ±[1% of<br>CLKIN<br>period<br>+ 200] | -      | ±[1% of<br>CLKIN<br>period<br>+ 200] | ps    |

| Duty Cycle <sup>(4)</sup>              |                                                                                                                                      |                                                 |                                               |             |                                      |        |                                      |       |

| CLKOUT_DUTY_CYCLE_DLL                  | Duty cycle variation for the CLK<br>CLK180, CLK270, CLK2X, CLK<br>CLKDV outputs, including the E<br>clock tree duty-cycle distortion | <2X180, and                                     | All                                           | -           | ±[1% of<br>CLKIN<br>period<br>+ 400] | -      | ±[1% of<br>CLKIN<br>period<br>+ 400] | ps    |

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/01/05 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11/23/05 | 2.0     | Added AC timing information and additional DC specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 03/22/06 | 3.0     | Upgraded data sheet status to Preliminary. Finalized production timing parameters. All speed grades for all Spartan-3E FPGAs are now Production status using the v1.21 speed files, as shown in Table 84. Expanded description in Note 2, Table 78. Updated pin-to-pin and clock-to-output timing based on final characterization, shown in Table 86. Updated system-synchronous input setup and hold times based on final characterization, shown in Table 87 and Table 88. Updated other I/O timing in Table 90. Provided input and output adjustments for LVPECL_25, DIFF_SSTL and DIFF_HSTL I/O standards that supersede the v1.21 speed file values, in Table 91 and Table 94. Reduced I/O three-state and set/reset delays in Table 93. Added XC3S100E FPGA in CP132 package to Table 96. Increased T <sub>AS</sub> slice flip-flop timing by 100 ps in Table 98. Updated distributed RAM timing in Table 99 and SRL16 timing in Table 100. Updated global clock timing, removed left/right clock buffer limits in Table 101. Updated block RAM timing in Table 103. Added DCM parameters for remainder of Step 0 device; added improved Step 1 DCM performance to Table 104, Table 105, Table 106, and Table 107. Added minimum INIT_B pulse width specification, T <sub>INIT</sub> , in Table 111. Increased data hold time for Slave Parallel mode to 1.0 ns (T <sub>SMCCD</sub> ) in Table 106, and Table 107. Corrected links in Table 118 and Table 120. Added MultiBoot timing specifications to Table 122. |

| 04/07/06 | 3.1     | Improved SSO limits for LVDS_25, MINI_LVDS_25, and RSDS_25 I/O standards in the QFP packages (Table 97). Removed potentially confusing Note 2 from Table 78.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 05/19/06 | 3.2     | Clarified that 100 mV of hysteresis applies to LVCMOS33 and LVCMOS25 I/O standards (Note 4, Table 80). Other minor edits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 05/30/06 | 3.2.1   | Corrected various typos and incorrect links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11/09/06 | 3.4     | Improved absolute maximum voltage specifications in Table 73, providing additional overshoot allowance. Widened the recommended voltage range for PCI and PCI-X standards in Table 80. Clarified Note 2, Table 83. Improved various timing specifications for v1.26 speed file. Added Table 85 to summarize the history of speed file releases after which time all devices became Production status. Added absolute minimum values for Table 86, Table 92, and Table 93. Updated pin-to-pin setup and hold timing based on default IFD_DELAY_VALUE settings in Table 87, Table 88, and Table 90. Added Table 89 about source-synchronous input capture sample window. Promoted Module 3 to Production status. Synchronized all modules to v3.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 03/16/07 | 3.5     | Based on extensive 90 nm production data, improved (reduced) the maximum quiescent current limits for the $I_{CCINTQ}$ , $I_{CCAUXQ}$ , and $I_{CCOQ}$ specifications in Table 79 by an average of 50%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 05/29/07 | 3.6     | Added note to Table 74 and Table 75 regarding HSWAP in step 0 devices. Updated t <sub>RPW_CLB</sub> in Table 98 to match value in speed file. Improved CLKOUT_FREQ_CLK90 to 200 MHz for Stepping 1 in Table 105.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 04/18/08 | 3.7     | Clarified that Stepping 0 was offered only for -4C and removed Stepping 0 -5 specifications. Added reference to XAPP459 in Table 73 and Table 77. Improved recommended max $V_{CCO}$ to 3.465V (3.3V + 5%) in Table 77. Removed minimum input capacitance from Table 78. Updated Recommended Operating Conditions for LVCMOS and PCI I/O standards in Table 80. Removed Absolute Minimums from Table 86, Table 92 and Table 93 and added footnote recommending use of Timing Analyzer for minimum values. Updated T <sub>PSFD</sub> and T <sub>PHFD</sub> in Table 87 to match current speed file. Update T <sub>RPW_IOB</sub> in Table 88 to match current speed file and CLB equivalent spec. Added XC3S500E VQG100 to Table 96. Replaced T <sub>MULCKID</sub> with T <sub>MSCKD</sub> for A, B, and P registers in Table 102. Updated CLKOUT_PER_JITT_FX in Table 107. Updated MAX_STEPS equation in Table 109. Updated Figure 77 and Table 120 to correct CCLK active edge. Updated links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08/26/09 | 3.8     | Added reference to XAPP459 in Table 73 note 2. Updated BPI timing in Figure 77, Table 119, and Table 120. Removed V <sub>REF</sub> requirements for differential HSTL and differential SSTL in Table 95. Added Spread Spectrum paragraph. Revised hold times for $T_{IOICKPD}$ in Table 88 and setup times for $T_{DICK}$ in Table 98. Added note 4 to Table 106 and note 3 to Table 107, and updated note 6 for Table 107 to add input jitter. |

| 10/29/12 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs. Revised note 2 in Table 73. Revised note 2 and $V_{\rm IN}$ description in Table 77, and added note 5. Added note 3 to Table 78.                                                                                                                                                                                                                                   |

## **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### **CRITICAL APPLICATIONS DISCLAIMER**