# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                        |

|--------------------------------|---------------------------------------------------------------|

| Number of LABs/CLBs            | 240                                                           |

| Number of Logic Elements/Cells | 2160                                                          |

| Total RAM Bits                 | 73728                                                         |

| Number of I/O                  | 66                                                            |

| Number of Gates                | 100000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 100-TQFP                                                      |

| Supplier Device Package        | 100-VQFP (14x14)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s100e-5vqg100c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Input Delay Functions**

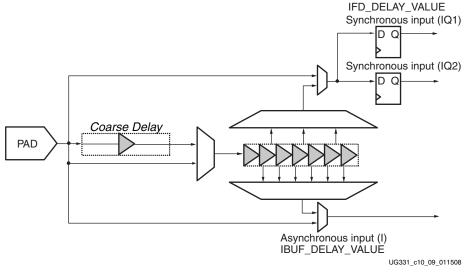

Each IOB has a programmable delay block that optionally delays the input signal. In Figure 6, the signal path has a coarse delay element that can be bypassed. The input signal then feeds a 6-tap delay line. The coarse and tap delays vary; refer to timing reports for specific delay values. All six taps are available via a multiplexer for use as an asynchronous input directly into the FPGA fabric. In this way, the delay is programmable in 12 steps. Three of the six taps are also available via a multiplexer to the D inputs of the synchronous storage elements. The delay inserted in the path to the storage element can be varied in six steps. The first, coarse delay element is common to both asynchronous and synchronous paths, and must be either used or not used for both paths.

The delay values are set up in the silicon once at configuration time—they are non-modifiable in device operation.

The primary use for the input delay element is to adjust the input delay path to ensure that there is no hold time requirement when using the input flip-flop(s) with a global clock. The default value is chosen automatically by the Xilinx software tools as the value depends on device size and the specific device edge where the flip-flop resides. The value set by the Xilinx ISE software is indicated in the Map report generated by the implementation tools, and the resulting effects on input timing are reported using the Timing Analyzer tool.

If the design uses a DCM in the clock path, then the delay element can be safely set to zero because the Delay-Locked Loop (DLL) compensation automatically ensures that there is still no input hold time requirement.

Both asynchronous and synchronous values can be modified, which is useful where extra delay is required on clock or data inputs, for example, in interfaces to various types of RAM.

These delay values are defined through the IBUF\_DELAY\_VALUE and the IFD\_DELAY\_VALUE parameters. The default IBUF\_DELAY\_VALUE is 0, bypassing the delay elements for the asynchronous input. The user can set this parameter to 0-12. The default IFD\_DELAY\_VALUE is AUTO. IBUF\_DELAY\_VALUE and IFD\_DELAY\_VALUE are independent for each input. If the same input pin uses both registered and non-registered input paths, both parameters can be used, but they must both be in the same half of the total delay (both either bypassing or using the coarse delay element).

Figure 6: Programmable Fixed Input Delay Elements

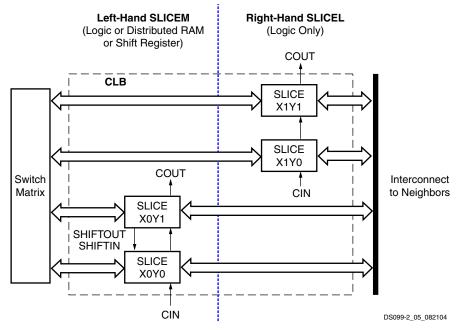

Figure 16: Arrangement of Slices within the CLB

#### **Slice Location Designations**

The Xilinx development software designates the location of a slice according to its X and Y coordinates, starting in the bottom left corner, as shown in Figure 14. The letter 'X' followed by a number identifies columns of slices, incrementing from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row, incrementing from the bottom of the die. Figure 16 shows the CLB located in the lower left-hand corner of the die. The SLICEM always has an even 'X' number, and the SLICEL always has an odd 'X' number.

### **Slice Overview**

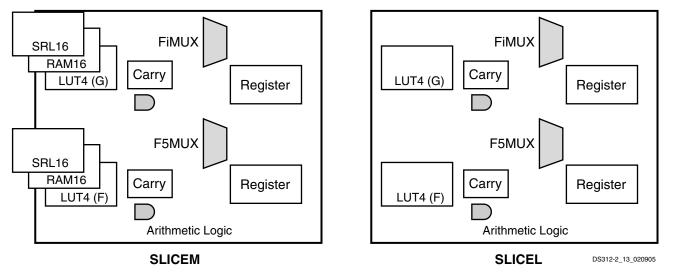

A slice includes two LUT function generators and two storage elements, along with additional logic, as shown in Figure 17.

Both SLICEM and SLICEL have the following elements in common to provide logic, arithmetic, and ROM functions:

- Two 4-input LUT function generators, F and G

- Two storage elements

- Two wide-function multiplexers, F5MUX and FiMUX

- Carry and arithmetic logic

initialized distributed RAM contents are not disturbed during the configuration process.

The distributed RAM is useful for smaller amounts of memory. Larger memory requirements can use the dedicated 18Kbit RAM blocks (see Block RAM).

## **Shift Registers**

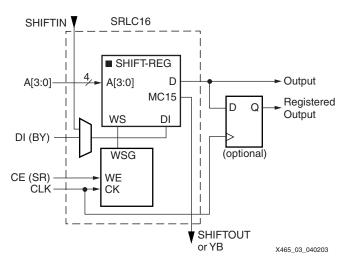

For additional information, refer to the "Using Look-Up Tables as Shift Registers (SRL16)" chapter in UG331.

It is possible to program each SLICEM LUT as a 16-bit shift register (see Figure 28). Used in this way, each LUT can delay serial data anywhere from 1 to 16 clock cycles without using any of the dedicated flip-flops. The resulting programmable delays can be used to balance the timing of data pipelines.

The SLICEM LUTs cascade from the G-LUT to the F-LUT through the DIFMUX (see Figure 15). SHIFTIN and SHIFTOUT lines cascade a SLICEM to the SLICEM below to form larger shift registers. The four SLICEM LUTs of a single CLB can be combined to produce delays up to 64 clock cycles. It is also possible to combine shift registers across more than one CLB.

Figure 28: Logic Cell SRL16 Structure

Each shift register provides a shift output MC15 for the last bit in each LUT, in addition to providing addressable access to any bit in the shift register through the normal D output. The address inputs A[3:0] are the same as the distributed RAM address lines, which come from the LUT inputs F[4:1] or G[4:1]. At the end of the shift register, the CLB flip-flop can be used to provide one more shift delay for the addressable bit.

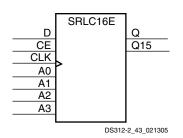

The shift register element is known as the SRL16 (Shift Register LUT 16-bit), with a 'C' added to signify a cascade ability (Q15 output) and 'E' to indicate a Clock Enable. See Figure 29 for an example of the SRLC16E component.

# Figure 29: SRL16 Shift Register Component with Cascade and Clock Enable

The functionality of the shift register is shown in Table 20. The SRL16 shifts on the rising edge of the clock input when the Clock Enable control is High. This shift register cannot be initialized either during configuration or during operation except by shifting data into it. The clock enable and clock inputs are shared between the two LUTs in a SLICEM. The clock enable input is automatically kept active if unused.

| Table | 20: | SRL16 | Shift | Register | Function |

|-------|-----|-------|-------|----------|----------|

|-------|-----|-------|-------|----------|----------|

| Inputs |     |    |   | Outputs       |       |  |

|--------|-----|----|---|---------------|-------|--|

| Am     | CLK | CE | D | Q Q15         |       |  |

| Am     | Х   | 0  | Х | Q[Am]         | Q[15] |  |

| Am     | 1   | 1  | D | Q[Am-1] Q[15] |       |  |

Notes:

1. m = 0, 1, 2, 3.

## **Block RAM Port Signal Definitions**

Representations of the dual-port primitive RAMB16\_S[ $w_A$ ]\_S[ $w_B$ ] and the single-port primitive RAMB16\_S[w] with their associated signals are shown in Figure 32a and Figure 32b, respectively. These signals are defined in Table 23. The control signals (WE, EN, CLK, and SSR) on the block RAM are active High. However, optional inverters on the control signals change the polarity of the active edge to active Low.

#### Design Note

Whenever a block RAM port is enabled (ENA or ENB = High), all address transitions must meet the data sheet setup and hold times with respect to the port clock (CLKA or CLKB), as shown in Table 103, page 138.This requirement must be met even if the RAM read output is of no interest.

#### Notes:

- 1. w<sub>A</sub> and w<sub>B</sub> are integers representing the total data path width (i.e., data bits plus parity bits) at Ports A and B, respectively.

- 2. p<sub>A</sub> and p<sub>B</sub> are integers that indicate the number of data path lines serving as parity bits.

- 3. r<sub>A</sub> and r<sub>B</sub> are integers representing the address bus width at ports A and B, respectively.

- 4. The control signals CLK, WE, EN, and SSR on both ports have the option of inverted polarity.

#### Figure 32: Block RAM Primitives

### Table 23: Block RAM Port Signals

| Signal<br>Description    | Port A<br>Signal<br>Name | Port B<br>Signal<br>Name | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|--------------------------|--------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address Bus              | ADDRA                    | ADDRB                    | Input     | The Address Bus selects a memory location for read or write operations.<br>The width (w) of the port's associated data path determines the number of<br>available address lines (r), as per Table 22.                                                                                                                                                                                                                                                                                                                                          |

|                          |                          |                          |           | Whenever a port is enabled (ENA or ENB = High), address transitions must<br>meet the data sheet setup and hold times with respect to the port clock<br>(CLKA or CLKB), as shown in Table 103, page 138. This requirement must<br>be met even if the RAM read output is of no interest.                                                                                                                                                                                                                                                         |

| Data Input Bus           | DIA                      | DIB                      | Input     | Data at the DI input bus is written to the RAM location specified by the address input bus (ADDR) during the active edge of the CLK input, when the clock enable (EN) and write enable (WE) inputs are active.                                                                                                                                                                                                                                                                                                                                 |

|                          |                          |                          |           | It is possible to configure a port's DI input bus width (w-p) based on Table 22. This selection applies to both the DI and DO paths of a given port.                                                                                                                                                                                                                                                                                                                                                                                           |

| Parity Data Input(s)     | DIPA                     | DIPB                     | Input     | Parity inputs represent additional bits included in the data input path.<br>Although referred to herein as "parity" bits, the parity inputs and outputs<br>have no special functionality for generating or checking parity and can be<br>used as additional data bits. The number of parity bits 'p' included in the DI<br>(same as for the DO bus) depends on a port's total data path width (w). See<br>Table 22.                                                                                                                            |

| Data Output Bus          | DOA                      | DOB                      | Output    | Data is written to the DO output bus from the RAM location specified by the address input bus, ADDR. See the DI signal description for DO port width configurations.                                                                                                                                                                                                                                                                                                                                                                           |

|                          |                          |                          |           | Basic data access occurs on the active edge of the CLK when WE is<br>inactive and EN is active. The DO outputs mirror the data stored in the<br>address ADDR memory location. Data access with WE active if the<br>WRITE_MODE attribute is set to the value: WRITE_FIRST, which<br>accesses data after the write takes place. READ_FIRST accesses data<br>before the write occurs. A third attribute, NO_CHANGE, latches the DO<br>outputs upon the assertion of WE. See Block RAM Data Operations for<br>details on the WRITE_MODE attribute. |

| Parity Data<br>Output(s) | DOPA                     | DOPB                     | Output    | Parity outputs represent additional bits included in the data input path. The number of parity bits 'p' included in the DI bus (same as for the DO bus) depends on a port's total data path width (w). See the DIP signal description for configuration details.                                                                                                                                                                                                                                                                               |

| Write Enable             | WEA                      | WEB                      | Input     | When asserted together with EN, this input enables the writing of data to the RAM. When WE is inactive with EN asserted, read operations are still possible. In this case, a latch passes data from the addressed memory location to the DO outputs.                                                                                                                                                                                                                                                                                           |

| Clock Enable             | ENA                      | ENB                      | Input     | When asserted, this input enables the CLK signal to perform read and write operations to the block RAM. When inactive, the block RAM does not perform any read or write operations.                                                                                                                                                                                                                                                                                                                                                            |

| Set/Reset                | SSRA                     | SSRB                     | Input     | When asserted, this pin forces the DO output latch to the value of the SRVAL attribute. It is synchronized to the CLK signal.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Clock                    | CLKA                     | CLKB                     | Input     | This input accepts the clock signal to which read and write operations are synchronized. All associated port inputs are required to meet setup times with respect to the clock signal's active edge. The data output bus responds after a clock-to-out delay referenced to the clock signal's active edge.                                                                                                                                                                                                                                     |

## **Digital Clock Managers (DCMs)**

For additional information, refer to the "Using Digital Clock Managers (DCMs)" chapter in  $\underline{\text{UG331}}$ .

## **Differences from the Spartan-3 Architecture**

- Spartan-3E FPGAs have two, four, or eight DCMs, depending on device size.

- The variable phase shifting feature functions differently on Spartan-3E FPGAs than from Spartan-3 FPGAs.

- The Spartan-3E DLLs support lower input frequencies, down to 5 MHz. Spartan-3 DLLs support down to 18 MHz.

## Overview

Spartan-3E FPGA Digital Clock Managers (DCMs) provide flexible, complete control over clock frequency, phase shift and skew. To accomplish this, the DCM employs a Delay-Locked Loop (DLL), a fully digital control system that uses feedback to maintain clock signal characteristics with a high degree of precision despite normal variations in operating temperature and voltage. This section provides a fundamental description of the DCM.

The XC3S100E FPGA has two DCMs, one at the top and one at the bottom of the device. The XC3S250E and XC3S500E FPGAs each include four DCMs, two at the top and two at the bottom. The XC3S1200E and XC3S1600E FPGAs contain eight DCMs with two on each edge (see also Figure 45). The DCM in Spartan-3E FPGAs is surrounded by CLBs within the logic array and is no longer located at the top and bottom of a column of block RAM as in the Spartan-3 architecture. The Digital Clock Manager is instantiated within a design using a "DCM" primitive.

The DCM supports three major functions:

- **Clock-skew Elimination:** Clock skew within a system occurs due to the different arrival times of a clock signal at different points on the die, typically caused by the clock signal distribution network. Clock skew increases setup and hold time requirements and increases clock-to-out times, all of which are undesirable in high frequency applications. The DCM eliminates clock skew by phase-aligning the output clock signal that it generates with the incoming clock signal. This mechanism effectively cancels out the clock distribution delays.

- **Frequency Synthesis:** The DCM can generate a wide range of different output clock frequencies derived from the incoming clock signal. This is accomplished by either multiplying and/or dividing the frequency of the input clock signal by any of several different factors.

- **Phase Shifting:** The DCM provides the ability to shift the phase of all its output clock signals with respect to the input clock signal.

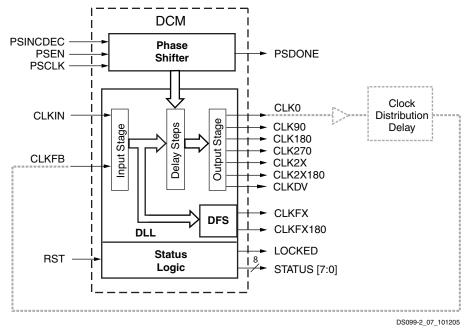

Although a single design primitive, the DCM consists of four interrelated functional units: the Delay-Locked Loop (DLL), the Digital Frequency Synthesizer (DFS), the Phase Shifter (PS), and the Status Logic. Each component has its associated signals, as shown in Figure 40.

Figure 40: DCM Functional Blocks and Associated Signals

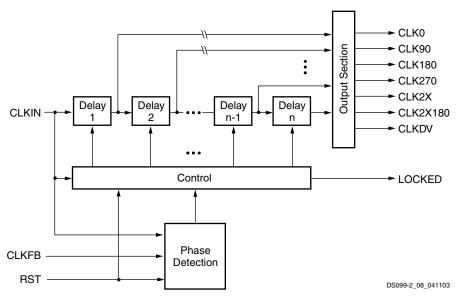

## Delay-Locked Loop (DLL)

The most basic function of the DLL component is to eliminate clock skew. The main signal path of the DLL consists of an input stage, followed by a series of discrete delay elements or *steps*, which in turn leads to an output stage. This path together with logic for phase detection and control forms a system complete with feedback as shown in Figure 41. In Spartan-3E FPGAs, the DLL is implemented using a counter-based delay line. The DLL component has two clock inputs, CLKIN and CLKFB, as well as seven clock outputs, CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV as described in Table 28. The clock outputs drive simultaneously. Signals that initialize and report the state of the DLL are discussed in Status Logic.

Figure 41: Simplified Functional Diagram of DLL

#### Table 28: DLL Signals

| Signal   | Direction | Description                                                                                                                |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| CLKIN    | Input     | Receives the incoming clock signal. See Table 30, Table 31, and Table 32 for optimal external inputs to a DCM.             |

| CLKFB    | Input     | Accepts either CLK0 or CLK2X as the feedback signal. (Set the CLK_FEEDBACK attribute accordingly).                         |

| CLK0     | Output    | Generates a clock signal with the same frequency and phase as CLKIN.                                                       |

| CLK90    | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 90°.                                           |

| CLK180   | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 180°.                                          |

| CLK270   | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 270°.                                          |

| CLK2X    | Output    | Generates a clock signal with the same phase as CLKIN, and twice the frequency.                                            |

| CLK2X180 | Output    | Generates a clock signal with twice the frequency of CLKIN, and phase-shifted 180° with respect to CLK2X.                  |

| CLKDV    | Output    | Divides the CLKIN frequency by CLKDV_DIVIDE value to generate lower frequency clock signal that is phase-aligned to CLKIN. |

The clock signal supplied to the CLKIN input serves as a reference waveform. The DLL seeks to align the rising-edge of feedback signal at the CLKFB input with the rising-edge of CLKIN input. When eliminating clock skew, the common approach to using the DLL is as follows: The CLK0 signal is passed through the clock distribution network that feeds all the registers it synchronizes. These registers are either

internal or external to the FPGA. After passing through the clock distribution network, the clock signal returns to the DLL via a feedback line called CLKFB. The control block inside the DLL measures the phase error between CLKFB and CLKIN. This phase error is a measure of the clock skew that the clock distribution network introduces. The control block activates the appropriate number of delay steps to

**E** XILINX.

SPI serial Flash PROMs and the Atmel AT45DB-series Data Flash PROMs using the <u>Platform Cable USB</u>, <u>Xilinx</u> <u>Parallel IV</u>, or other compatible programming cable.

## Byte-Wide Peripheral Interface (BPI) Parallel Flash Mode

For additional information, refer to the "Master BPI Mode" chapter in UG332.

In Byte-wide Peripheral Interface (BPI) mode (M[2:0] = <0:1:0> or <0:1:1>), a Spartan-3E FPGA configures itself from an industry-standard parallel NOR Flash PROM, as illustrated in Figure 58. The FPGA generates up to a 24-bit address lines to access an attached parallel Flash. Only 20 address lines are generated for Spartan-3E FPGAs in the TQ144 package. Similarly, the XC3S100E FPGA in the CP132 package only has 20 address lines while the XC3S250E and XC3S500E FPGAs in the same package have 24 address lines. When using the VQ100 package, the BPI mode is not available when using parallel NOR Flash, but is supported using parallel Platform Flash (XCFxxP).

The BPI configuration interface is primarily designed for standard parallel NOR Flash PROMs and supports both byte-wide (x8) and byte-wide/halfword (x8/x16) PROMs. The interface functions with halfword-only (x16) PROMs, but the upper byte in a portion of the PROM remains unused. For configuration, the BPI interface does not require any specific Flash PROM features, such as boot block or a specific sector size.

The BPI interface also functions with Xilinx parallel Platform Flash PROMs (XCFxxP), although the FPGA's address lines are left unconnected.

The BPI interface also works equally wells with other asynchronous memories that use a similar SRAM-style interface such as SRAM, NVRAM, EEPROM, EPROM, or masked ROM.

NAND Flash memory is commonly used in memory cards for digital cameras. Spartan-3E FPGAs do not configure directly from NAND Flash memories.

The FPGA's internal oscillator controls the interface timing and the FPGA supplies the clock on the CCLK output pin. However, the CCLK signal is not used in single FPGA applications. Similarly, the FPGA drives three pins Low during configuration (LDC[2:0]) and one pin High during configuration (HDC) to the PROM's control inputs. can also be eliminated from the interface. However, RDWR\_B must remain Low during configuration.

After configuration, all of the interface pins except DONE and PROG\_B are available as user I/Os. Alternatively, the bidirectional SelectMAP configuration interface is available after configuration. To continue using SelectMAP mode, set the **Persist** bitstream generator option to **Yes**. The external host can then read and verify configuration data. The Persist option will maintain A20-A23 as configuration pins although they are not used in SelectMAP mode.

The Slave Parallel mode is also used with BPI mode to create multi-FPGA daisy-chains. The lead FPGA is set for BPI mode configuration; all the downstream daisy-chain FPGAs are set for Slave Parallel configuration, as highlighted in Figure 59.

| Pin Name | FPGA Direction | Description                                                                                                                                                                                            | During Configuration                                                                                                                                                                                            | After Configuration                                                                                                     |

|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| HSWAP    | Input          | <b>User I/O Pull-Up Control</b> . When<br>Low during configuration, enables<br>pull-up resistors in all I/O pins to<br>respective I/O bank V <sub>CCO</sub> input.<br>0: Pull-ups during configuration | Drive at valid logic level throughout configuration.                                                                                                                                                            | User I/O                                                                                                                |

|          |                | 1: No pull-ups                                                                                                                                                                                         |                                                                                                                                                                                                                 |                                                                                                                         |

| M[2:0]   | Input          | <b>Mode Select</b> . Selects the FPGA configuration mode. See Design Considerations for the HSWAP, M[2:0], and VS[2:0] Pins.                                                                           | M2 = 1, M1 = 1, M0 = 0 Sampled<br>when INIT_B goes High.                                                                                                                                                        | User I/O                                                                                                                |

| D[7:0]   | Input          | Data Input.                                                                                                                                                                                            | Byte-wide data provided by host.<br>FPGA captures data on rising<br>CCLK edge.                                                                                                                                  | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |

| BUSY     | Output         | Busy Indicator.                                                                                                                                                                                        | If CCLK frequency is < 50 MHz,<br>this pin may be ignored. When<br>High, indicates that the FPGA is<br>not ready to receive additional<br>configuration data. Host must hold<br>data an additional clock cycle. | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |

| CSI_B    | Input          | Chip Select Input. Active Low.                                                                                                                                                                         | Must be Low throughout configuration.                                                                                                                                                                           | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |

| RDWR_B   | Input          | <b>Read/Write Control</b> . Active Low write enable.                                                                                                                                                   | Must be Low throughout configuration.                                                                                                                                                                           | User I/O. If bitstream<br>option <i>Persist=Yes</i> ,<br>becomes part of<br>SelectMap parallel<br>peripheral interface. |

| CCLK     | Input          | <b>Configuration Clock</b> . If CCLK PCB trace is long or has multiple connections, terminate this output to maintain signal integrity. See CCLK Design Considerations.                                | External clock.                                                                                                                                                                                                 | User I/O If bitstream option<br><i>Persist=Yes</i> , becomes<br>part of SelectMap parallel<br>peripheral interface.     |

| CSO_B    | Output         | Chip Select Output. Active Low.                                                                                                                                                                        | Not used in single FPGA<br>applications. In a daisy-chain<br>configuration, this pin connects to<br>the CSI_B pin of the next FPGA in<br>the chain. Actively drives.                                            | User I/O                                                                                                                |

#### Table 65: Slave Parallel Mode Connections

## **EXILINX**.

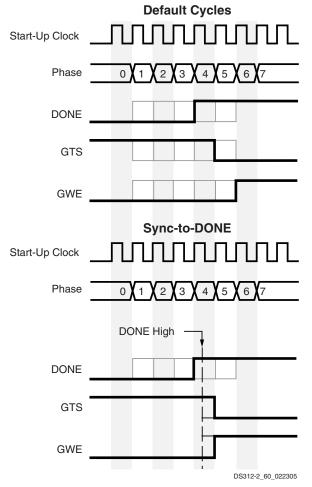

## Start-Up

At the end of configuration, the FPGA automatically pulses the Global Set/Reset (GSR) signal, placing all flip-flops in a known state. After configuration completes, the FPGA switches over to the user application loaded into the FPGA. The sequence and timing of how the FPGA switches over is programmable as is the clock source controlling the sequence.

The default start-up sequence appears in Figure 68, where the Global Three-State signal (GTS) is released one clock cycle after DONE goes High. This sequence allows the DONE signal to enable or disable any external logic used during configuration before the user application in the FPGA starts driving output signals. One clock cycle later, the Global Write Enable (GWE) signal is released. This allows signals to propagate within the FPGA before any clocked storage elements such as flip-flops and block ROM are enabled.

Figure 68: Default Start-Up Sequence

The function of the dual-purpose I/O pins, such as M[2:0], VS[2:0], HSWAP, and A[23:0], also changes when the DONE pin goes High. When DONE is High, these pins

become user I/Os. Like all user-I/O pins, GTS controls when the dual-purpose pins can drive out.

The relative timing of configuration events is programmed via the Bitstream Generator (BitGen) options in the Xilinx development software. For example, the GTS and GWE events can be programmed to wait for all the DONE pins to High on all the devices in a multiple-FPGA daisy-chain, forcing the FPGAs to start synchronously. Similarly, the start-up sequence can be paused at any stage, waiting for selected DCMs to lock to their respective input clock signals. See also Stabilizing DCM Clocks Before User Mode.

By default, the start-up sequence is synchronized to CCLK. Alternatively, the start-up sequence can be synchronized to a user-specified clock from within the FPGA application using the STARTUP\_SPARTAN3E library primitive and by setting the *StartupClk* bitstream generator option. The FPGA application can optionally assert the GSR and GTS signals via the STARTUP\_SPARTAN3E primitive. For JTAG configuration, the start-up sequence can be synchronized to the TCK clock input.

## **Bitstream Generator (BitGen) Options**

For additional information, refer to the "Configuration Bitstream Generator (BitGen) Settings" chapter in UG332.

Various Spartan-3E FPGA functions are controlled by specific bits in the configuration bitstream image. These

values are specified when creating the bitstream image with the Bitstream Generator (BitGen) software.

Table 69 provides a list of all BitGen options for Spartan-3EFPGAs.

#### Table 69: Spartan-3E FPGA Bitstream Generator (BitGen) Options

| Option Name | Pins/Function<br>Affected                            | Values<br>( <i>default</i> )   | Description                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ConfigRate  | CCLK,<br>Configuration                               | <u>1</u> , 3, 6,<br>12, 25, 50 | Sets the approximate frequency, in MHz, of the internal oscillator using for Master Serial, SPI, and BPI configuration modes. The internal oscillator powers up at its lowest frequency, and the new setting is loaded as part of the configuration bitstream. The software default value is 1 (~1.5 MHz) starting with ISE 8.1, Service Pack 1. |

| StartupClk  | Configuration,<br>Startup                            | <u>Cclk</u>                    | <b>Default.</b> The CCLK signal (internally or externally generated) controls the startup sequence when the FPGA transitions from configuration mode to the user mode. See Start-Up.                                                                                                                                                             |

|             |                                                      | UserClk                        | A clock signal from within the FPGA application controls the startup sequence when the FPGA transitions from configuration mode to the user mode. See Start-Up. The FPGA application supplies the user clock on the CLK pin on the STARTUP_SPARTAN3E primitive.                                                                                  |

|             |                                                      | Jtag                           | The JTAG TCK input controls the startup sequence when the FPGA transitions from the configuration mode to the user mode. See <u>Start-Up</u> .                                                                                                                                                                                                   |

| UnusedPin   | Unused I/O                                           | Pulldown                       | Default. All unused I/O pins and input-only pins have a pull-down resistor to GND.                                                                                                                                                                                                                                                               |

|             | Pins                                                 | Pullup                         | All unused I/O pins and input-only pins have a pull-up resistor to the VCCO_# supply for its associated I/O bank.                                                                                                                                                                                                                                |

|             |                                                      | Pullnone                       | All unused I/O pins and input-only pins are left floating (Hi-Z, high-impedance, three-state). Use external pull-up or pull-down resistors or logic to apply a valid signal level.                                                                                                                                                               |

| DONE_cycle  | DONE pin,<br>Configuration<br>Startup                | 1, 2, 3, <u>4</u> ,<br>5, 6    | Selects the Configuration Startup phase that activates the FPGA's DONE pin. See Start-Up.                                                                                                                                                                                                                                                        |

| GWE_cycle   | All flip-flops,<br>LUT RAMs, and<br>SRL16 shift      | 1, 2, 3, 4,<br>5, <u>6</u>     | Selects the Configuration Startup phase that asserts the internal write-enable signal to all flip-flops, LUT RAMs and shift registers (SRL16). It also enables block RAM read and write operations. See Start-Up.                                                                                                                                |

|             | registers, Block<br>RAM,<br>Configuration<br>Startup | Done                           | Waits for the DONE pin input to go High before asserting the internal write-enable signal to all flip-flops, LUT RAMs and shift registers (SRL16). Block RAM read and write operations are enabled at this time.                                                                                                                                 |

|             |                                                      | Keep                           | Retains the current GWE_cycle setting for partial reconfiguration applications.                                                                                                                                                                                                                                                                  |

| GTS_cycle   | All I/O pins,<br>Configuration                       | 1, 2, 3, 4,<br><u>5</u> , 6    | Selects the Configuration Startup phase that releases the internal three-state control, holding all I/O buffers in high-impedance (Hi-Z). Output buffers actively drive, if so configured, after this point. See Start-Up.                                                                                                                       |

|             |                                                      | Done                           | Waits for the DONE pin input to go High before releasing the internal three-state control, holding all I/O buffers in high-impedance (Hi-Z). Output buffers actively drive, if so configured, after this point.                                                                                                                                  |

|             |                                                      | Keep                           | Retains the current GTS_cycle setting for partial reconfiguration applications.                                                                                                                                                                                                                                                                  |

| LCK_cycle   | DCMs,                                                | <u>NoWait</u>                  | The FPGA does not wait for selected DCMs to lock before completing configuration.                                                                                                                                                                                                                                                                |

|             | Configuration<br>Startup                             | 0, 1, 2, 3,<br>4, 5, 6         | If one or more DCMs in the design have the STARTUP_WAIT attribute set to TRUE, the FPGA waits for such DCMs to acquire their respective input clock and assert their LOCKED output. This setting selects the Configuration Startup phase where the FPGA waits for the DCMs to lock.                                                              |

| DonePin     | DONE pin                                             | <u>Pullup</u>                  | Internally connects a pull-up resistor between DONE pin and V <sub>CCAUX</sub> . An external 330 $\Omega$ pull-up resistor to V <sub>CCAUX</sub> is still recommended.                                                                                                                                                                           |

|             |                                                      | Pullnone                       | No internal pull-up resistor on DONE pin. An external 330 $\Omega$ pull-up resistor to $V_{\text{CCAUX}}$ is required.                                                                                                                                                                                                                           |

## **Production Stepping**

The Spartan-3E FPGA family uses production stepping to indicate improved capabilities or enhanced features.

Stepping 1 is, by definition, a functional superset of Stepping 0. Furthermore, configuration bitstreams generated for Stepping 0 are compatible with Stepping 1. Designs operating on the Stepping 0 devices perform similarly on a Stepping 1 device.

## **Differences Between Steppings**

Table 71 summarizes the feature and performancedifferences between Stepping 0 devices and Stepping 1devices.

### Table 71: Differences between Spartan-3E Production Stepping Levels

|                                                                                                                     | Stepping 0                                                                                  | Stepping 1                                                |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Production status                                                                                                   | Production from 2005 to 2007                                                                | Production starting<br>March 2006                         |

| Speed grade and operating conditions                                                                                | -4C only                                                                                    | -4C, -4I, -5C                                             |

| JTAG ID code                                                                                                        | Different revision fields. Se                                                               | e Table 67.                                               |

| DCM DLL maximum input frequency                                                                                     | 90 MHz<br>(200 MHz for XC3S1200E)                                                           | 240 MHz (-4 speed grade)<br>275 MHz (-5 speed grade)      |

| DCM DFS output frequency range(s)                                                                                   | Split ranges at 5 – 90 MHz and<br>220 – 307 MHz<br>(single range 5 – 307 MHz for XC3S1200E) | Continuous range:<br>5 – 311 MHz (-4)<br>5 – 333 MHz (-5) |

| Supports multi-FPGA daisy-chain configurations from SPI Flash                                                       | No, single FPGA only                                                                        | Yes                                                       |

| JTAG configuration supported when FPGA in BPI<br>mode with a valid image in the attached parallel NOR<br>Flash PROM | No <sup>(1)</sup>                                                                           | Yes                                                       |

| JTAG EXTEST, INTEST, SAMPLE support                                                                                 | Yes: XC3S100E, XC3S250E, XC3S500E<br>No <sup>(2)</sup> : XC3S1200E, XC3S1600E               | Yes<br>All Devices                                        |

| Power sequencing when using HSWAP Pull-Up                                                                           | Requires V <sub>CCINT</sub> before V <sub>CCAUX</sub>                                       | Any sequence                                              |

| PCI compliance                                                                                                      | No                                                                                          | Yes                                                       |

#### Notes:

1. Workarounds exist. See Stepping 0 Limitations when Reprogramming via JTAG if FPGA Set for BPI Configuration.

2. JTAG BYPASS and JTAG configuration are supported

## **Ordering a Later Stepping**

-5C and -4I devices, and -4C devices (with date codes 0901 (2009) and later) always support the Stepping 1 feature set independent of the stepping code. Optionally, to order only Stepping 1 for the -4C devices, append an "S1" suffix to the standard ordering code, where '1' is the stepping number, as indicated in Table 72.

#### Table 72: Spartan-3E Optional Stepping Ordering

| Stepping<br>Number | Suffix Code | Status     |

|--------------------|-------------|------------|

| 0                  | None        | Production |

| 1                  | S1          | Production |

## **Software Version Requirements**

Production Spartan-3E applications must be processed using the Xilinx ISE 8.1i, Service Pack 3 or later development software, using the v1.21 or later speed files. The ISE 8.1i software implements critical bitstream generator updates.

For additional information on Spartan-3E development software and known issues, see the following Answer Record:

• Xilinx Answer #22253 http://www.xilinx.com/support/answers/22253.htm

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/16/07 | 3.5     | Added information about new Spartan-3 Generation user guides (Design Documentation Available).<br>Added cross-references to <u>UG331</u> : <i>Spartan-3 Generation FPGA User Guide</i> and to <u>UG332</u> : <i>Spartan-3 Generation Configuration User Guide</i> . Added note about possible JTAG configuration issues when the FPGA mode pins are set for Master mode and using software prior to ISE 9.1.01i (JTAG Mode).<br>Removed a few lingering references to "weak" pull-up resistors, including in Figure 12. Removed vestigial references regarding the LDC[2:0] and HDC pins during Slave Parallel Mode configuration.<br>These pins are not used in this configuration mode. |

| 05/29/07 | 3.6     | Added information about HSWAP and PCI differences between steppings to Table 71. Removed<br>"Performance Differences between Global Buffers" to match improved specs in Module 3. Updated<br>PROG_B pulse width descriptions to match specification in Module 3.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 04/18/08 | 3.7     | Corrected Figure 6 to show six taps and updated associated text. Added note for recommended pull-up on DONE in Table 55 and elsewhere. Added a caution regarding Persist of pins A20-A23. Updated Stepping description in Table 71 to note that only Stepping 1 is in production today. Updated links.                                                                                                                                                                                                                                                                                                                                                                                    |

| 08/26/09 | 3.8     | Added a frequency limitation to Equation 6. Added a new Equation 7 with a frequency limitation. Added a Spread Spectrum, page 56 paragraph. Added Table 42, page 60. Updated a Flash vendor name in Table 61, page 88. Removed the < symbol from the flash read access times in Table 62, page 88. Revised the first paragraph in Configuration Sequence, page 101. Revised the first paragraph in Power-On Behavior, page 110. Revised the second paragraph in Production Stepping, page 111. Revised the first paragraph in Ordering a Later Stepping, page 111.                                                                                                                        |

| 10/29/12 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs.<br>Updated the design note section in VARIABLE Phase Shift Mode. Added the VQ100 to the Quadrant Clock Routing section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

### **General Recommended Operating Conditions**

#### Table 77: General Recommended Operating Conditions

| Symbol                           | Description                                 |                                                           |            |       | Nominal           | Max                    | Units |

|----------------------------------|---------------------------------------------|-----------------------------------------------------------|------------|-------|-------------------|------------------------|-------|

| ТJ                               | Junction temperature                        | Commercial                                                | 0          | -     | 85                | °C                     |       |

|                                  |                                             | Industrial                                                |            | -40   | -                 | 100                    | °C    |

| V <sub>CCINT</sub>               | nternal supply voltage                      |                                                           |            | 1.140 | 1.200             | 1.260                  | V     |

| V <sub>CCO</sub> <sup>(1)</sup>  | Output driver supply voltage                |                                                           |            |       | -                 | 3.465                  | V     |

| V <sub>CCAUX</sub>               | Auxiliary supply voltage                    |                                                           |            | 2.375 | 2.500             | 2.625                  | V     |

| V <sub>IN</sub> <sup>(2,3)</sup> | Input voltage extremes to avoid             | I/O, Input-only, and                                      | IP or IO_# | -0.5  | -                 | V <sub>CCO</sub> + 0.5 | V     |

|                                  | turning on I/O protection diodes            | Dual-Purpose pins <sup>(4)</sup> IO_Lxxy_# <sup>(5)</sup> |            | -0.5  | -                 | V <sub>CCO</sub> + 0.5 | V     |

|                                  |                                             | Dedicated pins <sup>(6)</sup>                             | -0.5       | _     | $V_{CCAUX} + 0.5$ | V                      |       |

| T <sub>IN</sub>                  | Input signal transition time <sup>(7)</sup> |                                                           |            | -     | _                 | 500                    | ns    |

Notes:

- 1. This  $V_{CCO}$  range spans the lowest and highest operating voltages for all supported I/O standards. Table 80 lists the recommended  $V_{CCO}$  range specific to each of the single-ended I/O standards, and Table 82 lists that specific to the differential standards.

- Input voltages outside the recommended range require the I<sub>IK</sub> input clamp diode rating is met and no more than 100 pins exceed the range simultaneously. Refer to Table 73.

- 3. See XAPP459: Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families.

- 4. Each of the User I/O and Dual-Purpose pins is associated with one of the four banks' V<sub>CCO</sub> rails. Meeting the V<sub>IN</sub> limit ensures that the internal diode junctions that exist between these pins and their associated V<sub>CCO</sub> and GND rails do not turn on. The absolute maximum rating is provided in Table 73.

- 5. For single-ended signals that are placed on a differential-capable I/O, V<sub>IN</sub> of –0.2V to –0.5V is supported but can cause increased leakage between the two pins. See *Parasitic Leakage* in <u>UG331</u>, *Spartan-3 Generation FPGA User Guide*.

- All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> and GND rails do not turn on.

- 7. Measured between 10% and 90% V<sub>CCO</sub>. Follow Signal Integrity recommendations.

### **Quiescent Current Requirements**

#### Table 79: Quiescent Supply Current Characteristics

| Symbol              | Description                                 | Device    | Typical | Commercial<br>Maximum <sup>(1)</sup> | Industrial<br>Maximum <sup>(1)</sup> | Units |

|---------------------|---------------------------------------------|-----------|---------|--------------------------------------|--------------------------------------|-------|

| I <sub>CCINTQ</sub> | Quiescent V <sub>CCINT</sub> supply current | XC3S100E  | 8       | 27                                   | 36                                   | mA    |

|                     |                                             | XC3S250E  | 15      | 78                                   | 104                                  | mA    |

|                     |                                             | XC3S500E  | 25      | 106                                  | 145                                  | mA    |

|                     |                                             | XC3S1200E | 50      | 259                                  | 324                                  | mA    |

|                     |                                             | XC3S1600E | 65      | 366                                  | 457                                  | mA    |

| I <sub>CCOQ</sub>   | Quiescent V <sub>CCO</sub> supply current   | XC3S100E  | 0.8     | 1.0                                  | 1.5                                  | mA    |

|                     |                                             | XC3S250E  | 0.8     | 1.0                                  | 1.5                                  | mA    |

|                     |                                             | XC3S500E  | 0.8     | 1.0                                  | 1.5                                  | mA    |

|                     |                                             | XC3S1200E | 1.5     | 2.0                                  | 2.5                                  | mA    |

|                     |                                             | XC3S1600E | 1.5     | 2.0                                  | 2.5                                  | mA    |

| I <sub>CCAUXQ</sub> | Quiescent V <sub>CCAUX</sub> supply current | XC3S100E  | 8       | 12                                   | 13                                   | mA    |

|                     |                                             | XC3S250E  | 12      | 22                                   | 26                                   | mA    |

|                     |                                             | XC3S500E  | 18      | 31                                   | 34                                   | mA    |

|                     |                                             | XC3S1200E | 35      | 52                                   | 59                                   | mA    |

|                     |                                             | XC3S1600E | 45      | 76                                   | 86                                   | mA    |

#### Notes:

1. The maximum numbers in this table indicate the minimum current each power rail requires in order for the FPGA to power-on successfully.

- 2. The numbers in this table are based on the conditions set forth in Table 77.

- 3. Quiescent supply current is measured with all I/O drivers in a high-impedance state and with all pull-up/pull-down resistors at the I/O pads disabled. Typical values are characterized using typical devices at room temperature (T<sub>J</sub> of 25°C at V<sub>CCINT</sub> = 1.2 V, V<sub>CCO</sub> = 3.3V, and V<sub>CCAUX</sub> = 2.5V). The maximum limits are tested for each device at the respective maximum specified junction temperature and at maximum voltage limits with V<sub>CCINT</sub> = 1.26V, V<sub>CCO</sub> = 3.465V, and V<sub>CCAUX</sub> = 2.625V. The FPGA is programmed with a "blank" configuration data file (i.e., a design with no functional elements instantiated). For conditions other than those described above, (e.g., a design including functional elements), measured quiescent current levels may be different than the values in the table. For more accurate estimates for a specific design, use the Xilinx® XPower tools.

- 4. There are two recommended ways to estimate the total power consumption (quiescent plus dynamic) for a specific design: a) The <u>Spartan-3E XPower Estimator</u> provides quick, approximate, typical estimates, and does not require a netlist of the design. b) XPower Analyzer uses a netlist as input to provide maximum estimates as well as more accurate typical estimates.

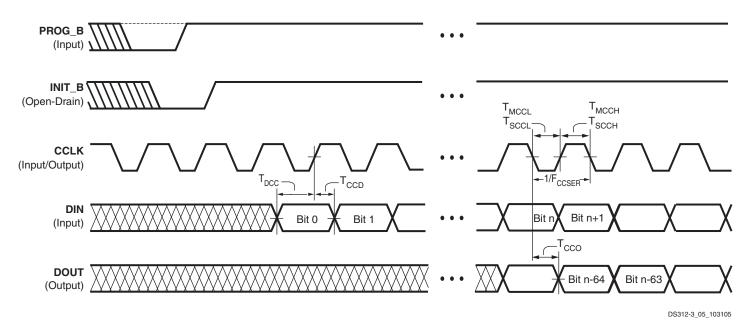

#### Master Serial and Slave Serial Mode Timing

| Figure 74: Waveforms | for Master Serial a | nd Slave Serial Configuration |

|----------------------|---------------------|-------------------------------|

|----------------------|---------------------|-------------------------------|

| Symbol             | Descri                                                                                           | Slave/                               | All Speed Grades |               | Units               |       |  |

|--------------------|--------------------------------------------------------------------------------------------------|--------------------------------------|------------------|---------------|---------------------|-------|--|

| Symbol             | Descri                                                                                           | ption                                | Master           | Min           | Max                 | Units |  |

| Clock-to-O         | utput Times                                                                                      |                                      |                  |               |                     |       |  |

| T <sub>CCO</sub>   | The time from the falling transition on the DOUT pin                                             | ne CCLK pin to data appearing at the | Both             | 1.5           | 10.0                | ns    |  |

| Setup Time         | es                                                                                               |                                      |                  |               |                     |       |  |

| T <sub>DCC</sub>   | The time from the setup of data at the DIN pin to the active edge of the CCLK pin                |                                      |                  | 11.0          | -                   | ns    |  |

| Hold Time          | S                                                                                                |                                      |                  |               |                     |       |  |

| T <sub>CCD</sub>   | The time from the active edge of the CCLK pin to the point when data is last held at the DIN pin |                                      |                  | 0             | -                   | ns    |  |

| Clock Timi         | ng                                                                                               |                                      |                  |               |                     |       |  |

| тссн               | T <sub>CCH</sub> High pulse width at the CCLK input pin                                          |                                      | Master           | See Table 114 |                     |       |  |

|                    |                                                                                                  |                                      | Slave            | See Table 115 |                     |       |  |

| T <sub>CCL</sub>   | Low pulse width at the CCLK input pin                                                            |                                      | Master           | See Table 114 |                     |       |  |

|                    |                                                                                                  |                                      | Slave            | Se            | e Table 115         |       |  |

| F <sub>CCSER</sub> | Frequency of the clock signal at the                                                             | No bitstream compression             | Slave            | 0             | 66 <mark>(2)</mark> | MHz   |  |

|                    | CCLK input pin                                                                                   | With bitstream compression           | 0                |               | 20                  | MHz   |  |

#### Table 116: Timing for the Master Serial and Slave Serial Configuration Modes

#### Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 77.

- 2. For serial configuration with a daisy-chain of multiple FPGAs, the maximum limit is 25 MHz.

## TQ144: 144-lead Thin Quad Flat Package

The XC3S100E and the XC3S250E FPGAs are available in the 144-lead thin quad flat package, TQ144. Both devices share a common footprint for this package as shown in Table 137 and Figure 82.

Table 137 lists all the package pins. They are sorted by bank number and then by pin name of the largest device. Pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier. The TQ144 package only supports 20 address output pins in the Byte-wide Peripheral Interface (BPI) configuration mode. In larger packages, there are 24 BPI address outputs.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx web site at:

http://www.xilinx.com/support/documentation/data\_sheets /s3e\_pin.zip

## **Pinout Table**

Table 137: TQ144 Package Pinout

| Bank | XC3S100E Pin Name | XC3S250E Pin Name | TQ144 Pin | Туре  |

|------|-------------------|-------------------|-----------|-------|

| 0    | IO                | 10                | P132      | I/O   |

| 0    | IO/VREF_0         | IO/VREF_0         | P124      | VREF  |

| 0    | IO_L01N_0         | IO_L01N_0         | P113      | I/O   |

| 0    | IO_L01P_0         | IO_L01P_0         | P112      | I/O   |

| 0    | IO_L02N_0         | IO_L02N_0         | P117      | I/O   |

| 0    | IO_L02P_0         | IO_L02P_0         | P116      | I/O   |

| 0    | IO_L04N_0/GCLK5   | IO_L04N_0/GCLK5   | P123      | GCLK  |

| 0    | IO_L04P_0/GCLK4   | IO_L04P_0/GCLK4   | P122      | GCLK  |

| 0    | IO_L05N_0/GCLK7   | IO_L05N_0/GCLK7   | P126      | GCLK  |

| 0    | IO_L05P_0/GCLK6   | IO_L05P_0/GCLK6   | P125      | GCLK  |

| 0    | IO_L07N_0/GCLK11  | IO_L07N_0/GCLK11  | P131      | GCLK  |

| 0    | IO_L07P_0/GCLK10  | IO_L07P_0/GCLK10  | P130      | GCLK  |

| 0    | IO_L08N_0/VREF_0  | IO_L08N_0/VREF_0  | P135      | VREF  |

| 0    | IO_L08P_0         | IO_L08P_0         | P134      | I/O   |

| 0    | IO_L09N_0         | IO_L09N_0         | P140      | I/O   |

| 0    | IO_L09P_0         | IO_L09P_0         | P139      | I/O   |

| 0    | IO_L10N_0/HSWAP   | IO_L10N_0/HSWAP   | P143      | DUAL  |

| 0    | IO_L10P_0         | IO_L10P_0         | P142      | I/O   |

| 0    | IP                | IP                | P111      | INPUT |

| 0    | IP                | IP                | P114      | INPUT |

| 0    | IP                | IP                | P136      | INPUT |

| 0    | IP                | IP                | P141      | INPUT |

| 0    | IP_L03N_0         | IP_L03N_0         | P120      | INPUT |

| 0    | IP_L03P_0         | IP_L03P_0         | P119      | INPUT |

| 0    | IP_L06N_0/GCLK9   | IP_L06N_0/GCLK9   | P129      | GCLK  |

| 0    | IP_L06P_0/GCLK8   | IP_L06P_0/GCLK8   | P128      | GCLK  |

| 0    | VCCO_0            | VCCO_0            | P121      | VCCO  |

| 0    | VCCO_0            | VCCO_0            | P138      | VCCO  |

| 1    | IO/A0             | IO/A0             | P98       | DUAL  |

| 1    | IO/VREF_1         | IO/VREF_1         | P83       | VREF  |

| 1    | IO_L01N_1/A15     | IO_L01N_1/A15     | P75       | DUAL  |

| 1    | IO_L01P_1/A16     | IO_L01P_1/A16     | P74       | DUAL  |

| 1    | IO_L02N_1/A13     | IO_L02N_1/A13     | P77       | DUAL  |

## User I/Os by Bank

Table 138 and Table 139 indicate how the 108 available

user-I/O pins are distributed between the four I/O banks on

the TQ144 package.

#### Table 138: User I/Os Per Bank for the XC3S100E in the TQ144 Package

| Package | I/O Bonk      | Maximum I/O | All Possible I/O Pins by Type |       |      |                     |                    |  |

|---------|---------------|-------------|-------------------------------|-------|------|---------------------|--------------------|--|

| Edge    | Edge I/O Bank |             | I/O                           | INPUT | DUAL | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> |  |

| Тор     | 0             | 26          | 9                             | 6     | 1    | 2                   | 8                  |  |

| Right   | 1             | 28          | 0                             | 5     | 21   | 2                   | 0 <sup>(2)</sup>   |  |

| Bottom  | 2             | 26          | 0                             | 4     | 20   | 2                   | 0 <sup>(2)</sup>   |  |

| Left    | 3             | 28          | 13                            | 4     | 0    | 3                   | 8                  |  |

| TOTAL   |               | 108         | 22                            | 19    | 42   | 9                   | 16                 |  |

#### Notes:

1. Some VREF and CLK pins are on INPUT pins.

2. The eight global clock pins in this bank have optional functionality during configuration and are counted in the DUAL column.

#### Table 139: User I/Os Per Bank for the XC3S250E in TQ144 Package

| Package | 1/O Demle | Maximum I/O | All Possible I/O Pins by Type |       |      |                     |                    |  |

|---------|-----------|-------------|-------------------------------|-------|------|---------------------|--------------------|--|

| Edge    | I/O Bank  | Maximum I/O | I/O                           | INPUT | DUAL | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> |  |

| Тор     | 0         | 26          | 9                             | 6     | 1    | 2                   | 8                  |  |

| Right   | 1         | 28          | 0                             | 5     | 21   | 2                   | 0(2)               |  |

| Bottom  | 2         | 26          | 0                             | 4     | 20   | 2                   | 0 <sup>(2)</sup>   |  |

| Left    | 3         | 28          | 11                            | 6     | 0    | 3                   | 8                  |  |

| TOTAL   |           | 108         | 20                            | 21    | 42   | 9                   | 16                 |  |

#### Notes:

1. Some VREF and CLK pins are on INPUT pins.

2. The eight global clock pins in this bank have optional functionality during configuration and are counted in the DUAL column.

### **Footprint Migration Differences**

Table 140 summarizes any footprint and functionality differences between the XC3S100E and the XC3S250E FPGAs that may affect easy migration between devices. There are four such pins. All other pins not listed in Table 140 unconditionally migrate between Spartan-3E devices available in the TQ144 package.