Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 2168                                                          |

| Number of Logic Elements/Cells | 19512                                                         |

| Total RAM Bits                 | 516096                                                        |

| Number of I/O                  | 304                                                           |

| Number of Gates                | 1200000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 400-BGA                                                       |

| Supplier Device Package        | 400-FBGA (21x21)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1200e-4fg400i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

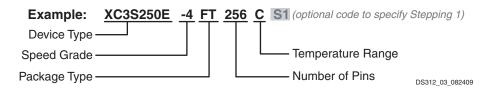

# **Ordering Information**

Spartan-3E FPGAs are available in both standard and Pb-free packaging options for all device/package combinations. All devices are available in Pb-free packages, which adds a 'G' character to the ordering code. All devices are available in either Commercial (C) or Industrial (I) temperature ranges. Both the standard –4 and faster –5 speed grades are available for the Commercial temperature range. However, only the –4 speed grade is available for the Industrial temperature range. See Table 2 for valid device/package combinations.

| Device                  |    | Speed Grade                     |                 | Package Type / Number of Pins                    |   | Temperature Range (T <sub>J</sub> ) |

|-------------------------|----|---------------------------------|-----------------|--------------------------------------------------|---|-------------------------------------|

| XC3S100E                | -4 | Standard Performance            | VQ100<br>VQG100 | 100-pin Very Thin Quad Flat Pack (VQFP)          | С | Commercial (0°C to 85°C)            |

| XC3S250E                | -5 | High Performance <sup>(1)</sup> | CP132<br>CPG132 | 132-ball Chip-Scale Package (CSP)                | I | Industrial (-40°C to 100°C)         |

| XC3S500E <sup>(2)</sup> |    |                                 | TQ144<br>TQG144 | 144-pin Thin Quad Flat Pack (TQFP)               |   |                                     |

| XC3S1200E               |    |                                 | PQ208<br>PQG208 | 208-pin Plastic Quad Flat Pack (PQFP)            |   |                                     |

| XC3S1600E               |    |                                 | FT256<br>FTG256 | 256-ball Fine-Pitch Thin Ball Grid Array (FTBGA) |   |                                     |

|                         |    |                                 | FG320<br>FGG320 | 320-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                     |

|                         |    |                                 | FG400<br>FGG400 | 400-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                     |

|                         |    |                                 | FG484<br>FGG484 | 484-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                     |

#### Notes:

1. The -5 speed grade is exclusively available in the Commercial temperature range.

- 2. The XC3S500E VQG100 is available only in the -4 Speed Grade.

- 3. See <u>DS635</u> for the XA Automotive Spartan-3E FPGAs.

## **Production Stepping**

The Spartan-3E FPGA family uses production stepping to indicate improved capabilities or enhanced features.

Stepping 1 is, by definition, a functional superset of Stepping 0. Furthermore, configuration bitstreams generated for any stepping are forward compatible. See Table 72 for additional details.

Xilinx has shipped both Stepping 0 and Stepping 1. Designs operating on the Stepping 0 devices perform similarly on a Stepping 1 device. Stepping 1 devices have been shipping since 2006. The faster speed grade (-5), Industrial (I grade), Automotive devices, and -4C devices with date codes 0901 (2009) and later, are always Stepping 1 devices. Only -4C devices have shipped as Stepping 0 devices.

To specify only the later stepping for the -4C, append an S# suffix to the standard ordering code, where # is the stepping number, as indicated in Table 3.

## Table 3: Spartan-3E Optional Stepping Level Ordering

| Stepping<br>Number | Suffix Code | Status     |

|--------------------|-------------|------------|

| 0                  | None or S0  | Production |

| 1                  | S1          | Production |

The stepping level is optionally marked on the device using a single number character, as shown in Figure 2, Figure 3, and Figure 4.

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/01/05 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                |

| 03/21/05 | 1.1     | Added XC3S250E in CP132 package to Table 2. Corrected number of differential I/O pairs for CP132 package. Added package markings for QFP packages (Figure 2) and CP132/CPG132 packages (Figure 4).                                                                                                                                                                                                     |

| 11/23/05 | 2.0     | Added differential HSTL and SSTL I/O standards. Updated Table 2 to indicate number of input-only pins. Added Production Stepping information, including example top marking diagrams.                                                                                                                                                                                                                  |

| 03/22/06 | 3.0     | Upgraded data sheet status to Preliminary. Added XC3S100E in CP132 package and updated I/O counts for the XC3S1600E in FG320 package (Table 2). Added information about dual markings for –5C and –4I product combinations to Package Marking.                                                                                                                                                         |

| 11/09/06 | 3.4     | Added 66 MHz PCI support and links to the Xilinx PCI LogiCORE data sheet. Indicated that Stepping 1 parts are Production status. Promoted Module 1 to Production status. Synchronized all modules to v3.4.                                                                                                                                                                                             |

| 04/18/08 | 3.7     | Added XC3S500E VQG100 package. Added reference to XA Automotive version. Updated links.                                                                                                                                                                                                                                                                                                                |

| 08/26/09 | 3.8     | Added paragraph to Configuration indicating the device supports MultiBoot configuration. Added package sizes to Table 2. Described the speed grade and temperature range guarantee for devices having a single mark in paragraph 3 under Package Marking. Deleted Pb-Free Packaging example under Ordering Information. Revised information under Production Stepping. Revised description of Table 3. |

| 10/29/12 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs.<br>Updated Table 2 footprint size of PQ208.                                                                                                                                                                                                                                                                               |

# **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

www.xilinx.com

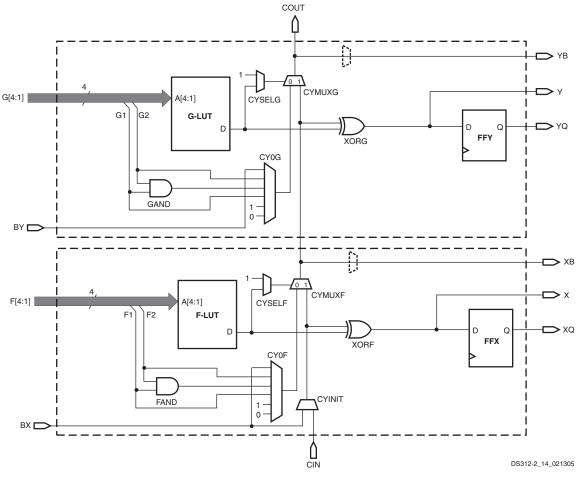

# **Carry and Arithmetic Logic**

For additional information, refer to the "Using Carry and Arithmetic Logic" chapter in UG331.

The carry chain, together with various dedicated arithmetic logic gates, support fast and efficient implementations of math operations. The carry logic is automatically used for most arithmetic functions in a design. The gates and multiplexers of the carry and arithmetic logic can also be used for general-purpose logic, including simple wide Boolean functions.

The carry chain enters the slice as CIN and exits as COUT, controlled by several multiplexers. The carry chain connects directly from one CLB to the CLB above. The carry chain can be initialized at any point from the BX (or BY) inputs.

The dedicated arithmetic logic includes the exclusive-OR gates XORF and XORG (upper and lower portions of the slice, respectively) as well as the AND gates GAND and FAND (upper and lower portions, respectively). These gates work in conjunction with the LUTs to implement efficient arithmetic functions, including counters and multipliers, typically at two bits per slice. See Figure 22 and Table 14.

### Table 14: Carry Logic Functions

| Function | Description                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CYINIT   | <ul> <li>Initializes carry chain for a slice. Fixed selection of:</li> <li>CIN carry input from the slice below</li> <li>BX input</li> </ul>                                                                                                                                                                            |  |  |  |  |

| CY0F     | <ul> <li>Carry generation for bottom half of slice. Fixed selection of:</li> <li>F1 or F2 inputs to the LUT (both equal 1 when a carry is to be generated)</li> <li>FAND gate for multiplication</li> <li>BX input for carry initialization</li> <li>Fixed 1 or 0 input for use as a simple Boolean function</li> </ul> |  |  |  |  |

www.xilinx.com

# **EXILINX**.

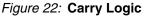

# **Block RAM**

For additional information, refer to the "Using Block RAM" chapter in UG331.

Spartan-3E devices incorporate 4 to 36 dedicated block RAMs, which are organized as dual-port configurable 18 Kbit blocks. Functionally, the block RAM is identical to the Spartan-3 architecture block RAM. Block RAM synchronously stores large amounts of data while distributed RAM, previously described, is better suited for buffering small amounts of data anywhere along signal paths. This section describes basic block RAM functions.

Each block RAM is configurable by setting the content's initial values, default signal value of the output registers, port aspect ratios, and write modes. Block RAM can be used in single-port or dual-port modes.

## Arrangement of RAM Blocks on Die

The block RAMs are located together with the multipliers on the die in one or two columns depending on the size of the device. The XC3S100E has one column of block RAM. The Spartan-3E devices ranging from the XC3S250E to XC3S1600E have two columns of block RAM. Table 21 shows the number of RAM blocks, the data storage capacity, and the number of columns for each device. Row(s) of CLBs are located above and below each block RAM column.

|           |                                  | -                                           |                      |

|-----------|----------------------------------|---------------------------------------------|----------------------|

| Device    | Total<br>Number of<br>RAM Blocks | Total<br>Addressable<br>Locations<br>(bits) | Number of<br>Columns |

| XC3S100E  | 4                                | 73,728                                      | 1                    |

| XC3S250E  | 12                               | 221,184                                     | 2                    |

| XC3S500E  | 20                               | 368,640                                     | 2                    |

| XC3S1200E | 28                               | 516,096                                     | 2                    |

| XC3S1600E | 36                               | 663,552                                     | 2                    |

### Table 21: Number of RAM Blocks by Device

Immediately adjacent to each block RAM is an embedded 18x18 hardware multiplier. The upper 16 bits of the block RAM's Port A Data input bus are shared with the upper 16 bits of the A multiplicand input bus of the multiplier. Similarly, the upper 16 bits of Port B's data input bus are shared with the B multiplicand input bus of the multiplier.

## The Internal Structure of the Block RAM

The block RAM has a dual port structure. The two identical data ports called A and B permit independent access to the common block RAM, which has a maximum capacity of 18,432 bits, or 16,384 bits with no parity bits (see parity bits description in Table 22). Each port has its own dedicated set of data, control, and clock lines for synchronous read

and write operations. There are four basic data paths, as shown in Figure 30:

- 1. Write to and read from Port A

- 2. Write to and read from Port B

- 3. Data transfer from Port A to Port B

- 4. Data transfer from Port B to Port A

Figure 30: Block RAM Data Paths

## **Number of Ports**

A choice among primitives determines whether the block RAM functions as dual- or single-port memory. A name of the form RAMB16\_S[w<sub>A</sub>]\_S[w<sub>B</sub>] calls out the dual-port primitive, where the integers  $w_A$  and  $w_B$  specify the total data path width at ports A and B, respectively. Thus, a RAMB16\_S9\_S18 is a dual-port RAM with a 9-bit Port A and an 18-bit Port B. A name of the form RAMB16\_S[w] identifies the single-port primitive, where the integer w specifies the total data path width of the lone port A. A RAMB16\_S18 is a single-port RAM with an 18-bit port.

## **Port Aspect Ratios**

Each port of the block RAM can be configured independently to select a number of different possible widths for the data input (DI) and data output (DO) signals as shown in Table 22.

# **Clocking Infrastructure**

For additional information, refer to the "Using Global Clock Resources" chapter in <u>UG331</u>.

The Spartan-3E clocking infrastructure, shown in Figure 45, provides a series of low-capacitance, low-skew interconnect lines well-suited to carrying high-frequency signals throughout the FPGA. The infrastructure also includes the clock inputs and BUFGMUX clock buffers/multiplexers. The Xilinx Place-and-Route (PAR) software automatically routes high-fanout clock signals using these resources.

## **Clock Inputs**

Clock pins accept external clock signals and connect directly to DCMs and BUFGMUX elements. Each Spartan-3E FPGA has:

- 16 Global Clock inputs (GCLK0 through GCLK15) located along the top and bottom edges of the FPGA

- 8 Right-Half Clock inputs (RHCLK0 through RHCLK7) located along the right edge

- 8 Left-Half Clock inputs (LHCLK0 through LHCLK7) located along the left edge

Clock inputs optionally connect directly to DCMs using dedicated connections. Table 30, Table 31, and Table 32 show the clock inputs that best feed a specific DCM within a given Spartan-3E part number. Different Spartan-3E FPGA densities have different numbers of DCMs. The XC3S1200E and XC3S1600E are the only two densities with the left- and right-edge DCMs.

Each clock input is also optionally a user-I/O pin and connects to internal interconnect. Some clock pad pins are input-only pins as indicated in Module 4, Pinout Descriptions.

## Design Note

Avoid using global clock input GCLK1 as it is always shared with the M2 mode select pin. Global clock inputs GCLK0, GCLK2, GCLK3, GCLK12, GCLK13, GCLK14, and GCLK15 have shared functionality in some configuration modes.

## **Clock Buffers/Multiplexers**

Clock Buffers/Multiplexers either drive clock input signals directly onto a clock line (BUFG) or optionally provide a multiplexer to switch between two unrelated, possibly asynchronous clock signals (BUFGMUX).

Each BUFGMUX element, shown in Figure 46, is a 2-to-1 multiplexer. The select line, S, chooses which of the two inputs, I0 or I1, drives the BUFGMUX's output signal, O, as described in Table 40. The switching from one clock to the other is glitch-less, and done in such a way that the output High and Low times are never shorter than the shortest

High or Low time of either input clock. The two clock inputs can be asynchronous with regard to each other, and the S input can change at any time, except for a short setup time prior to the rising edge of the presently selected clock (I0 or I1). This setup time is specified as TGSI in Table 101, page 136. Violating this setup time requirement possibly results in an undefined runt pulse output.

#### Table 40: BUFGMUX Select Mechanism

| S Input | O Output |

|---------|----------|

| 0       | I0 Input |

| 1       | I1 Input |

The BUFG clock buffer primitive drives a single clock signal onto the clock network and is essentially the same element as a BUFGMUX, just without the clock select mechanism. Similarly, the BUFGCE primitive creates an enabled clock buffer using the BUFGMUX select mechanism.

The I0 and I1 inputs to an BUFGMUX element originate from clock input pins, DCMs, or Double-Line interconnect, as shown in Figure 46. As shown in Figure 45, there are 24 BUFGMUX elements distributed around the four edges of the device. Clock signals from the four BUFGMUX elements at the top edge and the four at the bottom edge are truly global and connect to all clocking quadrants. The eight left-edge BUFGMUX elements only connect to the two clock quadrants in the left half of the device. Similarly, the eight right-edge BUFGMUX elements only connect to the right half of the device.

BUFGMUX elements are organized in pairs and share I0 and I1 connections with adjacent BUFGMUX elements from a common clock switch matrix as shown in Figure 46. For example, the input on I0 of one BUFGMUX is also a shared input to I1 of the adjacent BUFGMUX.

The clock switch matrix for the left- and right-edge BUFGMUX elements receive signals from any of the three following sources: an LHCLK or RHCLK pin as appropriate, a Double-Line interconnect, or a DCM in the XC3S1200E and XC3S1600E devices.

# Interconnect

For additional information, refer to the "Using Interconnect" chapter in <u>UG331</u>.

Interconnect is the programmable network of signal pathways between the inputs and outputs of functional elements within the FPGA, such as IOBs, CLBs, DCMs, and block RAM.

## Overview

Interconnect, also called routing, is segmented for optimal connectivity. Functionally, interconnect resources are identical to that of the Spartan-3 architecture. There are four kinds of interconnects: long lines, hex lines, double lines, and direct lines. The Xilinx Place and Route (PAR) software exploits the rich interconnect array to deliver optimal system performance and the fastest compile times.

## **Switch Matrix**

The switch matrix connects to the different kinds of interconnects across the device. An interconnect tile, shown in Figure 48, is defined as a single switch matrix connected to a functional element, such as a CLB, IOB, or DCM. If a functional element spans across multiple switch matrices such as the block RAM or multipliers, then an interconnect tile is defined by the number of switch matrices connected to that functional element. A Spartan-3E device can be represented as an array of interconnect tiles where interconnect resources are for the channel between any two adjacent interconnect tile rows or columns as shown in Figure 49.

Figure 48: Four Types of Interconnect Tiles (CLBs, IOBs, DCMs, and Block RAM/Multiplier)

| Switch     | Switch                      | Switch                    | Switch              | Switch          |

|------------|-----------------------------|---------------------------|---------------------|-----------------|

| Matrix     | Matrix                      | Matrix                    | Matrix              | Matrix          |

| Switch     | Switch                      | Switch                    | Switch              | Switch          |

| Matrix IOB | Matrix CLB                  | Matrix CLB                | Matrix CLB          | Matrix          |

| Switch     | Switch                      | Switch                    | Switch              | Switch          |

| Matrix IOB | Matrix CLB                  | Matrix CLB                | Matrix CLB          | Matrix          |

| Switch     | Switch                      | Switch                    | Switch              | Switch          |

| Matrix IOB | Matrix CLB                  | Matrix CLB                | Matrix CLB          | Matrix          |

| Switch     | Switch                      | Switch                    | Switch              | Switch          |

| Matrix IOB | Matrix CLB                  | Matrix CLB                | Matrix CLB          | Matrix          |

| Fig        | :<br>gure 49: Array of Inte | :<br>erconnect Tiles in S | :<br>partan-3E FPGA | DS312_09_100110 |

support byte-wide data. However, after configuration, the FPGA supports either x8 or x16 modes. In x16 mode, up to eight additional user I/O pins are required for the upper data bits, D[15:8].

Connecting a Spartan-3E FPGA to a x8/x16 Flash PROM is simple, but does require a precaution. Various Flash PROM vendors use slightly different interfaces to support both x8 and x16 modes. Some vendors (Intel, Micron, some STMicroelectronics devices) use a straightforward interface with pin naming that matches the FPGA connections. However, the PROM's A0 pin is wasted in x16 applications and a separate FPGA user-I/O pin is required for the D15 data line. Fortunately, the FPGA A0 pin is still available as a user I/O after configuration, even though it connects to the Flash PROM. Other vendors (AMD, Atmel, Silicon Storage Technology, some STMicroelectronics devices) use a pin-efficient interface but change the function of one pin, called IO15/A-1, depending if the PROM is in x8 or x16 mode. In x8 mode, BYTE# = 0, this pin is the least-significant address line. The A0 address line selects the halfword location. The A-1 address line selects the byte location. When in x16 mode, BYTE# = 1, the IO15/A-1 pin becomes the most-significant data bit, D15 because byte addressing is not required in this mode. Check to see if the Flash PROM has a pin named "IO15/A-1" or "DQ15/A-1". If so, be careful to connect x8/x16 Flash PROMs correctly, as shown in Table 63. Also, remember that the D[14:8] data connections require FPGA user I/O pins but that the D15 data is already connected for the FPGA's A0 pin.

| FPGA Pin | Connection to Flash PROM with<br>IO15/A-1 Pin                                                       | x8 Flash PROM Interface After<br>FPGA Configuration                       | x16 Flash PROM Interface After<br>FPGA Configuration |

|----------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|

| LDC2     | BYTE#                                                                                               | Drive LDC2 Low or leave<br>unconnected and tie PROM BYTE#<br>input to GND | Drive LCD2 High                                      |

| LDC1     | OE#                                                                                                 | Active-Low Flash PROM<br>output-enable control                            | Active-Low Flash PROM<br>output-enable control       |

| LDC0     | CS#                                                                                                 | Active-Low Flash PROM chip-select control                                 | Active-Low Flash PROM chip-select<br>control         |

| HDC      | WE#                                                                                                 | Flash PROM write-enable control                                           | Flash PROM write-enable control                      |

| A[23:1]  | A[n:0]                                                                                              | A[n:0]                                                                    | A[n:0]                                               |

| A0       | IO15/A-1                                                                                            | IO15/A-1 is the least-significant address input                           | IO15/A-1 is the most-significant data line, IO15     |

| D[7:0]   | IO[7:0]                                                                                             | IO[7:0]                                                                   | IO[7:0]                                              |

| User I/O | Upper data lines IO[14:8] not required<br>unless used as x16 Flash interface after<br>configuration | Upper data lines IO[14:8] not required                                    | IO[14:8]                                             |

Table 63: FPGA Connections to Flash PROM with IO15/A-1 Pin

Some x8/x16 Flash PROMs have a long setup time requirement on the BYTE# signal. For the FPGA to configure correctly, the PROM must be in x8 mode with BYTE# = 0 at power-on or when the FPGA's PROG\_B pin is pulsed Low. If required, extend the BYTE# setup time for a 3.3V PROM using an external 680  $\Omega$  pull-down resistor on the FPGA's LDC2 pin or by delaying assertion of the CSI\_B select input to the FPGA.

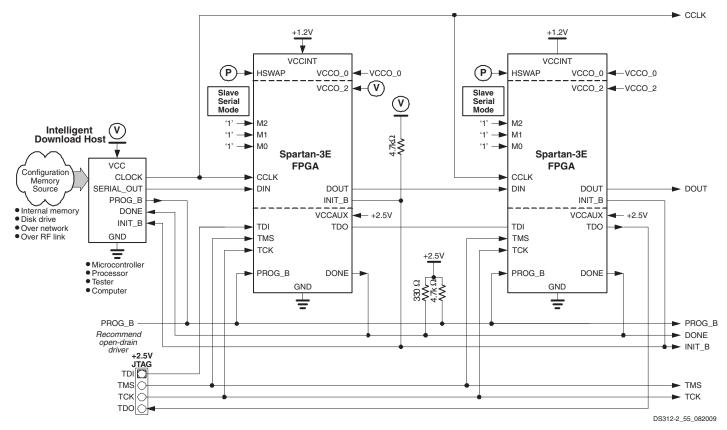

## **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain, as shown in Figure 59. Use BPI mode (M[2:0] = <0:1:0> or <0:1:1>) for the FPGA connected to the parallel NOR Flash PROM and Slave Parallel mode (M[2:0] = <1:1:0>) for all downstream FPGAs in the daisy-chain. If there are more than two FPGAs in the chain, then last FPGA in the chain can be from any Xilinx FPGA family. However, all intermediate FPGAs located in the

chain between the first and last FPGAs must from either the Spartan-3E or Virtex®-5 FPGA families.

After the master FPGA—the FPGA on the left in the diagram—finishes loading its configuration data from the parallel Flash PROM, the master device continues generating addresses to the Flash PROM and asserts its CSO\_B output Low, enabling the next FPGA in the daisy-chain. The next FPGA then receives parallel configuration data from the Flash PROM. The master FPGA's CCLK output synchronizes data capture.

If HSWAP = 1, an external  $4.7k\Omega$  pull-up resistor must be added on the CSO\_B pin. If HSWAP = 0, no external pull-up is necessary.

## Design Note

BPI mode daisy chain software support is available starting in ISE 8.2i.

http://www.xilinx.com/support/answers/23061.htm

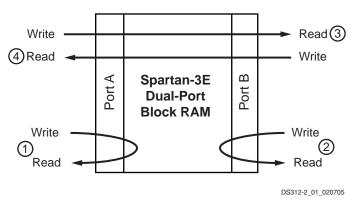

After the FPGA configures itself using BPI mode from one end of the parallel Flash PROM, then the FPGA can trigger a MultiBoot event and reconfigure itself from the opposite end of the parallel Flash PROM. MultiBoot is only available when using BPI mode and only for applications with a single Spartan-3E FPGA.

By default, MultiBoot mode is disabled. To trigger a MultiBoot event, assert a Low pulse lasting at least 300 ns on the MultiBoot Trigger (MBT) input to the STARTUP\_SPARTAN3E library primitive. When the MBT signal returns High after the 300 ns or longer pulse, the FPGA automatically reconfigures from the opposite end of the parallel Flash memory. Figure 60 shows an example usage. At power up, the FPGA loads itself from the attached parallel Flash PROM. In this example, the M0 mode pin is Low so the FPGA starts at address 0 and increments through the Flash PROM memory locations. After the FPGA completes configuration, the application initially loaded into the FPGA performs a board-level or system test using FPGA logic. If the test is successful, the FPGA then triggers a MultiBoot event, causing the FPGA to reconfigure from the opposite end of the Flash PROM memory. This second configuration contains the FPGA application for normal operation.

Similarly, the general FPGA application could trigger another MultiBoot event at any time to reload the diagnostics design, and so on.

DS312-2\_51\_103105

## Figure 60: Use MultiBoot to Load Alternate Configuration Images

In another potential application, the initial design loaded into the FPGA image contains a "golden" or "fail-safe" configuration image, which then communicates with the outside world and checks for a newer image. If there is a new configuration revision and the new image verifies as good, the "golden" configuration triggers a MultiBoot event to load the new image.

When a MultiBoot event is triggered, the FPGA then again drives its configuration pins as described in Table 59. However, the FPGA does not assert the PROG\_B pin. The system design must ensure that no other device drives on these same pins during the reconfiguration process. The FPGA's DONE, LDC[2:0], or HDC pins can temporarily disable any conflicting drivers during reconfiguration.

Asserting the PROG\_B pin Low overrides the MultiBoot feature and forces the FPGA to reconfigure starting from the end of memory defined by the mode pins, shown in Table 58.

Figure 64: Daisy-Chaining using Slave Serial Mode

## **JTAG Mode**

For additional information, refer to the "JTAG Configuration Mode and Boundary-Scan" chapter in UG332.

The Spartan-3E FPGA has a dedicated four-wire IEEE 1149.1/1532 JTAG port that is always available any time the FPGA is powered and regardless of the mode pin settings. However, when the FPGA mode pins are set for JTAG mode (M[2:0] = <1:0:1>), the FPGA waits to be configured via the JTAG port after a power-on event or when PROG\_B is asserted. Selecting the JTAG mode simply disables the other configuration modes. No other pins are required as part of the configuration interface.

Figure 65 illustrates a JTAG-only configuration interface. The JTAG interface is easily cascaded to any number of FPGAs by connecting the TDO output of one device to the TDI input of the next device in the chain. The TDO output of the last device in the chain loops back to the port connector.

### Design Note

If using software versions prior to ISE 9.1.01i, avoid configuring the FPGA using JTAG if...

- the mode pins are set for a Master mode

- the attached Master mode PROM contains a valid FPGA configuration bitstream.

The FPGA bitstream may be corrupted and the DONE pin may go High. The following Answer Record contains additional information.

http://www.xilinx.com/support/answers/22255.htm

## **EXILINX**.

## **General Recommended Operating Conditions**

#### Table 77: General Recommended Operating Conditions

| Symbol                           | De                                          | Description                   |                          |       | Nominal           | Max                    | Units |

|----------------------------------|---------------------------------------------|-------------------------------|--------------------------|-------|-------------------|------------------------|-------|

| ТJ                               | Junction temperature                        | Commercial                    | 0                        | -     | 85                | °C                     |       |

|                                  |                                             | Industrial                    |                          | -40   | -                 | 100                    | °C    |

| V <sub>CCINT</sub>               | Internal supply voltage                     |                               |                          | 1.140 | 1.200             | 1.260                  | V     |

| V <sub>CCO</sub> <sup>(1)</sup>  | Output driver supply voltage                |                               |                          | 1.100 | -                 | 3.465                  | V     |

| V <sub>CCAUX</sub>               | Auxiliary supply voltage                    |                               |                          | 2.375 | 2.500             | 2.625                  | V     |

| V <sub>IN</sub> <sup>(2,3)</sup> | Input voltage extremes to avoid             | I/O, Input-only, and          | IP or IO_#               | -0.5  | -                 | V <sub>CCO</sub> + 0.5 | V     |

|                                  | turning on I/O protection diodes            | Dual-Purpose pins (4)         | IO_Lxxy_# <sup>(5)</sup> | -0.5  | -                 | V <sub>CCO</sub> + 0.5 | V     |

|                                  |                                             | Dedicated pins <sup>(6)</sup> | -0.5                     | _     | $V_{CCAUX} + 0.5$ | V                      |       |

| T <sub>IN</sub>                  | Input signal transition time <sup>(7)</sup> |                               |                          | -     | _                 | 500                    | ns    |

Notes:

- 1. This  $V_{CCO}$  range spans the lowest and highest operating voltages for all supported I/O standards. Table 80 lists the recommended  $V_{CCO}$  range specific to each of the single-ended I/O standards, and Table 82 lists that specific to the differential standards.

- Input voltages outside the recommended range require the I<sub>IK</sub> input clamp diode rating is met and no more than 100 pins exceed the range simultaneously. Refer to Table 73.

- 3. See XAPP459: Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families.

- 4. Each of the User I/O and Dual-Purpose pins is associated with one of the four banks' V<sub>CCO</sub> rails. Meeting the V<sub>IN</sub> limit ensures that the internal diode junctions that exist between these pins and their associated V<sub>CCO</sub> and GND rails do not turn on. The absolute maximum rating is provided in Table 73.

- 5. For single-ended signals that are placed on a differential-capable I/O, V<sub>IN</sub> of –0.2V to –0.5V is supported but can cause increased leakage between the two pins. See *Parasitic Leakage* in <u>UG331</u>, *Spartan-3 Generation FPGA User Guide*.

- All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> and GND rails do not turn on.

- 7. Measured between 10% and 90% V<sub>CCO</sub>. Follow Signal Integrity recommendations.

### Table 92: Timing for the IOB Output Path

|                     | Description                                                                                                                               | Conditions                                                         |        | Speed Grade |      |       |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------|-------------|------|-------|

| Symbol              |                                                                                                                                           |                                                                    | Device | -5          | -4   | Units |

|                     |                                                                                                                                           |                                                                    |        | Min         | Min  |       |

| Clock-to-Outpu      | t Times                                                                                                                                   | 1                                                                  | 1      |             |      |       |

| T <sub>IOCKP</sub>  | When reading from the Output Flip-Flop (OFF), the time from the active transition at the OCLK input to data appearing at the Output pin   | LVCMOS25 <sup>(2)</sup> ,<br>12 mA output drive,<br>Fast slew rate | All    | 2.18        | 2.50 | ns    |

| Propagation Ti      | mes                                                                                                                                       | .1                                                                 | 3      |             |      |       |

| T <sub>IOOP</sub>   | The time it takes for data to travel from the IOB's O input to the Output pin                                                             | 12 mA output drive,                                                |        | 2.24        | 2.58 | ns    |

| T <sub>IOOLP</sub>  | The time it takes for data to travel from the O input through the OFF latch to the Output pin                                             | Fast slew rate                                                     |        | 2.32        | 2.67 | ns    |

| Set/Reset Time      | S                                                                                                                                         |                                                                    |        |             |      |       |

| T <sub>IOSRP</sub>  | Time from asserting the OFF's SR input to setting/resetting data at the Output pin                                                        | LVCMOS25 <sup>(2)</sup> ,<br>12 mA output drive,                   | All    | 3.27        | 3.76 | ns    |

| T <sub>IOGSRQ</sub> | Time from asserting the Global Set Reset (GSR)<br>input on the STARTUP_SPARTAN3E primitive to<br>setting/resetting data at the Output pin | Fast slew rate                                                     |        | 8.40        | 9.65 | ns    |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77 and Table 80.

2. This time requires adjustment whenever a signal standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. When this is true, *add* the appropriate Output adjustment from Table 94.

3. For minimum delays use the values reported by the Timing Analyzer.

### Table 94: Output Timing Adjustments for IOB

| LVCMOS25 w    | Convert Output Time from<br>LVCMOS25 with 12mA Drive and<br>Fast Slew Rate to the Following |       |       | Add the<br>Adjustment<br>Below |    |  |

|---------------|---------------------------------------------------------------------------------------------|-------|-------|--------------------------------|----|--|

| Signal Standa |                                                                                             |       | Speed | Grade                          | -  |  |

|               |                                                                                             | -5    | -4    |                                |    |  |

| Single-Ended  | Standards                                                                                   | 5     |       | r                              | 1  |  |

| LVTTL         | Slow                                                                                        | 2 mA  | 5.20  | 5.41                           | ns |  |

|               |                                                                                             | 4 mA  | 2.32  | 2.41                           | ns |  |

|               |                                                                                             | 6 mA  | 1.83  | 1.90                           | ns |  |

|               |                                                                                             | 8 mA  | 0.64  | 0.67                           | ns |  |

|               |                                                                                             | 12 mA | 0.68  | 0.70                           | ns |  |

|               |                                                                                             | 16 mA | 0.41  | 0.43                           | ns |  |

|               | Fast                                                                                        | 2 mA  | 4.80  | 5.00                           | ns |  |

|               |                                                                                             | 4 mA  | 1.88  | 1.96                           | ns |  |

|               |                                                                                             | 6 mA  | 1.39  | 1.45                           | ns |  |

|               |                                                                                             | 8 mA  | 0.32  | 0.34                           | ns |  |

|               |                                                                                             | 12 mA | 0.28  | 0.30                           | ns |  |

|               |                                                                                             | 16 mA | 0.28  | 0.30                           | ns |  |

| LVCMOS33      | Slow                                                                                        | 2 mA  | 5.08  | 5.29                           | ns |  |

|               |                                                                                             | 4 mA  | 1.82  | 1.89                           | ns |  |

|               |                                                                                             | 6 mA  | 1.00  | 1.04                           | ns |  |

|               |                                                                                             | 8 mA  | 0.66  | 0.69                           | ns |  |

|               |                                                                                             | 12 mA | 0.40  | 0.42                           | ns |  |

|               |                                                                                             | 16 mA | 0.41  | 0.43                           | ns |  |

|               | Fast                                                                                        | 2 mA  | 4.68  | 4.87                           | ns |  |

|               |                                                                                             | 4 mA  | 1.46  | 1.52                           | ns |  |

|               |                                                                                             | 6 mA  | 0.38  | 0.39                           | ns |  |

|               |                                                                                             | 8 mA  | 0.33  | 0.34                           | ns |  |

|               |                                                                                             | 12 mA | 0.28  | 0.30                           | ns |  |

|               |                                                                                             | 16 mA | 0.28  | 0.30                           | ns |  |

| LVCMOS25      | Slow                                                                                        | 2 mA  | 4.04  | 4.21                           | ns |  |

|               |                                                                                             | 4 mA  | 2.17  | 2.26                           | ns |  |

|               |                                                                                             | 6 mA  | 1.46  | 1.52                           | ns |  |

|               |                                                                                             | 8 mA  | 1.04  | 1.08                           | ns |  |

|               |                                                                                             | 12 mA | 0.65  | 0.68                           | ns |  |

|               | Fast                                                                                        | 2 mA  | 3.53  | 3.67                           | ns |  |

|               |                                                                                             | 4 mA  | 1.65  | 1.72                           | ns |  |

|               |                                                                                             | 6 mA  | 0.44  | 0.46                           | ns |  |

|               |                                                                                             | 8 mA  | 0.20  | 0.21                           | ns |  |

|               |                                                                                             | 12 mA | 0     | 0                              | ns |  |

### Table 94: Output Timing Adjustments for IOB (Cont'd)

| Convert Output Time from<br>LVCMOS25 with 12mA Drive and<br>Fast Slew Rate to the Following |           |        | Adjus<br>Bel | the<br>tment<br>ow<br>Grade | Units |  |

|---------------------------------------------------------------------------------------------|-----------|--------|--------------|-----------------------------|-------|--|

| Signal Standa                                                                               | rd (IOSTA | NDARD) | -            |                             |       |  |

|                                                                                             |           |        | -5           | -4                          |       |  |

| LVCMOS18                                                                                    | Slow      | 2 mA   | 5.03         | 5.24                        | ns    |  |

|                                                                                             |           | 4 mA   | 3.08         | 3.21                        | ns    |  |

|                                                                                             |           | 6 mA   | 2.39         | 2.49                        | ns    |  |

|                                                                                             |           | 8 mA   | 1.83         | 1.90                        | ns    |  |

|                                                                                             | Fast      | 2 mA   | 3.98         | 4.15                        | ns    |  |

|                                                                                             |           | 4 mA   | 2.04         | 2.13                        | ns    |  |

|                                                                                             |           | 6 mA   | 1.09         | 1.14                        | ns    |  |

|                                                                                             |           | 8 mA   | 0.72         | 0.75                        | ns    |  |

| LVCMOS15                                                                                    | Slow      | 2 mA   | 4.49         | 4.68                        | ns    |  |

|                                                                                             |           | 4 mA   | 3.81         | 3.97                        | ns    |  |

|                                                                                             |           | 6 mA   | 2.99         | 3.11                        | ns    |  |

|                                                                                             | Fast      | 2 mA   | 3.25         | 3.38                        | ns    |  |

|                                                                                             |           | 4 mA   | 2.59         | 2.70                        | ns    |  |

|                                                                                             |           | 6 mA   | 1.47         | 1.53                        | ns    |  |

| LVCMOS12                                                                                    | Slow      | 2 mA   | 6.36         | 6.63                        | ns    |  |

|                                                                                             | Fast      | 2 mA   | 4.26         | 4.44                        | ns    |  |

| HSTL_I_18                                                                                   |           |        | 0.33         | 0.34                        | ns    |  |

| HSTL_III_18                                                                                 |           |        | 0.53         | 0.55                        | ns    |  |

| PCI33_3                                                                                     |           |        | 0.44         | 0.46                        | ns    |  |

| PCI66_3                                                                                     |           |        | 0.44         | 0.46                        | ns    |  |

| SSTL18_I                                                                                    |           |        | 0.24         | 0.25                        | ns    |  |

| SSTL2_I                                                                                     |           |        | -0.20        | -0.20                       | ns    |  |

| Differential Sta                                                                            | ndards    |        | 1            |                             |       |  |

| LVDS_25                                                                                     |           |        | -0.55        | -0.55                       | ns    |  |

| BLVDS_25                                                                                    |           |        | 0.04         | 0.04                        | ns    |  |

| MINI_LVDS_25                                                                                |           |        | -0.56        | -0.56                       | ns    |  |

| LVPECL_25                                                                                   |           |        | Input        | Only                        | ns    |  |

| RSDS_25                                                                                     |           |        | -0.48        | -0.48                       | ns    |  |

| DIFF_HSTL_I_                                                                                | 18        |        | 0.42         | 0.42                        | ns    |  |

| DIFF_HSTL_III                                                                               | _18       |        | 0.53         | 0.55                        | ns    |  |

| DIFF_SSTL18_                                                                                | I         |        | 0.40         | 0.40                        | ns    |  |

| DIFF_SSTL2_I                                                                                |           |        | 0.44         | 0.44                        | ns    |  |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77, Table 80, and Table 82.

- 2. These adjustments are used to convert output- and three-state-path times originally specified for the LVCMOS25 standard with 12 mA drive and Fast slew rate to times that correspond to other signal standards. Do not adjust times that measure when outputs go into a high-impedance state.

| Symbol                    | Description                                                                                | Requirement                        | Units |

|---------------------------|--------------------------------------------------------------------------------------------|------------------------------------|-------|

| T <sub>CCS</sub>          | SPI serial Flash PROM chip-select time                                                     | $T_{CCS} \leq T_{MCCL1} - T_{CCO}$ | ns    |

| T <sub>DSU</sub>          | SPI serial Flash PROM data input setup time                                                | $T_{DSU} \leq T_{MCCL1} - T_{CCO}$ | ns    |

| T <sub>DH</sub>           | SPI serial Flash PROM data input hold time                                                 | $T_{DH} \leq T_{MCCH1}$            | ns    |

| T <sub>V</sub>            | SPI serial Flash PROM data clock-to-output time                                            | $T_V \leq T_{MCCLn} - T_{DCC}$     | ns    |

| $f_{C} \text{ or } f_{R}$ | Maximum SPI serial Flash PROM clock frequency (also depends on specific read command used) | $f_C \ge \frac{1}{T_{CCLKn(min)}}$ | MHz   |

Notes:

These requirements are for successful FPGA configuration in SPI mode, where the FPGA provides the CCLK frequency. The post configuration timing can be different to support the specific needs of the application loaded into the FPGA and the resulting clock source. 1.

Subtract additional printed circuit board routing delay as required by the application. 2.

# PQ208: 208-pin Plastic Quad Flat Package

The 208-pin plastic quad flat package, PQ208, supports two different Spartan-3E FPGAs, including the XC3S250E and the XC3S500E.

Table 141 lists all the PQ208 package pins. They are sorted by bank number and then by pin name. Pairs of pins that form a differential I/O pair appear together in the table. The table also shows the pin number for each pin and the pin type, as defined earlier.

An electronic version of this package pinout table and footprint diagram is available for download from the Xilinx website at:

http://www.xilinx.com/support/documentation/data\_sheets /s3e\_pin.zip

## **Pinout Table**

| Table 141 | able 141: PQ208 Package Pinout   |              |      |  |  |  |  |

|-----------|----------------------------------|--------------|------|--|--|--|--|

| Bank      | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре |  |  |  |  |

| 0         | Ю                                | P187         | I/O  |  |  |  |  |

| 0         | IO/VREF_0                        | P179         | VREF |  |  |  |  |

| 0         | IO_L01N_0                        | P161         | I/O  |  |  |  |  |

| 0         | IO_L01P_0                        | P160         | I/O  |  |  |  |  |

| 0         | IO_L02N_0/VREF_0                 | P163         | VREF |  |  |  |  |

| 0         | IO_L02P_0                        | P162         | I/O  |  |  |  |  |

| 0         | IO_L03N_0                        | P165         | I/O  |  |  |  |  |

| 0         | IO_L03P_0                        | P164         | I/O  |  |  |  |  |

| 0         | IO_L04N_0/VREF_0                 | P168         | VREF |  |  |  |  |

| 0         | IO_L04P_0                        | P167         | I/O  |  |  |  |  |

| 0         | IO_L05N_0                        | P172         | I/O  |  |  |  |  |

| 0         | IO_L05P_0                        | P171         | I/O  |  |  |  |  |

| 0         | IO_L07N_0/GCLK5                  | GCLK5 P178 G |      |  |  |  |  |

| 0         | IO_L07P_0/GCLK4                  | P177         | GCLK |  |  |  |  |

| 0         | IO_L08N_0/GCLK7                  | P181         | GCLK |  |  |  |  |

| 0         | IO_L08P_0/GCLK6                  | P180         | GCLK |  |  |  |  |

| 0         | IO_L10N_0/GCLK11                 | P186         | GCLK |  |  |  |  |

| 0         | IO_L10P_0/GCLK10                 | P185         | GCLK |  |  |  |  |

| 0         | IO_L11N_0                        | P190         | I/O  |  |  |  |  |

| 0         | IO_L11P_0                        | P189         | I/O  |  |  |  |  |

| 0         | IO_L12N_0/VREF_0                 | P193         | VREF |  |  |  |  |

| 0         | IO_L12P_0                        | P192         | I/O  |  |  |  |  |

| 0         | IO_L13N_0                        | P197         | I/O  |  |  |  |  |

| 0         | IO_L13P_0                        | P196         | I/O  |  |  |  |  |

| 0         | IO_L14N_0/VREF_0                 | P200         | VREF |  |  |  |  |

| 0         | IO_L14P_0                        | P199         | I/O  |  |  |  |  |

| 0         | IO_L15N_0                        | P203         | I/O  |  |  |  |  |

| Table 141: PQ208 Package Pinout |                                  |              |      |  |  |  |

|---------------------------------|----------------------------------|--------------|------|--|--|--|

| Bank                            | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре |  |  |  |

| 0                               | 10                               | P187         | I/O  |  |  |  |

| 0                               | IO/VREF_0                        | P179         | VREF |  |  |  |

| 0                               | IO_L01N_0                        | P161         | I/O  |  |  |  |

| 0                               | IO_L01P_0                        | P160         | I/O  |  |  |  |

| 0                               | IO_L02N_0/VREF_0                 | P163         | VREF |  |  |  |

| 0                               | IO_L02P_0                        | P162         | I/O  |  |  |  |

| 0                               | IO_L03N_0                        | P165         | I/O  |  |  |  |

| 0                               | IO_L03P_0                        | P164         | I/O  |  |  |  |

| 0                               | IO_L04N_0/VREF_0                 | P168         | VREF |  |  |  |

| 0                               | IO_L04P_0                        | P167         | I/O  |  |  |  |

| 0                               | IO_L05N_0                        | P172         | I/O  |  |  |  |

| 0                               | IO_L05P_0                        | P171         | I/O  |  |  |  |

| 0                               | IO_L07N_0/GCLK5                  | P178         | GCLK |  |  |  |

| 0                               | IO_L07P_0/GCLK4                  | P177         | GCLK |  |  |  |

| 0                               | IO_L08N_0/GCLK7                  | P181         | GCLK |  |  |  |

| 0                               | IO_L08P_0/GCLK6                  | P180         | GCLK |  |  |  |

| 0                               | IO_L10N_0/GCLK11                 | P186         | GCLK |  |  |  |

| 0                               | IO_L10P_0/GCLK10                 | P185         | GCLK |  |  |  |

| 0                               | IO_L11N_0                        | P190         | I/O  |  |  |  |

| 0                               | IO_L11P_0                        | P189         | I/O  |  |  |  |

| 0                               | IO_L12N_0/VREF_0                 | P193         | VREF |  |  |  |

| 0                               | IO_L12P_0                        | P192         | I/O  |  |  |  |

| 0                               | IO_L13N_0                        | P197         | I/O  |  |  |  |

| 0                               | IO_L13P_0                        | P196         | I/O  |  |  |  |

| 0                               | IO_L14N_0/VREF_0                 | P200         | VREF |  |  |  |

| Table | 141: | PQ208 | Package | Pinout | (Cont'd) |

|-------|------|-------|---------|--------|----------|

|-------|------|-------|---------|--------|----------|

| Bank | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре       |

|------|----------------------------------|--------------|------------|

| 0    | IO_L15P_0                        | P202         | I/O        |

| 0    | IO_L16N_0/HSWAP                  | P206         | DUAL       |

| 0    | IO_L16P_0                        | P205         | I/O        |

| 0    | IP                               | P159         | INPUT      |

| 0    | IP                               | P169         | INPUT      |

| 0    | IP                               | P194         | INPUT      |

| 0    | IP                               | P204         | INPUT      |

| 0    | IP_L06N_0                        | P175         | INPUT      |

| 0    | IP_L06P_0                        | P174         | INPUT      |

| 0    | IP_L09N_0/GCLK9                  | P184         | GCLK       |

| 0    | IP_L09P_0/GCLK8                  | P183         | GCLK       |

| 0    | VCCO_0                           | P176         | VCCO       |

| 0    | VCCO_0                           | P191         | VCCO       |

| 0    | VCCO_0                           | P201         | VCCO       |

| 1    | IO_L01N_1/A15                    | P107         | DUAL       |

| 1    | IO_L01P_1/A16                    | P106         | DUAL       |

| 1    | IO_L02N_1/A13                    | P109         | DUAL       |

| 1    | IO_L02P_1/A14                    | P108         | DUAL       |

| 1    | IO_L03N_1/VREF_1                 | P113         | VREF       |

| 1    | IO_L03P_1                        | P112         | I/O        |

| 1    | IO_L04N_1                        | P116         | I/O        |

| 1    | IO_L04P_1                        | P115         | I/O        |

| 1    | IO_L05N_1/A11                    | P120         | DUAL       |

| 1    | IO_L05P_1/A12                    | P119         | DUAL       |

| 1    | IO_L06N_1/VREF_1                 | P123         | VREF       |

| 1    | IO_L06P_1                        | P122         | I/O        |

| 1    | IO_L07N_1/A9/RHCLK1              | P127         | RHCLK/DUAL |

| 1    | IO_L07P_1/A10/RHCLK0             | P126         | RHCLK/DUAL |

| 1    | IO_L08N_1/A7/RHCLK3              | P129         | RHCLK/DUAL |

| 1    | IO_L08P_1/A8/RHCLK2              | P128         | RHCLK/DUAL |

| 1    | IO_L09N_1/A5/RHCLK5              | P133         | RHCLK/DUAL |

| 1    | IO_L09P_1/A6/RHCLK4              | P132         | RHCLK/DUAL |

| 1    | IO_L10N_1/A3/RHCLK7              | P135         | RHCLK/DUAL |

| 1    | IO_L10P_1/A4/RHCLK6              | P134         | RHCLK/DUAL |

| 1    | IO_L11N_1/A1                     | P138         | DUAL       |

| 1    | IO_L11P_1/A2                     | P137         | DUAL       |

| 1    | IO_L12N_1/A0                     | P140         | DUAL       |

| 1    | IO_L12P_1                        | P139         | I/O        |

| 1    | IO_L13N_1                        | P145         | I/O        |

| 1    | IO_L13P_1                        | P144         | I/O        |

| 1    | IO_L14N_1                        | P147         | I/O        |

| 1    | IO_L14P_1                        | P146         | I/O        |

## Table 141: PQ208 Package Pinout (Cont'd)

| Bank | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре      |

|------|----------------------------------|--------------|-----------|

| 1    | IO_L15N_1/LDC0                   | P151         | DUAL      |

| 1    | IO_L15P_1/HDC                    | P150         | DUAL      |

| 1    | IO_L16N_1/LDC2                   | P153         | DUAL      |

| 1    | IO_L16P_1/LDC1                   | P152         | DUAL      |

| 1    | IP                               | P110         | INPUT     |

| 1    | IP                               | P118         | INPUT     |

| 1    | IP                               | P124         | INPUT     |

| 1    | IP                               | P130         | INPUT     |

| 1    | IP                               | P142         | INPUT     |

| 1    | IP                               | P148         | INPUT     |

| 1    | IP                               | P154         | INPUT     |

| 1    | IP/VREF_1                        | P136         | VREF      |

| 1    | VCCO_1                           | P114         | VCCO      |

| 1    | VCCO_1                           | P125         | VCCO      |

| 1    | VCCO_1                           | P143         | VCCO      |

| 2    | IO/D5                            | P76          | DUAL      |

| 2    | IO/M1                            | P84          | DUAL      |

| 2    | IO/VREF_2                        | P98          | VREF      |

| 2    | IO_L01N_2/INIT_B                 | P56          | DUAL      |

| 2    | IO_L01P_2/CSO_B                  | P55          | DUAL      |

| 2    | IO_L03N_2/MOSI/CSI_B             | P61          | DUAL      |

| 2    | IO_L03P_2/DOUT/BUSY              | P60          | DUAL      |

| 2    | IO_L04N_2                        | P63          | I/O       |

| 2    | IO_L04P_2                        | P62          | I/O       |

| 2    | IO_L05N_2                        | P65          | I/O       |

| 2    | IO_L05P_2                        | P64          | I/O       |

| 2    | IO_L06N_2                        | P69          | I/O       |

| 2    | IO_L06P_2                        | P68          | I/O       |

| 2    | IO_L08N_2/D6/GCLK13              | P75          | DUAL/GCLK |

| 2    | IO_L08P_2/D7/GCLK12              | P74          | DUAL/GCLK |

| 2    | IO_L09N_2/D3/GCLK15              | P78          | DUAL/GCLK |

| 2    | IO_L09P_2/D4/GCLK14              | P77          | DUAL/GCLK |

| 2    | IO_L11N_2/D1/GCLK3               | P83          | DUAL/GCLK |

| 2    | IO_L11P_2/D2/GCLK2               | P82          | DUAL/GCLK |

| 2    | IO_L12N_2/DIN/D0                 | P87          | DUAL      |

| 2    | IO_L12P_2/M0                     | P86          | DUAL      |

| 2    | IO_L13N_2                        | P90          | I/O       |

| 2    | IO_L13P_2                        | P89          | I/O       |

| 2    | IO_L14N_2/A22                    | P94          | DUAL      |

| 2    | IO_L14P_2/A23                    | P93          | DUAL      |

| 2    | IO_L15N_2/A20                    | P97          | DUAL      |

| 2    | IO_L15P_2/A21                    | P96          | DUAL      |

| 2    | IO_L16N_2/VS1/A18                | P100         | DUAL      |

## Table 141: PQ208 Package Pinout (Cont'd)

| Bank | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре      |

|------|----------------------------------|--------------|-----------|

| 2    | IO_L16P_2/VS2/A19                | P99          | DUAL      |

| 2    | IO_L17N_2/CCLK                   | P103         | DUAL      |

| 2    | IO_L17P_2/VS0/A17                | P102         | DUAL      |

| 2    | IP                               | P54          | INPUT     |

| 2    | IP                               | P91          | INPUT     |

| 2    | IP                               | P101         | INPUT     |

| 2    | IP_L02N_2                        | P58          | INPUT     |

| 2    | IP_L02P_2                        | P57          | INPUT     |

| 2    | IP_L07N_2/VREF_2                 | P72          | VREF      |

| 2    | IP_L07P_2                        | P71          | INPUT     |

| 2    | IP_L10N_2/M2/GCLK1               | P81          | DUAL/GCLK |

| 2    | IP_L10P_2/RDWR_B/<br>GCLK0       | P80          | DUAL/GCLK |

| 2    | VCCO_2                           | P59          | VCCO      |

| 2    | VCCO_2                           | P73          | VCCO      |

| 2    | VCCO_2                           | P88          | VCCO      |

| 3    | IO/VREF_3                        | P45          | VREF      |

| 3    | IO_L01N_3                        | P3           | I/O       |

| 3    | IO_L01P_3                        | P2           | I/O       |

| 3    | IO_L02N_3/VREF_3                 | P5           | VREF      |

| 3    | IO_L02P_3                        | P4           | I/O       |

| 3    | IO_L03N_3                        | P9           | I/O       |

| 3    | IO_L03P_3                        | P8           | I/O       |

| 3    | IO_L04N_3                        | P12          | I/O       |

| 3    | IO_L04P_3                        | P11          | I/O       |

| 3    | IO_L05N_3                        | P16          | I/O       |

| 3    | IO_L05P_3                        | P15          | I/O       |

| 3    | IO_L06N_3                        | P19          | I/O       |

| 3    | IO_L06P_3                        | P18          | I/O       |

| 3    | IO_L07N_3/LHCLK1                 | P23          | LHCLK     |

| 3    | IO_L07P_3/LHCLK0                 | P22          | LHCLK     |

| 3    | IO_L08N_3/LHCLK3                 | P25          | LHCLK     |

| 3    | IO_L08P_3/LHCLK2                 | P24          | LHCLK     |

| 3    | IO_L09N_3/LHCLK5                 | P29          | LHCLK     |

| 3    | IO_L09P_3/LHCLK4                 | P28          | LHCLK     |

| 3    | IO_L10N_3/LHCLK7                 | P31          | LHCLK     |

| 3    | IO_L10P_3/LHCLK6                 | P30          | LHCLK     |

| 3    | IO_L11N_3                        | P34          | I/O       |

| 3    | IO_L11P_3                        | P33          | I/O       |

| 3    | IO_L12N_3                        | P36          | I/O       |

| 3    | IO_L12P_3                        | P35          | I/O       |

| 3    | IO_L13N_3                        | P40          | I/O       |

| 3    | IO_L13P_3                        | P39          | I/O       |

| 3    | IO_L14N_3                        | P42          | I/O       |

## Table 143: FT256 Package Pinout (Cont'd)

| Bank | XC3S250E Pin Name    | XC3S500E Pin Name    | XC3S1200E Pin Name   | FT256<br>Ball | Туре                                                             |

|------|----------------------|----------------------|----------------------|---------------|------------------------------------------------------------------|

| 1    | IO                   | IO                   | IP                   | M14           | 250E: I/O<br>500E: I/O<br>1200E: INPUT                           |

| 1    | IO/VREF_1            | IP/VREF_1            | IP/VREF_1            | D16           | 250E: VREF(I/O)<br>500E:<br>VREF(INPUT)<br>1200E:<br>VREF(INPUT) |

| 1    | IP/VREF_1            | IP/VREF_1            | IP/VREF_1            | H13           | VREF                                                             |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | E15           | VCCO                                                             |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | G11           | VCCO                                                             |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | K11           | VCCO                                                             |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | M15           | VCCO                                                             |

| 2    | IP                   | IP                   | IO                   | M7            | 250E: INPUT<br>500E: INPUT<br>1200E: I/O                         |

| 2    | IP                   | IP                   | IO                   | T12           | 250E: INPUT<br>500E: INPUT<br>1200E: I/O                         |

| 2    | IO/D5                | IO/D5                | IO/D5                | Т8            | DUAL                                                             |