Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Active                                                         |

| Number of LABs/CLBs            | 2168                                                           |

| Number of Logic Elements/Cells | 19512                                                          |

| Total RAM Bits                 | 516096                                                         |

| Number of I/O                  | 304                                                            |

| Number of Gates                | 1200000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                  |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                |

| Package / Case                 | 400-BGA                                                        |

| Supplier Device Package        | 400-FBGA (21x21)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1200e-5fgg400c |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Architectural Overview**

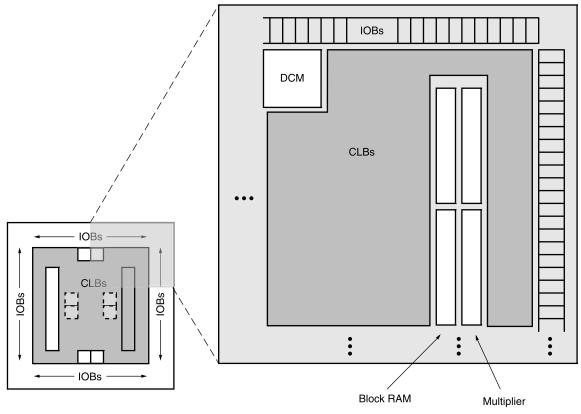

The Spartan-3E family architecture consists of five fundamental programmable functional elements:

- **Configurable Logic Blocks (CLBs)** contain flexible Look-Up Tables (LUTs) that implement logic plus storage elements used as flip-flops or latches. CLBs perform a wide variety of logical functions as well as store data.

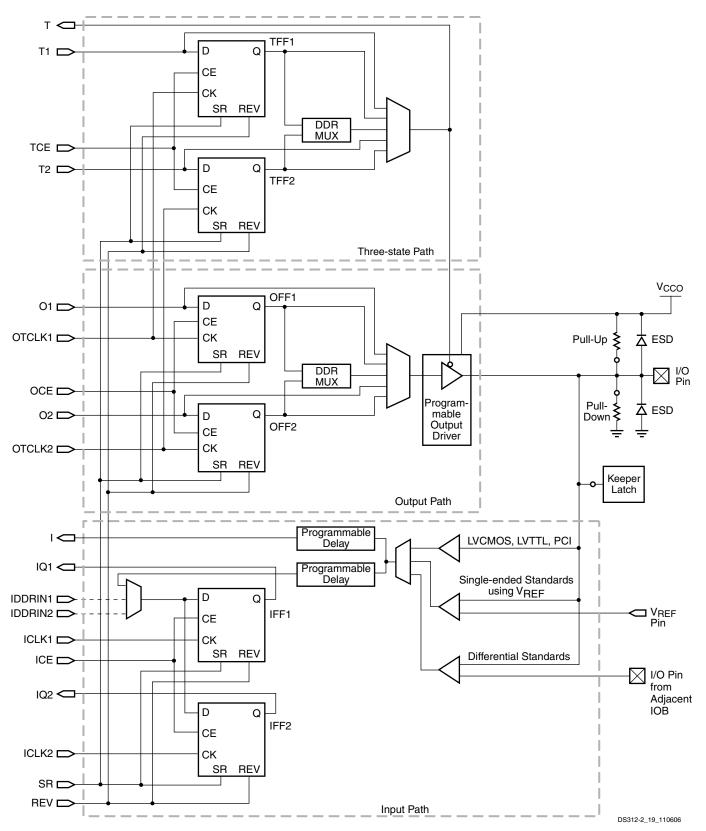

- Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3-state operation. Supports a variety of signal standards, including four high-performance differential standards. Double Data-Rate (DDR) registers are included.

- **Block RAM** provides data storage in the form of 18-Kbit dual-port blocks.

- **Multiplier Blocks** accept two 18-bit binary numbers as inputs and calculate the product.

• **Digital Clock Manager (DCM) Blocks** provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase-shifting clock signals.

These elements are organized as shown in Figure 1. A ring of IOBs surrounds a regular array of CLBs. Each device has two columns of block RAM except for the XC3S100E, which has one column. Each RAM column consists of several 18-Kbit RAM blocks. Each block RAM is associated with a dedicated multiplier. The DCMs are positioned in the center with two at the top and two at the bottom of the device. The XC3S100E has only one DCM at the top and bottom, while the XC3S1200E and XC3S1600E add two DCMs in the middle of the left and right sides.

The Spartan-3E family features a rich network of traces that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

DS312\_01\_111904

Figure 1: Spartan-3E Family Architecture

## Configuration

Spartan-3E FPGAs are programmed by loading configuration data into robust, reprogrammable, static CMOS configuration latches (CCLs) that collectively control all functional elements and routing resources. The FPGA's configuration data is stored externally in a PROM or some other non-volatile medium, either on or off the board. After applying power, the configuration data is written to the FPGA using any of seven different modes:

- Master Serial from a Xilinx Platform Flash PROM

- Serial Peripheral Interface (SPI) from an industry-standard SPI serial Flash

- Byte Peripheral Interface (BPI) Up or Down from an industry-standard x8 or x8/x16 parallel NOR Flash

- Slave Serial, typically downloaded from a processor

- Slave Parallel, typically downloaded from a processor

- Boundary Scan (JTAG), typically downloaded from a processor or system tester.

Furthermore, Spartan-3E FPGAs support MultiBoot configuration, allowing two or more FPGA configuration bitstreams to be stored in a single parallel NOR Flash. The FPGA application controls which configuration to load next and when to load it.

## I/O Capabilities

The Spartan-3E FPGA SelectIO interface supports many popular single-ended and differential standards. Table 2 shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination.

Spartan-3E FPGAs support the following single-ended standards:

- 3.3V low-voltage TTL (LVTTL)

- Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V, 1.5V, or 1.2V

- 3V PCI at 33 MHz, and in some devices, <u>66 MHz</u>

- HSTL I and III at 1.8V, commonly used in memory applications

- SSTL I at 1.8V and 2.5V, commonly used for memory applications

Spartan-3E FPGAs support the following differential standards:

- LVDS

- Bus LVDS

- mini-LVDS

- RSDS

- Differential HSTL (1.8V, Types I and III)

- Differential SSTL (2.5V and 1.8V, Type I)

- 2.5V LVPECL inputs

| Package                | VQ1<br>VQG                      |                  | CP <sup>.</sup><br>CPG | 132<br>132       |                    | 144<br>6144      | PQ:<br>PQC         |                  |                    | 256<br>1256      |                    | 320<br>3320       |                    | 400<br>6400        | FG4<br>FGG         |                    |

|------------------------|---------------------------------|------------------|------------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|------------------|--------------------|-------------------|--------------------|--------------------|--------------------|--------------------|

| Footprint<br>Size (mm) | 16 x                            | 16               | 8 :                    | x 8              | 22 >               | c 22             | 30.5 >             | c 30.5           | 17 ג               | k 17             | 19 >               | c 19              | 21 >               | k 21               | <b>23</b> :        | x 23               |

| Device                 | User                            | Diff             | User                   | Diff             | User               | Diff             | User               | Diff             | User               | Diff             | User               | Diff              | User               | Diff               | User               | Diff               |

| XC3S100E               | <b>66<sup>(2)</sup></b><br>9(7) | <b>30</b><br>(2) | <b>83</b><br>(11)      | <b>35</b><br>(2) | <b>108</b><br>(28) | <b>40</b><br>(4) | -                  | -                | -                  | -                | -                  | -                 | -                  | -                  | -                  | -                  |

| XC3S250E               | <b>66</b><br>(7)                | <b>30</b><br>(2) | <b>92</b><br>(7)       | <b>41</b><br>(2) | <b>108</b><br>(28) | <b>40</b><br>(4) | <b>158</b><br>(32) | <b>65</b><br>(5) | <b>172</b><br>(40) | <b>68</b><br>(8) | -                  | -                 | -                  | -                  | -                  | -                  |

| XC3S500E               | <b>66<sup>(3)</sup></b><br>(7)  | <b>30</b><br>(2) | <b>92</b><br>(7)       | <b>41</b><br>(2) | -                  | -                | <b>158</b><br>(32) | <b>65</b><br>(5) | <b>190</b><br>(41) | <b>77</b><br>(8) | <b>232</b><br>(56) | <b>92</b><br>(12) | -                  | -                  | -                  | -                  |

| XC3S1200E              | -                               | -                | -                      | -                | -                  | -                | -                  | -                | <b>190</b><br>(40) | <b>77</b><br>(8) | <b>250</b><br>(56) | <b>99</b><br>(12) | <b>304</b><br>(72) | <b>124</b><br>(20) | -                  | -                  |

| XC3S1600E              | -                               | -                | -                      | -                | -                  | -                | -                  | -                | -                  | -                | <b>250</b><br>(56) | <b>99</b><br>(12) | <b>304</b><br>(72) | <b>124</b><br>(20) | <b>376</b><br>(82) | <b>156</b><br>(21) |

### Table 2: Available User I/Os and Differential (Diff) I/O Pairs

#### Notes:

1. All Spartan-3E devices provided in the same package are pin-compatible as further described in Module 4, Pinout Descriptions.

2. The number shown in **bold** indicates the maximum number of I/O and input-only pins. The number shown in (*italics*) indicates the number of input-only pins.

3. The XC3S500E is available in the VQG100 Pb-free package and not the standard VQ100. The VQG100 and VQ100 pin-outs are identical and general references to the VQ100 will apply to the XC3S500E.

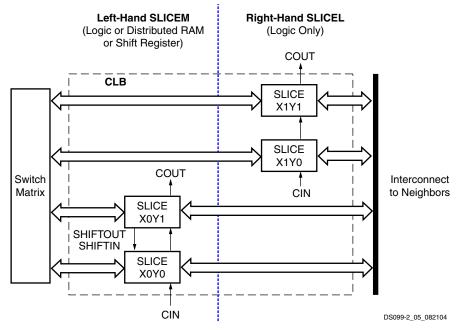

Figure 16: Arrangement of Slices within the CLB

### **Slice Location Designations**

The Xilinx development software designates the location of a slice according to its X and Y coordinates, starting in the bottom left corner, as shown in Figure 14. The letter 'X' followed by a number identifies columns of slices, incrementing from the left side of the die to the right. The letter 'Y' followed by a number identifies the position of each slice in a pair as well as indicating the CLB row, incrementing from the bottom of the die. Figure 16 shows the CLB located in the lower left-hand corner of the die. The SLICEM always has an even 'X' number, and the SLICEL always has an odd 'X' number.

### **Slice Overview**

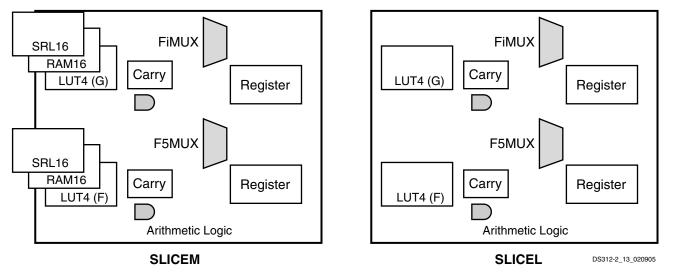

A slice includes two LUT function generators and two storage elements, along with additional logic, as shown in Figure 17.

Both SLICEM and SLICEL have the following elements in common to provide logic, arithmetic, and ROM functions:

- Two 4-input LUT function generators, F and G

- Two storage elements

- Two wide-function multiplexers, F5MUX and FiMUX

- Carry and arithmetic logic

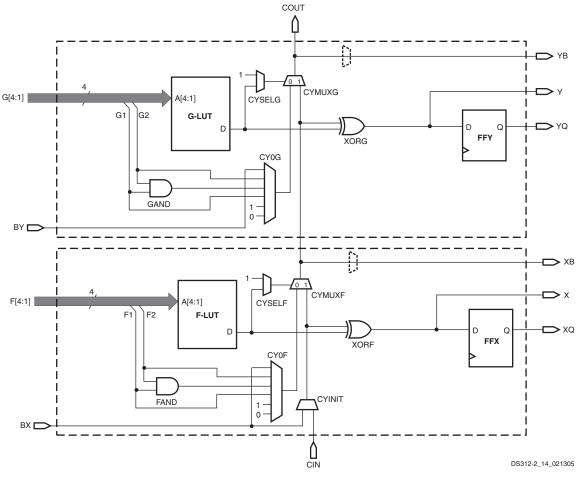

## **Carry and Arithmetic Logic**

For additional information, refer to the "Using Carry and Arithmetic Logic" chapter in UG331.

The carry chain, together with various dedicated arithmetic logic gates, support fast and efficient implementations of math operations. The carry logic is automatically used for most arithmetic functions in a design. The gates and multiplexers of the carry and arithmetic logic can also be used for general-purpose logic, including simple wide Boolean functions.

The carry chain enters the slice as CIN and exits as COUT, controlled by several multiplexers. The carry chain connects directly from one CLB to the CLB above. The carry chain can be initialized at any point from the BX (or BY) inputs.

The dedicated arithmetic logic includes the exclusive-OR gates XORF and XORG (upper and lower portions of the slice, respectively) as well as the AND gates GAND and FAND (upper and lower portions, respectively). These gates work in conjunction with the LUTs to implement efficient arithmetic functions, including counters and multipliers, typically at two bits per slice. See Figure 22 and Table 14.

#### Table 14: Carry Logic Functions

| Function | Description                                                                                                                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CYINIT   | <ul> <li>Initializes carry chain for a slice. Fixed selection of:</li> <li>CIN carry input from the slice below</li> <li>BX input</li> </ul>                                                                                                                                                                            |

| CY0F     | <ul> <li>Carry generation for bottom half of slice. Fixed selection of:</li> <li>F1 or F2 inputs to the LUT (both equal 1 when a carry is to be generated)</li> <li>FAND gate for multiplication</li> <li>BX input for carry initialization</li> <li>Fixed 1 or 0 input for use as a simple Boolean function</li> </ul> |

| Pin Name | FPGA<br>Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | During Configuration                                                                                                                                                                                                  | After Configuration                                                                                                                                                                                                        |

|----------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VS[2:0]  | Input                              | Variant Select. Instructs the FPGA how<br>to communicate with the attached SPI<br>Flash PROM. See Design Considerations<br>for the HSWAP, M[2:0], and VS[2:0] Pins.                                                                                                                                                                                                                                                                                                                                        | Must be at the logic levels shown<br>in Table 53. Sampled when<br>INIT_B goes High.                                                                                                                                   | User I/O                                                                                                                                                                                                                   |

| MOSI     | Output                             | Serial Data Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FPGA sends SPI Flash memory<br>read commands and starting<br>address to the PROM's serial<br>data input.                                                                                                              | User I/O                                                                                                                                                                                                                   |

| DIN      | Input                              | Serial Data Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FPGA receives serial data from PROM's serial data output.                                                                                                                                                             | User I/O                                                                                                                                                                                                                   |

| CSO_B    | Output                             | Chip Select Output. Active Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Connects to the SPI Flash<br>PROM's chip-select input. If<br>HSWAP = 1, connect this signal<br>to a 4.7 k $\Omega$ pull-up resistor to<br>3.3V.                                                                       | Drive CSO_B High after<br>configuration to disable the<br>SPI Flash and reclaim the<br>MOSI, DIN, and CCLK pins.<br>Optionally, re-use this pin<br>and MOSI, DIN, and CCLK<br>to continue communicating<br>with SPI Flash. |

| CCLK     | Output                             | <b>Configuration Clock</b> . Generated by<br>FPGA internal oscillator. Frequency<br>controlled by <b>ConfigRate</b> bitstream<br>generator option. If CCLK PCB trace is<br>long or has multiple connections,<br>terminate this output to maintain signal<br>integrity. See CCLK Design<br>Considerations.                                                                                                                                                                                                  | Drives PROM's clock input.                                                                                                                                                                                            | User I/O                                                                                                                                                                                                                   |

| DOUT     | Output                             | Serial Data Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Actively drives. Not used in<br>single-FPGA designs. In a<br>daisy-chain configuration, this<br>pin connects to DIN input of the<br>next FPGA in the chain.                                                           | User I/O                                                                                                                                                                                                                   |

| INIT_B   | Open-drain<br>bidirectional<br>I/O | <b>Initialization Indicator</b> . Active Low.<br>Goes Low at start of configuration during<br>Initialization memory clearing process.<br>Released at end of memory clearing,<br>when mode select pins are sampled. In<br>daisy-chain applications, this signal<br>requires an external 4.7 k $\Omega$ pull-up<br>resistor to VCCO_2.                                                                                                                                                                       | Active during configuration. If<br>SPI Flash PROM requires<br>> 2 ms to awake after powering<br>on, hold INIT_B Low until PROM<br>is ready. If CRC error detected<br>during configuration, FPGA<br>drives INIT_B Low. | User I/O. If unused in the application, drive INIT_B<br>High.                                                                                                                                                              |

| DONE     | Open-drain<br>bidirectional<br>I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external 330 $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                              | Low indicates that the FPGA is not yet configured.                                                                                                                                                                    | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully configured.                                                                                                                     |

| PROG_B   | Input                              | <b>Program FPGA</b> . Active Low. When<br>asserted Low for 500 ns or longer, forces<br>the FPGA to restart its configuration<br>process by clearing configuration<br>memory and resetting the DONE and<br>INIT_B pins once PROG_B returns High.<br>Recommend external 4.7 kΩ pull-up<br>resistor to 2.5V. Internal pull-up value<br>may be weaker (see Table 78). If driving<br>externally with a 3.3V output, use an<br>open-drain or open-collector driver or use<br>a current limiting series resistor. | Must be High to allow configuration to start.                                                                                                                                                                         | Drive PROG_B Low and<br>release to reprogram FPGA.<br>Hold PROG_B to force<br>FPGA I/O pins into Hi-Z,<br>allowing direct programming<br>access to SPI Flash PROM<br>pins.                                                 |

#### Table 55: Serial Peripheral Interface (SPI) Connections (Cont'd)

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | During Configuration                               | After Configuration                                                                                                                                                    |

|----------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external $330 \Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                                            | Low indicates that the FPGA is not yet configured. | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA is<br>successfully configured.                                                              |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low. When<br>asserted Low for 500 ns or longer,<br>forces the FPGA to restart its<br>configuration process by clearing<br>configuration memory and resetting<br>the DONE and INIT_B pins once<br>PROG_B returns High.<br>Recommend external 4.7 k $\Omega$<br>pull-up resistor to 2.5V. Internal<br>pull-up value may be weaker (see<br>Table 78). If driving externally with a<br>3.3V output, use an open-drain or<br>open-collector driver or use a<br>current limiting series resistor. | Must be High to allow configuration to start.      | Drive PROG_B Low and<br>release to reprogram<br>FPGA. Hold PROG_B to<br>force FPGA I/O pins into<br>Hi-Z, allowing direct<br>programming access to<br>Flash PROM pins. |

#### Table 59: Byte-Wide Peripheral Interface (BPI) Connections (Cont'd)

### **Voltage Compatibility**

V The FPGA's parallel Flash interface signals are within I/O Banks 1 and 2. The majority of parallel Flash PROMs use a single 3.3V supply voltage. Consequently, in most cases, the FPGA's VCCO\_1 and VCCO\_2 supply voltages must also be 3.3V to match the parallel Flash PROM. There are some 1.8V parallel Flash PROMs available and the FPGA interfaces with these devices if the VCCO\_1 and VCCO\_2 supplies are also 1.8V.

# Power-On Precautions if PROM Supply is Last in Sequence

Like SPI Flash PROMs, parallel Flash PROMs typically require some amount of internal initialization time when the supply voltage reaches its minimum value.

The PROM supply voltage also connects to the FPGA's VCCO\_2 supply input. In many systems, the PROM supply feeding the FPGA's VCCO\_2 input is valid before the FPGA's other V<sub>CCINT</sub> and V<sub>CCAUX</sub> supplies, and consequently, there is no issue. However, if the PROM supply is last in the sequence, a potential race occurs between the FPGA and the parallel Flash PROM. See

Power-On Precautions if 3.3V Supply is Last in Sequence for a similar description of the issue for SPI Flash PROMs.

### **Supported Parallel NOR Flash PROM Densities**

Table 60 indicates the smallest usable parallel Flash PROMto program a single Spartan-3E FPGA. Parallel Flashdensity is specified in bits but addressed as bytes. TheFPGA presents up to 24 address lines during configurationbut not all are required for single FPGA applications.Table 60 shows the minimum required number of addresslines between the FPGA and parallel Flash PROM. Theactual number of address line required depends on thedensity of the attached parallel Flash PROM.

A multiple-FPGA daisy-chained application requires a parallel Flash PROM large enough to contain the sum of the FPGA file sizes. An application can also use a larger-density parallel Flash PROM to hold additional data beyond just FPGA configuration data. For example, the parallel Flash PROM can also contain the application code for a MicroBlaze RISC processor core implemented within the Spartan-3E FPGA. After configuration, the MicroBlaze processor can execute directly from external Flash or can copy the code to other, faster system memory before executing the code.

#### Table 60: Number of Bits to Program a Spartan-3E FPGA and Smallest Parallel Flash PROM

| Spartan-3E FPGA | Uncompressed<br>File Sizes (bits) | Smallest Usable<br>Parallel Flash PROM | Minimum Required<br>Address Lines |

|-----------------|-----------------------------------|----------------------------------------|-----------------------------------|

| XC3S100E        | 581,344                           | 1 Mbit                                 | A[16:0]                           |

| XC3S250E        | 1,353,728                         | 2 Mbit                                 | A[17:0]                           |

| XC3S500E        | 2,270,208                         | 4 Mbit                                 | A[18:0]                           |

| XC3S1200E       | 3,841,184                         | 4 Mbit                                 | A[18:0]                           |

| XC3S1600E       | 5,969,696                         | 8 Mbit                                 | A[19:0]                           |

## **Powering Spartan-3E FPGAs**

For additional information, refer to the "Powering Spartan-3 Generation FPGAs" chapter in <u>UG331</u>.

## **Voltage Supplies**

Like Spartan-3 FPGAs, Spartan-3E FPGAs have multiple voltage supply inputs, as shown in Table 70. There are two

### Table 70: Spartan-3E Voltage Supplies

supply inputs for internal logic functions,  $V_{CCINT}$  and  $V_{CCAUX}$ . Each of the four I/O banks has a separate  $V_{CCO}$  supply input that powers the output buffers within the associated I/O bank. All of the  $V_{CCO}$  connections to a specific I/O bank must be connected and must connect to the same voltage.

| Supply Input       | Description                                                                                                                                                                                        | Nominal Supply Voltage                        |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|--|

| V <sub>CCINT</sub> | Internal core supply voltage. Supplies all internal logic functions, such as CLBs, block RAM, and multipliers. Input to Power-On Reset (POR) circuit.                                              | 1.2V                                          |  |  |

| V <sub>CCAUX</sub> | Auxiliary supply voltage. Supplies Digital Clock Managers (DCMs), differential drivers, dedicated configuration pins, JTAG interface. Input to Power-On Reset (POR) circuit.                       | 2.5V                                          |  |  |

| VCCO_0             | Supplies the output buffers in I/O Bank 0, the bank along the top edge of the FPGA.                                                                                                                | Selectable, 3.3V, 2.5V, 1.8,<br>1.5V, or 1.2V |  |  |

| VCCO_1             | Supplies the output buffers in I/O Bank 1, the bank along the right edge of the FPGA. In Byte-Wide Peripheral Interface (BPI) Parallel Flash Mode, connects to the same voltage as the Flash PROM. | Selectable, 3.3V, 2.5V, 1.8,<br>1.5V, or 1.2V |  |  |

| VCCO_2             | Supplies the output buffers in I/O Bank 2, the bank along the bottom edge of the FPGA. Connects to the same voltage as the FPGA configuration source. Input to Power-On Reset (POR) circuit.       | Selectable, 3.3V, 2.5V, 1.8,<br>1.5V, or 1.2V |  |  |

| VCCO_3             | Supplies the output buffers in I/O Bank 3, the bank along the left edge of the FPGA.                                                                                                               | Selectable, 3.3V, 2.5V, 1.8,<br>1.5V, or 1.2V |  |  |

In a 3.3V-only application, all four V<sub>CCO</sub> supplies connect to 3.3V. However, Spartan-3E FPGAs provide the ability to bridge between different I/O voltages and standards by applying different voltages to the V<sub>CCO</sub> inputs of different banks. Refer to I/O Banking Rules for which I/O standards can be intermixed within a single I/O bank.

Each I/O bank also has an separate, optional input voltage reference supply, called V<sub>REF</sub> If the I/O bank includes an I/O standard that requires a voltage reference such as HSTL or SSTL, then all V<sub>REF</sub> pins within the I/O bank must be connected to the same voltage.

## Spartan-3 FPGA Family: DC and Switching Characteristics

DS312 (4.0) October 29, 2012

#### **Product Specification**

## **DC Electrical Characteristics**

In this section, specifications may be designated as Advance, Preliminary, or Production. These terms are defined as follows:

<u>Advance</u>: Initial estimates are based on simulation, early characterization, and/or extrapolation from the characteristics of other families. Values are subject to change. Use as estimates, not for production.

**<u>Preliminary</u>:** Based on characterization. Further changes are not expected.

**Production:** These specifications are approved once the silicon has been characterized over numerous production lots. Parameter values are considered stable with no future changes expected.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. **Unless** otherwise noted, the published parameter values apply to all Spartan®-3E devices. AC and DC characteristics are specified using the same numbers for both commercial and industrial grades.

### **Absolute Maximum Ratings**

Stresses beyond those listed under Table 73, Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions is not implied. Exposure to absolute maximum conditions for extended periods of time adversely affects device reliability.

| Symbol                               | Description                              | Con                                           | ditions                 | Min   | Max                                    | Units |

|--------------------------------------|------------------------------------------|-----------------------------------------------|-------------------------|-------|----------------------------------------|-------|

| V <sub>CCINT</sub>                   | Internal supply voltage                  | -0.5                                          | 1.32                    | V     |                                        |       |

| V <sub>CCAUX</sub>                   | Auxiliary supply voltage                 |                                               |                         | -0.5  | 3.00                                   | V     |

| V <sub>CCO</sub>                     | Output driver supply voltage             |                                               | -0.5                    | 3.75  | V                                      |       |

| V <sub>REF</sub>                     | Input reference voltage                  |                                               |                         | -0.5  | V <sub>CCO</sub> +0.5 <sup>(1)</sup>   | V     |

| V <sub>IN</sub> <sup>(1,2,3,4)</sup> | Voltage applied to all User I/O pins and | Driver in a                                   | Commercial              | -0.95 | 4.4                                    | V     |

|                                      | Dual-Purpose pins                        | high-impedance<br>state                       | Industrial              | -0.85 | 4.3                                    | V     |

|                                      | Voltage applied to all Dedicated pins    |                                               | All temp. ranges        | -0.5  | V <sub>CCAUX</sub> +0.5 <sup>(3)</sup> | V     |

| I <sub>IK</sub>                      | Input clamp current per I/O pin          | $-0.5 \text{ V} < \text{V}_{IN} < (\text{V})$ | <sub>CCO</sub> + 0.5 V) | -     | ±100                                   | mA    |

| V <sub>ESD</sub>                     | Electrostatic Discharge Voltage          | Human body mod                                | lel                     | -     | ±2000                                  | V     |

|                                      |                                          | Charged device n                              | nodel                   | -     | ±500                                   | V     |

|                                      |                                          | Machine model                                 |                         | -     | ±200                                   | V     |

| TJ                                   | Junction temperature                     | ature                                         |                         |       |                                        | °C    |

| T <sub>STG</sub>                     | Storage temperature                      | -65                                           | 150                     | °C    |                                        |       |

#### Table 73: Absolute Maximum Ratings

Notes:

- 1. Each of the User I/O and Dual-Purpose pins is associated with one of the four banks'  $V_{CCO}$  rails. Keeping  $V_{IN}$  within 500 mV of the associated  $V_{CCO}$  rails or ground rail ensures that the internal diode junctions do not turn on. Table 77 specifies the  $V_{CCO}$  range used to evaluate the maximum  $V_{IN}$  voltage.

- Input voltages outside the -0.5V to V<sub>CCO</sub> + 0.5V (or V<sub>CCAUX</sub> + 0.5V) voltage range are require the I<sub>IK</sub> input diode clamp diode rating is met and no more than 100 pins exceed the range simultaneously. Prolonged exposure to such current may compromise device reliability. A sustained current of 10 mA will not compromise device reliability. See <u>XAPP459</u>: *Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families* for more details.

- 3. All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> rail do not turn on. Table 77 specifies the V<sub>CCAUX</sub> range used to evaluate the maximum V<sub>IN</sub> voltage. As long as the V<sub>IN</sub> max specification is met, oxide stress is not possible.

- 4. See XAPP459: Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Families.

- 5. For soldering guidelines, see <u>UG112</u>: Device Packaging and Thermal Characteristics and <u>XAPP427</u>: Implementation and Solder Reflow Guidelines for Pb-Free Packages.

© Copyright 2005–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

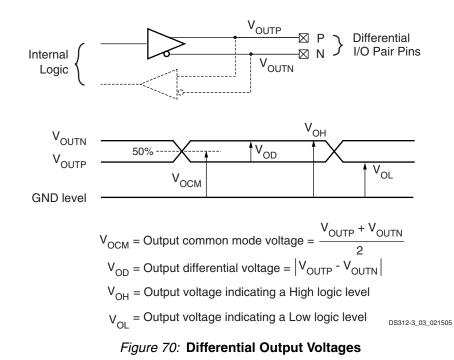

Table 83: DC Characteristics of User I/Os Using Differential Signal Standards

| IOSTANDARD       |             | V <sub>OD</sub> |             | ΔV          | ΔV <sub>OD</sub> V <sub>OCM</sub> |            |            |            | ΔV <sub>OCM</sub> |             | V <sub>OH</sub>         | V <sub>OL</sub>         |  |

|------------------|-------------|-----------------|-------------|-------------|-----------------------------------|------------|------------|------------|-------------------|-------------|-------------------------|-------------------------|--|

| Attribute        | Min<br>(mV) | Typ<br>(mV)     | Max<br>(mV) | Min<br>(mV) | Max<br>(mV)                       | Min<br>(V) | Тур<br>(V) | Max<br>(V) | Min<br>(mV)       | Max<br>(mV) | Min<br>(V)              | Max<br>(V)              |  |

| LVDS_25          | 250         | 350             | 450         | -           | -                                 | 1.125      | —          | 1.375      | -                 | -           | -                       | —                       |  |

| BLVDS_25         | 250         | 350             | 450         | _           | -                                 | -          | 1.20       | -          | -                 | _           | -                       | -                       |  |

| MINI_LVDS_25     | 300         | -               | 600         | -           | 50                                | 1.0        | -          | 1.4        | -                 | 50          | -                       | -                       |  |

| RSDS_25          | 100         | -               | 400         | _           | -                                 | 1.1        | -          | 1.4        | -                 | _           | -                       | -                       |  |

| DIFF_HSTL_I_18   | _           | -               | -           | -           | -                                 | -          | -          | -          | -                 | -           | $V_{CCO} - 0.4$         | 0.4                     |  |

| DIFF_HSTL_III_18 | _           | -               | -           | -           | -                                 | -          | -          | -          | -                 | _           | $V_{CCO} - 0.4$         | 0.4                     |  |

| DIFF_SSTL18_I    | _           | -               | -           | -           | -                                 | -          | -          | -          | -                 | -           | V <sub>TT</sub> + 0.475 | V <sub>TT</sub> – 0.475 |  |

| DIFF_SSTL2_I     | _           | —               | Ι           | -           | -                                 | -          | -          | -          | -                 | —           | V <sub>TT</sub> + 0.61  | V <sub>TT</sub> – 0.61  |  |

#### Notes:

1. The numbers in this table are based on the conditions set forth in Table 77 and Table 82.

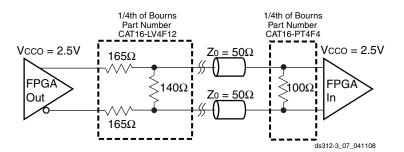

Output voltage measurements for all differential standards are made with a termination resistor (R<sub>T</sub>) of 100Ω across the N and P pins of the differential signal pair. The exception is for BLVDS, shown in Figure 71.

3. At any given time, no more than two of the following differential output standards may be assigned to an I/O bank: LVDS\_25, RSDS\_25, MINI\_LVDS\_25

Figure 71: External Termination Resistors for BLVDS Transmitter and BLVDS Receiver

#### Table 94: Output Timing Adjustments for IOB

| Convert O<br>LVCMOS25 wi<br>Fast Slew Ra<br>Signal Standa | ith 12mA I<br>te to the F | Drive and ollowing | Adjus<br>Bel | the<br>tment<br>ow<br>Grade | Units |  |

|-----------------------------------------------------------|---------------------------|--------------------|--------------|-----------------------------|-------|--|

| Signal Standa                                             |                           |                    | -5           | -4                          | -     |  |

| Single-Ended                                              | Standards                 | 6                  |              |                             |       |  |

| LVTTL                                                     | Slow                      | 2 mA               | 5.20         | 5.41                        | ns    |  |

|                                                           |                           | 4 mA               | 2.32         | 2.41                        | ns    |  |

|                                                           |                           | 6 mA               | 1.83         | 1.90                        | ns    |  |

|                                                           |                           | 8 mA               | 0.64         | 0.67                        | ns    |  |

|                                                           |                           | 12 mA              | 0.68         | 0.70                        | ns    |  |

|                                                           |                           | 16 mA              | 0.41         | 0.43                        | ns    |  |

|                                                           | Fast                      | 2 mA               | 4.80         | 5.00                        | ns    |  |

|                                                           |                           | 4 mA               | 1.88         | 1.96                        | ns    |  |

|                                                           |                           | 6 mA               | 1.39         | 1.45                        | ns    |  |

|                                                           |                           | 8 mA               | 0.32         | 0.34                        | ns    |  |

|                                                           |                           | 12 mA              | 0.28         | 0.30                        | ns    |  |

|                                                           |                           | 16 mA              | 0.28         | 0.30                        | ns    |  |

| VCMOS33                                                   | Slow                      | 2 mA               | 5.08         | 5.29                        | ns    |  |

|                                                           |                           | 4 mA               | 1.82         | 1.89                        | ns    |  |

|                                                           |                           | 6 mA               | 1.00         | 1.04                        | ns    |  |

|                                                           |                           | 8 mA               | 0.66         | 0.69                        | ns    |  |

|                                                           |                           | 12 mA              | 0.40         | 0.42                        | ns    |  |

|                                                           |                           | 16 mA              | 0.41         | 0.43                        | ns    |  |

|                                                           | Fast                      | 2 mA               | 4.68         | 4.87                        | ns    |  |

|                                                           |                           | 4 mA               | 1.46         | 1.52                        | ns    |  |

|                                                           |                           | 6 mA               | 0.38         | 0.39                        | ns    |  |

|                                                           |                           | 8 mA               | 0.33         | 0.34                        | ns    |  |

|                                                           |                           | 12 mA              | 0.28         | 0.30                        | ns    |  |

|                                                           |                           | 16 mA              | 0.28         | 0.30                        | ns    |  |

| LVCMOS25                                                  | Slow                      | 2 mA               | 4.04         | 4.21                        | ns    |  |

|                                                           |                           | 4 mA               | 2.17         | 2.26                        | ns    |  |

|                                                           |                           | 6 mA               | 1.46         | 1.52                        | ns    |  |

|                                                           |                           | 8 mA               | 1.04         | 1.08                        | ns    |  |

|                                                           |                           | 12 mA              | 0.65         | 0.68                        | ns    |  |

|                                                           | Fast                      | 2 mA               | 3.53         | 3.67                        | ns    |  |

|                                                           |                           | 4 mA               | 1.65         | 1.72                        | ns    |  |

|                                                           |                           | 6 mA               | 0.44         | 0.46                        | ns    |  |

|                                                           |                           | 8 mA               | 0.20         | 0.21                        | ns    |  |

|                                                           |                           | 12 mA              | 0            | 0                           | ns    |  |

### Table 94: Output Timing Adjustments for IOB (Cont'd)

| Convert Ou<br>LVCMOS25 wit<br>Fast Slew Rate | h 12mA [ | Drive and | Adjus<br>Bel | the<br>tment<br>low | Units |

|----------------------------------------------|----------|-----------|--------------|---------------------|-------|

| Signal Standa                                |          |           | Speed        | Grade               |       |

|                                              |          |           | -5           | -4                  |       |

| LVCMOS18                                     | Slow     | 2 mA      | 5.03         | 5.24                | ns    |

|                                              |          | 4 mA      | 3.08         | 3.21                | ns    |

|                                              |          | 6 mA      | 2.39         | 2.49                | ns    |

|                                              |          | 8 mA      | 1.83         | 1.90                | ns    |

|                                              | Fast     | 2 mA      | 3.98         | 4.15                | ns    |

|                                              |          | 4 mA      | 2.04         | 2.13                | ns    |

|                                              |          | 6 mA      | 1.09         | 1.14                | ns    |

|                                              |          | 8 mA      | 0.72         | 0.75                | ns    |

| LVCMOS15                                     | Slow     | 2 mA      | 4.49         | 4.68                | ns    |

|                                              |          | 4 mA      | 3.81         | 3.97                | ns    |

|                                              |          | 6 mA      | 2.99         | 3.11                | ns    |

|                                              | Fast     | 2 mA      | 3.25         | 3.38                | ns    |

|                                              |          | 4 mA      | 2.59         | 2.70                | ns    |

|                                              |          | 6 mA      | 1.47         | 1.53                | ns    |

| LVCMOS12                                     | Slow     | 2 mA      | 6.36         | 6.63                | ns    |

|                                              | Fast     | 2 mA      | 4.26         | 4.44                | ns    |

| HSTL_I_18                                    | L        | L         | 0.33         | 0.34                | ns    |

| HSTL_III_18                                  |          |           | 0.53         | 0.55                | ns    |

| PCI33_3                                      |          |           | 0.44         | 0.46                | ns    |

| PCI66_3                                      |          |           | 0.44         | 0.46                | ns    |

| SSTL18_I                                     |          |           | 0.24         | 0.25                | ns    |

| SSTL2_I                                      |          |           | -0.20        | -0.20               | ns    |

| Differential Sta                             | Indards  |           |              |                     |       |

| LVDS_25                                      |          |           | -0.55        | -0.55               | ns    |

| BLVDS_25                                     |          |           | 0.04         | 0.04                | ns    |

| MINI_LVDS_25                                 |          |           | -0.56        | -0.56               | ns    |

| LVPECL_25                                    | Input    | Only      | ns           |                     |       |

| RSDS_25                                      |          |           | -0.48        | -0.48               | ns    |

| DIFF_HSTL_I_                                 | 18       |           | 0.42         | 0.42                | ns    |

| DIFF_HSTL_III                                | _18      |           | 0.53         | 0.55                | ns    |

| DIFF_SSTL18_                                 | I        |           | 0.40         | 0.40                | ns    |

| DIFF_SSTL2_I                                 |          |           | 0.44         | 0.44                | ns    |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 95 and are based on the operating conditions set forth in Table 77, Table 80, and Table 82.

- 2. These adjustments are used to convert output- and three-state-path times originally specified for the LVCMOS25 standard with 12 mA drive and Fast slew rate to times that correspond to other signal standards. Do not adjust times that measure when outputs go into a high-impedance state.

### Phase Shifter (PS)

#### Table 108: Recommended Operating Conditions for the PS in Variable Phase Mode

|                                     |                                                       |     | Grade |     |     |       |

|-------------------------------------|-------------------------------------------------------|-----|-------|-----|-----|-------|

| Symbol                              | Description                                           | -   | 5     | -4  |     | Units |

|                                     |                                                       | Min | Мах   | Min | Max |       |

| Operating Frequ                     | iency Ranges                                          |     |       |     |     |       |

| PSCLK_FREQ<br>(F <sub>PSCLK</sub> ) | Frequency for the PSCLK input                         | 1   | 167   | 1   | 167 | MHz   |

| Input Pulse Req                     | uirements                                             |     | •     | •   | -   |       |

| PSCLK_PULSE                         | PSCLK pulse width as a percentage of the PSCLK period | 40% | 60%   | 40% | 60% | -     |

#### Table 109: Switching Characteristics for the PS in Variable Phase Mode

| Symbol                   | Description                                                                                               | Equa                 | ation                                           | Units |

|--------------------------|-----------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------|-------|

| Phase Shifting Range     |                                                                                                           |                      |                                                 |       |

| MAX_STEPS <sup>(2)</sup> | Maximum allowed number of DCM_DELAY_STEP steps<br>for a given CLKIN clock period, where $T = CLKIN$ clock | CLKIN < 60 MHz       | ±[INTEGER(10 ●<br>(T <sub>CLKIN</sub> – 3 ns))] | steps |

|                          | period in ns. If using CLKIN_DIVIDE_BY_2 = TRUE, double the effective clock period. <sup>(3)</sup>        | CLKIN ≥ 60 MHz       | ±[INTEGER(15 ●<br>(T <sub>CLKIN</sub> – 3 ns))] | steps |

| FINE_SHIFT_RANGE_MIN     | Minimum guaranteed delay for variable phase shifting                                                      | ±[MAX_S<br>DCM_DELAY | STEPS •<br>′_STEP_MIN]                          | ns    |

| FINE_SHIFT_RANGE_MAX     | Maximum guaranteed delay for variable phase shifting                                                      | ±[MAX_9<br>DCM_DELAY | STEPS •<br>_STEP_MAX]                           | ns    |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 77 and Table 108.

- 2. The maximum variable phase shift range, MAX\_STEPS, is only valid when the DCM is has no initial fixed phase shifting, i.e., the PHASE\_SHIFT attribute is set to 0.

- 3. The DCM\_DELAY\_STEP values are provided at the bottom of Table 105.

### **Miscellaneous DCM Timing**

#### Table 110: Miscellaneous DCM Timing

| Symbol                             | Description                                                                                                                                   | Min | Max | Units           |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|

| DCM_RST_PW_MIN <sup>(1)</sup>      | Minimum duration of a RST pulse width                                                                                                         | 3   | -   | CLKIN<br>cycles |

| DCM_RST_PW_MAX <sup>(2)</sup>      | Maximum duration of a RST pulse width                                                                                                         | N/A | N/A | seconds         |

| DCM_CONFIG_LAG_TIME <sup>(3)</sup> | Maximum duration from $V_{\rm CCINT}$ applied to FPGA configuration successfully completed (DONE pin goes High) and clocks applied to DCM DLL | N/A | N/A | minutes         |

#### Notes:

1. This limit only applies to applications that use the DCM DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV). The DCM DFS outputs (CLKFX, CLKFX180) are unaffected.

- 2. This specification is equivalent to the Virtex-4 DCM\_RESET specification. This specification does not apply for Spartan-3E FPGAs.

- 3. This specification is equivalent to the Virtex-4 TCONFIG specification. This specification does not apply for Spartan-3E FPGAs.

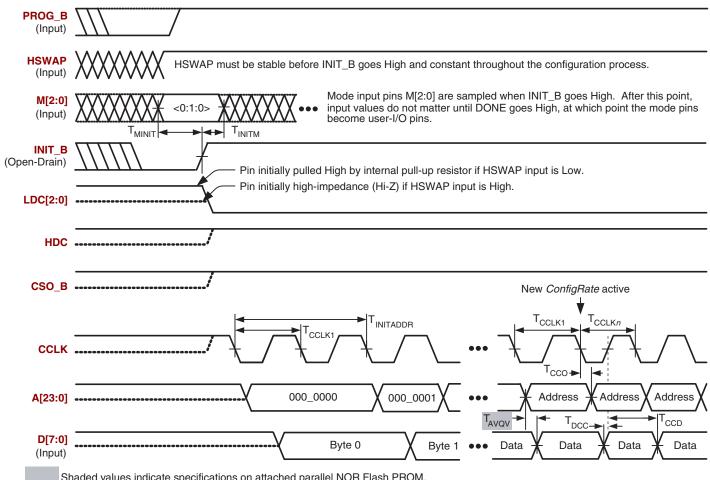

## Byte Peripheral Interface (BPI) Configuration Timing

Shaded values indicate specifications on attached parallel NOR Flash PROM.

DS312-3\_08\_032409

#### Figure 77: Waveforms for Byte-wide Peripheral Interface (BPI) Configuration (BPI-DN mode shown)

| Table | 120: Timing for Byte-wide | <b>Peripheral Interface</b> | (BPI) Configuration Mode |

|-------|---------------------------|-----------------------------|--------------------------|

|       |                           |                             |                          |

| Symbol                | Description                                                                              |                               | Minimum | Maximum      | Units                        |

|-----------------------|------------------------------------------------------------------------------------------|-------------------------------|---------|--------------|------------------------------|

| T <sub>CCLK1</sub>    | Initial CCLK clock period                                                                |                               |         | ee Table 112 |                              |

| T <sub>CCLKn</sub>    | CCLK clock period after FPGA loads ConfigRate setting                                    |                               | S       | ee Table 112 |                              |

| T <sub>MINIT</sub>    | Setup time on CSI_B, RDWR_B, and M[2:0] mode pins before the rising edge of INIT_B       |                               |         | -            | ns                           |

| T <sub>INITM</sub>    | Hold time on CSI_B, RDWR_B, and M[2:0] mode pins after the rising edge of INIT_B         |                               |         | -            | ns                           |

| T <sub>INITADDR</sub> | Minimum period of initial A[23:0] address cycle; LDC[2:0] and HDC are asserted and valid | BPI-UP:<br>(M[2:0] = <0:1:0>) | 5       | 5            | T <sub>CCLK1</sub><br>cycles |

|                       |                                                                                          | BPI-DN:<br>(M[2:0] = <0:1:1>) | 2       | 2            |                              |

| T <sub>CCO</sub>      | Address A[23:0] outputs valid after CCLK falling edge                                    |                               | S       | ee Table 116 |                              |

| T <sub>DCC</sub>      | Setup time on D[7:0] data inputs before CCLK rising edge                                 |                               | S       | ee Table 116 |                              |

| T <sub>CCD</sub>      | Hold time on D[7:0] data inputs after CCLK rising edge                                   |                               | S       | ee Table 116 |                              |

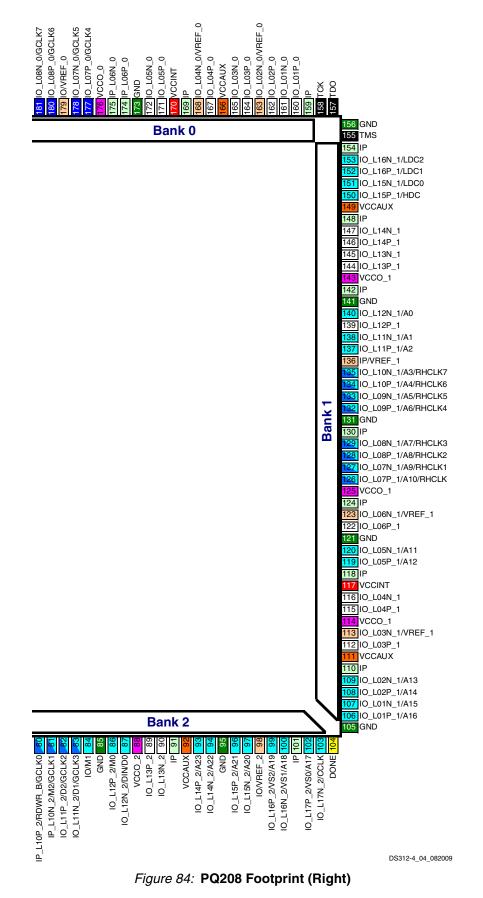

## Spartan-3 FPGA Family: Pinout Descriptions

DS312 (4.0) October 29, 2012

#### **Product Specification**

## Introduction

This section describes the various pins on a Spartan®-3E FPGA and how they connect within the supported component packages.

## **Pin Types**

Most pins on a Spartan-3E FPGA are general-purpose, user-defined I/O pins. There are, however, up to 11 different functional types of pins on Spartan-3E packages, as outlined in Table 124. In the package footprint drawings that follow, the individual pins are color-coded according to pin type as in the table.

| Type / Color<br>Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin Name(s) in Type <sup>(1)</sup>                                                                                                                                             |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O                  | Unrestricted, general-purpose user-I/O pin. Most pins can be paired together to form differential I/Os.                                                                                                                                                                                                                                                                                                                                                                                                                           | IO<br>IO_Lxxy_#                                                                                                                                                                |

| INPUT                | Unrestricted, general-purpose input-only pin. This pin does not have an output structure, differential termination resistor, or PCI clamp diode.                                                                                                                                                                                                                                                                                                                                                                                  | IP<br>IP_Lxxy_#                                                                                                                                                                |

| DUAL                 | Dual-purpose pin used in some configuration modes during the configuration<br>process and then usually available as a user I/O after configuration. If the pin is not<br>used during configuration, this pin behaves as an I/O-type pin. Some of the<br>dual-purpose pins are also shared with bottom-edge global (GCLK) or right-half<br>(RHCLK) clock inputs. See the Configuration section in Module 2 for additional<br>information on these signals.                                                                         | M[2:0]<br>HSWAP<br>CCLK<br>MOSI/CSI_B<br>D[7:1]<br>D0/DIN<br>CSO_B<br>RDWR_B<br>BUSY/DOUT<br>INIT_B<br>A[23:20]<br>A19/VS2<br>A18/VS1<br>A17/VS0<br>A[16:0]<br>LDC[2:0]<br>HDC |

| VREF                 | Dual-purpose pin that is either a user-I/O pin or Input-only pin, or, along with all other VREF pins in the same bank, provides a reference voltage input for certain I/O standards. If used for a reference voltage within a bank, all VREF pins within the bank must be connected.                                                                                                                                                                                                                                              | IP/VREF_#<br>IP_Lxxy_#/VREF_#<br>IO/VREF_#<br>IO_Lxxy_#/VREF_#                                                                                                                 |

| CLK                  | Either a user-I/O pin or Input-only pin, or an input to a specific clock buffer driver.<br>Every package has 16 global clock inputs that optionally clock the entire device. The<br>RHCLK inputs optionally clock the right-half of the device. The LHCLK inputs<br>optionally clock the left-half of the device. Some of the clock pins are shared with the<br>dual-purpose configuration pins and are considered DUAL-type. See the Clocking<br>Infrastructure section in Module 2 for additional information on these signals. | IO_Lxxy_#/GCLK[15:10, 7:2]<br>IP_Lxxy_#/GCLK[9:8, 1:0]<br>IO_Lxxy_#/LHCLK[7:0]<br>IO_Lxxy_#/RHCLK[7:0]                                                                         |

| CONFIG               | Dedicated configuration pin. Not available as a user-I/O pin. Every package has two dedicated configuration pins. These pins are powered by VCCAUX. See the Configuration section in Module 2 for details.                                                                                                                                                                                                                                                                                                                        | DONE, PROG_B                                                                                                                                                                   |

| JTAG                 | Dedicated JTAG pin. Not available as a user-I/O pin. Every package has four dedicated JTAG pins. These pins are powered by VCCAUX.                                                                                                                                                                                                                                                                                                                                                                                                | TDI, TMS, TCK, TDO                                                                                                                                                             |

| GND                  | Dedicated ground pin. The number of GND pins depends on the package used. All must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                  | GND                                                                                                                                                                            |

#### Table 124: Types of Pins on Spartan-3E FPGAs

© Copyright 2005–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

## Package Thermal Characteristics

The power dissipated by an FPGA application has implications on package selection and system design. The power consumed by a Spartan-3E FPGA is reported using either the <u>XPower Estimator</u> or the <u>XPower Analyzer</u> calculator integrated in the Xilinx ISE® development software. Table 130 provides the thermal characteristics for the various Spartan-3E package offerings.

The junction-to-case thermal resistance  $(\theta_{JC})$  indicates the difference between the temperature measured on the

package body (case) and the die junction temperature per watt of power consumption. The junction-to-board ( $\theta_{JB}$ ) value similarly reports the difference between the board and junction temperature. The junction-to-ambient ( $\theta_{JA}$ ) value reports the temperature difference per watt between the ambient environment and the junction temperature. The  $\theta_{JA}$ value is reported at different air velocities, measured in linear feet per minute (LFM). The Still Air (0 LFM) column shows the  $\theta_{JA}$  value in a system without a fan. The thermal resistance drops with increasing air flow.

| Device    | Package | Junction-to-Case Junction-to-Board | Junction-to-Board  | Junction-to-Ambient (θ <sub>JA</sub> )<br>at Different Air Flows |         |         |         | Units   |

|-----------|---------|------------------------------------|--------------------|------------------------------------------------------------------|---------|---------|---------|---------|

|           | Раскаде | (θ <sub>JC</sub> )                 | (θ <sub>JB</sub> ) | Still Air<br>(0 LFM)                                             | 250 LFM | 500 LFM | 750 LFM | Units   |

| XC3S100E  |         | 13.0                               | 30.9               | 49.0                                                             | 40.7    | 37.9    | 37.0    | °C/Watt |

| XC3S250E  | VQ100   | 11.0                               | 25.9               | 43.3                                                             | 36.0    | 33.6    | 32.7    | °C/Watt |

| XC3S500E  |         | 9.8                                |                    | 40.0                                                             | 33.3    | 31.0    | 30.2    | °C/Watt |

| XC3S100E  |         | 19.3                               | 42.0               | 62.1                                                             | 55.3    | 52.8    | 51.2    | °C/Watt |

| XC3S250E  | CP132   | 11.8                               | 28.1               | 48.3                                                             | 41.8    | 39.5    | 38.0    | °C/Watt |

| XC3S500E  |         | 8.5                                | 21.3               | 41.5                                                             | 35.2    | 32.9    | 31.5    | °C/Watt |

| XC3S100E  | T0144   | 8.2                                | 31.9               | 52.1                                                             | 40.5    | 34.6    | 32.5    | °C/Watt |

| XC3S250E  | TQ144   | 7.2                                | 25.7               | 37.6                                                             | 29.2    | 25.0    | 23.4    | °C/Watt |

| XC3S250E  |         | 9.8                                | 29.0               | 37.0                                                             | 27.3    | 24.1    | 22.4    | °C/Watt |

| XC3S500E  | PQ208   | 8.5                                | 26.8               | 36.1                                                             | 26.6    | 23.6    | 21.8    | °C/Watt |

| XC3S250E  |         | 12.4                               | 27.7               | 35.8                                                             | 29.3    | 28.4    | 28.1    | °C/Watt |

| XC3S500E  | FT256   | 9.6                                | 22.2               | 31.1                                                             | 25.0    | 24.0    | 23.6    | °C/Watt |

| XC3S1200E |         | 6.5                                | 16.4               | 26.2                                                             | 20.5    | 19.3    | 18.9    | °C/Watt |

| XC3S500E  |         | 9.8                                | 15.6               | 26.1                                                             | 20.6    | 19.4    | 18.6    | °C/Watt |

| XC3S1200E | FG320   | 8.2                                | 12.5               | 23.0                                                             | 17.7    | 16.4    | 15.7    | °C/Watt |

| XC3S1600E |         | 7.1                                | 10.6               | 21.1                                                             | 15.9    | 14.6    | 13.8    | °C/Watt |

| XC3S1200E | FC 400  | 7.5                                | 12.4               | 22.3                                                             | 17.2    | 16.0    | 15.3    | °C/Watt |

| XC3S1600E | FG400   | 6.0                                | 10.4               | 20.3                                                             | 15.2    | 14.0    | 13.3    | °C/Watt |

| XC3S1600E | FG484   | 5.7                                | 9.4                | 18.8                                                             | 12.5    | 11.3    | 10.8    | °C/Watt |

#### Table 130: Spartan-3E Package Thermal Characteristics

### Table 133: CP132 Package Pinout (Cont'd)

| Bank | XC3S100E<br>Pin Name   | XC3S250E<br>XC3S500E<br>Pin Name | CP132 Ball | Туре                                   |

|------|------------------------|----------------------------------|------------|----------------------------------------|

| 2    | N.C. (♠)               | IO_L08P_2/A23                    | N9         | 100E: N.C.<br>Others: DUAL             |

| 2    | N.C. (�)               | IO_L09N_2/A20                    | M10        | 100E: N.C.<br>Others: DUAL             |

| 2    | N.C. (�)               | IO_L09P_2/A21                    | N10        | 100E: N.C.<br>Others: DUAL             |

| 2    | IO_L10N_2/VS1/A18      | IO_L10N_2/VS1/A18                | M11        | DUAL                                   |

| 2    | IO_L10P_2/VS2/A19      | IO_L10P_2/VS2/A19                | N11        | DUAL                                   |

| 2    | IO_L11N_2/CCLK         | IO_L11N_2/CCLK                   | N12        | DUAL                                   |