Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 3688                                                          |

| Number of Logic Elements/Cells | 33192                                                         |

| Total RAM Bits                 | 663552                                                        |

| Number of I/O                  | 250                                                           |

| Number of Gates                | 1600000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 320-BGA                                                       |

| Supplier Device Package        | 320-FBGA (19x19)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1600e-4fg320i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

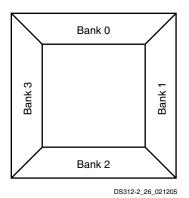

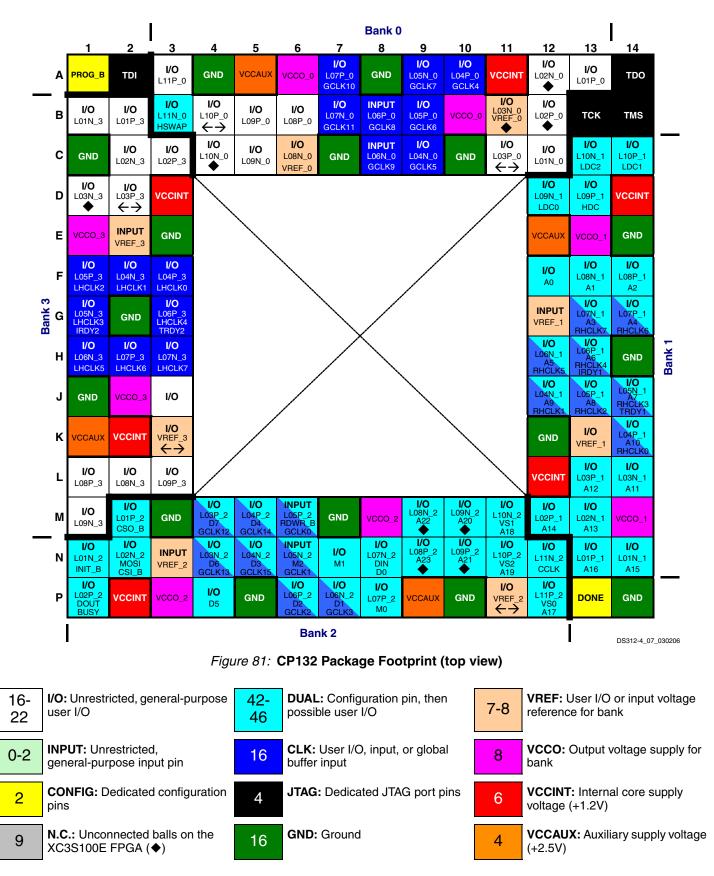

## **IOBs Organized into Banks**

The Spartan-3E architecture organizes IOBs into four I/O banks as shown in Figure 13. Each bank maintains separate V<sub>CCO</sub> and V<sub>REF</sub> supplies. The separate supplies allow each bank to independently set V<sub>CCO</sub>. Similarly, the V<sub>REF</sub> supplies can be set for each bank. Refer to Table 6 and Table 7 for V<sub>CCO</sub> and V<sub>REF</sub> requirements.

When working with Spartan-3E devices, most of the differential I/O standards are compatible and can be combined within any given bank. Each bank can support any two of the following differential standards: LVDS\_25 outputs, MINI\_LVDS\_25 outputs, and RSDS\_25 outputs. As an example, LVDS\_25 outputs, RSDS\_25 outputs, and any other differential inputs while using on-chip differential termination are a valid combination. A combination not allowed is a single bank with LVDS\_25 outputs.

Figure 13: Spartan-3E I/O Banks (top view)

## I/O Banking Rules

When assigning I/Os to banks, these  $V_{CCO}\xspace$  rules must be followed:

- 1. All  $V_{CCO}$  pins on the FPGA must be connected even if a bank is unused.

- 2. All  $V_{CCO}$  lines associated within a bank must be set to the same voltage level.

- 3. The V<sub>CCO</sub> levels used by all standards assigned to the I/Os of any given bank must agree. The Xilinx development software checks for this. Table 6 and Table 7 describe how different standards use the V<sub>CCO</sub> supply.

- 4. If a bank does not have any  $V_{CCO}$  requirements, connect  $V_{CCO}$  to an available voltage, such as 2.5V or 3.3V. Some configuration modes might place additional  $V_{CCO}$  requirements. Refer to Configuration for more information.

If any of the standards assigned to the Inputs of the bank use  $V_{\text{REF}}$  then the following additional rules must be observed:

- 1. All V<sub>BEE</sub> pins must be connected within a bank.

- 2. All V<sub>REF</sub> lines associated with the bank must be set to the same voltage level.

- The V<sub>REF</sub> levels used by all standards assigned to the Inputs of the bank must agree. The Xilinx development software checks for this. Table 6 describes how different standards use the V<sub>REF</sub> supply.

If  $V_{REF}$  is not required to bias the input switching thresholds, all associated  $V_{REF}$  pins within the bank can be used as user I/Os or input pins.

# Package Footprint Compatibility

Sometimes, applications outgrow the logic capacity of a specific Spartan-3E FPGA. Fortunately, the Spartan-3E family is designed so that multiple part types are available in pin-compatible package footprints, as described in Module 4, Pinout Descriptions. In some cases, there are subtle differences between devices available in the same footprint. These differences are outlined for each package, such as pins that are unconnected on one device but connected on another in the same package or pins that are dedicated inputs on one package but full I/O on another. When designing the printed circuit board (PCB), plan for potential future upgrades and package migration.

The Spartan-3E family is not pin-compatible with any previous Xilinx FPGA family.

## **Dedicated Inputs**

Dedicated Inputs are IOBs used only as inputs. Pin names designate a Dedicated Input if the name starts with *IP*, for example, IP or IP\_Lxxx\_x. Dedicated inputs retain the full functionality of the IOB for input functions with a single exception for differential inputs (IP\_Lxxx\_x). For the differential Dedicated Inputs, the on-chip differential termination is not available. To replace the on-chip differential termination, choose a differential pair that supports outputs (IO\_Lxxx\_x) or use an external 100 $\Omega$  termination resistor on the board.

## **ESD** Protection

Clamp diodes protect all device pads against damage from Electro-Static Discharge (ESD) as well as excessive voltage transients. Each I/O has two clamp diodes: one diode extends P-to-N from the pad to  $V_{CCO}$  and a second diode extends N-to-P from the pad to GND. During operation, these diodes are normally biased in the off state. These clamp diodes are always connected to the pad, regardless of the signal standard selected. The presence of diodes limits the ability of Spartan-3E I/Os to tolerate high signal voltages. The V<sub>IN</sub> absolute maximum rating in Table 73 of Module 3, DC and Switching Characteristics specifies the voltage range that I/Os can tolerate.

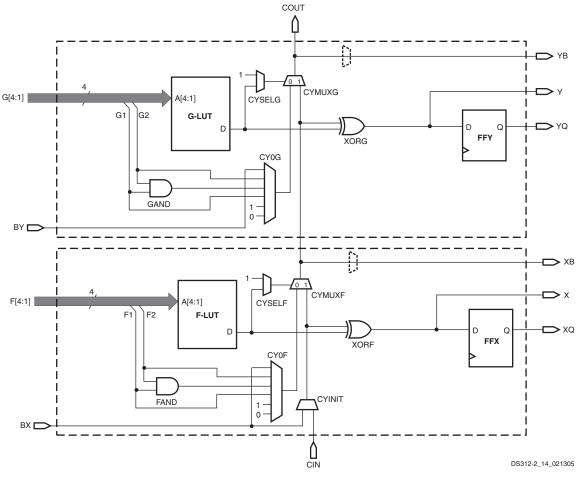

# **Carry and Arithmetic Logic**

For additional information, refer to the "Using Carry and Arithmetic Logic" chapter in UG331.

The carry chain, together with various dedicated arithmetic logic gates, support fast and efficient implementations of math operations. The carry logic is automatically used for most arithmetic functions in a design. The gates and multiplexers of the carry and arithmetic logic can also be used for general-purpose logic, including simple wide Boolean functions.

The carry chain enters the slice as CIN and exits as COUT, controlled by several multiplexers. The carry chain connects directly from one CLB to the CLB above. The carry chain can be initialized at any point from the BX (or BY) inputs.

The dedicated arithmetic logic includes the exclusive-OR gates XORF and XORG (upper and lower portions of the slice, respectively) as well as the AND gates GAND and FAND (upper and lower portions, respectively). These gates work in conjunction with the LUTs to implement efficient arithmetic functions, including counters and multipliers, typically at two bits per slice. See Figure 22 and Table 14.

#### Table 14: Carry Logic Functions

| Function | Description                                                                                                                                                                                                                                                                                                             |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CYINIT   | <ul> <li>Initializes carry chain for a slice. Fixed selection of:</li> <li>CIN carry input from the slice below</li> <li>BX input</li> </ul>                                                                                                                                                                            |  |  |  |

| CY0F     | <ul> <li>Carry generation for bottom half of slice. Fixed selection of:</li> <li>F1 or F2 inputs to the LUT (both equal 1 when a carry is to be generated)</li> <li>FAND gate for multiplication</li> <li>BX input for carry initialization</li> <li>Fixed 1 or 0 input for use as a simple Boolean function</li> </ul> |  |  |  |

www.xilinx.com

## Table 14: Carry Logic Functions (Cont'd)

| Function | Description                                                                                                                                                                                                                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CY0G     | <ul> <li>Carry generation for top half of slice. Fixed selection of:</li> <li>G1 or G2 inputs to the LUT (both equal 1 when a carry is to be generated)</li> <li>GAND gate for multiplication</li> <li>BY input for carry initialization</li> <li>Fixed 1 or 0 input for use as a simple Boolean function</li> </ul> |

| CYMUXF   | <ul> <li>Carry generation or propagation mux for bottom half of slice. Dynamic selection via CYSELF of:</li> <li>CYINIT carry propagation (CYSELF = 1)</li> <li>CY0F carry generation (CYSELF = 0)</li> </ul>                                                                                                        |

| CYMUXG   | <ul> <li>Carry generation or propagation mux for top half of slice. Dynamic selection via CYSELF of:</li> <li>CYMUXF carry propagation (CYSELG = 1)</li> <li>CY0G carry generation (CYSELG = 0)</li> </ul>                                                                                                           |

| CYSELF   | <ul> <li>Carry generation or propagation select for bottom half of slice. Fixed selection of:</li> <li>F-LUT output (typically XOR result)</li> <li>Fixed 1 to always propagate</li> </ul>                                                                                                                           |

| CYSELG   | <ul> <li>Carry generation or propagation select for top half of slice. Fixed selection of:</li> <li>G-LUT output (typically XOR result)</li> <li>Fixed 1 to always propagate</li> </ul>                                                                                                                              |

| XORF     | <ul> <li>Sum generation for bottom half of slice. Inputs from:</li> <li>F-LUT</li> <li>CYINIT carry signal from previous stage</li> <li>Result is sent to either the combinatorial or registered output for the top of the slice.</li> </ul>                                                                         |

| XORG     | <ul> <li>Sum generation for top half of slice. Inputs from:</li> <li>G-LUT</li> <li>CYMUXF carry signal from previous stage</li> <li>Result is sent to either the combinatorial or registered output for the top of the slice.</li> </ul>                                                                            |

| FAND     | <ul> <li>Multiplier partial product for bottom half of slice. Inputs:</li> <li>F-LUT F1 input</li> <li>F-LUT F2 input</li> <li>Result is sent through CY0F to become the carry generate signal into CYMUXF</li> </ul>                                                                                                |

| GAND     | <ul> <li>Multiplier partial product for top half of slice. Inputs:</li> <li>G-LUT G1 input</li> <li>G-LUT G2 input</li> <li>Result is sent through CY0G to become the carry generate signal into CYMUXG</li> </ul>                                                                                                   |

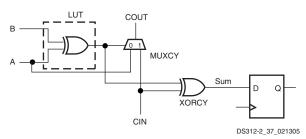

The basic usage of the carry logic is to generate a half-sum in the LUT via an XOR function, which generates or propagates a carry out COUT via the carry mux CYMUXF (or CYMUXG), and then complete the sum with the dedicated XORF (or XORG) gate and the carry input CIN. This structure allows two bits of an arithmetic function in each slice. The CYMUXF (or CYMUXG) can be instantiated using the MUXCY element, and the XORF (or XORG) can be instantiated using the XORCY element.

The FAND (or GAND) gate is used for partial product multiplication and can be instantiated using the MULT\_AND component. Partial products are generated by two-input AND gates and then added. The carry logic is efficient for the adder, but one of the inputs must be outside the LUT as shown in Figure 23.

# Figure 23: Using the MUXCY and XORCY in the Carry Logic

The FAND (or GAND) gate is used to duplicate one of the partial products, while the LUT generates both partial products and the XOR function, as shown in Figure 24.

www.xilinx.com

## Initialization

The CLB storage elements are initialized at power-up, during configuration, by the global GSR signal, and by the individual SR or REV inputs to the CLB. The storage elements can also be re-initialized using the GSR input on the STARTUP\_SPARTAN3E primitive. See Global Controls (STARTUP\_SPARTAN3E).

| Signal | Description                                                                                                                                                                                                                                                                                                                                                             |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR     | Set/Reset input. Forces the storage element into the state specified by the attribute SRHIGH or SRLOW. SRHIGH forces a logic 1 when SR is asserted. SRLOW forces a logic 0. For each slice, set and reset can be set to be synchronous or asynchronous.                                                                                                                 |

| REV    | Reverse of Set/Reset input. A second input (BY)<br>forces the storage element into the opposite state.<br>The reset condition is predominant over the set<br>condition if both are active. Same<br>synchronous/asynchronous setting as for SR.                                                                                                                          |

| GSR    | Global Set/Reset. GSR defaults to active High but can<br>be inverted by adding an inverter in front of the GSR<br>input of the STARTUP_SPARTAN3E element. The<br>initial state after configuration or GSR is defined by a<br>separate INIT0 and INIT1 attribute. By default, setting<br>the SRLOW attribute sets INIT0, and setting the<br>SRHIGH attribute sets INIT1. |

# **Distributed RAM**

For additional information, refer to the "Using Look-Up Tables as Distributed RAM" chapter in UG331.

The LUTs in the SLICEM can be programmed as distributed RAM. This type of memory affords moderate amounts of data buffering anywhere along a data path. One SLICEM LUT stores 16 bits (RAM16). The four LUT inputs F[4:1] or G[4:1] become the address lines labeled A[4:1] in the device model and A[3:0] in the design components, providing a 16x1 configuration in one LUT. Multiple SLICEM LUTs can be combined in various ways to store larger amounts of data, including 16x4, 32x2, or 64x1 configurations in one CLB. The fifth and sixth address lines required for the 32-deep and 64-deep configurations, respectively, are implemented using the BX and BY inputs, which connect to the write enable logic for writing and the F5MUX and F6MUX for reading.

Writing to distributed RAM is always synchronous to the SLICEM clock (WCLK for distributed RAM) and enabled by the SLICEM SR input which functions as the active-High Write Enable (WE). The read operation is asynchronous, and, therefore, during a write, the output initially reflects the old data at the address being written.

The distributed RAM outputs can be captured using the flip-flops within the SLICEM element. The WE write-enable control for the RAM and the CE clock-enable control for the flip-flop are independent, but the WCLK and CLK clock inputs are shared. Because the RAM read operation is asynchronous, the output data always reflects the currently addressed RAM location.

A dual-port option combines two LUTs so that memory access is possible from two independent data lines. The same data is written to both 16x1 memories but they have independent read address lines and outputs. The dual-port function is implemented by cascading the G-LUT address lines, which are used for both read and write, to the F-LUT write address lines (WF[4:1] in Figure 15), and by cascading the G-LUT data input D1 through the DIF\_MUX in Figure 15 and to the D1 input on the F-LUT. One CLB provides a 16x1 dual-port memory as shown in Figure 26.

Any write operation on the D input and any read operation on the SPO output can occur simultaneously with and independently from a read operation on the second read-only port, DPO.

# Multiplier/Block RAM Interaction

Each multiplier is located adjacent to an 18 Kbit block RAM and shares some interconnect resources. Configuring an 18 Kbit block RAM for 36-bit wide data (512 x 36 mode) prevents use of the associated dedicated multiplier. The upper 16 bits of the 'A' multiplicand input are shared with the upper 16 bits of the block RAM's Port A Data input. Similarly, the upper 16 bits of the 'B' multiplicand input are shared with Port B's data input. See also Figure 48, page 62.

Table 27 defines each port of the MULT18X18SIO primitive.

## Table 27: MULT18X18SIO Embedded Multiplier Primitives Description

| Signal Name | Direction | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A[17:0]     | Input     | The primary 18-bit two's complement value for multiplication. The block multiplies by this value asynchronously if the optional AREG and PREG registers are omitted. When AREG and/or PREG are used, the value provided on this port is qualified by the rising edge of CLK, subject to the appropriate register controls.                                                                                                                                                                                                                                                                                            |  |  |  |

| B[17:0]     | Input     | The second 18-bit two's complement value for multiplication if the B_INPUT attribute is set to DIRECT. The block multiplies by this value asynchronously if the optional BREG and PREG registers are omitted. When BREG and/or PREG are used, the value provided on this port is qualified by the rising edge of CLK, subject to the appropriate register controls.                                                                                                                                                                                                                                                   |  |  |  |

| BCIN[17:0]  | Input     | The second 18-bit two's complement value for multiplication if the B_INPUT attribute is set to CASCADE. The block multiplies by this value asynchronously if the optional BREG and PREG registers are omitted. When BREG and/or PREG are used, the value provided on this port is qualified by the rising edge of CLK, subject to the appropriate register controls.                                                                                                                                                                                                                                                  |  |  |  |

| P[35:0]     | Output    | The 36-bit two's complement product resulting from the multiplication of the two input values applied to the multiplier. If the optional AREG, BREG and PREG registers are omitted, the output operates asynchronously. Use of PREG causes this output to respond to the rising edge of CLK with the value qualified by CEP and RSTP. If PREG is omitted, but AREG and BREG are used, this output responds to the rising edge of CLK with the value qualified by CEP, RSTA, CEB, and RSTB. If PREG is omitted and only one of AREG or BREG is used, this output responds to both asynchronous and synchronous events. |  |  |  |

| BCOUT[17:0] | Output    | The value being applied to the second input of the multiplier. When the optional BREG register is omitted, this output responds asynchronously in response to changes at the B[17:0] or BCIN[17:0] ports according to the setting of the B_INPUT attribute. If BREG is used, this output responds to the rising edge of CLK with the value qualified by CEB and RSTB.                                                                                                                                                                                                                                                 |  |  |  |

| CEA         | Input     | Clock enable qualifier for the optional AREG register. The value provided on the A[17:0] port is captured by AREG in response to a rising edge of CLK when this signal is High, provided that RSTA is Low.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| RSTA        | Input     | Synchronous reset for the optional AREG register. AREG content is forced to the value zero in response to a rising edge of CLK when this signal is High.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| CEB         | Input     | Clock enable qualifier for the optional BREG register. The value provided on the B[17:0] or BCIN[17:0] port is captured by BREG in response to a rising edge of CLK when this signal is High, provided that RSTB is Low.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| RSTB        | Input     | Synchronous reset for the optional BREG register. BREG content is forced to the value zero response to a rising edge of CLK when this signal is High.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| CEP         | Input     | Clock enable qualifier for the optional PREG register. The value provided on the output of the multiplier port is captured by PREG in response to a rising edge of CLK when this signal is High, provided that RSTP is Low.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| RSTP        | Input     | Synchronous reset for the optional PREG register. PREG content is forced to the value zero in response to a rising edge of CLK when this signal is High.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

#### Notes:

1. The control signals CLK, CEA, RSTA, CEB, RSTB, CEP, and RSTP have the option of inverted polarity.

# **Digital Clock Managers (DCMs)**

For additional information, refer to the "Using Digital Clock Managers (DCMs)" chapter in  $\underline{\text{UG331}}$ .

## **Differences from the Spartan-3 Architecture**

- Spartan-3E FPGAs have two, four, or eight DCMs, depending on device size.

- The variable phase shifting feature functions differently on Spartan-3E FPGAs than from Spartan-3 FPGAs.

- The Spartan-3E DLLs support lower input frequencies, down to 5 MHz. Spartan-3 DLLs support down to 18 MHz.

## Overview

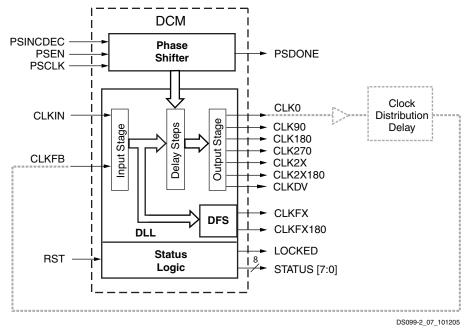

Spartan-3E FPGA Digital Clock Managers (DCMs) provide flexible, complete control over clock frequency, phase shift and skew. To accomplish this, the DCM employs a Delay-Locked Loop (DLL), a fully digital control system that uses feedback to maintain clock signal characteristics with a high degree of precision despite normal variations in operating temperature and voltage. This section provides a fundamental description of the DCM.

The XC3S100E FPGA has two DCMs, one at the top and one at the bottom of the device. The XC3S250E and XC3S500E FPGAs each include four DCMs, two at the top and two at the bottom. The XC3S1200E and XC3S1600E FPGAs contain eight DCMs with two on each edge (see also Figure 45). The DCM in Spartan-3E FPGAs is surrounded by CLBs within the logic array and is no longer located at the top and bottom of a column of block RAM as in the Spartan-3 architecture. The Digital Clock Manager is instantiated within a design using a "DCM" primitive.

The DCM supports three major functions:

- **Clock-skew Elimination:** Clock skew within a system occurs due to the different arrival times of a clock signal at different points on the die, typically caused by the clock signal distribution network. Clock skew increases setup and hold time requirements and increases clock-to-out times, all of which are undesirable in high frequency applications. The DCM eliminates clock skew by phase-aligning the output clock signal that it generates with the incoming clock signal. This mechanism effectively cancels out the clock distribution delays.

- **Frequency Synthesis:** The DCM can generate a wide range of different output clock frequencies derived from the incoming clock signal. This is accomplished by either multiplying and/or dividing the frequency of the input clock signal by any of several different factors.

- **Phase Shifting:** The DCM provides the ability to shift the phase of all its output clock signals with respect to the input clock signal.

Although a single design primitive, the DCM consists of four interrelated functional units: the Delay-Locked Loop (DLL), the Digital Frequency Synthesizer (DFS), the Phase Shifter (PS), and the Status Logic. Each component has its associated signals, as shown in Figure 40.

Figure 40: DCM Functional Blocks and Associated Signals

# **Clocking Infrastructure**

For additional information, refer to the "Using Global Clock Resources" chapter in <u>UG331</u>.

The Spartan-3E clocking infrastructure, shown in Figure 45, provides a series of low-capacitance, low-skew interconnect lines well-suited to carrying high-frequency signals throughout the FPGA. The infrastructure also includes the clock inputs and BUFGMUX clock buffers/multiplexers. The Xilinx Place-and-Route (PAR) software automatically routes high-fanout clock signals using these resources.

## **Clock Inputs**

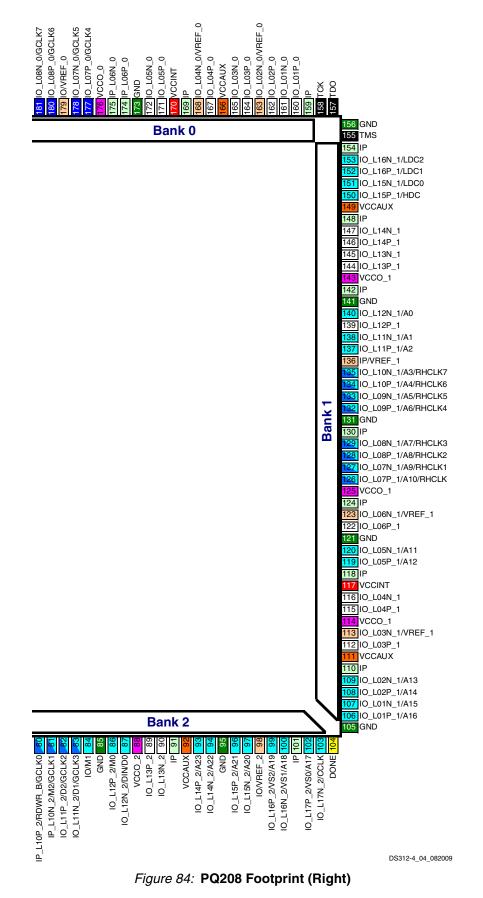

Clock pins accept external clock signals and connect directly to DCMs and BUFGMUX elements. Each Spartan-3E FPGA has:

- 16 Global Clock inputs (GCLK0 through GCLK15) located along the top and bottom edges of the FPGA

- 8 Right-Half Clock inputs (RHCLK0 through RHCLK7) located along the right edge

- 8 Left-Half Clock inputs (LHCLK0 through LHCLK7) located along the left edge

Clock inputs optionally connect directly to DCMs using dedicated connections. Table 30, Table 31, and Table 32 show the clock inputs that best feed a specific DCM within a given Spartan-3E part number. Different Spartan-3E FPGA densities have different numbers of DCMs. The XC3S1200E and XC3S1600E are the only two densities with the left- and right-edge DCMs.

Each clock input is also optionally a user-I/O pin and connects to internal interconnect. Some clock pad pins are input-only pins as indicated in Module 4, Pinout Descriptions.

## Design Note

Avoid using global clock input GCLK1 as it is always shared with the M2 mode select pin. Global clock inputs GCLK0, GCLK2, GCLK3, GCLK12, GCLK13, GCLK14, and GCLK15 have shared functionality in some configuration modes.

## **Clock Buffers/Multiplexers**

Clock Buffers/Multiplexers either drive clock input signals directly onto a clock line (BUFG) or optionally provide a multiplexer to switch between two unrelated, possibly asynchronous clock signals (BUFGMUX).

Each BUFGMUX element, shown in Figure 46, is a 2-to-1 multiplexer. The select line, S, chooses which of the two inputs, I0 or I1, drives the BUFGMUX's output signal, O, as described in Table 40. The switching from one clock to the other is glitch-less, and done in such a way that the output High and Low times are never shorter than the shortest

High or Low time of either input clock. The two clock inputs can be asynchronous with regard to each other, and the S input can change at any time, except for a short setup time prior to the rising edge of the presently selected clock (I0 or I1). This setup time is specified as TGSI in Table 101, page 136. Violating this setup time requirement possibly results in an undefined runt pulse output.

#### Table 40: BUFGMUX Select Mechanism

| S Input | O Output |

|---------|----------|

| 0       | I0 Input |

| 1       | I1 Input |

The BUFG clock buffer primitive drives a single clock signal onto the clock network and is essentially the same element as a BUFGMUX, just without the clock select mechanism. Similarly, the BUFGCE primitive creates an enabled clock buffer using the BUFGMUX select mechanism.

The I0 and I1 inputs to an BUFGMUX element originate from clock input pins, DCMs, or Double-Line interconnect, as shown in Figure 46. As shown in Figure 45, there are 24 BUFGMUX elements distributed around the four edges of the device. Clock signals from the four BUFGMUX elements at the top edge and the four at the bottom edge are truly global and connect to all clocking quadrants. The eight left-edge BUFGMUX elements only connect to the two clock quadrants in the left half of the device. Similarly, the eight right-edge BUFGMUX elements only connect to the right half of the device.

BUFGMUX elements are organized in pairs and share I0 and I1 connections with adjacent BUFGMUX elements from a common clock switch matrix as shown in Figure 46. For example, the input on I0 of one BUFGMUX is also a shared input to I1 of the adjacent BUFGMUX.

The clock switch matrix for the left- and right-edge BUFGMUX elements receive signals from any of the three following sources: an LHCLK or RHCLK pin as appropriate, a Double-Line interconnect, or a DCM in the XC3S1200E and XC3S1600E devices. W Table 54 shows the connections between the SPI Flash PROM and the FPGA's SPI configuration interface. Each SPI Flash PROM vendor uses slightly different signal naming. The SPI Flash PROM's write protect and hold

controls are not used by the FPGA during configuration. However, the  $\overline{\text{HOLD}}$  pin must be High during the configuration process. The PROM's write protect input must be High in order to write or program the Flash memory.

#### Table 54: Example SPI Flash PROM Connections and Pin Naming

| SPI Flash Pin               | FPGA Connection                                                                                                                                                                                                                                                                   | STMicro | NexFlash | Silicon<br>Storage<br>Technology | Atmel<br>DataFlash |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|----------------------------------|--------------------|

| DATA_IN                     | MOSI                                                                                                                                                                                                                                                                              | D       | DI       | SI                               | SI                 |

| DATA_OUT                    | DIN                                                                                                                                                                                                                                                                               | Q       | DO       | SO                               | SO                 |

| SELECT                      | CSO_B                                                                                                                                                                                                                                                                             | S       | CS       | CE#                              | CS                 |

| CLOCK                       | CCLK                                                                                                                                                                                                                                                                              | С       | CLK      | SCK                              | SCK                |

| WR_PROTECT                  | Not required for FPGA configuration. Must be High<br>to program SPI Flash. Optional connection to<br>FPGA user I/O after configuration.                                                                                                                                           | W       | WP       | WP#                              | WP                 |

| HOLD<br>(see Figure 53)     | Not required for FPGA configuration but must be<br>High during configuration. Optional connection to<br>FPGA user I/O after configuration. Not applicable<br>to Atmel DataFlash.                                                                                                  | HOLD    | HOLD     | HOLD#                            | N/A                |

| RESET<br>(see Figure 54)    | Only applicable to Atmel DataFlash. Not required<br>for FPGA configuration but must be High during<br>configuration. Optional connection to FPGA user<br>I/O after configuration. Do not connect to FPGA's<br>PROG_B as this will prevent direct programming of<br>the DataFlash. | N/A     | N/A      | N/A                              | RESET              |

| RDY/BUSY<br>(see Figure 54) | Only applicable to Atmel DataFlash and only<br>available on certain packages. Not required for<br>FPGA configuration. Output from DataFlash<br>PROM. Optional connection to FPGA user I/O after<br>configuration.                                                                 | N/A     | N/A      | N/A                              | RDY/BUSY           |

The mode select pins, M[2:0], and the variant select pins, VS[2:0] are sampled when the FPGA's INIT\_B output goes High and must be at defined logic levels during this time. After configuration, when the FPGA's DONE output goes High, these pins are all available as full-featured user-I/O pins.

P Similarly, the FPGA's HSWAP pin must be Low to enable pull-up resistors on all user-I/O pins or High to

disable the pull-up resistors. The HSWAP control must remain at a constant logic level throughout FPGA configuration. After configuration, when the FPGA's DONE output goes High, the HSWAP pin is available as full-featured user-I/O pin and is powered by the VCCO\_0 supply.

In a single-FPGA application, the FPGA's DOUT pin is not used but is actively driving during the configuration process.

#### Table 55: Serial Peripheral Interface (SPI) Connections

| Pin Name   | FPGA<br>Direction | Description                                                                                                                                                                                                     | During Configuration                                         | After Configuration |  |

|------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------|--|

| HSWAP<br>P | Input             | <b>User I/O Pull-Up Control</b> . When Low during configuration, enables pull-up resistors in all I/O pins to respective I/O bank V <sub>CCO</sub> input.<br>0: Pull-ups during configuration<br>1: No pull-ups | Drive at valid logic level<br>throughout configuration.      | User I/O            |  |

| M[2:0]     | Input             | <b>Mode Select</b> . Selects the FPGA configuration mode. See Design Considerations for the HSWAP, M[2:0], and VS[2:0] Pins.                                                                                    | M2 = 0, M1 = 0, M0 = 1.<br>Sampled when INIT_B goes<br>High. | User I/O            |  |

support byte-wide data. However, after configuration, the FPGA supports either x8 or x16 modes. In x16 mode, up to eight additional user I/O pins are required for the upper data bits, D[15:8].

Connecting a Spartan-3E FPGA to a x8/x16 Flash PROM is simple, but does require a precaution. Various Flash PROM vendors use slightly different interfaces to support both x8 and x16 modes. Some vendors (Intel, Micron, some STMicroelectronics devices) use a straightforward interface with pin naming that matches the FPGA connections. However, the PROM's A0 pin is wasted in x16 applications and a separate FPGA user-I/O pin is required for the D15 data line. Fortunately, the FPGA A0 pin is still available as a user I/O after configuration, even though it connects to the Flash PROM. Other vendors (AMD, Atmel, Silicon Storage Technology, some STMicroelectronics devices) use a pin-efficient interface but change the function of one pin, called IO15/A-1, depending if the PROM is in x8 or x16 mode. In x8 mode, BYTE# = 0, this pin is the least-significant address line. The A0 address line selects the halfword location. The A-1 address line selects the byte location. When in x16 mode, BYTE# = 1, the IO15/A-1 pin becomes the most-significant data bit, D15 because byte addressing is not required in this mode. Check to see if the Flash PROM has a pin named "IO15/A-1" or "DQ15/A-1". If so, be careful to connect x8/x16 Flash PROMs correctly, as shown in Table 63. Also, remember that the D[14:8] data connections require FPGA user I/O pins but that the D15 data is already connected for the FPGA's A0 pin.

| FPGA Pin | Connection to Flash PROM with<br>IO15/A-1 Pin                                                       | x8 Flash PROM Interface After<br>FPGA Configuration                       | x16 Flash PROM Interface After<br>FPGA Configuration |  |

|----------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------|--|

| LDC2     | BYTE#                                                                                               | Drive LDC2 Low or leave<br>unconnected and tie PROM BYTE#<br>input to GND | Drive LCD2 High                                      |  |

| LDC1     | OE#                                                                                                 | Active-Low Flash PROM<br>output-enable control                            | Active-Low Flash PROM<br>output-enable control       |  |

| LDC0     | CS#                                                                                                 | Active-Low Flash PROM chip-select control                                 | Active-Low Flash PROM chip-select<br>control         |  |

| HDC      | WE#                                                                                                 | Flash PROM write-enable control                                           | Flash PROM write-enable control                      |  |

| A[23:1]  | A[n:0]                                                                                              | A[n:0]                                                                    | A[n:0]                                               |  |

| A0       | IO15/A-1                                                                                            | IO15/A-1 is the least-significant address input                           | IO15/A-1 is the most-significant data line, IO15     |  |

| D[7:0]   | IO[7:0]                                                                                             | IO[7:0]                                                                   | IO[7:0]                                              |  |

| User I/O | Upper data lines IO[14:8] not required<br>unless used as x16 Flash interface after<br>configuration | Upper data lines IO[14:8] not required                                    | IO[14:8]                                             |  |

Table 63: FPGA Connections to Flash PROM with IO15/A-1 Pin

Some x8/x16 Flash PROMs have a long setup time requirement on the BYTE# signal. For the FPGA to configure correctly, the PROM must be in x8 mode with BYTE# = 0 at power-on or when the FPGA's PROG\_B pin is pulsed Low. If required, extend the BYTE# setup time for a 3.3V PROM using an external 680  $\Omega$  pull-down resistor on the FPGA's LDC2 pin or by delaying assertion of the CSI\_B select input to the FPGA.

## **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain, as shown in Figure 59. Use BPI mode (M[2:0] = <0:1:0> or <0:1:1>) for the FPGA connected to the parallel NOR Flash PROM and Slave Parallel mode (M[2:0] = <1:1:0>) for all downstream FPGAs in the daisy-chain. If there are more than two FPGAs in the chain, then last FPGA in the chain can be from any Xilinx FPGA family. However, all intermediate FPGAs located in the

chain between the first and last FPGAs must from either the Spartan-3E or Virtex®-5 FPGA families.

After the master FPGA—the FPGA on the left in the diagram—finishes loading its configuration data from the parallel Flash PROM, the master device continues generating addresses to the Flash PROM and asserts its CSO\_B output Low, enabling the next FPGA in the daisy-chain. The next FPGA then receives parallel configuration data from the Flash PROM. The master FPGA's CCLK output synchronizes data capture.

If HSWAP = 1, an external  $4.7k\Omega$  pull-up resistor must be added on the CSO\_B pin. If HSWAP = 0, no external pull-up is necessary.

## Design Note

BPI mode daisy chain software support is available starting in ISE 8.2i.

http://www.xilinx.com/support/answers/23061.htm

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | During Configuration                                                                                      | After Configuration                                                                                    |

|----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| INIT_B   | Open-drain<br>bidirectional I/O | <b>Initialization Indicator</b> . Active Low.<br>Goes Low at the start of<br>configuration during the Initialization<br>memory clearing process. Released<br>at the end of memory clearing, when<br>mode select pins are sampled. In<br>daisy-chain applications, this signal<br>requires an external 4.7 k $\Omega$ pull-up<br>resistor to VCCO_2.                                                                                                                               | Active during configuration. If<br>CRC error detected during<br>configuration, FPGA drives<br>INIT_B Low. | User I/O. If unused in the<br>application, drive INIT_B<br>High.                                       |

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external 330 $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                     | Low indicates that the FPGA is not yet configured.                                                        | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully configured. |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low. When asserted Low for 500 ns or longer, forces the FPGA to restart its configuration process by clearing configuration memory and resetting the DONE and INIT_B pins once PROG_B returns High. Recommend external 4.7 k $\Omega$ pull-up resistor to 2.5V. Internal pull-up value may be weaker (see Table 78). If driving externally with a 3.3V output, use an open-drain or open-collector driver or use a current limiting series resistor. | Must be High to allow<br>configuration to start.                                                          | Drive PROG_B Low and<br>release to reprogram<br>FPGA.                                                  |

#### Table 65: Slave Parallel Mode Connections (Cont'd)

## **Voltage Compatibility**

W Most Slave Parallel interface signals are within the FPGA's I/O Bank 2, supplied by the VCCO\_2 supply input. The VCCO\_2 voltage can be 1.8V, 2.5V, or 3.3V to match the requirements of the external host, ideally 2.5V. Using 1.8V or 3.3V requires additional design considerations as the DONE and PROG\_B pins are powered by the FPGA's 2.5V V<sub>CCAUX</sub> supply. See <u>XAPP453</u>: *The 3.3V Configuration of Spartan-3 FPGAs* for additional information.

## **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain. Use Slave Parallel mode (M[2:0] = <1:1:0>) for all FPGAs in the daisy-chain. The schematic in Figure 62 is optimized for FPGA downloading and does not support the SelectMAP read interface. The FPGA's RDWR\_B pin must be Low during configuration.

After the lead FPGA is filled with its configuration data, the lead FPGA enables the next FPGA in the daisy-chain by asserting is chip-select output, CSO\_B.

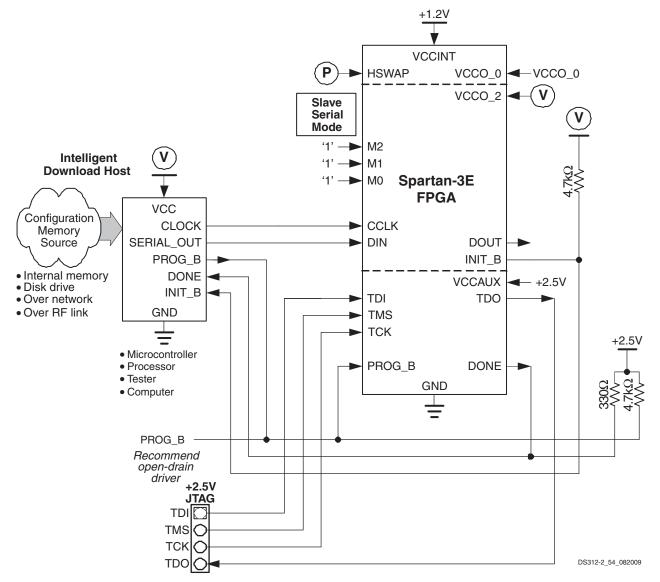

Figure 63: Slave Serial Configuration

The mode select pins, M[2:0], are sampled when the FPGA's INIT\_B output goes High and must be at defined logic levels during this time. After configuration, when the FPGA's DONE output goes High, the mode pins are available as full-featured user-I/O pins.

P Similarly, the FPGA's HSWAP pin must be Low to enable pull-up resistors on all user-I/O pins or High to disable the pull-up resistors. The HSWAP control must remain at a constant logic level throughout FPGA configuration. After configuration, when the FPGA's DONE output goes High, the HSWAP pin is available as full-featured user-I/O pin and is powered by the VCCO\_0 supply.

## Voltage Compatibility

W Most Slave Serial interface signals are within the FPGA's I/O Bank 2, supplied by the VCCO\_2 supply input. The VCCO\_2 voltage can be 3.3V, 2.5V, or 1.8V to match the requirements of the external host, ideally 2.5V. Using 3.3V or 1.8V requires additional design considerations as the DONE and PROG\_B pins are powered by the FPGA's 2.5V V<sub>CCAUX</sub> supply. See <u>XAPP453</u>: *The 3.3V Configuration of Spartan-3 FPGAs* for additional information.

## **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain, as shown in Figure 64. Use Slave Serial mode (M[2:0] = <1:1:>) for all FPGAs in the daisy-chain. After the lead FPGA is filled with its configuration data, the lead

#### Table 95: Test Methods for Timing Measurement at I/Os (Cont'd)

| Signal Standard  | Inputs               |                        | Outputs                |                                   | Inputs and<br>Outputs |                    |

|------------------|----------------------|------------------------|------------------------|-----------------------------------|-----------------------|--------------------|

| (IOSTANDARD)     | V <sub>REF</sub> (V) | V <sub>L</sub> (V)     | V <sub>H</sub> (V)     | <b>R<sub>T</sub> (</b> Ω <b>)</b> | V <sub>T</sub> (V)    | V <sub>M</sub> (V) |

| DIFF_HSTL_I_18   | -                    | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                                | 0.9                   | V <sub>ICM</sub>   |

| DIFF_HSTL_III_18 | -                    | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                                | 1.8                   | V <sub>ICM</sub>   |

| DIFF_SSTL18_I    | -                    | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                                | 0.9                   | V <sub>ICM</sub>   |

| DIFF_SSTL2_I     | -                    | V <sub>REF</sub> – 0.5 | V <sub>REF</sub> + 0.5 | 50                                | 1.25                  | V <sub>ICM</sub>   |

#### Notes:

- 1. Descriptions of the relevant symbols are as follows:

- V<sub>REF</sub> The reference voltage for setting the input switching threshold

- V<sub>ICM</sub> The common mode input voltage

- $V_{\rm M}$  Voltage of measurement point on signal transition

- $V_L$  Low-level test voltage at Input pin

- V<sub>H</sub> High-level test voltage at Input pin

- R<sub>T</sub> Effective termination resistance, which takes on a value of 1MΩ when no parallel termination is required

- V<sub>T</sub> Termination voltage

- 2. The load capacitance (CL) at the Output pin is 0 pF for all signal standards.

- 3. According to the PCI specification.

The capacitive load ( $C_L$ ) is connected between the output and GND. The Output timing for all standards, as published in the speed files and the data sheet, is always based on a  $C_L$  value of zero. High-impedance probes (less than 1 pF) are used for all measurements. Any delay that the test fixture might contribute to test measurements is subtracted from those measurements to produce the final timing numbers as published in the speed files and data sheet.

# Using IBIS Models to Simulate Load Conditions in Application

IBIS models permit the most accurate prediction of timing delays for a given application. The parameters found in the IBIS model (V<sub>REF</sub>, R<sub>REF</sub>, and V<sub>MEAS</sub>) correspond directly with the parameters used in Table 95 (V<sub>T</sub>, R<sub>T</sub>, and V<sub>M</sub>). Do not confuse V<sub>REF</sub> (the termination voltage) from the IBIS model with V<sub>REF</sub> (the input-switching threshold) from the table. A fourth parameter, C<sub>REF</sub> is always zero. The four parameters describe all relevant output test conditions. IBIS models are found in the Xilinx development software as well as at the following link:

http://www.xilinx.com/support/download/index.htm

Delays for a given application are simulated according to its specific load conditions as follows:

- 1. Simulate the desired signal standard with the output driver connected to the test setup shown in Figure 72. Use parameter values  $V_T$ ,  $R_T$ , and  $V_M$  from Table 95.  $C_{\mathsf{REF}}$  is zero.

- 2. Record the time to V<sub>M</sub>.

- 3. Simulate the same signal standard with the output driver connected to the PCB trace with load. Use the appropriate IBIS model (including  $V_{REF}$ ,  $R_{REF}$ ,  $C_{REF}$  and  $V_{MEAS}$  values) or capacitive value to represent the load.

- 4. Record the time to V<sub>MEAS</sub>.

- 5. Compare the results of steps 2 and 4. Add (or subtract) the increase (or decrease) in delay to (or from) the appropriate Output standard adjustment (Table 94) to yield the worst-case delay of the PCB trace.

## Phase Shifter (PS)

#### Table 108: Recommended Operating Conditions for the PS in Variable Phase Mode

|                                     |                                                       |     | Speed Grade |     |     |       |  |  |

|-------------------------------------|-------------------------------------------------------|-----|-------------|-----|-----|-------|--|--|

| Symbol                              | Description                                           | -   | 5           | -4  |     | Units |  |  |

|                                     |                                                       | Min | Мах         | Min | Max | 1     |  |  |

| Operating Frequ                     | iency Ranges                                          |     |             |     |     |       |  |  |

| PSCLK_FREQ<br>(F <sub>PSCLK</sub> ) | Frequency for the PSCLK input                         | 1   | 167         | 1   | 167 | MHz   |  |  |

| Input Pulse Req                     | uirements                                             |     | •           | •   | -   |       |  |  |

| PSCLK_PULSE                         | PSCLK pulse width as a percentage of the PSCLK period | 40% | 60%         | 40% | 60% | -     |  |  |

#### Table 109: Switching Characteristics for the PS in Variable Phase Mode

| Symbol                   | Description                                                                                               | Equa                                 | Units                                           |       |

|--------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------|-------|

| Phase Shifting Range     |                                                                                                           |                                      |                                                 |       |

| MAX_STEPS <sup>(2)</sup> | Maximum allowed number of DCM_DELAY_STEP steps<br>for a given CLKIN clock period, where $T = CLKIN$ clock | CLKIN < 60 MHz                       | ±[INTEGER(10 ●<br>(T <sub>CLKIN</sub> – 3 ns))] | steps |

|                          | period in ns. If using CLKIN_DIVIDE_BY_2 = TRUE, double the effective clock period. <sup>(3)</sup>        | CLKIN ≥ 60 MHz                       | ±[INTEGER(15 ●<br>(T <sub>CLKIN</sub> – 3 ns))] | steps |

| FINE_SHIFT_RANGE_MIN     | Minimum guaranteed delay for variable phase shifting                                                      | ±[MAX_STEPS •<br>DCM_DELAY_STEP_MIN] |                                                 |       |

| FINE_SHIFT_RANGE_MAX     | Maximum guaranteed delay for variable phase shifting                                                      | ±[MAX_STEPS •<br>DCM_DELAY_STEP_MAX] |                                                 |       |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 77 and Table 108.

- 2. The maximum variable phase shift range, MAX\_STEPS, is only valid when the DCM is has no initial fixed phase shifting, i.e., the PHASE\_SHIFT attribute is set to 0.

- 3. The DCM\_DELAY\_STEP values are provided at the bottom of Table 105.

## **Miscellaneous DCM Timing**

#### Table 110: Miscellaneous DCM Timing

| Symbol                             | Description                                                                                                                                   | Min | Max | Units           |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|

| DCM_RST_PW_MIN <sup>(1)</sup>      | Minimum duration of a RST pulse width                                                                                                         | 3   | -   | CLKIN<br>cycles |

| DCM_RST_PW_MAX <sup>(2)</sup>      | Maximum duration of a RST pulse width                                                                                                         | N/A | N/A | seconds         |

| DCM_CONFIG_LAG_TIME <sup>(3)</sup> | Maximum duration from $V_{\rm CCINT}$ applied to FPGA configuration successfully completed (DONE pin goes High) and clocks applied to DCM DLL | N/A | N/A | minutes         |

#### Notes:

1. This limit only applies to applications that use the DCM DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV). The DCM DFS outputs (CLKFX, CLKFX180) are unaffected.

- 2. This specification is equivalent to the Virtex-4 DCM\_RESET specification. This specification does not apply for Spartan-3E FPGAs.

- 3. This specification is equivalent to the Virtex-4 TCONFIG specification. This specification does not apply for Spartan-3E FPGAs.

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/01/05 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11/23/05 | 2.0     | Added AC timing information and additional DC specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 03/22/06 | 3.0     | Upgraded data sheet status to Preliminary. Finalized production timing parameters. All speed grades for all Spartan-3E FPGAs are now Production status using the v1.21 speed files, as shown in Table 84. Expanded description in Note 2, Table 78. Updated pin-to-pin and clock-to-output timing based on final characterization, shown in Table 86. Updated system-synchronous input setup and hold times based on final characterization, shown in Table 87 and Table 88. Updated other I/O timing in Table 90. Provided input and output adjustments for LVPECL_25, DIFF_SSTL and DIFF_HSTL I/O standards that supersede the v1.21 speed file values, in Table 91 and Table 94. Reduced I/O three-state and set/reset delays in Table 93. Added XC3S100E FPGA in CP132 package to Table 96. Increased T <sub>AS</sub> slice flip-flop timing by 100 ps in Table 98. Updated distributed RAM timing in Table 99 and SRL16 timing in Table 100. Updated global clock timing, removed left/right clock buffer limits in Table 101. Updated block RAM timing in Table 103. Added DCM parameters for remainder of Step 0 device; added improved Step 1 DCM performance to Table 104, Table 105, Table 106, and Table 107. Added minimum INIT_B pulse width specification, T <sub>INIT</sub> , in Table 111. Increased data hold time for Slave Parallel mode to 1.0 ns (T <sub>SMCCD</sub> ) in Table 106, and Table 107. Corrected links in Table 118 and Table 120. Added MultiBoot timing specifications to Table 122. |

| 04/07/06 | 3.1     | Improved SSO limits for LVDS_25, MINI_LVDS_25, and RSDS_25 I/O standards in the QFP packages (Table 97). Removed potentially confusing Note 2 from Table 78.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 05/19/06 | 3.2     | Clarified that 100 mV of hysteresis applies to LVCMOS33 and LVCMOS25 I/O standards (Note 4, Table 80). Other minor edits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 05/30/06 | 3.2.1   | Corrected various typos and incorrect links.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11/09/06 | 3.4     | Improved absolute maximum voltage specifications in Table 73, providing additional overshoot allowance. Widened the recommended voltage range for PCI and PCI-X standards in Table 80. Clarified Note 2, Table 83. Improved various timing specifications for v1.26 speed file. Added Table 85 to summarize the history of speed file releases after which time all devices became Production status. Added absolute minimum values for Table 86, Table 92, and Table 93. Updated pin-to-pin setup and hold timing based on default IFD_DELAY_VALUE settings in Table 87, Table 88, and Table 90. Added Table 89 about source-synchronous input capture sample window. Promoted Module 3 to Production status. Synchronized all modules to v3.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 03/16/07 | 3.5     | Based on extensive 90 nm production data, improved (reduced) the maximum quiescent current limits for the $I_{CCINTQ}$ , $I_{CCAUXQ}$ , and $I_{CCOQ}$ specifications in Table 79 by an average of 50%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |