# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 3688                                                          |

| Number of Logic Elements/Cells | 33192                                                         |

| Total RAM Bits                 | 663552                                                        |

| Number of I/O                  | 304                                                           |

| Number of Gates                | 1600000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 400-BGA                                                       |

| Supplier Device Package        | 400-FBGA (21x21)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1600e-4fg400c |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Introduction

As described in Architectural Overview, the Spartan-3E FPGA architecture consists of five fundamental functional elements:

- Input/Output Blocks (IOBs)

- Configurable Logic Block (CLB) and Slice Resources

- Block RAM

- Dedicated Multipliers

- Digital Clock Managers (DCMs)

The following sections provide detailed information on each of these functions. In addition, this section also describes the following functions:

- Clocking Infrastructure

- Interconnect

- Configuration

- Powering Spartan-3E FPGAs

### Input/Output Blocks (IOBs)

For additional information, refer to the "Using I/O Resources" chapter in <u>UG331</u>.

### **IOB** Overview

The Input/Output Block (IOB) provides a programmable, unidirectional or bidirectional interface between a package pin and the FPGA's internal logic. The IOB is similar to that of the Spartan-3 family with the following differences:

- Input-only blocks are added

- Programmable input delays are added to all blocks

- DDR flip-flops can be shared between adjacent IOBs

The unidirectional input-only block has a subset of the full IOB capabilities. Thus there are no connections or logic for an output path. The following paragraphs assume that any reference to output functionality does not apply to the input-only blocks. The number of input-only blocks varies with device size, but is never more than 25% of the total IOB count.

Figure 5 is a simplified diagram of the IOB's internal structure. There are three main signal paths within the IOB: the output path, input path, and 3-state path. Each path has its own pair of storage elements that can act as either registers or latches. For more information, see Storage Element Functions. The three main signal paths are as follows:

The input path carries data from the pad, which is bonded to a package pin, through an optional programmable delay element directly to the I line. After the delay element, there are alternate routes through a pair of storage elements to the IQ1 and IQ2 lines. The IOB outputs I, IQ1, and IQ2 lead to the FPGA's internal logic. The delay element can be set to ensure a hold time of zero (see Input Delay Functions).

- The output path, starting with the O1 and O2 lines, carries data from the FPGA's internal logic through a multiplexer and then a three-state driver to the IOB pad. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements.

- The 3-state path determines when the output driver is high impedance. The T1 and T2 lines carry data from the FPGA's internal logic through a multiplexer to the output driver. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements.

- All signal paths entering the IOB, including those associated with the storage elements, have an inverter option. Any inverter placed on these paths is automatically absorbed into the IOB.

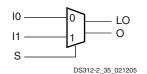

The wide multiplexers can be used by the automatic tools or instantiated in a design using a component such as the F5MUX. The symbol, signals, and function are described in Figure 21, Table 12, and Table 13. The description is similar for the F6MUX, F7MUX, and F8MUX. Each has versions with a general output, local output, or both.

Figure 21: F5MUX with Local and General Outputs

#### Table 12: F5MUX Inputs and Outputs

| Signal | Function                                                                                                                          |

|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| 10     | Input selected when S is Low                                                                                                      |

| 11     | Input selected when S is High                                                                                                     |

| S      | Select input                                                                                                                      |

| LO     | Local Output that connects to the F5 or FX CLB pins,<br>which use local feedback to the FXIN inputs to the<br>FiMUX for cascading |

| 0      | General Output that connects to the general-purpose combinatorial or registered outputs of the CLB                                |

#### Table 13: F5MUX Function

| Inputs |    |    | Outputs |    |  |

|--------|----|----|---------|----|--|

| S      | 10 | l1 | 0       | LO |  |

| 0      | 1  | Х  | 1       | 1  |  |

| 0      | 0  | Х  | 0       | 0  |  |

| 1      | Х  | 1  | 1       | 1  |  |

| 1      | Х  | 0  | 0       | 0  |  |

#### Table 22: Port Aspect Ratios

| Total Data<br>Path Width<br>(w bits) | DI/DO Data<br>Bus Width<br>(w-p bits) <sup>(1)</sup> | DIP/DOP<br>Parity Bus<br>Width (p bits) | ADDR<br>Bus Width<br>(r bits) <sup>(2)</sup> | DI/DO<br>[w-p-1:0] | DIP/DOP<br>[p-1:0] | ADDR<br>[r-1:0] | No. of<br>Addressable<br>Locations (n) <sup>(3)</sup> | Block RAM<br>Capacity<br>(w*n bits) <sup>(4)</sup> |

|--------------------------------------|------------------------------------------------------|-----------------------------------------|----------------------------------------------|--------------------|--------------------|-----------------|-------------------------------------------------------|----------------------------------------------------|

| 1                                    | 1                                                    | 0                                       | 14                                           | [0:0]              | -                  | [13:0]          | 16,384                                                | 16,384                                             |

| 2                                    | 2                                                    | 0                                       | 13                                           | [1:0]              | -                  | [12:0]          | 8,192                                                 | 16,384                                             |

| 4                                    | 4                                                    | 0                                       | 12                                           | [3:0]              | -                  | [11:0]          | 4,096                                                 | 16,384                                             |

| 9                                    | 8                                                    | 1                                       | 11                                           | [7:0]              | [0:0]              | [10:0]          | 2,048                                                 | 18,432                                             |

| 18                                   | 16                                                   | 2                                       | 10                                           | [15:0]             | [1:0]              | [9:0]           | 1,024                                                 | 18,432                                             |

| 36                                   | 32                                                   | 4                                       | 9                                            | [31:0]             | [3:0]              | [8:0]           | 512                                                   | 18,432                                             |

#### Notes:

- 1. The width of the total data path (w) is the sum of the DI/DO bus width (w-p) and any parity bits (p).

- 2. The width selection made for the DI/DO bus determines the number of address lines (r) according to the relationship expressed as: r = 14 - [log(w-p)/log9(2)].

- 3. The number of address lines delimits the total number (n) of addressable locations or depth according to the following equation:  $n = 2^{r}$ .

- 4. The product of w and n yields the total block RAM capacity.

If the data bus width of Port A differs from that of Port B, the block RAM automatically performs a bus-matching function as described in Figure 31. When data is written to a port with a narrow bus and then read from a port with a wide bus, the latter port effectively combines "narrow" words to form "wide" words. Similarly, when data is written into a port with a wide bus and then read from a port with a narrow bus, the latter port divides "wide" words to form "narrow" words. Parity bits are not available if the data port width is configured as x4, x2, or x1. For example, if a x36 data word (32 data, 4 parity) is addressed as two x18 halfwords (16 data, 2 parity), the parity bits associated with each data byte are mapped within the block RAM to the appropriate parity bits. The same effect happens when the x36 data word is mapped as four x9 words.

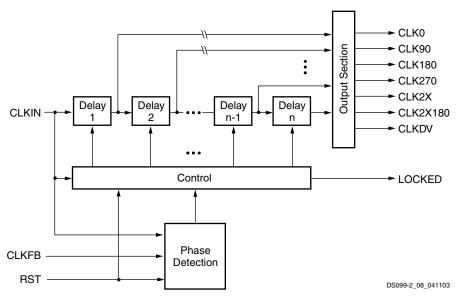

### Delay-Locked Loop (DLL)

The most basic function of the DLL component is to eliminate clock skew. The main signal path of the DLL consists of an input stage, followed by a series of discrete delay elements or *steps*, which in turn leads to an output stage. This path together with logic for phase detection and control forms a system complete with feedback as shown in Figure 41. In Spartan-3E FPGAs, the DLL is implemented using a counter-based delay line. The DLL component has two clock inputs, CLKIN and CLKFB, as well as seven clock outputs, CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV as described in Table 28. The clock outputs drive simultaneously. Signals that initialize and report the state of the DLL are discussed in Status Logic.

Figure 41: Simplified Functional Diagram of DLL

#### Table 28: DLL Signals

| Signal   | Direction | Description                                                                                                                |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------|

| CLKIN    | Input     | Receives the incoming clock signal. See Table 30, Table 31, and Table 32 for optimal external inputs to a DCM.             |

| CLKFB    | Input     | Accepts either CLK0 or CLK2X as the feedback signal. (Set the CLK_FEEDBACK attribute accordingly).                         |

| CLK0     | Output    | Generates a clock signal with the same frequency and phase as CLKIN.                                                       |

| CLK90    | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 90°.                                           |

| CLK180   | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 180°.                                          |

| CLK270   | Output    | Generates a clock signal with the same frequency as CLKIN, phase-shifted by 270°.                                          |

| CLK2X    | Output    | Generates a clock signal with the same phase as CLKIN, and twice the frequency.                                            |

| CLK2X180 | Output    | Generates a clock signal with twice the frequency of CLKIN, and phase-shifted 180° with respect to CLK2X.                  |

| CLKDV    | Output    | Divides the CLKIN frequency by CLKDV_DIVIDE value to generate lower frequency clock signal that is phase-aligned to CLKIN. |

The clock signal supplied to the CLKIN input serves as a reference waveform. The DLL seeks to align the rising-edge of feedback signal at the CLKFB input with the rising-edge of CLKIN input. When eliminating clock skew, the common approach to using the DLL is as follows: The CLK0 signal is passed through the clock distribution network that feeds all the registers it synchronizes. These registers are either

internal or external to the FPGA. After passing through the clock distribution network, the clock signal returns to the DLL via a feedback line called CLKFB. The control block inside the DLL measures the phase error between CLKFB and CLKIN. This phase error is a measure of the clock skew that the clock distribution network introduces. The control block activates the appropriate number of delay steps to

### **DLL Clock Output and Feedback Connections**

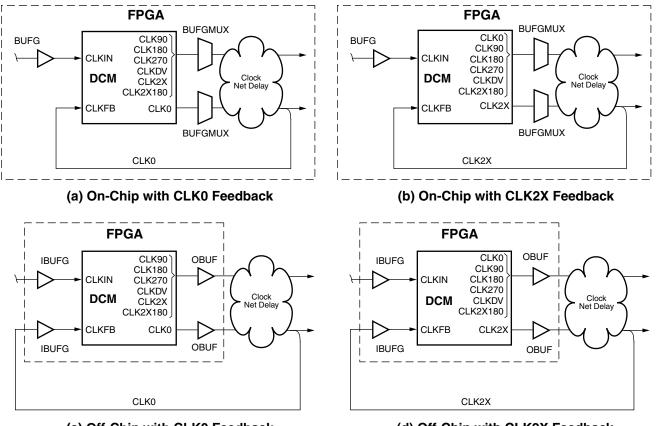

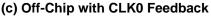

As many as four of the nine DCM clock outputs can simultaneously drive four of the BUFGMUX buffers on the same die edge. All DCM clock outputs can simultaneously drive general routing resources, including interconnect leading to OBUF buffers.

The feedback loop is essential for DLL operation. Either the CLK0 or CLK2X outputs feed back to the CLKFB input via a BUFGMUX global buffer to eliminate the clock distribution delay. The specific BUFGMUX buffer used to feed back the CLK0 or CLK2X signal is ideally one of the BUFGMUX buffers associated with a specific DCM, as shown in Table 30, Table 31, and Table 32.

The feedback path also phase-aligns the other seven DLL outputs: CLK0, CLK90, CLK180, CLK270, CLKDV, CLK2X, or CLK2X180. The CLK\_FEEDBACK attribute value must agree with the physical feedback connection. Use "1X" for CLK0 feedback and "2X" for CLK2X feedback. If the DFS unit is used stand-alone, without the DLL, then no feedback is required and set the CLK\_FEEDBACK attribute to "NONE".

Two basic cases determine how to connect the DLL clock outputs and feedback connections: on-chip synchronization and off-chip synchronization, which are illustrated in Figure 42a through Figure 42d.

In the on-chip synchronization case in Figure 42a and Figure 42b, it is possible to connect any of the DLL's seven output clock signals through general routing resources to the FPGA's internal registers. Either a Global Clock Buffer (BUFG) or a BUFGMUX affords access to the global clock network. As shown in Figure 42a, the feedback loop is created by routing CLK0 (or CLK2X) in Figure 42b to a global clock net, which in turn drives the CLKFB input.

In the off-chip synchronization case in Figure 42c and Figure 42d, CLK0 (or CLK2X) plus any of the DLL's other output clock signals exit the FPGA using output buffers (OBUF) to drive an external clock network plus registers on the board. As shown in Figure 42c, the feedback loop is formed by feeding CLK0 (or CLK2X) in Figure 42d back into the FPGA, then to the DCM's CLKFB input via a Global Buffer Input, specified in Table 30.

(d) Off-Chip with CLK2X Feedback

DS099-2\_09\_082104

Figure 42: Input Clock, Output Clock, and Feedback Connections for the DLL

The connections for the bottom-edge BUFGMUX elements are similar to the top-edge connections (see Figure 46).

🐮 XILINX.

On the left and right edges, only two clock inputs feed each pair of BUFGMUX elements.

Figure 46: Clock Switch Matrix to BUFGMUX Pair Connectivity

### **Quadrant Clock Routing**

The clock routing within the FPGA is quadrant-based, as shown in Figure 45. Each clock quadrant supports eight total clock signals, labeled 'A' through 'H' in Table 41 and Figure 47. The clock source for an individual clock line originates either from a global BUFGMUX element along the top and bottom edges or from a BUFGMUX element along the associated edge, as shown in Figure 47. The clock lines feed the synchronous resource elements (CLBs, IOBs, block RAM, multipliers, and DCMs) within the quadrant.

The four quadrants of the device are:

- Top Right (TR)

- Bottom Right (BR)

- Bottom Left (BL)

- Top Left (TL)

Note that the quadrant clock notation (TR, BR, BL, TL) is separate from that used for similar IOB placement constraints.

To estimate the quadrant location for a particular I/O, see the footprint diagrams in Module 4, Pinout Descriptions. For exact quadrant locations, use the floorplanning tool. In the QFP packages (VQ100, TQ144 and PQ208) the quadrant borders fall in the middle of each side of the package, at a GND pin. The clock inputs fall on the quadrant boundaries, as indicated in Table 42.

Table 42: QFP Package Clock Quadrant Locations

| Clock Pins  | Quadrant |

|-------------|----------|

| GCLK[3:0]   | BR       |

| GCLK[7:4]   | TR       |

| GCLK[11:8]  | TL       |

| GCLK[15:12] | BL       |

| RHCLK[3:0]  | BR       |

| RHCLK[7:4]  | TR       |

| LHCLK[3:0]  | TL       |

| LHCLK[7:4]  | BL       |

In a few cases, a dedicated input is physically in one quadrant of the device but connects to a different clock quadrant:

- FT256, H16 is in clock quadrant BR

- FG320, K2 is in clock quadrant BL

- FG400, L8 is in clock quadrant TL and the I/O at N11 is in clock quadrant BL

- FG484, M2 is in clock quadrant TL and L15 is in clock quadrant BR

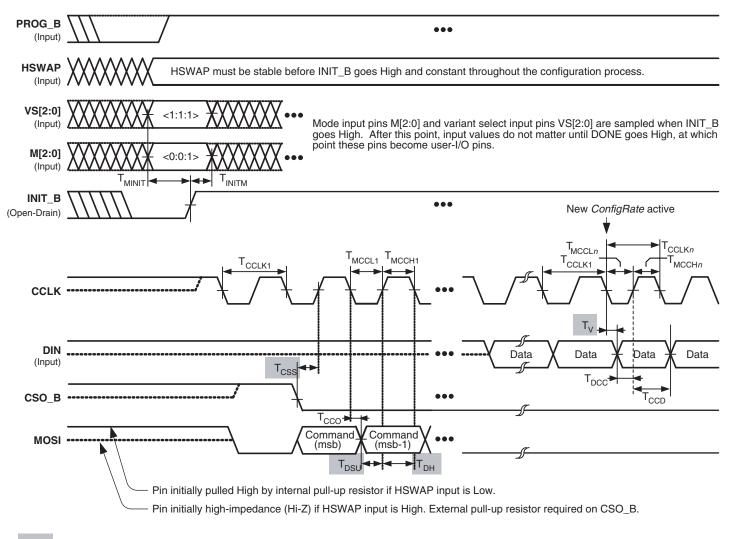

| HSWAP Value | I/O Pull-up Resistors<br>during Configuration |                                                                                                                             |                                                                                                                                                                     |  |  |

|-------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |                                               | High                                                                                                                        | Low                                                                                                                                                                 |  |  |

| 0           | Enabled                                       | Pulled High via an internal pull-up resistor to the associated $V_{CCO}$ supply. No external pull-up resistor is necessary. | Pulled Low using an appropriately sized pull-down resistor to GND.<br>For a 2.5V or 3.3V interface: $R \le 560\Omega$ . For a 1.8V interface: $R \le 1.1 k\Omega$ . |  |  |

| 1           | Disabled                                      | Pulled High using a 3.3 to $4.7 k\Omega$ resistor to the associated V <sub>CCO</sub> supply.                                | Pulled Low using a 3.3 to $4.7k\Omega$ resistor to GND.                                                                                                             |  |  |

#### Table 49: Pull-up or Pull-down Values for HSWAP, M[2:0], and VS[2:0]

The logic level on HSWAP dictates how to define the logic levels on M[2:0] and VS[2:0], as shown in Table 49. If the application requires HSWAP to be High, the HSWAP pin is pulled High using an external  $3.3k\Omega$  to  $4.7k\Omega$  resistor to VCCO\_0. If the application requires HSWAP to be Low during configuration, then HSWAP is either connected to GND or pulled Low using an appropriately sized external pull-down resistor to VCCO\_0. The external pull-down resistor to VCCO\_0. The external pull-down resistor must be strong enough to define a logic Low on HSWAP for the I/O standard used during configuration. For 2.5V or 3.3V I/O, the pull-down resistor is  $560\Omega$  or lower. For 1.8V I/O, the pull-down resistor is  $1.1k\Omega$  or lower.

Once HSWAP is defined, use Table 49 to define the logic values for M[2:0] and VS[2:0].

Use the weakest external pull-up or pull-down resistor value allowed by the application. The resistor must be strong enough to define a logic Low or High during configuration. However, when driving the HSWAP, M[2:0], or VS[2:0] pins after configuration, the output driver must be strong enough to overcome the pull-up or pull-down resistor value and generate the appropriate logic levels. For example, to overcome a 560 $\Omega$  pull-down resistor, a 3.3V FPGA I/O pin must use a 6 mA or stronger driver.

###

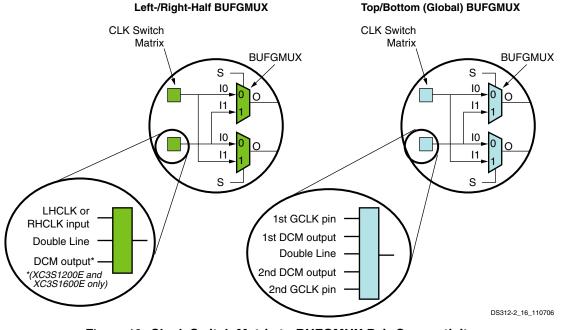

### SPI Serial Flash Mode

For additional information, refer to the "Master SPI Mode" chapter in UG332.

In SPI Serial Flash mode (M[2:0] = <0:0:1>), the Spartan-3E FPGA configures itself from an attached industry-standard SPI serial Flash PROM, as illustrated in Figure 53 and Figure 54. The FPGA supplies the CCLK output clock from its internal oscillator to the clock input of the attached SPI Flash PROM.

(S) Although SPI is a standard four-wire interface, various available SPI Flash PROMs use different command protocols. The FPGA's variant select pins, VS[2:0], define how the FPGA communicates with the SPI Flash, including which SPI Flash command the FPGA issues to start the read operation and the number of dummy bytes inserted before the FPGA expects to receive valid data from the SPI Flash. Table 53 shows the available SPI Flash PROMs expected to operate with Spartan-3E FPGAs. Other compatible devices might work but have not been tested for suitability with Spartan-3E FPGAs. All other VS[2:0] values are reserved for future use. Consult the data sheet for the desired SPI Flash device to determine its suitability. The basic timing requirements and waveforms are provided in

## Serial Peripheral Interface (SPI) Configuration Timing in Module 3.

Figure 53 shows the general connection diagram for those SPI Flash PROMs that support the 0x03 READ command or the 0x0B FAST READ commands.

Figure 54 shows the connection diagram for Atmel DataFlash serial PROMs, which also use an SPI-based protocol. 'B'-series DataFlash devices are limited to FPGA applications operating over the commercial temperature range. Industrial temperature range applications must use 'C'- or 'D'-series DataFlash devices, which have a shorter DataFlash select setup time, because of the faster FPGA CCLK frequency at cold temperatures.

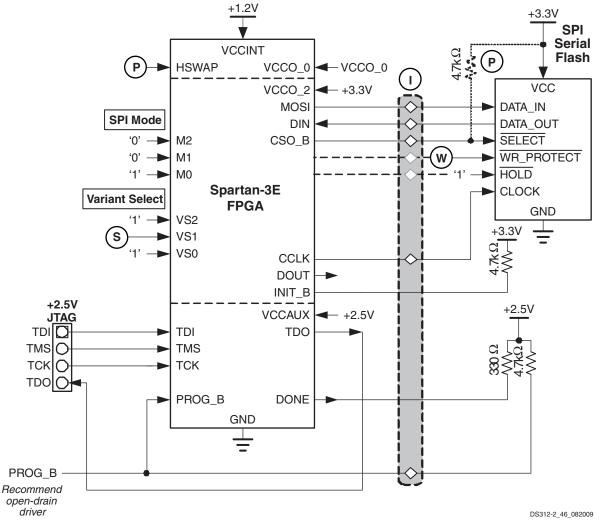

### **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain, as shown in Figure 57. Daisy-chaining from a single SPI serial Flash PROM is supported in Stepping 1 devices. It is not supported in Stepping 0 devices. Use SPI Flash mode (M[2:0] = <0:0:1>) for the FPGA connected to the Platform Flash PROM and Slave Serial mode (M[2:0] = <1:1:1>) for all other FPGAs in the daisy-chain. After the master FPGA—the FPGA on the left in the diagram—finishes loading its configuration data from the SPI Flash PROM, the master device uses its DOUT output pin to supply data to the next device in the daisy-chain, on the falling CCLK edge.

#### Design Note

SPI mode daisy chains are supported only in Stepping 1 silicon versions.

Figure 57: Daisy-Chaining from SPI Flash Mode (Stepping 1)

#### **Programming Support**

For successful daisy-chaining, the **DONE\_cycle** configuration option must be set to cycle 5 or sooner. The default cycle is 4. See Table 69 and the Start-Up section for additional information.

U In production applications, the SPI Flash PROM is usually pre-programmed before it is mounted on the printed circuit board. The <u>Xilinx ISE development software</u> produces industry-standard programming files that can be used with third-party gang programmers. Consult your specific SPI Flash vendor for recommended production programming solutions. In-system programming support is available from some third-party PROM programmers using a socket adapter with attached wires. To gain access to the SPI Flash signals, drive the FPGA's PROG\_B input Low with an open-drain driver. This action places all FPGA I/O pins, including those attached to the SPI Flash, in high-impedance (Hi-Z). If the HSWAP input is Low, the I/Os have pull-up resistors to the V<sub>CCO</sub> input on their respective I/O bank. The external programming hardware then has direct access to the SPI Flash pins. The programming access points are highlighted in the gray box in Figure 53, Figure 54, and Figure 57.

Beginning with the Xilinx ISE 8.2i software release, the iMPACT programming utility provides direct, in-system prototype programming support for STMicro M25P-series

### **EXILINX**.

### **XILINX**.

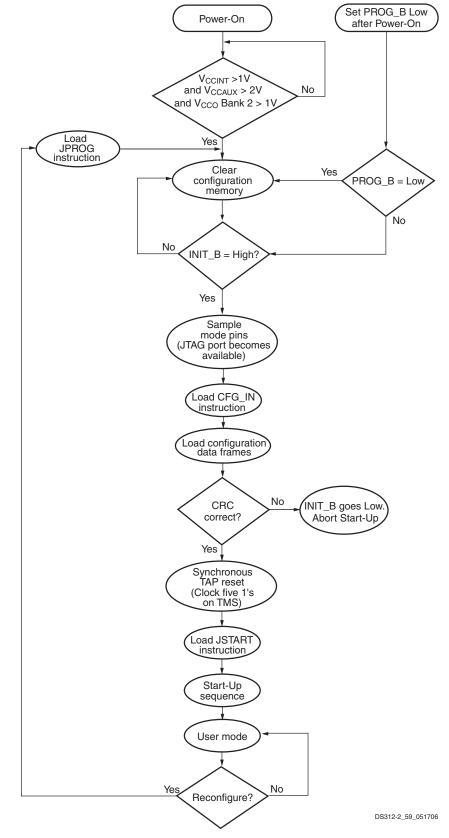

Figure 67: Boundary-Scan Configuration Flow Diagram

www.xilinx.com

### **Configuration Clock (CCLK) Characteristics**

### Table 112: Master Mode CCLK Output Period by ConfigRate Option Setting

| Symbol              | Description                                | <i>ConfigRate</i><br>Setting | Temperature<br>Range | Minimum | Maximum | Units |

|---------------------|--------------------------------------------|------------------------------|----------------------|---------|---------|-------|

| T <sub>CCLK1</sub>  | CCLK clock period by<br>ConfigRate setting | 1<br>(power-on value and     | Commercial           | 570     | 1,250   | ns    |

| CCLK1               | Comgnate setting                           | default value)               | Industrial           | 485     | 1,230   | ns    |

| т                   |                                            | 3                            | Commercial           | 285     | 625     | ns    |

| T <sub>CCLK3</sub>  |                                            | 3                            | Industrial           | 242     | 025     | ns    |

| т                   | CCLK6                                      | 6                            | Commercial           | 142     | 313     | ns    |

| CCLK6               |                                            | 0                            | Industrial           | 121     |         | ns    |

| т                   | _                                          | 12                           | Commercial           | 71.2    | - 157   | ns    |

| T <sub>CCLK12</sub> |                                            |                              | Industrial           | 60.6    |         | ns    |

| Τ                   |                                            | 25                           | Commercial           | 35.5    | 78.2    | ns    |

| T <sub>CCLK25</sub> |                                            | 25                           | Industrial           | 30.3    |         | ns    |

| T <sub>CCLK50</sub> |                                            | 50                           | Commercial           | 17.8    | 39.1    | ns    |

|                     |                                            | 50                           | Industrial           | 15.1    |         | ns    |

#### Notes:

1. Set the ConfigRate option value when generating a configuration bitstream. See Bitstream Generator (BitGen) Options in Module 2.

| Symbol              | Description                                                  | <i>ConfigRate</i><br>Setting | Temperature<br>Range | Minimum | Maximum | Units |

|---------------------|--------------------------------------------------------------|------------------------------|----------------------|---------|---------|-------|

| F <sub>CCLK1</sub>  | Equivalent CCLK clock frequency by <i>ConfigRate</i> setting | 1<br>(power-on value and     | Commercial           | 0.8     | 1.8     | MHz   |

| ' CCLK1             | by <b>comgnate</b> setting                                   | default value)               | Industrial           | 0.0     | 2.1     | MHz   |

| E                   | CLK3                                                         | 3                            | Commercial           | 1.6     | 3.6     | MHz   |

| F <sub>CCLK3</sub>  |                                                              | 3                            | Industrial           | 1.0     | 4.2     | MHz   |

| Family              | _                                                            | 6                            | Commercial           | 3.2     | 7.1     | MHz   |

| F <sub>CCLK6</sub>  |                                                              | 0                            | Industrial           | 0.2     | 8.3     | MHz   |

| F                   |                                                              | 12                           | Commercial           | 6.4     | 14.1    | MHz   |

| F <sub>CCLK12</sub> |                                                              | 12                           | Industrial           | 0.4     | 16.5    | MHz   |

| E                   |                                                              | 25                           | Commercial           | 12.8    | 28.1    | MHz   |

| F <sub>CCLK25</sub> |                                                              | 20                           | Industrial           | 12.0    | 33.0    | MHz   |

| Familia             |                                                              | 50                           | Commercial           | 25.6    | 56.2    | MHz   |

| F <sub>CCLK50</sub> |                                                              | 50                           | Industrial           | 20.0    | 66.0    | MHz   |

#### Table 114: Master Mode CCLK Output Minimum Low and High Time

| Symbol             | Description                                                 |             | ConfigRate Setting |     |    |      |      |     | Units |

|--------------------|-------------------------------------------------------------|-------------|--------------------|-----|----|------|------|-----|-------|

| Symbol             | Description                                                 | Description |                    | 3   | 6  | 12   | 25   | 50  | Units |

| T <sub>MCCL,</sub> | TMCCL,<br>MCCHMaster mode CCLK minimum<br>Low and High time | Commercial  | 276                | 138 | 69 | 34.5 | 17.1 | 8.5 | ns    |

| I MCCH             |                                                             | Industrial  | 235                | 117 | 58 | 29.3 | 14.5 | 7.3 | ns    |

#### Table 115: Slave Mode CCLK Input Low and High Time

| Symbol                                  | Description            | Min | Мах | Units |

|-----------------------------------------|------------------------|-----|-----|-------|

| T <sub>SCCL,</sub><br>T <sub>SCCH</sub> | CCLK Low and High time | 5   | ∞   | ns    |

### Serial Peripheral Interface (SPI) Configuration Timing

Shaded values indicate specifications on attached SPI Flash PROM.

ds312-3\_06\_110206

#### Figure 76: Waveforms for Serial Peripheral Interface (SPI) Configuration

#### Table 118: Timing for Serial Peripheral Interface (SPI) Configuration Mode

| Symbol             | Description                                                                 | Minimum       | Maximum | Units |

|--------------------|-----------------------------------------------------------------------------|---------------|---------|-------|

| T <sub>CCLK1</sub> | Initial CCLK clock period                                                   | See Table 112 |         |       |

| T <sub>CCLKn</sub> | CCLK clock period after FPGA loads ConfigRate setting                       | See Table 112 |         |       |

| T <sub>MINIT</sub> | Setup time on VS[2:0] and M[2:0] mode pins before the rising edge of INIT_B | 50            | -       | ns    |

| T <sub>INITM</sub> | Hold time on VS[2:0] and M[2:0]mode pins after the rising edge of INIT_B    | 0             | -       | ns    |

| T <sub>CCO</sub>   | MOSI output valid after CCLK edge                                           | See Table 116 |         |       |

| T <sub>DCC</sub>   | Setup time on DIN data input before CCLK edge                               | See Table 116 |         |       |

| T <sub>CCD</sub>   | Hold time on DIN data input after CCLK edge                                 | See Table 116 |         |       |

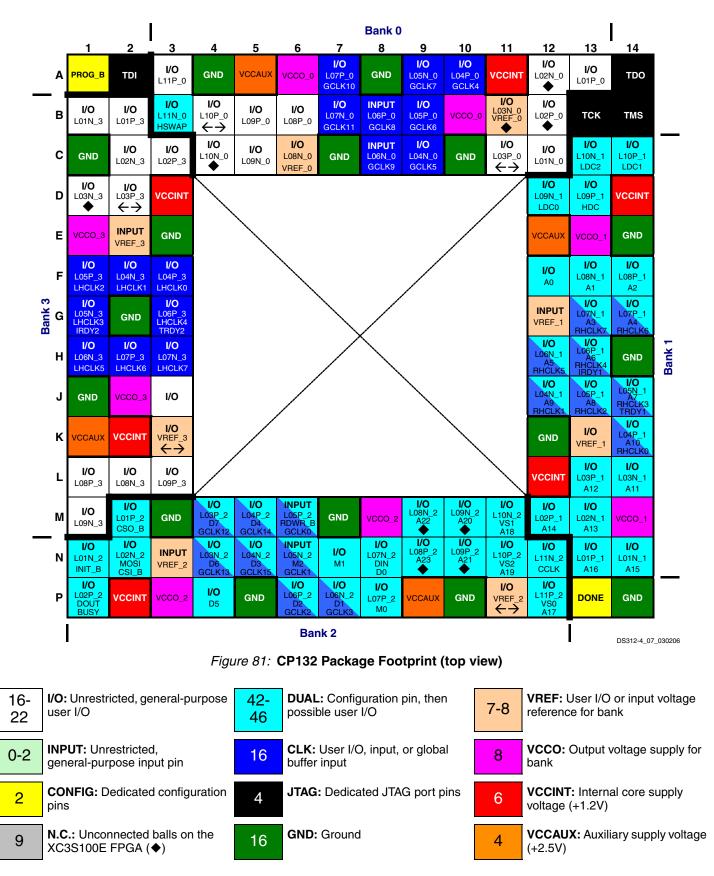

#### Table 129: Maximum User I/O by Package

|           |         | Maximum                        | Maximum        | Maximum               | All Possible I/Os by Type |       |      |                     |                    |      |  |  |

|-----------|---------|--------------------------------|----------------|-----------------------|---------------------------|-------|------|---------------------|--------------------|------|--|--|

| Device    | Package | User I/Os<br>and<br>Input-Only | Input-<br>Only | Differential<br>Pairs | I/O                       | INPUT | DUAL | VREF <sup>(1)</sup> | CLK <sup>(2)</sup> | N.C. |  |  |

| XC3S100E  |         | 66                             | 7              | 30                    | 16                        | 1     | 21   | 4                   | 24                 | 0    |  |  |

| XC3S250E  | VQ100   | 66                             | 7              | 30                    | 16                        | 1     | 21   | 4                   | 24                 | 0    |  |  |

| XC3S500E  |         | 66                             | 7              | 30                    | 16                        | 1     | 21   | 4                   | 24                 | 0    |  |  |

| XC3S100E  |         | 83                             | 11             | 35                    | 16                        | 2     | 42   | 7                   | 16                 | 9    |  |  |

| XC3S250E  | CP132   | 92                             | 7              | 41                    | 22                        | 0     | 46   | 8                   | 16                 | 0    |  |  |

| XC3S500E  |         | 92                             | 7              | 41                    | 22                        | 0     | 46   | 8                   | 16                 | 0    |  |  |

| XC3S100E  | TO144   | 108                            | 28             | 40                    | 22                        | 19    | 42   | 9                   | 16                 | 0    |  |  |

| XC3S250E  | - TQ144 | 108 28                         |                | 40                    | 20                        | 21    | 42   | 9                   | 16                 | 0    |  |  |

| XC3S250E  | PQ208   | 158                            | 32             | 65                    | 58                        | 25    | 46   | 13                  | 16                 | 0    |  |  |

| XC3S500E  | PQ206   | 158                            | 32             | 65                    | 58                        | 25    | 46   | 13                  | 16                 | 0    |  |  |

| XC3S250E  |         | 172                            | 40             | 68                    | 62                        | 33    | 46   | 15                  | 16                 | 18   |  |  |

| XC3S500E  | FT256   | 190                            | 41             | 77                    | 76                        | 33    | 46   | 19                  | 16                 | 0    |  |  |

| XC3S1200E |         | 190                            | 40             | 77                    | 78                        | 31    | 46   | 19                  | 16                 | 0    |  |  |

| XC3S500E  |         | 232                            | 56             | 92                    | 102                       | 48    | 46   | 20                  | 16                 | 18   |  |  |

| XC3S1200E | FG320   | 250                            | 56             | 99                    | 120                       | 47    | 46   | 21                  | 16                 | 0    |  |  |

| XC3S1600E |         | 250                            | 56             | 99                    | 120                       | 47    | 46   | 21                  | 16                 | 0    |  |  |

| XC3S1200E | FC 400  | 304                            | 72             | 124                   | 156                       | 62    | 46   | 24                  | 16                 | 0    |  |  |

| XC3S1600E | - FG400 | 304                            | 72             | 124                   | 156                       | 62    | 46   | 24                  | 16                 | 0    |  |  |

| XC3S1600E | FG484   | 376                            | 82             | 156                   | 214                       | 72    | 46   | 28                  | 16                 | 0    |  |  |

#### Notes:

1. Some VREF pins are on INPUT pins. See pinout tables for details.

All devices have 24 possible global clock and right- and left-half side clock inputs. The right-half and bottom-edge clock pins have shared functionality in some FPGA configuration modes. Consequently, some clock pins are counted in the DUAL column. 4 GCLK pins, including 2 DUAL pins, are on INPUT pins.

Electronic versions of the package pinout tables and footprints are available for download from the Xilinx website. Download the files from the following location:

http://www.xilinx.com/support/documentation/data\_sheets/s3e\_pin.zip

Using a spreadsheet program, the data can be sorted and reformatted according to any specific needs. Similarly, the ASCII-text file is easily parsed by most scripting programs.

### **Footprint Migration Differences**

Table 136 summarizes any footprint and functionality differences between the XC3S100E, the XC3S250E, and the XC3S500E FPGAs that may affect easy migration between devices in the CP132 package. There are 14 such balls. All other pins not listed in Table 136 unconditionally migrate between Spartan-3E devices available in the CP132 package.

The XC3S100E is duplicated on both the left and right sides of the table to show migrations to and from the XC3S250E and the XC3S500E. The arrows indicate the direction for easy migration. A double-ended arrow ( $\leftarrow \rightarrow$ ) indicates that the two pins have identical functionality. A left-facing arrow  $(\leftarrow)$  indicates that the pin on the device on the right unconditionally migrates to the pin on the device on the left. It may be possible to migrate the opposite direction depending on the I/O configuration. For example, an I/O pin (Type = I/O) can migrate to an input-only pin (Type = INPUT) if the I/O pin is configured as an input.

The XC3S100E FPGA in the CP132 package has four fewer BPI-mode address lines than the XC3S250E and XC3S500E.

| CP132<br>Ball | Bank          | XC3S100E<br>Type | Migration     | XC3S250E<br>Type | Migration         | XC3S500E<br>Type | Migration | XC3S100E<br>Type |  |

|---------------|---------------|------------------|---------------|------------------|-------------------|------------------|-----------|------------------|--|

| A12           | 0             | N.C.             | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | N.C.             |  |

| B4            | 0             | INPUT            | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | INPUT            |  |

| B11           | 0             | N.C.             | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | N.C.             |  |

| B12           | 0             | N.C.             | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | N.C.             |  |

| C4            | 0             | N.C.             | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | N.C.             |  |

| C11           | 0             | INPUT            | $\rightarrow$ | I/O              | $\leftrightarrow$ | I/O              | ÷         | INPUT            |  |

| D1            | 3             | N.C.             | $\rightarrow$ | I/O              |                   | I/O              | ÷         | N.C.             |  |

| D2            | 3             | I/O              | $\rightarrow$ | I/O (Diff)       | $\leftrightarrow$ | I/O (Diff)       | ÷         | I/O              |  |

| K3            | 3             | VREF(INPUT)      | $\rightarrow$ | VREF(I/O)        | $\leftrightarrow$ | VREF(I/O)        | ÷         | VREF(INPUT)      |  |

| M9            | 2             | N.C.             | $\rightarrow$ | DUAL             | $\leftrightarrow$ | DUAL             | ÷         | N.C.             |  |

| M10           | 2             | N.C.             | $\rightarrow$ | DUAL             | $\leftrightarrow$ | DUAL             | ÷         | N.C.             |  |

| N9            | 2             | N.C.             | $\rightarrow$ | DUAL             | $\leftrightarrow$ | DUAL             | ÷         | N.C.             |  |

| N10           | 2             | N.C.             | $\rightarrow$ | DUAL             | $\leftrightarrow$ | DUAL             | ÷         | N.C.             |  |

| P11           | P11 2 VREF(IN |                  | $\rightarrow$ | VREF(I/O)        | $\leftrightarrow$ | VREF(I/O)        | ÷         | VREF(INPUT)      |  |

| DIFFERI       | ENCES         |                  | 14            |                  | 0                 |                  | 14        |                  |  |

### Table 136: CP132 Footprint Migration Differences

Legend:

$\leftrightarrow$  This pin is identical on the device on the left and the right.

This pin can unconditionally migrate from the device on the left to the device on the right. Migration in the other direction may be possible depending on how the pin is configured for the device on the right.

+ This pin can unconditionally migrate from the device on the right to the device on the left. Migration in the other direction may be possible depending on how the pin is configured for the device on the left.

### **CP132 Footprint**

www.xilinx.com

### Table 141: PQ208 Package Pinout (Cont'd)

| Bank   | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре   |

|--------|----------------------------------|--------------|--------|

| 3      | IO_L14P_3                        | P41          | I/O    |

| 3      | IO_L15N_3                        | P48          | I/O    |

| 3      | IO_L15P_3                        | P47          | I/O    |

| 3      | IO_L16N_3                        | P50          | I/O    |

| 3      | IO_L16P_3                        | P49          | I/O    |

| 3      | IP                               | P6           | INPUT  |

| 3      | IP                               | P14          | INPUT  |

| 3      | IP                               | P26          | INPUT  |

| 3      | IP                               | P32          | INPUT  |

| 3      | IP                               | P43          | INPUT  |

| 3      | IP                               | P51          | INPUT  |

| 3      | IP/VREF_3                        | P20          | VREF   |

| 3      | VCCO_3                           | P21          | VCCO   |

| 3      | VCCO_3                           | P38          | VCCO   |

| 3      | VCCO_3                           | P46          | VCCO   |

| GND    | GND                              | P10          | GND    |

| GND    | GND                              | P17          | GND    |

| GND    | GND                              | P27          | GND    |

| GND    | GND                              | P37          | GND    |

| GND    | GND                              | P52          | GND    |

| GND    | GND                              | P53          | GND    |

| GND    | GND                              | P70          | GND    |

| GND    | GND                              | P79          | GND    |

| GND    | GND                              | P85          | GND    |

| GND    | GND                              | P95          | GND    |

| GND    | GND                              | P105         | GND    |

| GND    | GND                              | P121         | GND    |

| GND    | GND                              | P131         | GND    |

| GND    | GND                              | P141         | GND    |

| GND    | GND                              | P156         | GND    |

| GND    | GND                              | P173         | GND    |

| GND    | GND                              | P182         | GND    |

| GND    | GND                              | P188         | GND    |

| GND    | GND                              | P198         | GND    |

| GND    | GND                              | P208         | GND    |

| VCCAUX | DONE                             | P104         | CONFIG |

| VCCAUX | PROG_B                           | P1           | CONFIG |

| VCCAUX | тск                              | P158         | JTAG   |

| VCCAUX | TDI                              | P207         | JTAG   |

| VCCAUX | TDO                              | P157         | JTAG   |

| VCCAUX | TMS                              | P155         | JTAG   |

| VCCAUX | VCCAUX                           | P7           | VCCAUX |

| VCCAUX | VCCAUX                           | P44          | VCCAUX |

### Table 141: PQ208 Package Pinout (Cont'd)

| Bank   | XC3S250E<br>XC3S500E<br>Pin Name | PQ208<br>Pin | Туре   |

|--------|----------------------------------|--------------|--------|

| VCCAUX | VCCAUX                           | P66          | VCCAUX |

| VCCAUX | VCCAUX                           | P92          | VCCAUX |

| VCCAUX | VCCAUX                           | P111         | VCCAUX |

| VCCAUX | VCCAUX                           | P149         | VCCAUX |

| VCCAUX | VCCAUX                           | P166         | VCCAUX |

| VCCAUX | VCCAUX                           | P195         | VCCAUX |

| VCCINT | VCCINT                           | P13          | VCCINT |

| VCCINT | VCCINT                           | P67          | VCCINT |

| VCCINT | VCCINT                           | P117         | VCCINT |

| VCCINT | VCCINT                           | P170         | VCCINT |

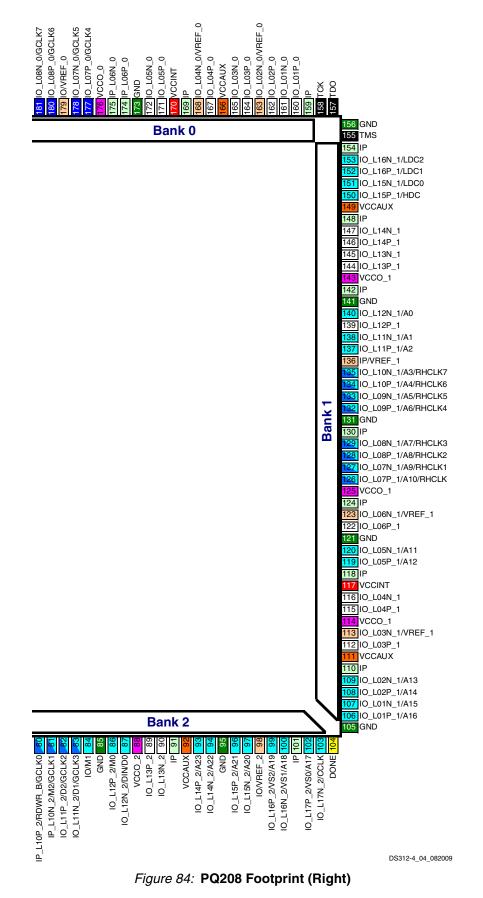

### PQ208 Footprint (Right)

www.xilinx.com

### Table 143: FT256 Package Pinout (Cont'd)

| Bank | XC3S250E Pin Name    | XC3S500E Pin Name    | XC3S1200E Pin Name   | FT256<br>Ball | Туре                                                             |  |

|------|----------------------|----------------------|----------------------|---------------|------------------------------------------------------------------|--|

| 1    | IO                   | IO                   | IP                   | M14           | 250E: I/O<br>500E: I/O<br>1200E: INPUT                           |  |

| 1    | IO/VREF_1            | IP/VREF_1            | IP/VREF_1            | D16           | 250E: VREF(I/O)<br>500E:<br>VREF(INPUT)<br>1200E:<br>VREF(INPUT) |  |

| 1    | IP/VREF_1            | IP/VREF_1            | IP/VREF_1            | H13           | VREF                                                             |  |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | E15           | VCCO                                                             |  |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | G11           | VCCO                                                             |  |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | K11           | VCCO                                                             |  |

| 1    | VCCO_1               | VCCO_1               | VCCO_1               | M15           | VCCO                                                             |  |

| 2    | IP                   | IP                   | 10                   | M7            | 250E: INPUT<br>500E: INPUT<br>1200E: I/O                         |  |

| 2    | IP                   | IP                   | IO                   | T12           | 250E: INPUT<br>500E: INPUT<br>1200E: I/O                         |  |

| 2    | IO/D5                | IO/D5                | IO/D5                | Т8            | DUAL                                                             |  |

| 2    | IO/M1                | IO/M1                | IO/M1                | T10           | DUAL                                                             |  |

| 2    | IO/VREF_2            | IO/VREF_2            | IO/VREF_2            | P13           | VREF                                                             |  |

| 2    | IO/VREF_2            | IO/VREF_2            | IO/VREF_2            | R4            | VREF                                                             |  |

| 2    | IO_L01N_2/INIT_B     | IO_L01N_2/INIT_B     | IO_L01N_2/INIT_B     | P4            | DUAL                                                             |  |

| 2    | IO_L01P_2/CSO_B      | IO_L01P_2/CSO_B      | IO_L01P_2/CSO_B      | P3            | DUAL                                                             |  |

| 2    | IO_L03N_2/MOSI/CSI_B | IO_L03N_2/MOSI/CSI_B | IO_L03N_2/MOSI/CSI_B | N5            | DUAL                                                             |  |

| 2    | IO_L03P_2/DOUT/BUSY  | IO_L03P_2/DOUT/BUSY  | IO_L03P_2/DOUT/BUSY  | P5            | DUAL                                                             |  |

| 2    | IO_L04N_2            | IO_L04N_2            | IO_L04N_2            | T5            | I/O                                                              |  |

| 2    | IO_L04P_2            | IO_L04P_2            | IO_L04P_2            | T4            | I/O                                                              |  |

| 2    | IO_L05N_2            | IO_L05N_2            | IO_L05N_2            | N6            | I/O                                                              |  |

| 2    | IO_L05P_2            | IO_L05P_2            | IO_L05P_2            | M6            | I/O                                                              |  |

| 2    | IO_L06N_2            | IO_L06N_2            | IO_L06N_2            | P6            | I/O                                                              |  |

| 2    | IO_L06P_2            | IO_L06P_2            | IO_L06P_2            | R6            | I/O                                                              |  |

| 2    | N.C. (�)             | IO_L07N_2            | IO_L07N_2            | P7            | 250E: N.C.<br>500E: I/O<br>1200E: I/O                            |  |

| 2    | N.C. (�)             | IO_L07P_2            | IO_L07P_2            | N7            | 250E: N.C.<br>500E: I/O<br>1200E: I/O                            |  |

| 2    | IO_L09N_2/D6/GCLK13  | IO_L09N_2/D6/GCLK13  | IO_L09N_2/D6/GCLK13  | L8            | DUAL/GCLK                                                        |  |

| 2    | IO_L09P_2/D7/GCLK12  | IO_L09P_2/D7/GCLK12  | IO_L09P_2/D7/GCLK12  | M8            | DUAL/GCLK                                                        |  |

| 2    | IO_L10N_2/D3/GCLK15  | IO_L10N_2/D3/GCLK15  | IO_L10N_2/D3/GCLK15  | P8            | DUAL/GCLK                                                        |  |

| 2    | IO_L10P_2/D4/GCLK14  | IO_L10P_2/D4/GCLK14  | IO_L10P_2/D4/GCLK14  | N8            | DUAL/GCLK                                                        |  |

| 2    | IO_L12N_2/D1/GCLK3   | IO_L12N_2/D1/GCLK3   | IO_L12N_2/D1/GCLK3   | N9            | DUAL/GCLK                                                        |  |

| 2    | IO_L12P_2/D2/GCLK2   | IO_L12P_2/D2/GCLK2   | IO_L12P_2/D2/GCLK2   | P9            | DUAL/GCLK                                                        |  |

| 2    | IO_L13N_2/DIN/D0     | IO_L13N_2/DIN/D0     | IO_L13N_2/DIN/D0     | M9            | DUAL                                                             |  |

| 2    | IO_L13P_2/M0         | IO_L13P_2/M0         | IO_L13P_2/M0         | L9            | DUAL                                                             |  |

www.xilinx.com

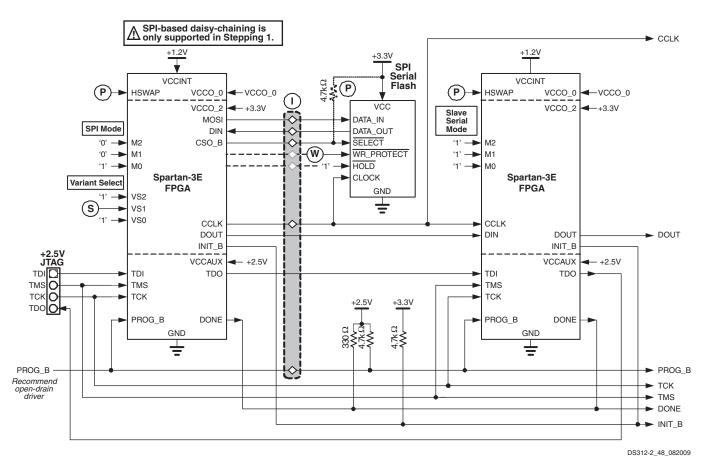

### FT256 Footprint

|         | Bank 0<br>1 2 _ 3 4 5 6 7 8 9 10 11 |                  |                      |                                  |                               |                                  |                                |                         |                                |                                         | 11                                        | 12                        | 13                             | 14                            | 15                                 | 16                            |                                      |                                      |            |

|---------|-------------------------------------|------------------|----------------------|----------------------------------|-------------------------------|----------------------------------|--------------------------------|-------------------------|--------------------------------|-----------------------------------------|-------------------------------------------|---------------------------|--------------------------------|-------------------------------|------------------------------------|-------------------------------|--------------------------------------|--------------------------------------|------------|

|         |                                     | A                | GND                  | TDI                              | INPUT                         | <b>I/O</b><br>L17N_0<br>VREF 0   | <b>I/O</b><br>L17P_0           | VCCAUX                  | <i>i</i> /o                    | INPUT<br>L10P_0<br>GCLK8                | I/O<br>L09N_0<br>GCLK7                    | I/O<br>L09P_0<br>GCLK6    | VCCAUX                         | 1/0                           | I/O<br>L03N_0<br>VREF 0            | <b>I/O</b><br>L01N_0          | тск                                  | GND                                  |            |

| -       | _                                   | в                | <b>I/O</b><br>L01P_3 | <b>I/O</b><br>L01N_3             | <b>I/O</b><br>L19N_0<br>HSWAP | I/O                              | VCCO_0                         | INPUT<br>←→             | <b>I/O</b><br>L13P_0<br>♦      | INPUT<br>L10N_0<br>GCLK9                | GND                                       | INPUT<br>←→               | <b>I/O</b><br>L05N_0<br>VREF 0 | VCCO_0                        | <b>I/O</b><br>L03P_0               | <b>I/O</b><br>L01P_0          | TMS                                  | INPUT                                | -          |

|         |                                     | с                | <b>I/O</b><br>L02P_3 | <b>I/O</b><br>L02N_3<br>VREF_3   | <b>I/O</b><br>L19P_0          | <b>I/O</b><br>L18N_0             | <b>I/O</b><br>L18P_0           | <b>I/O</b><br>L15P_0    | <b>I/O</b><br>L13N_0<br>♠      | <b>I/O</b><br>L11P_0<br>GCLK10          | INPUT<br>L07N_0                           | INPUT<br>L07P_0           | <b>I/O</b><br>L05P_0           | INPUT<br>L02N_0               | INPUT                              | TDO                           | <b>I/O</b><br>L19N_1<br>LDC2         | <b>I/O</b><br>L19P_1<br>LDC1         |            |

|         |                                     | D                | <b>I/O</b><br>L05P_3 | INPUT                            | PROG_B                        | VCCINT                           | INPUT<br>L16P_0                | <b>I/O</b><br>L15N_0    | <b>I/O</b><br>L14N_0<br>VREF 0 | <b>I/O</b><br>L11N_0<br>GCLK11          | <b>I/O</b><br>VREF_0                      | <b>I/O</b><br>L06P_0      | <b>I/O</b><br>L04P_0           | INPUT<br>L02P_0               | VCCINT                             | <b>I/O</b><br>L18N_1<br>LDC0  | <b>I/O</b><br>L18P_1<br>HDC          | INPUT<br>VREF_1<br>←→                |            |

|         |                                     | E                | <b>I/O</b><br>L05N_3 | VCCO_3                           | <b>I/O</b><br>L03P_3          | <b>I/O</b><br>L03N_3             | VCCINT                         | INPUT<br>L16N_0         | <b>I/O</b><br>L14P_0           | <b>I/O</b><br>L12P_0                    | <b>I/O</b><br>L08P_0<br>GCLK4             | <b>I/O</b><br>L06N_0      | <b>I/O</b><br>L04N_0           | VCCINT                        | <b>I/O</b><br>L17P_1<br>♠          | INPUT                         | VCCO_1                               | <b>I/O</b><br>L17N_1<br>♦            |            |

|         |                                     | F                | VCCAUX               | INPUT                            | <b>I/O</b><br>L04P_3          | I/O<br>L04N_3<br>VREF_3          | INPUT<br>←→                    | GND                     | VCCO_0                         | <b>I/O</b><br>L12N_0                    | <b>I/O</b><br>L08N_0<br>GCLK5             | VCCO_0                    | GND                            | <b>I/O</b><br>L16N_1          | <b>I/O</b><br>L16P_1               | <b>I/O</b><br>L15P_1          | <b>I/O</b><br>L15N_1                 | VCCAUX                               |            |

|         |                                     | G                | INPUT<br>VREF_3      | <b>I/O</b><br>L07N_3             | <b>I/O</b><br>L07P_3          | I/O<br>L06N_3                    | <b>I/O</b><br>L06P_3           | VCCO_3                  | GND                            | GND                                     | GND                                       | GND                       | VCCO_1                         | INPUT                         | <b>I/O</b><br>L14P_1               | <b>I/O</b><br>L14N_1<br>A0    | <b>I/O</b><br>L13P_1<br>A2           | <b>I/O</b><br>L13N_1<br>A1           |            |

|         |                                     | н                | INPUT                | GND                              | I/O<br>L09P_3<br>LHCLK2       | I/O<br>L09N_3<br>LHCLK3<br>IRDY2 | <b>I/O</b><br>L08P_3<br>LHCLK0 | I/O<br>L08N_3<br>LHCLK1 | GND                            | GND                                     | GND                                       | GND                       | I/O<br>L12N_1<br>A3<br>RHCLK7  | I/O<br>L12P_1<br>A4<br>RHCLK6 | INPUT<br>VREF_1                    | I/O<br>L11N_1<br>A5<br>RHCLK5 | <b>I/O</b><br>L11P_1<br>A6<br>RHCLK4 | INPUT                                | (1         |

|         | Bank                                | J                | <b>I/O</b><br>L12P_3 | I/O<br>L10P_3<br>LHCLK4<br>TRDY2 | I/O<br>L10N_3<br>LHCLK5       | I/O<br>L11N_3<br>LHCLK7          | I/O<br>L11P_3<br>LHCLK6        | INPUT                   | GND                            | GND                                     | GND                                       | GND                       | INPUT                          | INPUT                         | I/O<br>L10N_1<br>A7<br>RHCLK3      | I/O<br>L10P_1<br>A8<br>RHCLK2 | GND                                  | <b>I/O</b><br>L09N_1<br>A9<br>RHCLK1 | Bank       |

|         |                                     | к                | <b>I/O</b><br>L12N_3 | <b>I/O</b><br>L13P_3             | <b>I/O</b><br>L13N_3          | INPUT                            | <b>I/O</b><br>L15P_3           | VCCO_3                  | GND                            | GND                                     | GND                                       | GND                       | VCCO_1                         | <b>I/O</b><br>L07N_1<br>A11   | TRDY1<br>I/O<br>L07P_1<br>A12      | I/O<br>L08N_1<br>VREF_1       | <b>I/O</b><br>L08P_1                 | I/O<br>L09P_1<br>A10<br>RHCLK0       |            |

|         |                                     | L                | VCCAUX               | <b>I/O</b><br>L14N_3<br>VREF_3   | <b>I/O</b><br>L14P_3          | <b>I/O</b><br>L17N_3             | <b>I/O</b><br>L15N_3           | GND                     | VCCO_2                         | <b>I/O</b><br>L09N_2<br>D6<br>GCLK13    | <b>I/O</b><br>L13P_2<br>M0                | VCCO_2                    | GND                            | <b>I/O</b><br>L05P_1<br>♠     | <b>I/O</b><br>L05N_1<br>♠          | <b>I/O</b><br>L06P_1          | <b>I/O</b><br>L06N_1                 | VCCAUX                               |            |

|         |                                     | м                | <b>I/O</b><br>L16P_3 | VCCO_3                           | INPUT                         | <b>I/O</b><br>L17P_3             | VCCINT                         | <b>I/O</b><br>L05P_2    | INPUT<br>←→                    | I/O<br>L09P_2<br>D7<br>GCLK12           | <b>I/O</b><br>L13N_2<br>DIN               | <b>I/O</b><br>L15N_2      | INPUT<br>L17N_2                | VCCINT                        |                                    | INPUT<br>←→                   | VCCO_1                               | <b>I/O</b><br>L04N_1<br>VREF_1       |            |

|         |                                     | N                | <b>I/O</b><br>L16N_3 | INPUT<br>VREF_3<br>←→            | INPUT                         | VCCINT                           | I/O<br>L03N_2<br>MOSI<br>CSI_B | <b>I/O</b><br>L05N_2    | <b>I/O</b><br>L07P_2           | <b>I/O</b><br>L10P_2<br>D4              | D0<br><b>I/O</b><br>L12N_2<br>D1<br>GCLK3 | <b>I/O</b><br>L15P_2      | INPUT<br>L17P_2                | <b>I/O</b><br>L18N_2<br>A20   | VCCINT                             | <b>I/O</b><br>L03P_1<br>♦     | I/O<br>L03N_1<br>VREF_1              | <b>I/O</b><br>L04P_1                 |            |

|         |                                     | Р                | <b>I/O</b><br>L18N_3 | <b>I/O</b><br>L18P_3             | <b>I/O</b><br>L01P_2<br>CSO B | <b>I/O</b><br>L01N_2<br>INIT B   | L03P_2<br>DOUT<br>BUSY         | <b>I/O</b><br>L06N_2    | <b>I/O</b><br>L07N_2           | GCLK14<br>I/O<br>L10N_2<br>D3<br>GCLK15 | I/O<br>L12P_2<br>D2<br>GCLK2              | <b>I/O</b><br>L14P_2<br>♠ | <b>I/O</b><br>L16N_2<br>A22    | <b>I/O</b><br>L18P_2<br>A21   | <b>I/O</b><br>VREF_2               | I/O<br>L20P_2<br>VS0<br>A17   | <b>I/O</b><br>L02N_1<br>A13          | <b>I/O</b><br>L02P_1<br>A14          |            |

|         |                                     | R                | <b>I/O</b><br>L19N_3 | <b>I/O</b><br>L19P_3             | INPUT<br>L02N_2               | I/O<br>VREF_2                    | VCCO_2                         | <b>I/O</b><br>L06P_2    | INPUT<br>L08P_2                | GND                                     | INPUT<br>L11N_2<br>M2<br>GCLK1            | I/O<br>L14N_2<br>VREF_2   | <b>I/O</b><br>L16P_2<br>A23    | VCCO_2                        | <b>I/O</b><br>L19N_2<br>VS1<br>A18 | I/O<br>L20N_2<br>CCLK         | <b>I/O</b><br>L01N_1<br>A15          | <b>I/O</b><br>L01P_1<br>A16          |            |

| -       |                                     | т                | GND                  | INPUT                            | INPUT<br>L02P_2               | <b>I/O</b><br>L04P_2             | <b>I/O</b><br>L04N_2           | VCCAUX                  | INPUT<br>L08N_2<br>VREF_2      | <b>I/O</b><br>D5                        | INPUT<br>L11P_2<br>RDWR_B<br>GCLK0        | <b>I/O</b><br>M1          | VCCAUX                         | INPUT<br>←→                   | I/O<br>L19P_2<br>VS2<br>A19        | INPUT                         | DONE                                 | GND                                  | -          |

|         |                                     | •                |                      |                                  |                               | I                                | I                              |                         |                                | Bank 2                                  | COLIC                                     |                           |                                |                               | 1110                               |                               | <b></b>                              | DS312-4_05                           | 101805     |

|         |                                     |                  |                      |                                  |                               |                                  | Figure                         | 9 <i>85:</i> F          | T256                           | Packa                                   | ge Fo                                     | otprint                   | t (top v                       | view)                         |                                    |                               |                                      |                                      |            |

| 2       |                                     | <b>CC</b><br>pin |                      | Dedica                           | ated co                       | nfigura                          | tion                           | 4                       | JTAG:                          | Dedica                                  | ated JT                                   | AG por                    | t pins                         | 8                             |                                    | CINT:<br>tage (+              | Internal<br>1.2V)                    | core s                               | upply      |

| 28      |                                     | GN               | ID: Gro              | ound                             |                               |                                  |                                | 16                      | <b>VCCO</b><br>bank            | : Outpu                                 | ut volta                                  | ge supp                   | oly for                        | 8                             |                                    | <b>CAUX:</b><br>2.5V)         | Auxilia                              | ry supp                              | ly voltage |

| 6<br>←→ |                                     | pa               |                      | migratio                         |                               | For flex<br>these p              |                                | 18<br>(♦)               | Uncon                          | inected                                 | pins o                                    | n XC3S                    | 250E                           |                               |                                    |                               |                                      |                                      |            |

www.xilinx.com