Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 3688                                                          |

| Number of Logic Elements/Cells | 33192                                                         |

| Total RAM Bits                 | 663552                                                        |

| Number of I/O                  | 304                                                           |

| Number of Gates                | 1600000                                                       |

| Voltage - Supply               | 1.14V ~ 1.26V                                                 |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 400-BGA                                                       |

| Supplier Device Package        | 400-FBGA (21x21)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xc3s1600e-4fg400i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Supply Voltages for the IOBs

The IOBs are powered by three supplies:

- 1. The  $V_{CCO}$  supplies, one for each of the FPGA's I/O banks, power the output drivers. The voltage on the  $V_{CCO}$  pins determines the voltage swing of the output signal.

- 2.  $V_{CCINT}$  is the main power supply for the FPGA's internal logic.

- V<sub>CCAUX</sub> is an auxiliary source of power, primarily to optimize the performance of various FPGA functions such as I/O switching.

# I/O and Input-Only Pin Behavior During Power-On, Configuration, and User Mode

In this section, all behavior described for I/O pins also applies to input-only pins and dual-purpose I/O pins that are not actively involved in the currently-selected configuration mode.

All I/O pins have ESD clamp diodes to their respective V<sub>CCO</sub> supply and from GND, as shown in Figure 5. The V<sub>CCINT</sub> (1.2V), V<sub>CCAUX</sub> (2.5V), and V<sub>CCO</sub> supplies can be applied in any order. Before the FPGA can start its configuration process, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> must have reached their respective minimum recommended operating levels indicated in Table 74. At this time, all output drivers are in a high-impedance state. V<sub>CCO</sub> Bank 2, V<sub>CCINT</sub>, and V<sub>CCAUX</sub> serve as inputs to the internal Power-On Reset circuit (POR).

A Low level applied to the HSWAP input enables pull-up resistors on user-I/O and input-only pins from power-on throughout configuration. A High level on HSWAP disables the pull-up resistors, allowing the I/Os to float. HSWAP contains an internal pull-up resistor and defaults to High if left floating. As soon as power is applied, the FPGA begins initializing its configuration memory. At the same time, the FPGA internally asserts the Global Set-Reset (GSR), which asynchronously resets all IOB storage elements to a default Low state. Also see Pin Behavior During Configuration.

Upon the completion of initialization and the beginning of configuration, INIT\_B goes High, sampling the M0, M1, and M2 inputs to determine the configuration mode. Configuration data is then loaded into the FPGA. The I/O drivers remain in a high-impedance state (with or without pull-up resistors, as determined by the HSWAP input) throughout configuration.

At the end of configuration, the GSR net is released, placing the IOB registers in a Low state by default, unless the loaded design reverses the polarity of their respective SR inputs.

The Global Three State (GTS) net is released during Start-Up, marking the end of configuration and the

beginning of design operation in the User mode. After the GTS net is released, all user I/Os go active while all unused I/Os are pulled down (PULLDOWN). The designer can control how the unused I/Os are terminated after GTS is released by setting the Bitstream Generator (BitGen) option UnusedPin to PULLUP, PULLDOWN, or FLOAT.

One clock cycle later (default), the Global Write Enable (GWE) net is released allowing the RAM and registers to change states. Once in User mode, any pull-up resistors enabled by HSWAP revert to the user settings and HSWAP is available as a general-purpose I/O. For more information on PULLUP and PULLDOWN, see Pull-Up and Pull-Down Resistors.

# Behavior of Unused I/O Pins After Configuration

By default, the Xilinx ISE development software automatically configures all unused I/O pins as input pins with individual internal pull-down resistors to GND.

This default behavior is controlled by the **UnusedPin** bitstream generator (BitGen) option, as described in Table 69.

# JTAG Boundary-Scan Capability

All Spartan-3E IOBs support boundary-scan testing compatible with IEEE 1149.1/1532 standards. During boundary-scan operations such as EXTEST and HIGHZ the pull-down resistor is active. See JTAG Mode for more information on programming via JTAG.

# **EXILINX**.

# **Block RAM**

For additional information, refer to the "Using Block RAM" chapter in UG331.

Spartan-3E devices incorporate 4 to 36 dedicated block RAMs, which are organized as dual-port configurable 18 Kbit blocks. Functionally, the block RAM is identical to the Spartan-3 architecture block RAM. Block RAM synchronously stores large amounts of data while distributed RAM, previously described, is better suited for buffering small amounts of data anywhere along signal paths. This section describes basic block RAM functions.

Each block RAM is configurable by setting the content's initial values, default signal value of the output registers, port aspect ratios, and write modes. Block RAM can be used in single-port or dual-port modes.

# Arrangement of RAM Blocks on Die

The block RAMs are located together with the multipliers on the die in one or two columns depending on the size of the device. The XC3S100E has one column of block RAM. The Spartan-3E devices ranging from the XC3S250E to XC3S1600E have two columns of block RAM. Table 21 shows the number of RAM blocks, the data storage capacity, and the number of columns for each device. Row(s) of CLBs are located above and below each block RAM column.

|           |                                  | •                                           |                      |

|-----------|----------------------------------|---------------------------------------------|----------------------|

| Device    | Total<br>Number of<br>RAM Blocks | Total<br>Addressable<br>Locations<br>(bits) | Number of<br>Columns |

| XC3S100E  | 4                                | 73,728                                      | 1                    |

| XC3S250E  | 12                               | 221,184                                     | 2                    |

| XC3S500E  | 20                               | 368,640                                     | 2                    |

| XC3S1200E | 28                               | 516,096                                     | 2                    |

| XC3S1600E | 36                               | 663,552                                     | 2                    |

#### Table 21: Number of RAM Blocks by Device

Immediately adjacent to each block RAM is an embedded 18x18 hardware multiplier. The upper 16 bits of the block RAM's Port A Data input bus are shared with the upper 16 bits of the A multiplicand input bus of the multiplier. Similarly, the upper 16 bits of Port B's data input bus are shared with the B multiplicand input bus of the multiplier.

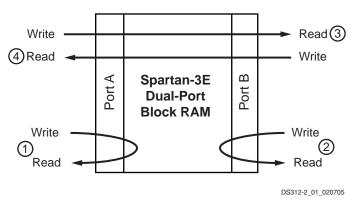

# The Internal Structure of the Block RAM

The block RAM has a dual port structure. The two identical data ports called A and B permit independent access to the common block RAM, which has a maximum capacity of 18,432 bits, or 16,384 bits with no parity bits (see parity bits description in Table 22). Each port has its own dedicated set of data, control, and clock lines for synchronous read

and write operations. There are four basic data paths, as shown in Figure 30:

- 1. Write to and read from Port A

- 2. Write to and read from Port B

- 3. Data transfer from Port A to Port B

- 4. Data transfer from Port B to Port A

Figure 30: Block RAM Data Paths

## **Number of Ports**

A choice among primitives determines whether the block RAM functions as dual- or single-port memory. A name of the form RAMB16\_S[w<sub>A</sub>]\_S[w<sub>B</sub>] calls out the dual-port primitive, where the integers  $w_A$  and  $w_B$  specify the total data path width at ports A and B, respectively. Thus, a RAMB16\_S9\_S18 is a dual-port RAM with a 9-bit Port A and an 18-bit Port B. A name of the form RAMB16\_S[w] identifies the single-port primitive, where the integer w specifies the total data path width of the lone port A. A RAMB16\_S18 is a single-port RAM with an 18-bit port.

# **Port Aspect Ratios**

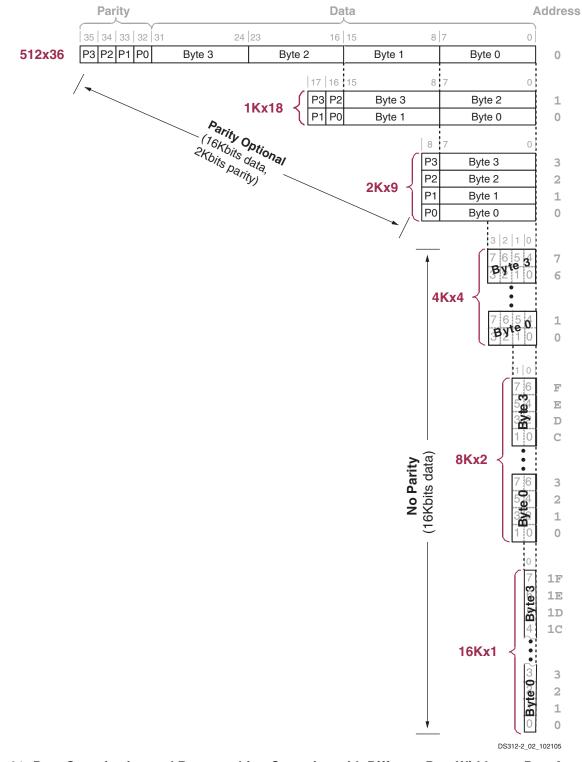

Each port of the block RAM can be configured independently to select a number of different possible widths for the data input (DI) and data output (DO) signals as shown in Table 22.

# **XILINX**.

# PRODUCT NOT RECOMMENDED FOR NEW DESIGNS

Figure 31: Data Organization and Bus-matching Operation with Different Port Widths on Port A and Port B

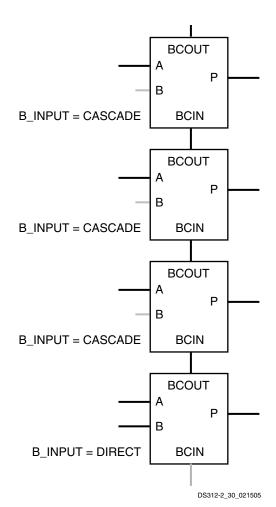

The BCIN and BCOUT ports have associated dedicated routing that connects adjacent multipliers within the same column. Via the cascade connection, the BCOUT port of one multiplier block drives the BCIN port of the multiplier block directly above it. There is no connection to the BCIN port of the bottom-most multiplier block in a column or a connection from the BCOUT port of the top-most block in a column. As an example, Figure 39 shows the multiplier cascade capability within the XC3S100E FPGA, which has a single column of multiplier, four blocks tall. For clarity, the figure omits the register control inputs.

Figure 39: Multiplier Cascade Connection

When using the BREG register, the cascade connection forms a shift register structure typically used in DSP algorithms such as direct-form FIR filters. When the BREG register is omitted, the cascade structure essentially feeds the same input value to more than one multiplier. This parallel connection serves to create wide-input multipliers, implement transpose FIR filters, and is used in any application that requires that several multipliers have the same input value.

# Configuration

For additional information on configuration, refer to UG332: *Spartan-3 Generation Configuration User Guide.*

# **Differences from Spartan-3 FPGAs**

In general, Spartan-3E FPGA configuration modes are a superset to those available in Spartan-3 FPGAs. Two new modes added in Spartan-3E FPGAs provide a glueless configuration interface to industry-standard parallel NOR Flash and SPI serial Flash memories.

# **Configuration Process**

The function of a Spartan-3E FPGA is defined by loading application-specific configuration data into the FPGA's internal, reprogrammable CMOS configuration latches (CCLs), similar to the way a microprocessor's function is defined by its application program. For FPGAs, this configuration process uses a subset of the device pins, some of which are dedicated to configuration; other pins are merely borrowed and returned to the application as general-purpose user I/Os after configuration completes.

Spartan-3E FPGAs offer several configuration options to minimize the impact of configuration on the overall system design. In some configuration modes, the FPGA generates a clock and loads itself from an external memory source, either serially or via a byte-wide data path. Alternatively, an external host such as a microprocessor downloads the FPGA's configuration data using a simple synchronous serial interface or via a byte-wide peripheral-style interface. Furthermore, multiple-FPGA designs share a single configuration memory source, creating a structure called a daisy chain.

Three FPGA pins—M2, M1, and M0—select the desired configuration mode. The mode pin settings appear in Table 44. The mode pin values are sampled during the start of configuration when the FPGA's INIT\_B output goes High. After the FPGA completes configuration, the mode pins are available as user I/Os.

|                                                                    | Master<br>Serial                          | SPI                                   | BPI                                                                                              | Slave Parallel                                                                                       | Slave Serial                                                                        | JTAG                                                                              |

|--------------------------------------------------------------------|-------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| M[2:0] mode pin settings                                           | <0:0:0>                                   | <0:0:1>                               | <0:1:0>=Up<br><0:1:1>=Down                                                                       | <1:1:0>                                                                                              | <1:1:1>                                                                             | <1:0:1>                                                                           |

| Data width                                                         | Serial                                    | Serial                                | Byte-wide                                                                                        | Byte-wide                                                                                            | Serial                                                                              | Serial                                                                            |

| Configuration memory source                                        | Xilinx<br><u>Platform</u><br><u>Flash</u> | Industry-standard<br>SPI serial Flash | Industry-standard<br>parallel NOR<br>Flash or Xilinx<br>parallel <u>Platform</u><br><u>Flash</u> | Any source via<br>microcontroller,<br>CPU, Xilinx<br>parallel <u>Platform</u><br><u>Flash</u> , etc. | Any source via<br>microcontroller,<br>CPU, Xilinx<br><u>Platform Flash,</u><br>etc. | Any source via<br>microcontroller,<br>CPU, <u>System</u><br><u>ACE™ CF</u> , etc. |

| Clock source                                                       | Internal oscillator                       | Internal oscillator                   | Internal oscillator                                                                              | External clock<br>on CCLK pin                                                                        | External clock<br>on CCLK pin                                                       | External clock<br>on TCK pin                                                      |

| Total I/O pins borrowed during configuration                       | 8                                         | 13                                    | 46                                                                                               | 21                                                                                                   | 8                                                                                   | 0                                                                                 |

| Configuration mode for<br>downstream daisy-<br>chained FPGAs       | Slave Serial                              | Slave Serial                          | Slave Parallel                                                                                   | Slave Parallel or<br>Memory<br>Mapped                                                                | Slave Serial                                                                        | JTAG                                                                              |

| Stand-alone FPGA<br>applications (no<br>external download<br>host) | 1                                         | 1                                     | 1                                                                                                | Possible using<br>XCFxxP<br>Platform Flash,<br>which optionally<br>generates CCLK                    | Possible using<br>XCFxxP<br>Platform Flash,<br>which optionally<br>generates CCLK   |                                                                                   |

| Uses low-cost,<br>industry-standard<br>Flash                       |                                           | 1                                     | 1                                                                                                |                                                                                                      |                                                                                     |                                                                                   |

| Supports optional<br>MultiBoot,<br>multi-configuration<br>mode     |                                           |                                       | 1                                                                                                |                                                                                                      |                                                                                     |                                                                                   |

#### Table 46: Pin Behavior during Configuration (Cont'd)

| Pin Name | Master Serial | SPI (Serial<br>Flash) | BPI (Parallel<br>NOR Flash) | JTAG | Slave Parallel | Slave Serial | I/O Bank <sup>(3)</sup> |

|----------|---------------|-----------------------|-----------------------------|------|----------------|--------------|-------------------------|

| D0/DIN   | DIN           | DIN                   | D0                          |      | D0             | DIN          | 2                       |

| RDWR_B   |               |                       | RDWR_B                      |      | RDWR_B         |              | 2                       |

| A23      |               |                       | A23                         |      |                |              | 2                       |

| A22      |               |                       | A22                         |      |                |              | 2                       |

| A21      |               |                       | A21                         |      |                |              | 2                       |

| A20      |               |                       | A20                         |      |                |              | 2                       |

| A19/VS2  |               | VS2                   | A19                         |      |                |              | 2                       |

| A18/VS1  |               | VS1                   | A18                         |      |                |              | 2                       |

| A17/VS0  |               | VS0                   | A17                         |      |                |              | 2                       |

| A16      |               |                       | A16                         |      |                |              | 1                       |

| A15      |               |                       | A15                         |      |                |              | 1                       |

| A14      |               |                       | A14                         |      |                |              | 1                       |

| A13      |               |                       | A13                         |      |                |              | 1                       |

| A12      |               |                       | A12                         |      |                |              | 1                       |

| A11      |               |                       | A11                         |      |                |              | 1                       |

| A10      |               |                       | A10                         |      |                |              | 1                       |

| A9       |               |                       | A9                          |      |                |              | 1                       |

| A8       |               |                       | A8                          |      |                |              | 1                       |

| A7       |               |                       | A7                          |      |                |              | 1                       |

| A6       |               |                       | A6                          |      |                |              | 1                       |

| A5       |               |                       | A5                          |      |                |              | 1                       |

| A4       |               |                       | A4                          |      |                |              | 1                       |

| A3       |               |                       | A3                          |      |                |              | 1                       |

| A2       |               |                       | A2                          |      |                |              | 1                       |

| A1       |               |                       | A1                          |      |                |              | 1                       |

| A0       |               |                       | A0                          |      |                |              | 1                       |

| LDC0     |               |                       | LDC0                        |      |                |              | 1                       |

| LDC1     |               |                       | LDC1                        |      |                |              | 1                       |

| LDC2     |               |                       | LDC2                        |      |                |              | 1                       |

| HDC      |               |                       | HDC                         |      |                |              | 1                       |

#### Notes:

1. Gray shaded cells represent pins that are in a high-impedance state (Hi-Z, floating) during configuration. These pins have an optional internal pull-up resistor to their respective V<sub>CCO</sub> supply pin that is active throughout configuration if the HSWAP input is Low.

2. Yellow shaded cells represent pins with an internal pull-up resistor to its respective voltage supply rail that is active during configuration, regardless of the HSWAP pin.

3. Note that dual-purpose outputs are supplied by  $V_{CCO}$ , and configuration inputs are supplied by  $V_{CCAUX}$ .

The HSWAP pin itself has a pull-up resistor enabled during configuration. However, the VCCO\_0 supply voltage must be applied before the pull-up resistor becomes active. If the VCCO\_0 supply ramps after the VCCO\_2 power supply, do not let HSWAP float; tie HSWAP to the desired logic level externally.

Spartan-3E FPGAs have only six dedicated configuration pins, including the DONE and PROG\_B pins, and the four JTAG boundary-scan pins: TDI, TDO, TMS, and TCK. All other configuration pins are dual-purpose I/O pins and are available to the FPGA application after the DONE pin goes High. See <u>Start-Up</u> for additional information. Table 47 shows the default I/O standard setting for the various configuration pins during the configuration process. The configuration interface is designed primarily for 2.5V operation when the VCCO\_2 (and VCCO\_1 in BPI mode) connects to 2.5V.

| Table 47: Default I/O Standard Setting During Con | ıfig- |

|---------------------------------------------------|-------|

| uration (VCCO_2 = 2.5V)                           |       |

| Pin(s)              | I/O Standard | Output Drive | Slew Rate |

|---------------------|--------------|--------------|-----------|

| All, including CCLK | LVCMOS25     | 8 mA         | Slow      |

| Pin Name | FPGA<br>Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | During Configuration                                                                                                                                                                                                  | After Configuration                                                                                                                                                                                                        |

|----------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VS[2:0]  | Input                              | Variant Select. Instructs the FPGA how<br>to communicate with the attached SPI<br>Flash PROM. See Design Considerations<br>for the HSWAP, M[2:0], and VS[2:0] Pins.                                                                                                                                                                                                                                                                                                                                        | Must be at the logic levels shown<br>in Table 53. Sampled when<br>INIT_B goes High.                                                                                                                                   | User I/O                                                                                                                                                                                                                   |

| MOSI     | Output                             | Serial Data Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FPGA sends SPI Flash memory<br>read commands and starting<br>address to the PROM's serial<br>data input.                                                                                                              | User I/O                                                                                                                                                                                                                   |

| DIN      | Input                              | Serial Data Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FPGA receives serial data from PROM's serial data output.                                                                                                                                                             | User I/O                                                                                                                                                                                                                   |

| CSO_B    | Output                             | Chip Select Output. Active Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Connects to the SPI Flash<br>PROM's chip-select input. If<br>HSWAP = 1, connect this signal<br>to a 4.7 k $\Omega$ pull-up resistor to<br>3.3V.                                                                       | Drive CSO_B High after<br>configuration to disable the<br>SPI Flash and reclaim the<br>MOSI, DIN, and CCLK pins.<br>Optionally, re-use this pin<br>and MOSI, DIN, and CCLK<br>to continue communicating<br>with SPI Flash. |

| CCLK     | Output                             | <b>Configuration Clock</b> . Generated by<br>FPGA internal oscillator. Frequency<br>controlled by <b>ConfigRate</b> bitstream<br>generator option. If CCLK PCB trace is<br>long or has multiple connections,<br>terminate this output to maintain signal<br>integrity. See CCLK Design<br>Considerations.                                                                                                                                                                                                  | Drives PROM's clock input.                                                                                                                                                                                            | User I/O                                                                                                                                                                                                                   |

| DOUT     | Output                             | Serial Data Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Actively drives. Not used in<br>single-FPGA designs. In a<br>daisy-chain configuration, this<br>pin connects to DIN input of the<br>next FPGA in the chain.                                                           | User I/O                                                                                                                                                                                                                   |

| INIT_B   | Open-drain<br>bidirectional<br>I/O | <b>Initialization Indicator</b> . Active Low.<br>Goes Low at start of configuration during<br>Initialization memory clearing process.<br>Released at end of memory clearing,<br>when mode select pins are sampled. In<br>daisy-chain applications, this signal<br>requires an external 4.7 k $\Omega$ pull-up<br>resistor to VCCO_2.                                                                                                                                                                       | Active during configuration. If<br>SPI Flash PROM requires<br>> 2 ms to awake after powering<br>on, hold INIT_B Low until PROM<br>is ready. If CRC error detected<br>during configuration, FPGA<br>drives INIT_B Low. | User I/O. If unused in the application, drive INIT_B<br>High.                                                                                                                                                              |

| DONE     | Open-drain<br>bidirectional<br>I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external 330 $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                                              | Low indicates that the FPGA is not yet configured.                                                                                                                                                                    | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully configured.                                                                                                                     |

| PROG_B   | Input                              | <b>Program FPGA</b> . Active Low. When<br>asserted Low for 500 ns or longer, forces<br>the FPGA to restart its configuration<br>process by clearing configuration<br>memory and resetting the DONE and<br>INIT_B pins once PROG_B returns High.<br>Recommend external 4.7 kΩ pull-up<br>resistor to 2.5V. Internal pull-up value<br>may be weaker (see Table 78). If driving<br>externally with a 3.3V output, use an<br>open-drain or open-collector driver or use<br>a current limiting series resistor. | Must be High to allow configuration to start.                                                                                                                                                                         | Drive PROG_B Low and<br>release to reprogram FPGA.<br>Hold PROG_B to force<br>FPGA I/O pins into Hi-Z,<br>allowing direct programming<br>access to SPI Flash PROM<br>pins.                                                 |

#### Table 55: Serial Peripheral Interface (SPI) Connections (Cont'd)

| Pin Name | FPGA Direction                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | During Configuration                                                                                      | After Configuration                                                                                    |

|----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| INIT_B   | Open-drain<br>bidirectional I/O | <b>Initialization Indicator</b> . Active Low.<br>Goes Low at the start of<br>configuration during the Initialization<br>memory clearing process. Released<br>at the end of memory clearing, when<br>mode select pins are sampled. In<br>daisy-chain applications, this signal<br>requires an external 4.7 k $\Omega$ pull-up<br>resistor to VCCO_2.                                                                                                                               | Active during configuration. If<br>CRC error detected during<br>configuration, FPGA drives<br>INIT_B Low. | User I/O. If unused in the<br>application, drive INIT_B<br>High.                                       |

| DONE     | Open-drain<br>bidirectional I/O | <b>FPGA Configuration Done</b> . Low during configuration. Goes High when FPGA successfully completes configuration. Requires external 330 $\Omega$ pull-up resistor to 2.5V.                                                                                                                                                                                                                                                                                                     | Low indicates that the FPGA is not yet configured.                                                        | Pulled High via external<br>pull-up. When High,<br>indicates that the FPGA<br>successfully configured. |

| PROG_B   | Input                           | <b>Program FPGA</b> . Active Low. When asserted Low for 500 ns or longer, forces the FPGA to restart its configuration process by clearing configuration memory and resetting the DONE and INIT_B pins once PROG_B returns High. Recommend external 4.7 k $\Omega$ pull-up resistor to 2.5V. Internal pull-up value may be weaker (see Table 78). If driving externally with a 3.3V output, use an open-drain or open-collector driver or use a current limiting series resistor. | Must be High to allow<br>configuration to start.                                                          | Drive PROG_B Low and<br>release to reprogram<br>FPGA.                                                  |

#### Table 65: Slave Parallel Mode Connections (Cont'd)

### **Voltage Compatibility**

W Most Slave Parallel interface signals are within the FPGA's I/O Bank 2, supplied by the VCCO\_2 supply input. The VCCO\_2 voltage can be 1.8V, 2.5V, or 3.3V to match the requirements of the external host, ideally 2.5V. Using 1.8V or 3.3V requires additional design considerations as the DONE and PROG\_B pins are powered by the FPGA's 2.5V V<sub>CCAUX</sub> supply. See <u>XAPP453</u>: *The 3.3V Configuration of Spartan-3 FPGAs* for additional information.

### **Daisy-Chaining**

If the application requires multiple FPGAs with different configurations, then configure the FPGAs using a daisy chain. Use Slave Parallel mode (M[2:0] = <1:1:0>) for all FPGAs in the daisy-chain. The schematic in Figure 62 is optimized for FPGA downloading and does not support the SelectMAP read interface. The FPGA's RDWR\_B pin must be Low during configuration.

After the lead FPGA is filled with its configuration data, the lead FPGA enables the next FPGA in the daisy-chain by asserting is chip-select output, CSO\_B.

# **Switching Characteristics**

All Spartan-3E FPGAs ship in two speed grades: -4 and the higher performance -5. Switching characteristics in this document may be designated as Advance, Preliminary, or Production, as shown in Table 84. Each category is defined as follows:

<u>Advance</u>: These specifications are based on simulations only and are typically available soon after establishing FPGA specifications. Although speed grades with this designation are considered relatively stable and conservative, some under-reporting might still occur.

**Preliminary**: These specifications are based on complete early silicon characterization. Devices and speed grades with this designation are intended to give a better indication of the expected performance of production silicon. The probability of under-reporting preliminary delays is greatly reduced compared to Advance data.

**Production**: These specifications are approved once enough production silicon of a particular device family member has been characterized to provide full correlation between speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes. Typically, the slowest speed grades transition to Production before faster speed grades.

# **Software Version Requirements**

Production-quality systems must use FPGA designs compiled using a speed file designated as PRODUCTION status. FPGAs designs using a less mature speed file designation should only be used during system prototyping or pre-production qualification. FPGA designs with speed files designated as Advance or Preliminary should not be used in a production-quality system.

Whenever a speed file designation changes, as a device matures toward Production status, rerun the latest Xilinx ISE software on the FPGA design to ensure that the FPGA design incorporates the latest timing information and software updates.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. **Unless** otherwise noted, the published parameter values apply to all Spartan-3E devices. AC and DC characteristics are specified using the same numbers for both commercial and industrial grades.

Create a Xilinx user account and sign up to receive automatic e-mail notification whenever this data sheet or the associated user guides are updated.

Sign Up for Alerts on Xilinx.com https://secure.xilinx.com/webreg/register.do

?group=myprofile&languageID=1

Timing parameters and their representative values are selected for inclusion below either because they are important as general design requirements or they indicate fundamental device performance characteristics. The Spartan-3E speed files (v1.27), part of the Xilinx Development Software, are the original source for many but not all of the values. The speed grade designations for these files are shown in Table 84. For more complete, more precise, and worst-case data, use the values reported by the Xilinx static timing analyzer (TRACE in the Xilinx development software) and back-annotated to the simulation netlist.

| Device    | Advance | Preliminary | Production   |

|-----------|---------|-------------|--------------|

| XC3S100E  |         |             | -MIN, -4, -5 |

| XC3S250E  |         |             | -MIN, -4, -5 |

| XC3S500E  |         |             | -MIN, -4, -5 |

| XC3S1200E |         |             | -MIN, -4, -5 |

| XC3S1600E |         |             | -MIN, -4, -5 |

|           |         | •           |              |

Table 84: Spartan-3E v1.27 Speed Grade Designations

Table 85 provides the history of the Spartan-3E speed filessince all devices reached Production status.

| Table | 85: | Spartan-3E | Speed File | Version | History |

|-------|-----|------------|------------|---------|---------|

|-------|-----|------------|------------|---------|---------|

| Version | ISE<br>Release | Description                                                                        |

|---------|----------------|------------------------------------------------------------------------------------|

| 1.27    | 9.2.03i        | Added XA Automotive.                                                               |

| 1.26    | 8.2.02i        | Added -0/-MIN speed grade, which includes minimum values.                          |

| 1.25    | 8.2.01i        | Added XA Automotive devices to speed file. Improved model for left and right DCMs. |

| 1.23    | 8.2i           | Updated input setup/hold values based<br>on default IFD_DELAY_VALUE<br>settings.   |

| 1.21    | 8.1.03i        | All Spartan-3E FPGAs and all speed grades elevated to Production status.           |

# Table 97: Recommended Number of SimultaneouslySwitching Outputs per V<sub>CCO</sub>/GND Pair

Table 97: Recommended Number of SimultaneouslySwitching Outputs per V<sub>CCO</sub>/GND Pair (Cont'd)

|                        |        |     | Package Type |           |           |           |                                  |

|------------------------|--------|-----|--------------|-----------|-----------|-----------|----------------------------------|

| Signal Sta<br>(IOSTAN) |        |     | VQ<br>100    | TQ<br>144 | PQ<br>208 | CP<br>132 | FT256<br>FG320<br>FG400<br>FG484 |

| LVCMOS15               | Slow   | 2   | 16           | 10        | 10        | 19        | 55                               |

|                        |        | 4   | 8            | 7         | 7         | 9         | 31                               |

|                        |        | 6   | 6            | 5         | 5         | 9         | 18                               |

|                        | Fast   | 2   | 9            | 9         | 9         | 13        | 25                               |

|                        |        | 4   | 7            | 7         | 7         | 7         | 16                               |

|                        |        | 6   | 5            | 5         | 5         | 5         | 13                               |

| LVCMOS12               | Slow   | 2   | 17           | 11        | 11        | 16        | 55                               |

|                        | Fast   | 2   | 10           | 10        | 10        | 10        | 31                               |

| PCI33_3                |        |     | 8            | 8         | 8         | 16        | 16                               |

| PCI66_3                |        |     | 8            | 8         | 8         | 13        | 13                               |

| PCIX                   |        |     | 7            | 7         | 7         | 11        | 11                               |

| HSTL_I_18              |        |     | 10           | 10        | 10        | 16        | 17                               |

| HSTL_III_18            |        |     | 10           | 10        | 10        | 16        | 16                               |

| SSTL18_I               |        |     | 9            | 9         | 9         | 15        | 15                               |

| SSTL2_I                |        |     | 12           | 12        | 12        | 18        | 18                               |

| Differential           | Standa | rds | (Numb        | er of I/  | 0 Pairs   | or Cha    | innels)                          |

| LVDS_25                |        |     | 6            | 6         | 6         | 12        | 20                               |

| BLVDS_25               |        |     | 4            | 4         | 4         | 4         | 4                                |

| MINI_LVDS_2            | 25     |     | 6            | 6         | 6         | 12        | 20                               |

| LVPECL_25              |        |     |              |           | Input O   | nly       |                                  |

| RSDS_25                |        |     | 6            | 6         | 6         | 12        | 20                               |

| DIFF_HSTL_I_18         |        |     | 5            | 5         | 5         | 8         | 8                                |

| DIFF_HSTL_I            | III_18 |     | 5            | 5         | 5         | 8         | 8                                |

| DIFF_SSTL18            | 3_I    |     | 4            | 4         | 4         | 7         | 7                                |

| DIFF_SSTL2_            | _1     |     | 6            | 6         | 6         | 9         | 8                                |

#### Notes:

- The numbers in this table are recommendations that assume sound board layout practice. This table assumes the following parasitic factors: combined PCB trace and land inductance per VCCO and GND pin of 1.0 nH, receiver capacitive load of 15 pF. Test limits are the VIL/VIH voltage limits for the respective I/O standard.

- 2. The PQ208 results are based on physical measurements of a PQ208 package soldered to a typical printed circuit board. All other results are based on worst-case simulation and an interpolation of the PQ208 physical results.

- If more than one signal standard is assigned to the I/Os of a given bank, refer to <u>XAPP689</u>: Managing Ground Bounce in Large FPGAs for information on how to perform weighted average SSO calculations.

## Configurable Logic Block (CLB) Timing

### Table 98: CLB (SLICEM) Timing

|                      |                                                                                                                                               |      | Speed Grade |      |      |     |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|------|------|-----|

| Symbol               | Description                                                                                                                                   | -5   |             | -    | -4   |     |

|                      |                                                                                                                                               | Min  | Max         | Min  | Max  |     |

| Clock-to-Output T    | imes                                                                                                                                          |      |             |      |      |     |

| Т <sub>СКО</sub>     | When reading from the FFX (FFY) Flip-Flop, the time<br>from the active transition at the CLK input to data<br>appearing at the XQ (YQ) output |      | 0.52        | -    | 0.60 | ns  |

| Setup Times          |                                                                                                                                               |      |             | 1    |      |     |

| T <sub>AS</sub>      | Time from the setup of data at the F or G input to the active transition at the CLK input of the CLB                                          | 0.46 | -           | 0.52 | -    | ns  |

| T <sub>DICK</sub>    | Time from the setup of data at the BX or BY input to the active transition at the CLK input of the CLB                                        | 1.58 | -           | 1.81 | -    | ns  |

| Hold Times           |                                                                                                                                               |      |             |      |      |     |

| T <sub>AH</sub>      | Time from the active transition at the CLK input to the point where data is last held at the F or G input                                     | 0    | -           | 0    | -    | ns  |

| Т <sub>СКDI</sub>    | Time from the active transition at the CLK input to the point where data is last held at the BX or BY input                                   | 0    | -           | 0    | -    | ns  |

| Clock Timing         |                                                                                                                                               |      |             |      |      |     |

| Т <sub>СН</sub>      | The High pulse width of the CLB's CLK signal                                                                                                  | 0.70 | -           | 0.80 | -    | ns  |

| T <sub>CL</sub>      | The Low pulse width of the CLK signal                                                                                                         | 0.70 | -           | 0.80 | -    | ns  |

| F <sub>TOG</sub>     | Toggle frequency (for export control)                                                                                                         | 0    | 657         | 0    | 572  | MHz |

| Propagation Time     | S                                                                                                                                             |      |             |      |      |     |

| T <sub>ILO</sub>     | The time it takes for data to travel from the CLB's F (G) input to the X (Y) output                                                           | -    | 0.66        | -    | 0.76 | ns  |

| Set/Reset Pulse W    | lidth                                                                                                                                         |      |             |      |      |     |

| T <sub>RPW_CLB</sub> | The minimum allowable pulse width, High or Low, to the CLB's SR input                                                                         | 1.57 | -           | 1.80 | -    | ns  |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 77.

### Phase Shifter (PS)

#### Table 108: Recommended Operating Conditions for the PS in Variable Phase Mode

|                                     |                                                       |     | Speed Grade |     |     |     |  |

|-------------------------------------|-------------------------------------------------------|-----|-------------|-----|-----|-----|--|

| Symbol                              | Description                                           | -   | -5          |     | -4  |     |  |

|                                     |                                                       | Min | Мах         | Min | Max |     |  |

| Operating Frequ                     | iency Ranges                                          |     |             |     |     |     |  |

| PSCLK_FREQ<br>(F <sub>PSCLK</sub> ) | Frequency for the PSCLK input                         | 1   | 167         | 1   | 167 | MHz |  |

| Input Pulse Req                     | uirements                                             |     | •           | •   | -   |     |  |

| PSCLK_PULSE                         | PSCLK pulse width as a percentage of the PSCLK period | 40% | 60%         | 40% | 60% | -   |  |

#### Table 109: Switching Characteristics for the PS in Variable Phase Mode

| Symbol                                                                                                                                                                                      | Description                                                                                        | Equa                                 | Units                                           |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------|-------|

| Phase Shifting Range                                                                                                                                                                        |                                                                                                    |                                      |                                                 |       |

| AX_STEPS <sup>(2)</sup> Maximum allowed number of DCM_DELAY_ST<br>for a given CLKIN clock period, where T = CLKIN clock period, where T = CLKIN clock period, where T = CLKIN clock period. |                                                                                                    | CLKIN < 60 MHz                       | ±[INTEGER(10 ●<br>(T <sub>CLKIN</sub> – 3 ns))] | steps |

|                                                                                                                                                                                             | period in ns. If using CLKIN_DIVIDE_BY_2 = TRUE, double the effective clock period. <sup>(3)</sup> | CLKIN ≥ 60 MHz                       | ±[INTEGER(15 ●<br>(T <sub>CLKIN</sub> – 3 ns))] | steps |

| FINE_SHIFT_RANGE_MIN                                                                                                                                                                        | Minimum guaranteed delay for variable phase shifting                                               | ±[MAX_STEPS •<br>DCM_DELAY_STEP_MIN] |                                                 | ns    |

| FINE_SHIFT_RANGE_MAX                                                                                                                                                                        | Maximum guaranteed delay for variable phase shifting                                               | ±[MAX_9<br>DCM_DELAY                 | ns                                              |       |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 77 and Table 108.

- 2. The maximum variable phase shift range, MAX\_STEPS, is only valid when the DCM is has no initial fixed phase shifting, i.e., the PHASE\_SHIFT attribute is set to 0.

- 3. The DCM\_DELAY\_STEP values are provided at the bottom of Table 105.

### **Miscellaneous DCM Timing**

#### Table 110: Miscellaneous DCM Timing

| Symbol                             | Description                                                                                                                                   |     | Max | Units           |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|

| DCM_RST_PW_MIN <sup>(1)</sup>      | Minimum duration of a RST pulse width                                                                                                         | 3   | -   | CLKIN<br>cycles |

| DCM_RST_PW_MAX <sup>(2)</sup>      | Maximum duration of a RST pulse width                                                                                                         | N/A | N/A | seconds         |

| DCM_CONFIG_LAG_TIME <sup>(3)</sup> | Maximum duration from $V_{\rm CCINT}$ applied to FPGA configuration successfully completed (DONE pin goes High) and clocks applied to DCM DLL | N/A | N/A | minutes         |

#### Notes:

1. This limit only applies to applications that use the DCM DLL outputs (CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV). The DCM DFS outputs (CLKFX, CLKFX180) are unaffected.

- 2. This specification is equivalent to the Virtex-4 DCM\_RESET specification. This specification does not apply for Spartan-3E FPGAs.

- 3. This specification is equivalent to the Virtex-4 TCONFIG specification. This specification does not apply for Spartan-3E FPGAs.

## **Configuration Clock (CCLK) Characteristics**

### Table 112: Master Mode CCLK Output Period by ConfigRate Option Setting

| Symbol              | Description                                | <i>ConfigRate</i><br>Setting | Temperature<br>Range | Minimum | Maximum | Units |

|---------------------|--------------------------------------------|------------------------------|----------------------|---------|---------|-------|

| T <sub>CCLK1</sub>  | CCLK clock period by<br>ConfigRate setting | 1<br>(power-on value and     | Commercial           | 570     | 1,250   | ns    |

| CCLK1               | Comgnate setting                           | default value)               | Industrial           | 485     | 1,230   | ns    |

| т                   | _                                          | 3                            | Commercial           | 285     | 625     | ns    |

| T <sub>CCLK3</sub>  |                                            | 3                            | Industrial           | 242     | 020     | ns    |

| т                   |                                            | 6                            | Commercial           | 142     | 313     | ns    |

| T <sub>CCLK6</sub>  |                                            | 0                            | Industrial           | 121     |         | ns    |

| т                   | _                                          | 12                           | Commercial           | 71.2    | 157     | ns    |

| T <sub>CCLK12</sub> |                                            | 12                           | Industrial           | 60.6    |         | ns    |

| Τ                   |                                            | 25                           | Commercial           | 35.5    | - 78.2  | ns    |

| T <sub>CCLK25</sub> |                                            | 25                           | Industrial           | 30.3    | 70.2    | ns    |

| Τ                   |                                            | 50                           | Commercial           | 17.8    | 39.1    | ns    |

| T <sub>CCLK50</sub> |                                            | 50                           | Industrial           | 15.1    |         | ns    |

#### Notes:

1. Set the ConfigRate option value when generating a configuration bitstream. See Bitstream Generator (BitGen) Options in Module 2.

| Symbol              | Description                                                  | <i>ConfigRate</i><br>Setting | Temperature<br>Range | Minimum | Maximum | Units |

|---------------------|--------------------------------------------------------------|------------------------------|----------------------|---------|---------|-------|

| F <sub>CCLK1</sub>  | Equivalent CCLK clock frequency by <i>ConfigRate</i> setting | 1<br>(power-on value and     | Commercial           | 0.8     | 1.8     | MHz   |

| ' CCLK1             | by <b>comgnate</b> setting                                   | default value)               | Industrial           | 0.0     | 2.1     | MHz   |

| E                   | _                                                            | 3                            | Commercial           | 1.6     | 3.6     | MHz   |

| F <sub>CCLK3</sub>  |                                                              | 5                            | Industrial           | 1.0     | 4.2     | MHz   |

| Family              | _                                                            | 6                            | Commercial           | 3.2     | 7.1     | MHz   |

| F <sub>CCLK6</sub>  |                                                              | 0                            | Industrial           | 5.2     | 8.3     | MHz   |

| F                   |                                                              | 12                           | Commercial           | 6.4     | 14.1    | MHz   |

| F <sub>CCLK12</sub> |                                                              | 12                           | Industrial           | 0.4     | 16.5    | MHz   |

| E                   |                                                              | 25                           | Commercial           | 12.8    | 28.1    | MHz   |

| F <sub>CCLK25</sub> |                                                              | 25                           | Industrial           | 12.0    | 33.0    | MHz   |

| Familia             |                                                              | 50                           | Commercial           | 25.6    | 56.2    | MHz   |

| F <sub>CCLK50</sub> |                                                              | 50                           | Industrial           | 20.0    | 66.0    | MHz   |

#### Table 114: Master Mode CCLK Output Minimum Low and High Time

| Symbol Description |                                              |            | ConfigRate Setting |     |    |      |      |     | Units |

|--------------------|----------------------------------------------|------------|--------------------|-----|----|------|------|-----|-------|

| Symbol             | Description                                  | 1          |                    | 3   | 6  | 12   | 25   | 50  | Units |

| T <sub>MCCL,</sub> | T <sub>MCCL</sub> , Master mode CCLK minimum |            | 276                | 138 | 69 | 34.5 | 17.1 | 8.5 | ns    |

| MCCH               |                                              | Industrial | 235                | 117 | 58 | 29.3 | 14.5 | 7.3 | ns    |

### Table 115: Slave Mode CCLK Input Low and High Time

| Symbol                                  | Description            | Min | Мах | Units |

|-----------------------------------------|------------------------|-----|-----|-------|

| T <sub>SCCL,</sub><br>T <sub>SCCH</sub> | CCLK Low and High time | 5   | ∞   | ns    |

#

### Table 117: Timing for the Slave Parallel Configuration Mode (Cont'd)

| Symbol                |                                | Descriptio                                 |                                       | All Spee | s<br>Units |     |  |

|-----------------------|--------------------------------|--------------------------------------------|---------------------------------------|----------|------------|-----|--|

| Symbol                |                                | Descriptio                                 | 11                                    | Min Max  |            |     |  |

| Clock Timing          |                                |                                            |                                       |          |            |     |  |

| Т <sub>ССН</sub>      | The High pulse width at the Co | The High pulse width at the CCLK input pin |                                       |          | -          | ns  |  |

| T <sub>CCL</sub>      | The Low pulse width at the CO  | CLK input pin                              |                                       | 5        | -          | ns  |  |

| F <sub>CCPAR</sub>    | Frequency of the clock signal  | No bitstream                               | Not using the BUSY pin <sup>(2)</sup> | 0        | 50         | MHz |  |

| at the CCLK input pin | compression                    | Using the BUSY pin                         | 0                                     | 66       | MHz        |     |  |

|                       |                                | With bitstream compression                 |                                       |          | 20         | MHz |  |

Notes:

- 1. The numbers in this table are based on the operating conditions set forth in Table 77.

- 2. In the Slave Parallel mode, it is necessary to use the BUSY pin when the CCLK frequency exceeds this maximum specification.

- 3. Some Xilinx documents refer to Parallel modes as "SelectMAP" modes.

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/01/05 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11/23/05 | 2.0     | Added AC timing information and additional DC specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 03/22/06 | 3.0     | Upgraded data sheet status to Preliminary. Finalized production timing parameters. All speed grades for all Spartan-3E FPGAs are now Production status using the v1.21 speed files, as shown in Table 84. Expanded description in Note 2, Table 78. Updated pin-to-pin and clock-to-output timing based on final characterization, shown in Table 86. Updated system-synchronous input setup and hold times based on final characterization, shown in Table 87 and Table 88. Updated other I/O timing in Table 90. Provided input and output adjustments for LVPECL_25, DIFF_SSTL and DIFF_HSTL I/O standards that supersede the v1.21 speed file values, in Table 91 and Table 94. Reduced I/O three-state and set/reset delays in Table 93. Added XC3S100E FPGA in CP132 package to Table 96. Increased T <sub>AS</sub> slice flip-flop timing by 100 ps in Table 98. Updated distributed RAM timing in Table 99 and SRL16 timing in Table 100. Updated global clock timing, removed left/right clock buffer limits in Table 101. Updated block RAM timing in Table 103. Added DCM parameters for remainder of Step 0 device; added improved Step 1 DCM performance to Table 104, Table 105, Table 106, and Table 107. Added minimum INIT_B pulse width specification, T <sub>INIT</sub> , in Table 111. Increased data hold time for Slave Parallel mode to 1.0 ns (T <sub>SMCCD</sub> ) in Table 106, and Table 107. Corrected links in Table 118 and Table 120. Added MultiBoot timing specifications to Table 122. |

| 04/07/06 | 3.1     | Improved SSO limits for LVDS_25, MINI_LVDS_25, and RSDS_25 I/O standards in the QFP packages (Table 97). Removed potentially confusing Note 2 from Table 78.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |